Issue Date: January 7, 2010

# ML610Q340/ML610340

8-bit Microcontroller with Voice Output Function

#### **GENERAL DESCRIPTION**

Equipped with an OKI SEMICONDUCTOR original 8-bit CPU nX-U8/100, the ML610Q340/ML610340 is a high-performance 8-bit CMOS microcontroller that integrates a wide variety of peripherals such as a timer, synchronous serial port, and voice output function. The nX-U8/100 CPU is capable of executing instructions efficiently on a one-instruction-per-clock-pulse basis through parallel processing by the 3-stage pipelined architecture. The microcontroller is also equipped with a flash memory that has achieved low voltage and low power consumption (at read) equivalent to mask ROMs, so it is best suited to battery-driven applications such as cellular phones. In addition, it has an on-chip debugging function, which allows software debugging/rewriting with the LSI mounted on the board.

#### **FEATURES**

#### • CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction repertoire: 16-bit length instructions

- Instruction set: Transfer, arithmetic operations, comparison, logical operations, multiply/divide operations, bit manipulation, bit logical operations, jump, conditional jump, call return stack manipulation, and arithmetic shift instructions.

- Built-in on-chip debugging function

- Minimum instruction execution time:

0.244 μs (@ 4.096 MHz system clock)

#### • Internal memory

- ML610Q340

- Has 96-Kbyte flash memory (48K × 16-bit) built in. (including unusable 1KByte TEST area)

- ML610340

- Has 96-Kbyte mask memory (48K × 16-bit) built in. (including unusable 1KByte TEST area)

- Has 512-byte RAM (512  $\times$  8-bit) built in.

#### • Interrupt controller

- Non-maskable interrupt: 2 sources (1 internal source and 1 external sources)

- Maskable interrupt: 12 sources (8 internal sources and 4 external sources)

## • Time-base counter

- Low-speed side time-base counter × 1ch

- High-speed side time-base counter × 1ch

# • Watchdog timer

- Generates a non-maskable interrupt upon the first overflow and a system reset occurs upon the second

- Free-running

- Selectable overflow period: 4 types (125 ms, 500 ms, 2 sec, 8 sec)

## • Timer

- 8-bit × 2ch (16-bit configuration also enabled)

#### Voice output function

- Voice synthesis method: 4-bit ADPCM2 / 8-bit non-linear PCM / 8-bit PCM / 16-bit PCM

- Sampling frequency: 6.4/8/10.7/12.8/16/21.3/25.6/32 kHz

### • Speaker amplifier output power

-1W(at 5V)

## • Synchronous serial port

- Master/slave selectable

- LSB/MSB-first selectable

- 8-bit/16-bit length selectable

#### • General-purpose port

- Input-only port  $\times$  4ch

- Output-only port × 4ch (those as secondary functions are also included)

- Input-output port × 4ch (those as secondary functions are also included)

#### • Reset

- Resetting by the RESET\_N pin

- Resetting upon power-on detection

- Resetting upon WDT overflow detection

#### • Clock

Low-speed side clock

Internal frequency division (1/128 of the high-speed side clock)

High-speed side clock

Crystal/ceramic oscillation (4.096 MHz), external clock

## • Power management

- HALT mode: Halts the execution of instructions issued by the CPU (the peripheral circuits continue operating)

- STOP mode: Stops low-speed and high-speed oscillation (the CPU and the peripheral circuits stop operating)

- Clock gear: Allows changing the frequency of the high-speed system clock by software (oscillator clock divided by 1, 2, 4, or 8)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

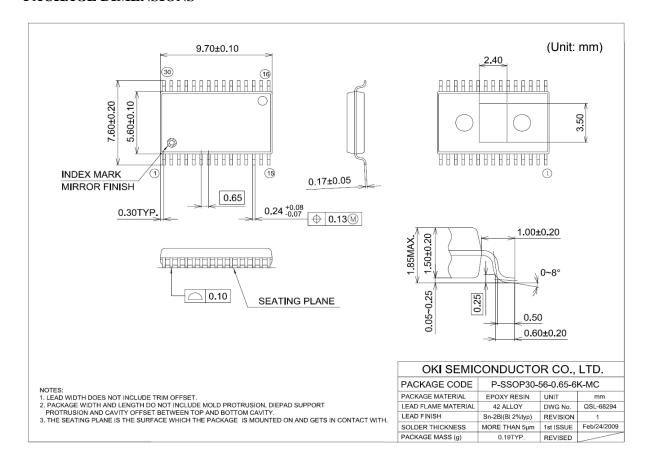

# • Shipment

- 30-pin SSOP

- High-speed side clock: Crystal/ceramic oscillation (4.096 MHz)

Flash Memory : ML610Q340-xxxMB (blank product: ML610Q340-NNNMB)

Mask Memory : ML610340-xxxMB

- High-speed side clock : external clock

Flash Memory : ML610Q340J-xxxMB (blank product: ML610Q340J-NNNMB)

Mask Memory : ML610340J-xxxMB

xxx: ROM code number

## • Guaranteed operating range

- Operating temperature: -40°C to +85°C

- Operating voltage:  $V_{DD} = 2.2$  to 5.5 V,  $SPV_{DD} = 2.3$  to 5.5 V (Be sure to apply the same voltage to all the power supplies.)

#### **BLOCK DIAGRAM**

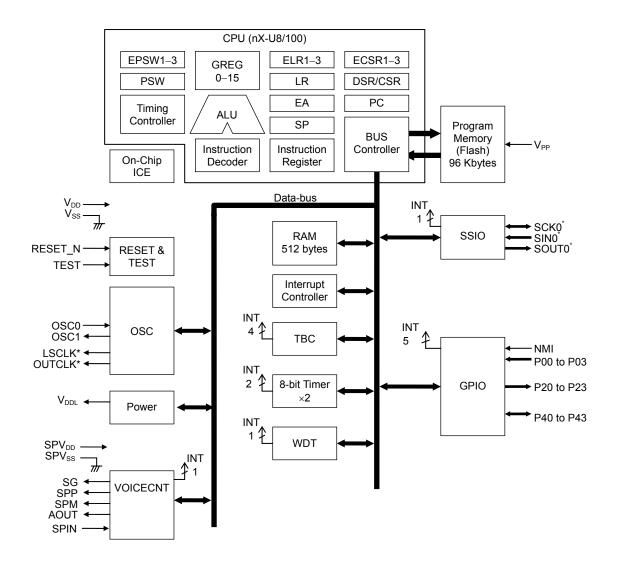

# ML610Q340

Figure 1 is a block diagram of the ML610Q340.

Symbols with an asterisk "\*" indicate that each of them is the secondary or tertiary function of the corresponding port.

Figure 1 Block Diagram of ML610Q340

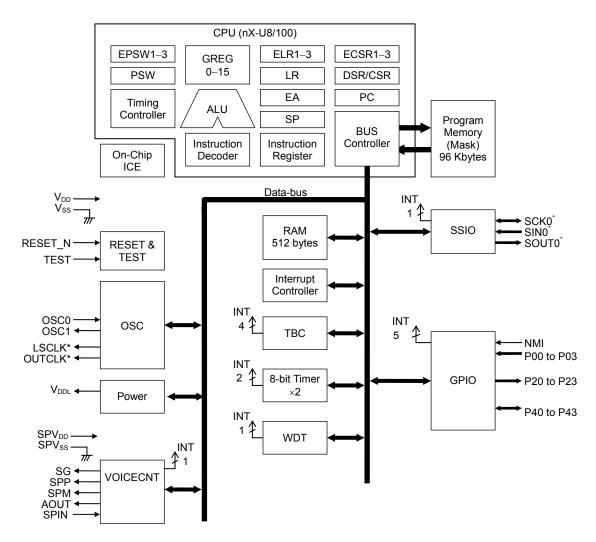

# ML610340

Figure 2 is a block diagram of the ML610340.

Symbols with an asterisk "\*" indicate that each of them is the secondary or tertiary function of the corresponding port.

Figure 2 Block Diagram of ML610340

# PIN CONFIGURATION

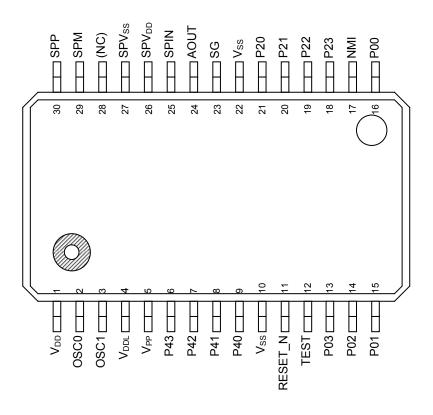

# ML610Q340 SSOP package product

NC: No Connection

Figure 3 Pin Configuration of ML610Q340 Package Product

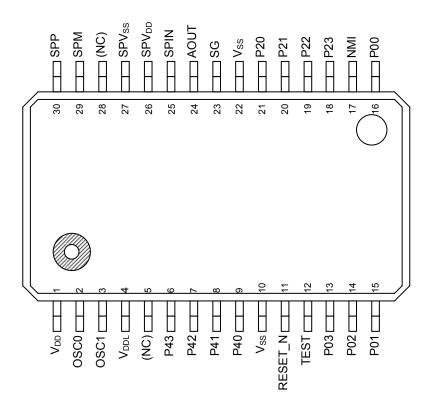

# ML610340 SSOP package product

NC: No Connection

Figure 4 Pin Configuration of ML610340 Package Product

# LIST OF PINS

| PAD   | Primary function    |     |                                                                | Secondary function |     |                         | Tertiary function |     |             |

|-------|---------------------|-----|----------------------------------------------------------------|--------------------|-----|-------------------------|-------------------|-----|-------------|

| No    | Pin name            | I/O | Description                                                    | Pin name           | I/O | Description             | Pin name          | I/O | Description |

| 10,22 | Vss                 | _   | Negative power supply pin                                      | _                  | _   | _                       | _                 | _   | _           |

| 1     | V <sub>DD</sub>     | _   | Positive power supply pin                                      | _                  | _   | _                       | _                 | _   | _           |

| 4     | $V_{DDL}$           | _   | Power supply for internal logic (internally generated)         | _                  | _   | _                       | _                 | _   | _           |

| 27    | SPV <sub>SS</sub>   | _   | Negative power supply pin for built-in speaker amplifier       | _                  | _   | _                       | _                 | _   | _           |

| 26    | SPV <sub>DD</sub>   | _   | Positive power supply<br>pin for built-in speaker<br>amplifier | _                  | _   | _                       | _                 | _   | _           |

| 5     | V <sub>PP</sub> (*) | _   | Power supply pin for flash memory                              | _                  | _   | _                       | _                 | _   | _           |

| 12    | TEST                | I/O | Input/output pin for testing                                   | _                  | _   | _                       | _                 | _   | _           |

| 11    | RESET_N             | ı   | Reset input pin                                                |                    |     |                         |                   |     |             |

| 2     | OSC0                | -   | Connection pin for high-speed clock oscillation                | _                  |     |                         | l                 |     |             |

| 3     | OSC1                | 0   | Connection pin for high-speed clock oscillation                | P11                | 1   | Input port              |                   |     |             |

| 24    | AOUT                | 0   | LINE output                                                    | _                  | _   | _                       | _                 | _   |             |

| 25    | SPIN                | I   | Analog input to the built-in speaker amplifier                 | _                  |     | _                       | -                 |     | _           |

| 23    | SG                  | 0   | Reference power supply pin of the built-in speaker amplifier   | _                  | l   | _                       |                   | l   |             |

| 30    | SPP                 | 0   | Positive output pin of the built-in speaker amplifier          | _                  |     |                         | _                 |     | _           |

| 29    | SPM                 | 0   | Negative output pin of the built-in speaker amplifier          | _                  | _   | _                       | _                 | _   | _           |

| 17    | NMI                 | 1   | Input port,<br>non-maskable<br>interrupt                       | _                  | _   | _                       | _                 | _   | _           |

| 16    | P00/EXI0            | 1   | Input port / External interrupt                                | _                  | _   | _                       | _                 | _   | _           |

| 15    | P01/EXI1            | I   | Input port / External interrupt                                | _                  | _   | _                       | _                 | _   | _           |

| 14    | P02/EXI2            | I   | Input port / External interrupt                                | _                  | _   | _                       | _                 | _   | _           |

| 13    | P03/EXI3            | I   | Input port / External interrupt                                | _                  | _   | _                       | _                 | _   | _           |

| 21    | P20/LED0            | 0   | Output port / LED drive                                        | LSCLK              | 0   | Low-speed clock output  |                   |     |             |

| 20    | P21/LED1            | 0   | Output port / LED drive                                        | OUTCLK             | 0   | high-speed clock output |                   |     |             |

| 19    | P22/LED2            | 0   | Output port / LED drive                                        | _                  |     |                         | _                 |     |             |

| 18    | P23/LED3            | 0   | Output port / LED drive                                        | _                  | _   |                         | _                 | _   |             |

| PAD | Primary function |     |                   | Sec      | function | Tertiary function |          |     |                                               |

|-----|------------------|-----|-------------------|----------|----------|-------------------|----------|-----|-----------------------------------------------|

| No  | Pin name         | I/O | Description       | Pin name | I/O      | Description       | Pin name | I/O | Description                                   |

| 9   | P40              | I/O | Input/output port | _        | _        | _                 | SIN0     | I   | SSIO0 data input                              |

| 8   | P41              | I/O | Input/output port | _        | _        | _                 | SCK0     | I/O | SSIO0<br>synchronous<br>clock<br>input/output |

| 7   | P42              | I/O | Input/output port | _        | _        | _                 | SOUT0    | 0   | SSIO0 data output                             |

| 6   | P43              | I/O | Input/output port | _        | _        |                   | _        |     | _                                             |

<sup>\*:</sup> Applies to the ML610Q340.

# PIN DESCRIPTION

|                     |          |                                                                                                             | Drimony                |          |

|---------------------|----------|-------------------------------------------------------------------------------------------------------------|------------------------|----------|

| Pin name            | I/O      | Description                                                                                                 | Primary/<br>Secondary/ | Logic    |

| 1 III Hairic        | 1,0      | Description                                                                                                 | Tertiary               | Logic    |

| Power supply        |          | L                                                                                                           | Tortiary               | I        |

| V <sub>SS</sub>     | Τ_       | Negative power supply pin                                                                                   | _                      | _        |

| V <sub>DD</sub>     | <b>—</b> | Positive power supply pin                                                                                   | _                      | _        |

| V <sub>DDL</sub>    | <b>—</b> | Positive power supply pin for internal logic (internally generated)                                         | _                      | _        |

| - BBE               |          | Capacitors $C_L$ (see measuring circuit 1) are connected between this pin and $V_{SS}$                      |                        |          |

| SPVss               | _        | Negative power supply pin for built-in speaker amplifier                                                    | _                      | _        |

| SPV <sub>DD</sub>   | _        | Positive power supply pin for built-in speaker amplifier                                                    | _                      | _        |

| V <sub>PP</sub> (*) | _        | Power supply pin for flash memory                                                                           | _                      | _        |

| Test                |          |                                                                                                             |                        | •        |

| TEST                | I/O      | Input/output pin for testing. Has a pull-down resistor built in.                                            | _                      | Positive |

| System              |          |                                                                                                             |                        | l .      |

| RESET_N             |          | Reset input pin. When this pin is set to a "L" level, the device is                                         |                        |          |

|                     |          | placed in system reset mode and the internal circuit is initialized.                                        |                        | Negative |

|                     |          | If after that this pin is set to a "H" level, program execution                                             | _                      | iveyauve |

|                     |          | starts. This pin has a pull-up resistor built in.                                                           |                        |          |

| OSC0                | I        | Pins for connecting a crystal unit for high speed clock.                                                    | _                      | _        |

| OSC1                | 0        | Connect a 4.096 MHz crystal unit (see Measuring Circuit 1) to                                               | _                      |          |

|                     |          | these pins. Also, connect capacitors ( $C_{DH}$ and $C_{GH}$ ) between these pins and $V_{SS}$ as required. |                        |          |

| LSCLK               | 0        | Low-speed clock output. This function is allocated to the                                                   | Secondary              |          |

| LOOLK               |          | secondary function of the P20 pin.                                                                          | Secondary              |          |

| OUTCLK              | 0        | High-speed clock output. This function is allocated to the                                                  | Secondary              | _        |

|                     |          | secondary function of the P21 pin.                                                                          | ,                      |          |

| General-purpos      | e Input  | t port                                                                                                      |                        |          |

| P00-P03             | I        | General-purpose input ports.                                                                                | Primary                | Positive |

| General-purpos      | e Outp   | ut port                                                                                                     |                        |          |

| P20-P23             | 0        | General-purpose output ports.                                                                               |                        |          |

|                     |          | Provided with a secondary function. Cannot be used as ports if                                              | Primary                | Positive |

|                     |          | their secondary function is used.                                                                           |                        |          |

| General-purpos      |          |                                                                                                             |                        | T        |

| P40-P43             | I/O      | General-purpose input/output ports.                                                                         |                        |          |

|                     |          | Provided with a secondary function. Cannot be used as ports if                                              | Primary                | Positive |

|                     |          | their secondary function is used.                                                                           |                        |          |

<sup>\*</sup>Applies to the ML610Q340.

|                   |         |                                                                                                                                                                                                                     | Primary/   |                       |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

| Pin name          | I/O     | Description                                                                                                                                                                                                         | Secondary/ | Logic                 |

|                   |         | 2 333                                                                                                                                                                                                               | Tertiary   |                       |

| Synchronous se    | rial (S | SIO)                                                                                                                                                                                                                |            | •                     |

| SIN0              | I       | Synchronous serial data input pin. Allocated to the tertiary function of the P40 pin.                                                                                                                               | Tertiary   | Positive              |

| SCK0              | I/O     | Synchronous serial clock input/output pin. Allocated to the tertiary function of the P41 pin.                                                                                                                       | Tertiary   | _                     |

| SOUT0             | 0       | Synchronous serial data output pin. Allocated to the tertiary function of the P42 pin.                                                                                                                              | Tertiary   | Positive              |

| External interrup | ot      |                                                                                                                                                                                                                     |            |                       |

| NMI               | I       | External non-maskable interrupt input pin. The interrupt occurs on both the rising and falling edges.                                                                                                               | Primary    | Positive/<br>Negative |

| EXI0-3            | I       | External maskable interrupt input pins. It is possible, for each bit, to specify whether the interrupt is enabled and select the interrupt edge by software. Allocated to the primary function of the P00–P03 pins. | Primary    | Positive/<br>Negative |

| LED drive         |         |                                                                                                                                                                                                                     |            |                       |

| LED0-3            | 0       | NMOS open drain pins to allow direct driving of LED. Allocated to the secondary function of the P20–P23 pins.                                                                                                       | Primary    | Positive/<br>Negative |

| Voice output fur  | nction  |                                                                                                                                                                                                                     |            |                       |

| AOUT              | 0       | LINE output pin. When you use built-in speaker amplifier, connect with the SPIN pin.                                                                                                                                | _          | _                     |

| SPIN              | I       | Analog input pin of the internal speaker amplifier.                                                                                                                                                                 | _          | _                     |

| SG                | 0       | Reference voltage output pin of the internal speaker amplifier.                                                                                                                                                     | _          | _                     |

| SPP               | 0       | Positive output pin of the internal speaker amplifier.                                                                                                                                                              |            | _                     |

| SPM               | 0       | Negative output pin of the internal speaker amplifier.                                                                                                                                                              | _          | _                     |

# **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

$(V_{SS} = SPV_{SS} = 0V)$

| Parameter              | Symbol            | Condition     | Rating                       | Unit |

|------------------------|-------------------|---------------|------------------------------|------|

| Power supply voltage 1 | $V_{DD}$          | Ta = 25°C     | -0.3 to +7.0                 | V    |

| Power supply voltage 2 | SPV <sub>DD</sub> | Ta = 25°C     | -0.3 to +7.0                 | V    |

| Power supply voltage 3 | $V_{DDL}$         | Ta = 25°C     | -0.3 to +3.6                 | V    |

| Power supply voltage 4 | $V_{PP}$          | Ta = 25°C     | -0.3 to +9.5                 | V    |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C     | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage         | $V_{OUT}$         | Ta = 25°C     | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current 1       | I <sub>OUT1</sub> | P4, Ta = 25°C | -12 to +11                   | mA   |

| Output current 2       | I <sub>OUT2</sub> | P2, Ta = 25°C | −12 to +20                   | mA   |

| Power dissipation      | PD                | Ta = 25°C     | 861                          | mW   |

| Storage temperature    | T <sub>STG</sub>  | _             | −55 to +150                  | °C   |

# **Recommended Operating Conditions**

$(V_{SS} = SPV_{SS} = 0V)$

|                                                        |                  | <b>-</b>  | _            |      |

|--------------------------------------------------------|------------------|-----------|--------------|------|

| Parameter                                              | Symbol           | Condition | Range        | Unit |

| Operating temperature                                  | T <sub>OP</sub>  | _         | −40 to +85   | °C   |

| Operating voltage                                      | $V_{DD}$         | _         | 2.2 to 5.5   | V    |

| Operating voltage                                      | $SPV_{DD}$       | _         | 2.3 to 5.5   | V    |

| Operating frequency (CPU)                              | f <sub>OP</sub>  | _         | 437k to 4.2M | Hz   |

| High-speed crystal/ceramic oscillation frequency       | f <sub>XTH</sub> | _         | 4.0M, 4.096M | Hz   |

| High-speed crystal oscillation                         | C <sub>DH</sub>  | _         | 15 to 32     |      |

| external capacitor                                     | C <sub>GH</sub>  | _         | 15 to 32     | pF   |

| Capacitor externally connected to V <sub>DDL</sub> pin | C <sub>L</sub>   | _         | 10±30%       | μF   |

| Capacitor externally connected to SG pin               | C <sub>SG</sub>  | _         | 0.1±30%      | μF   |

# **Flash Memory Operating Conditions**

$(V_{SS} = SPV_{SS} = 0V)$

|                       |                 |                     | (-00 -      | 1 100 11 |

|-----------------------|-----------------|---------------------|-------------|----------|

| Parameter             | Symbol          | Condition           | Range       | Unit     |

| Operating temperature | T <sub>OP</sub> | At write/erase      | 0 to +40    | °C       |

|                       | $V_{DD}$        | At write/erase      | 2.7 to 3.6  |          |

| Operating voltage     | $V_{DDL}$       | At write/erase (*1) | 2.5 to 2.75 | V        |

|                       | $V_{PP}$        | At write/erase (*1) | 7.7 to 8.3  |          |

| Maximum rewrite count | C <sub>EP</sub> | <u> </u>            | 80          | times    |

| Data retention period | $Y_{DR}$        | _                   | 10          | years    |

<sup>\*1:</sup> When writing data to, or erasing data from, flash ROM, it is necessary to apply a voltage within the range specified above to the  $V_{DDL}$  pin.

# DC Characteristics (1 of 5)

(V<sub>DD</sub> = SPV<sub>DD</sub> = 2.2 to 5.5V, V<sub>SS</sub> = SPV<sub>SS</sub> = 0V, Ta = -40 to  $+85^{\circ}$ C, unless otherwise specified)

|                                      |                   |           |      |      | -,   |      |                   |

|--------------------------------------|-------------------|-----------|------|------|------|------|-------------------|

| Parameter                            | Symbol            | Condition | Min. | Тур. | Max. | Unit | Measuring circuit |

| High-speed oscillation start time    | T <sub>XTH</sub>  | _         | _    | 2    | 20   | ms   |                   |

| Reset pulse width                    | P <sub>RST</sub>  | _         | 100  | _    | _    |      |                   |

| Reset noise rejection pulse width    | P <sub>NRST</sub> | _         | _    | _    | 0.4  | μS   | 1                 |

| Time from power-on reset to power-up | T <sub>POR</sub>  | _         | _    | _    | 10   | ms   |                   |

# DC Characteristics (2 of 5)

$(V_{DD} = SPV_{DD} = 2.3 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

|                                                                        |                 |                                                                                   | ıa-                    | <del>-10 10 100</del> | C, unicoo                 | Othici Wist | specified)        |

|------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|------------------------|-----------------------|---------------------------|-------------|-------------------|

| Parameter                                                              | Symbol          | Condition                                                                         | Min.                   | Тур.                  | Max.                      | Unit        | Measuring circuit |

| LINE amplifier output load resistance                                  | R <sub>LA</sub> | At 1/2V <sub>DD</sub> output                                                      | 10                     | _                     | _                         | kΩ          |                   |

| LINE amplifier output voltage range                                    | V <sub>AD</sub> | At output load                                                                    | V <sub>DD</sub> ×1/6   | _                     | V <sub>DD</sub> ×5/6      | V           |                   |

| SG output voltage                                                      | V <sub>SG</sub> | _                                                                                 | $0.95 \times V_{DD}/2$ | DV <sub>DD</sub> /2   | 1.05 × V <sub>DD</sub> /2 | V           |                   |

| SG output resistance                                                   | Rsg             | _                                                                                 | 57                     | 96                    | 135                       | kΩ          |                   |

| SPM, SPP output load resistance                                        | RLSP            | _                                                                                 | 8                      | _                     | _                         | Ω           |                   |

| Speaker amplifier output                                               | PSPO1           | $SPV_{DD} = 3.3V,$ $f = 1kHz,$ $RSPO = 8\Omega,$ $THD \ge 10\%$ $At SPIN Input$   | _                      | 0.5                   | _                         | W           | 1                 |

| power                                                                  | PSPO2           | $SPV_{DD} = 5.0V,$ $f = 1kHz,$ $RSPO = 8\Omega,$ $THD \ge 10\%$ $At SPIN Input$   | _                      | 1                     | _                         | W           |                   |

| Output offset voltage<br>between SPM and SPP<br>with no signal present | VOF             | SPV <sub>DD</sub> =3.0V,<br>SPIN – SPM gain<br>= +6dB<br>With a load of $8\Omega$ | -50                    | _                     | +50                       | mV          |                   |

# DC Characteristics (3 of 5) ML610Q340

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter          | Symbol | Condition                                                                  |                                            | Min. | Тур. | Max. | Unit | Measuring circuit |

|--------------------|--------|----------------------------------------------------------------------------|--------------------------------------------|------|------|------|------|-------------------|

|                    |        | CPU: In STOP state.                                                        | Ta ≤ +40°C                                 | _    | 0.5  | 2.0  |      | μΑ                |

| Supply current 1   | IDD1   | Low-speed/high-speed oscillation: stopped Ta ≤ +85°C                       | Ta ≤ +85°C                                 | I    | 0.5  | 8    | μА   |                   |

|                    |        | CPU: Running at                                                            | V <sub>DD</sub> =                          |      | 1.7  | 4    |      |                   |

| Crommby arranged 4 | IDD4   | 4.096MHz<br>Crystal/ceramic<br>oscillating mode *1                         | $SPV_{DD} = 3.0V$                          |      | 1.7  |      |      |                   |

| Supply current 4   |        |                                                                            | V <sub>DD</sub> =                          | _    | 2.2  | 4    |      |                   |

|                    |        |                                                                            | $SPV_{DD} = 5.0V$                          |      | 2.2  |      |      | 1                 |

|                    |        | CPU: Running at                                                            | V <sub>DD</sub> =                          |      | 2    | 10   | mA   |                   |

|                    |        | 4.096MHz                                                                   | SPV <sub>DD</sub> = 3.0V                   | _    | 3    | 12   |      |                   |

| Supply current 5   | IDD5   | Crystal/ceramic oscillating mode *1 During voice playback (no output load) | V <sub>DD</sub> = SPV <sub>DD</sub> = 5.0V |      | 8    | 12   |      |                   |

<sup>\*1:</sup> Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

# DC Characteristics ML610340

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter        | Symbol                                                                           | Condition                                 |                                            | Min. | Тур. | Max. | Unit | Measuring circuit |

|------------------|----------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|------|------|------|------|-------------------|

| Supply current 1 |                                                                                  | CPU: In STOP state.                       | Ta ≤ +40°C                                 | l    | 0.5  | 2.0  |      |                   |

|                  | IDD1                                                                             | Low-speed/high-speed oscillation: stopped | Ta ≤ +85°C                                 |      | 0.5  | 8    | μА   | l                 |

| Supply current 4 | IDD4                                                                             | CPU: Running at 4.096MHz                  | $V_{DD} = SPV_{DD} = 3.0V$                 | _    | 0.75 | 4    |      |                   |

|                  |                                                                                  | Crystal/ceramic oscillating mode *1       | $V_{DD} = SPV_{DD} = 5.0V$                 | _    | 1.5  | 4    |      | 1                 |

| Supply current 5 |                                                                                  | CPU: Running at 4.096MHz                  | $V_{DD} = SPV_{DD} = 3.0V$                 | _    | 3    | 12   | mA   |                   |

|                  | IDD5  Crystal/ceramic oscillating mode *1 During voice playback (no output load) |                                           | V <sub>DD</sub> = SPV <sub>DD</sub> = 5.0V | _    | 8    | 12   |      |                   |

<sup>\*1:</sup> Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

## PACKAGE DIMENSIONS

#### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. OKI SEMICONDUCTOR assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by OKI SEMICONDUCTOR authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2008 OKI SEMICONDUCTOR CO., LTD.