#### **DESCRIPTION**

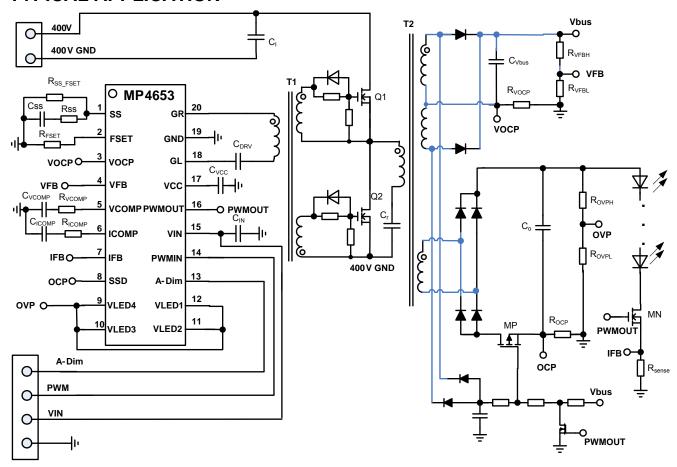

The MP465 3 is a CC/CV mode L LC TV LED driver for LED backlight ting, especially for larg e size TV LE D backlight ing. Powered by 9V to 30V input supplies, the MP4653 outputs two 180 degree phase shifted driving signals for the external power stages. Its enhanced 9V gate driver provides adequa te driving capability and can direct ly drive the external MOSF ETs through an external gate driving transformer.

The MP46 53 integrat es a constant current control loop for the LED current regulation and also a const ant voltage control loop for the DC bus voltage, which is used to generate system power supplies like 12 V/5V with other DC/DC converters. The CC/CV control loo p programs the operating frequency of the LLC power stage and thus regulates the LED current and also the bus voltage.

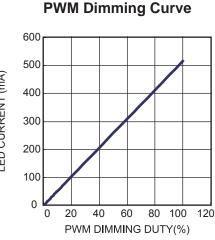

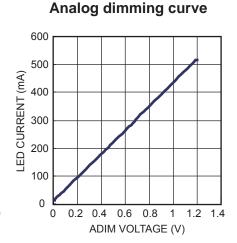

The MP4653 incorporates both analog dimming and PWM dimming to the LED current. A driving sign all is output to directly drive the dimming MOSFET, which helps to achieve fast and high contrast ratio PWM dimming.

The PWM dimming signal is also u sed for the CC/CV mode control. At PWM on interval, the CC mode is effect ive and the LE D current is regulated; at PWM off i nterval, the CV mode is effective and the DC b us voltage is regulated. The gate d riving signal and thus t he energy through the power stage are continu ous at both the PWM on interval a nd the PWM off interval. This helps to eliminate the system audible noise at PWM dimming.

The MP46 53 features sufficient and smart protection to increa se system reliability. It protects the fault condition at both the DC bus stage and the LED driver stage.

The protection for the DC bus stage include s the over voltage prot ection and over current protection (short protection).

The protection for the LED driver stage includes the open LED protection, short LED protection, over LED current protection and a ny point of LED string short to ground protection.

Thermal protection is integrated in MP4653. The MP4653 is available in SOIC20 package.

#### **FEATURES**

- Secondary Side "Real LIPS" LLC Controller

- CC/CV Frequency Control Loop

- Audible Noise Elimination

- Continuous driving signal at PWM dimming and LED fault condition

- 9V to 30V Input Voltage Range

- Analog and PWM Dimming

- Input Under Voltage Lockout

- DC Bus Output Over Voltage Protection

- DC Bus Short Protection

- System Auto-recovery and Hiccup Timer

- LED Open, Short Protection

- LED Output Over Voltage, Over LED Current Protection

- Any Point of LED String Short to GND Protection

- Available in SOIC 20 Package

#### **APPLICATIONS**

- LCD TVs and Monitors

- Desktop LCD Flat Panel Displays

- Flat Panel Video Displays

- Street Lighting

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

### **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP4653GY     | SOIC20  | MP4653      |

<sup>\*</sup> For Tape & Reel, add suffix -Z (eg. MP4653GY-Z);

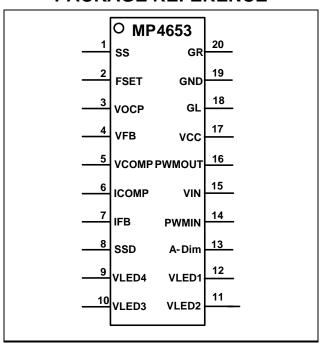

### **PACKAGE REFERENCE**

| ABSOLUTE MAXIMUM               | RATINGS "                               |

|--------------------------------|-----------------------------------------|

| Supply Voltage V <sub>in</sub> | 0.3V to +38V                            |

| GL,GR,VCC PWMOUT               | -0.5V to 10.7V                          |

| SSD, VOCP                      | 6.5V to + 4V                            |

| Other pins                     | 0.5V to +7V                             |

| Junction Temperature           | 150°C                                   |

| Continuous Power Dissipation   | (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                | 1.7 W                                   |

| Storage Temperature            | -65°C to +150°C                         |

| Operating frequency            | 300kHz                                  |

##

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| SOIC20                 | . 72                    | . 30                    | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause ex cessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

### **ELECTRICAL CHARACTERISTICS**

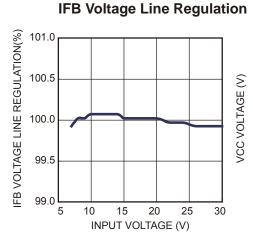

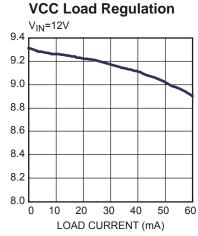

$V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                                  | Symbol                        | Condition                                                                                                                                                              | Min   | Тур              | Max   | Units |

|--------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|-------|

| Gate driver GL, GR                         |                               |                                                                                                                                                                        |       |                  |       |       |

| Gate Pull-Down                             | $R_{GD}$                      | Igate = 20mA                                                                                                                                                           |       | 2                |       | Ω     |

| Gate Pull-Up                               | $R_{GU}$                      | Igate = 20mA                                                                                                                                                           |       | 7.5              |       | Ω     |

| Output Source Current                      | I <sub>SOURCE</sub>           | With 1nF load                                                                                                                                                          |       | 1 <sup>[5]</sup> |       | Α     |

| Output Sink Current                        | I <sub>SINK</sub>             | With 1nF load                                                                                                                                                          |       | 2 <sup>[5]</sup> |       | Α     |

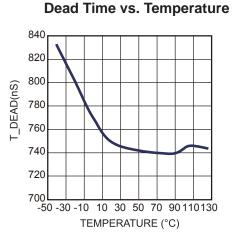

| Dead time                                  | t <sub>dead</sub>             |                                                                                                                                                                        | 600   | 750              | 900   | ns    |

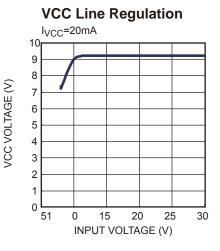

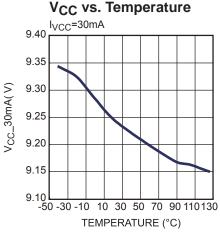

| Gate Driver Supply Voltage (VCC            | )                             |                                                                                                                                                                        |       |                  |       |       |

| Voltage V                                  |                               | I <sub>VCC</sub> =0mA                                                                                                                                                  | 9     | 9.4              | 9.8   | V     |

| Voltage V                                  | VCC                           | I <sub>VCC</sub> =30mA 8.8                                                                                                                                             |       | 9.3              |       | V     |

| Current I                                  | VCC                           |                                                                                                                                                                        |       | 20               | 50    | mA    |

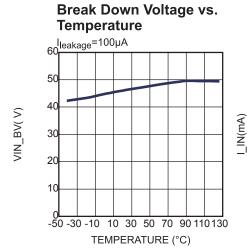

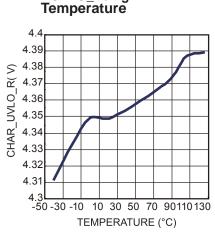

| Vin UVLO threshold                         | V <sub>TH_UVLO_VIN</sub>      | VCC rising                                                                                                                                                             | 4.2   | 4.35             | 4.5   | V     |

| VCC UVLO Hysteresis                        | V <sub>TH_VIN_HYST</sub>      |                                                                                                                                                                        |       | 240              |       | mV    |

| <b>Brightness Dimming Control Rar</b>      | ige                           |                                                                                                                                                                        |       |                  |       |       |

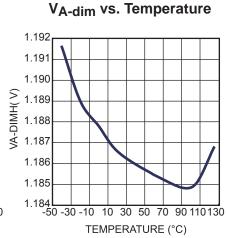

| Analog Dimming Full Scale                  | V <sub>A-dim</sub> Anal       | og dimming                                                                                                                                                             | 1.13  | 1.18             | 1.23  | V     |

| PWM Logic Input Threshold                  | $V_{TH-PWM}$                  | PWM dimming                                                                                                                                                            | 1.6   | 1.9              | 2.2   | V     |

| PWM Logic Input Hysteresis                 | $V_{TH	ext{-}PWM	ext{-}Hyst}$ | PWM dimming                                                                                                                                                            |       | 0.5              |       | V     |

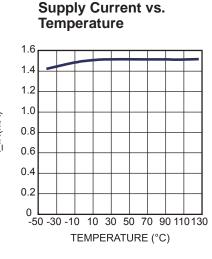

| Supply Current                             |                               |                                                                                                                                                                        |       |                  |       |       |

| Supply Current                             | I <sub>IN</sub>               | No driver output                                                                                                                                                       |       | 1.6              | 2.5   | mA    |

| Operating Frequency                        |                               |                                                                                                                                                                        |       |                  |       |       |

| Minimum Frequency Set Voltage              | $V_{FSET}$                    |                                                                                                                                                                        | 0.95  | 1                | 1.05  | V     |

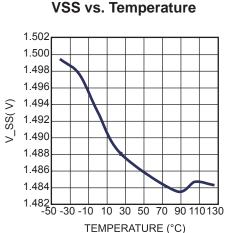

| SS pin voltage                             | Vss                           | At normal operation                                                                                                                                                    | 1.45  | 1.49             | 1.53  | V     |

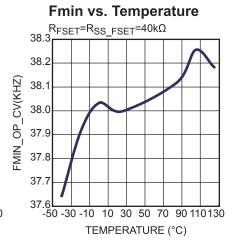

| Minimum operating frequency                | F <sub>min_op</sub>           | $\begin{array}{l} \text{RFSET=R}_{\text{SS\_FSET}}\text{=}40\text{k}\Omega,\\ \text{IFB=0.1V(ICOMP=2.2V),}\\ \text{PWMIN=high} \end{array}$                            | 35.6  | 38.6             | 41.6  | kHz   |

| Maximum Operating Frequency                | F <sub>max_op</sub>           | $\begin{array}{c} \text{RFSET=R}_{\text{SS\_FSET}}\text{=}40\text{k}\Omega,,\\ \text{IFB=0.21V}(\bar{\text{ICOMP}}\text{=}1\text{V}),\\ \text{PWMIN=high} \end{array}$ | 2.2   | 2.5              | 2.8   | Fmin  |

| Output PWM Dimming Signal for              | LED (PWMOU                    | Γ)                                                                                                                                                                     |       |                  |       |       |

| Logic High Voltage                         | $V_{\text{H-PWMOUT}}$         | Normal Operation                                                                                                                                                       | 9V    | 9.4              | 9.8   | V     |

| Logic Low Voltage                          | $V_{L\text{-PWMOUT}}$         | At Fault Condition, or PWMIN=0                                                                                                                                         |       |                  | 0.3   | V     |

| Output PWM Source Current                  | I <sub>SOURCE_PWMOUT</sub>    | 100pF on PWMOUT pin                                                                                                                                                    |       | 5                |       | mA    |

| Output PWM Sink Current                    | I <sub>SINK_PWMOUT</sub>      | 100pF on PWMOUT pin                                                                                                                                                    |       | 100              |       | mA    |

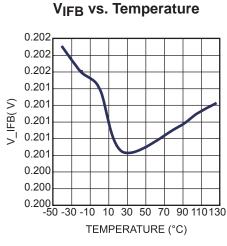

| LED Current Feedback (IFB)                 |                               |                                                                                                                                                                        |       |                  |       |       |

| Magnitude  V                               | IFB                           |                                                                                                                                                                        | 0.192 | 0.2              | 0.208 | V     |

| LED Sho rt Thresh old for Immediate action | V <sub>IFBS</sub>             |                                                                                                                                                                        | 540   | 600              | 660   | mV    |

| LED short detection blanking time          | $T_{blank}$                   |                                                                                                                                                                        | 100   | 140              | 180   | ns    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                                   | Symbol                               | Condition                         | Min                 | Тур                | Max                | Units |

|---------------------------------------------|--------------------------------------|-----------------------------------|---------------------|--------------------|--------------------|-------|

| LED sho rt threshold for slow action        | $V_{IFBSC}$                          |                                   | 270                 | 300                | 330                | mV    |

| Delay time for slow action                  | T <sub>delay_IFB</sub>               | 300mV <v<sub>IFB&lt;600mV</v<sub> | 100                 | 200                | 350                | μs    |

| Internal Current Loop Compensa              | tion Transcond                       | uctance Opamp (ICOMP)             |                     |                    |                    |       |

| Gain Bandwidth product                      | GB_I                                 | 75pF on ICOMP                     |                     | 1.0 <sup>[6]</sup> |                    | MHz   |

| Open Loop DC Gain                           | $A_{V_{-}I}$                         | ICOMP open                        | 60 <sup>[6]</sup>   |                    |                    | dB    |

| Input Common-mode range                     | $V_{CM\_I}$                          |                                   | -0.3 <sup>[6]</sup> |                    | 4 <sup>[6]</sup>   | ٧     |

| Transconductance Gm_I                       |                                      |                                   |                     | 830                |                    | μA/V  |

| Saturated output current                    | I <sub>sat_I</sub>                   |                                   | 35                  | 50                 | 65                 | μA    |

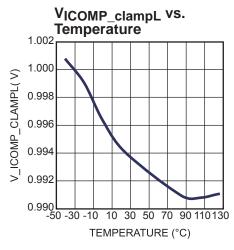

| Low level clamp voltage                     | VICOMP_L                             | Normal operation                  | 0.95                | 1                  | 1.05               | V     |

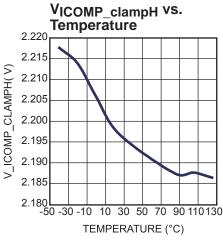

| High level clamp votlage                    | VICOMP_H                             | Normal operation                  | 2.15                | 2.2                | 2.25               | V     |

| DC Bus Voltage Feedback (VFB)               |                                      |                                   |                     |                    |                    |       |

| Sampling Delay Time                         | T <sub>dealy_sample</sub> P\         | VM falling edge                   |                     |                    | 100 <sup>[6]</sup> | ns    |

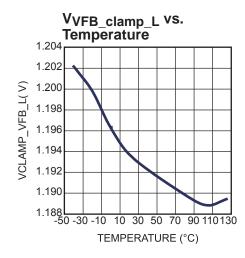

| Minimum clamp voltage                       | $V_{min\_clamp\_VFB}$                |                                   | 1.1                 | 1.2                | 1.3                | V     |

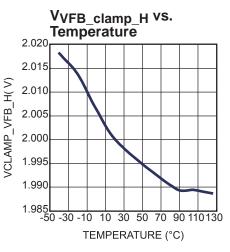

| Maximum clamp voltage                       | $V_{max\_clamp\_VFB}$                |                                   | 1.9                 | 2                  | 2.1                | V     |

| Internal Voltage Loop Comper                | nsation Transo                       | conductance Opamp (VC             | OMP)                |                    |                    |       |

| Gain Bandwidth product                      | GB_V                                 | 75pF on VCOMP                     |                     | 1.0 <sup>[6]</sup> |                    | MHz   |

| Open Loop DC Gain                           | $A_{V\_V}$                           | VCOMP open                        | 60 <sup>[6]</sup>   |                    |                    | dB    |

| Low level clamp voltage                     | VVCOMP_L                             | Normal operation                  | 0.95                | 1                  | 1.05               | V     |

| High level clamp votlage                    | VVCOMP_H                             | Normal operation                  | 2.15                | 2.2                | 2.25               | V     |

| Transconductance                            | Gm_V                                 |                                   |                     | 160                |                    | μΑ/V  |

| Saturated output current                    | I <sub>sat_V</sub>                   |                                   | 35                  | 50                 | 65                 | μΑ    |

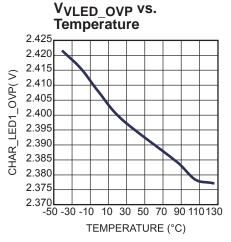

| Over LED Voltage Protection (VLED1~VLED4)   |                                      |                                   |                     |                    |                    |       |

| Over LED Voltage Protectio n<br>Threshold   | $V_{TH(OVP\_LED)}$                   |                                   | 2.25                | 2.40               | 2.55               | ٧     |

| Over LED voltage delay time                 | T <sub>delay_VLED</sub>              |                                   | 1.7                 | 2.3                | 2.9                | μs    |

| Gain of differential voltage                |                                      |                                   | 14.7                | 16.3               | 17.9               |       |

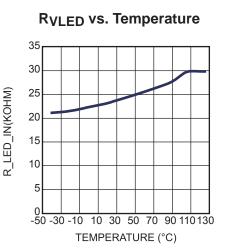

| Internal resistance                         | $R_{VLED}$                           |                                   | 19                  | 23                 | 27                 | kΩ    |

| Hiccup mode fault delay timer(ICOMP, VCOMP) |                                      |                                   |                     |                    |                    |       |

| ICOMP Valley Threshold                      | $V_{th\_low(ICOMP)}$                 |                                   | 0.35                | 0.45               | 0.55               | V     |

| ICOMP Peak Threshold                        | $V_{\text{th\_peak(ICOMP)}}$         |                                   | 2.7                 | 3                  | 3.3                | V     |

| ICOMP charging current at hiccup mode       | I <sub>charge_fault(ICOMP)</sub>     |                                   | 1.6                 | 2                  | 2.4                | μΑ    |

| ICOMP di scharging current at hiccup mode   | I <sub>discharge_fault(ICOM</sub> P) | 1.6                               |                     | 2                  | 2.4                | μΑ    |

| VCOMP Valley Threshold                      | $V_{\text{th\_low}(\text{VCOMP})}$   |                                   | 0.35                | 0.45               | 0.55               | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                                | Symbol                           | Condition                                      | Min  | Тур  | Max  | Units                |

|------------------------------------------|----------------------------------|------------------------------------------------|------|------|------|----------------------|

| VCOMP Peak Threshold                     | V <sub>th_peak(VCOMP)</sub>      | 2.7                                            |      | 3    | 3.3  | V                    |

| VCOMP charging current at hiccup mode    | I <sub>charge_fault(VCOMP)</sub> | 1.6                                            |      | 2    | 2.4  | μΑ                   |

| VCOMP discharging current at hiccup mode | I <sub>discharge_fault(VCO</sub> | 1.6                                            |      | 2    | 2.4  | μA                   |

| Burst mode (Pulse Skipping) three        | eshold (VCOMP                    | , ICOMP,VFB, IFB)                              |      |      |      |                      |

| VCOMP threshold for burst mode           | V <sub>TH_burst_VCOMP</sub>      | VFB>1.1V <sub>SH</sub> 1.05                    |      | 1.1  | 1.15 | V                    |

| VCOMP hystere sis for burst mode         |                                  |                                                | 70   | 90   | 110  | mV                   |

| VFB threshold for burst mode             | $V_{TH\_burst\_VFB}$             |                                                | 1    | 1.1  | 1.2  | $V_{SH}$             |

| VFB reset threshold for burs t mode      | V <sub>TH_reset_burst_VFB</sub>  |                                                |      | 1    |      | V <sub>SH</sub>      |

| ICOMP threshold for burst mode           | V <sub>TH_burst_ICOMP</sub>      | V <sub>IFB</sub> >1.1V <sub>IFB_REF</sub> 1.05 |      | 1.1  | 1.15 | V                    |

| ICOMP hysteresis for burst mode          |                                  |                                                | 70   | 90   | 110  | mV                   |

| IFB threshold for burst mode             | $V_{TH\_burst\_IFB}$             |                                                | 1    | 1.1  | 1.2  | $V_{IFB\_REF}$       |

| IFB reset threshold for burst mode       | V <sub>TH_reset_burst_IFB</sub>  |                                                |      | 1    |      | V <sub>IFB_REF</sub> |

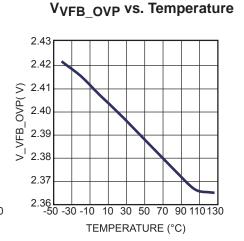

| Over Bus Voltage Protection (VFB)        |                                  |                                                |      |      |      |                      |

| Over bu s Voltage Pro tection Threshold  | $V_{TH(OVP\_VFB)}$               |                                                | 2.25 | 2.40 | 2.55 | V                    |

| Delay Time                               |                                  | VFB>2.4V                                       | 1.7  | 2.3  | 2.9  | μs                   |

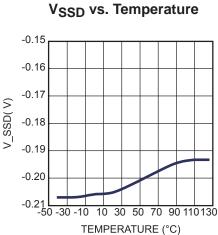

| Short LED stage Detection (SSD)          | )                                |                                                |      |      |      |                      |

| SSD Threshold                            | $V_{TH\_SSD}$                    |                                                | -225 | -200 | -175 | mV                   |

| SSD Detection Delay Time                 | T <sub>D_SSD</sub> SSD           | <-200 mV                                       | 1.8  | 2.4  | 3    | μs                   |

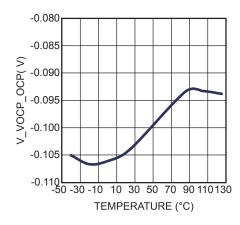

| Short Bus Stage Detection (OCP           | )                                |                                                |      |      |      |                      |

| OCP detection threshold                  | V <sub>TH_OCP</sub>              |                                                | -120 | -100 | -80  | mV                   |

| OCP delay time                           | T <sub>D_OCP</sub> OCF           | <-100mV                                        | 1.8  | 2.4  | 3    | μs                   |

<sup>\*:</sup> For design reference, not test parameter.

<sup>[5]:</sup> for bench evaluation only

<sup>[6]:</sup> for design only, not to be test

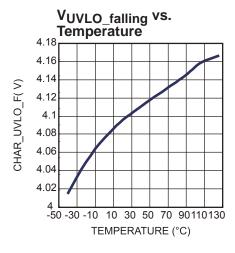

#### TYPICAL CHARACTERISTICS

V<sub>UVLO</sub> rising vs.

## **TYPICAL CHARACTERISTICS (continued)**

# **TYPICAL CHARACTERISTICS (continued)**

#### **VVOCP OCP vs. Temperature**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

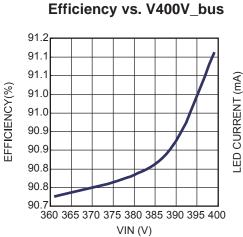

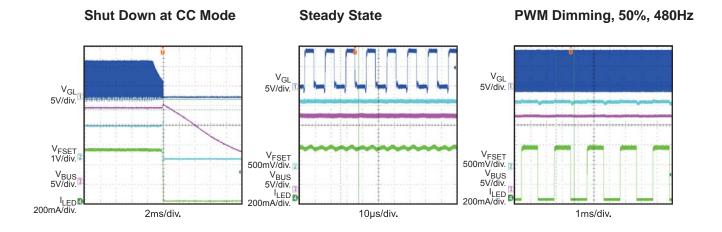

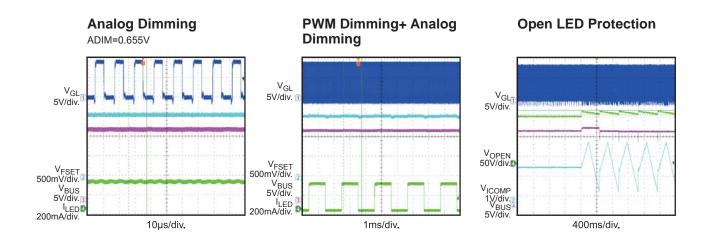

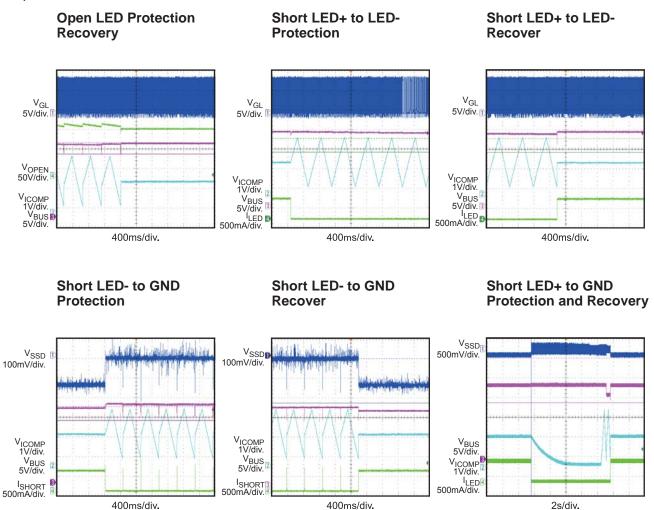

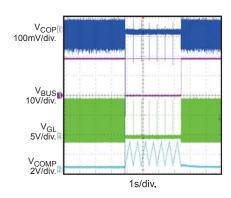

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN}$  = 12V, 400V\_bus=380V,  $V_{LED}$  = 120V, ILED=130mA\*4 strings, DC/DC output=12V/1.5A,  $T_A$  = 25°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN}$  = 12V, 400V\_bus=380V,  $V_{LED}$  = 120V, ILED=130mA\*4 strings, DC/DC output=12V/1.5A,  $T_A$  = 25°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN}$  = 12V, 400V\_bus=380V,  $V_{LED}$  = 120V, ILED=130mA\*4 strings, DC/DC output=12V/1.5A,  $T_A$  = 25°C, unless otherwise noted.

Short DC bus to GND Protection and Recover

## **PIN FUNCTIONS**

| Pin# | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 SS |       | Soft Start. This pin functions soft start and also sets the operating frequency together with FSET pin. Connect a resistor ( $R_{SS\_FSET}$ ) in parallel with a resistor (Rss) and a capacitor (Css) in series to this pin. The sourcing current of this pin together with the sourcing current of FSET pin determines the operating frequency. The resistor $R_{SS\_FSET}$ together with the resistor on FSET pin sets the operating frequency; the resistor Rss and the capacitor Css functions the soft start. The normal voltage on this pin is 1.49 V and is pulled low to 0V at bus voltage stage fault condition. The Rss and Css network sets the start up operating frequency and the soft start time. |

| 2 FS | ET    | Frequency Set. Conne ct a resi stor from the is pine to GND. The eoperating frequency is determined by the sourcing current through this pin and SS pin. The voltage of FSET pine is programmed by the current control loop and the voltage constrol loop, and so do esit he operating frequency.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3 VC | CP    | Over current protection of bus stage. This pin senses the secondary current of the bus stage, when the VOCP voltage is lower than -100mV, IC triggers bus stage protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 VF | В     | Bus voltage feedba ck. This pin fee ds b ack the bus volta ge for regul ation. MP465 3 automatically samples the VFB voltage at PWM ON interval and u ses it as the reference voltage of the bus voltage control loop at PWM OFF interval.  The voltage on VFB pin is also used for over voltage protection of bus voltage stage. When the voltage on VFB pin exceeds 2.4V, the over voltage protection of bus voltage stage is triggered.                                                                                                                                                                                                                                                                       |

| 5    | VCOMP | Feedback Compensation Node of voltage control loop. Connect a compensation capacitor or a R-C network from this pin to GND.  VCOMP pin is also used as the hiccup timer for the fault protection of the Bus voltage stage. When fault condition occurs in the bus voltage stage, the VCOMP is disconnected from the internal voltage loop and the hiccup timer for the voltage bus voltage stage starts. An internal current source charges VCOMP until 3V and then discharges it to 0.45V.                                                                                                                                                                                                                      |

| 6    | ICOMP | Feedback Compensation Node of current control loop. Connect a compensation capacitor or a R-C network from this pin to GND. ICOMP pin is also used as the hiccup ti mer for the LED stage prote ction. When fault condition of the LED stage occurs, the ICOMP pin is disconnected from the internal amplifier and LED stage hiccup timer starts. An internal current source charges ICOMP until 3V and then discharges it to 0.45V.                                                                                                                                                                                                                                                                             |

| 7    | IFB   | LED Current Feedback Input. This pin feeds back the LED current through a sensing resistor. The internal error amplifier sinks a current from the ICOMP pin proportional to the absolute value of the voltage at this pin. The average voltage at this pin is regulated to the reference voltage (controlled by the A-dim voltage, 0.2V when A-dim is high). The voltage on this pin is also used for over LED current detection. When the voltage on this pin gets higher than 0.3V for 200µs or when the voltage gets higher than 0.6V, the IC triggers the LED stage protection.                                                                                                                              |

| 8    | SSD   | Short string protection. This pin feeds back t he se condary side current of the LED drive r stage. When the voltage on this pin is less t han -200mV, IC triggers the LED driver stage protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9    | VLED4 | Voltage feedback of LED string4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10   | VLED3 | Voltage feedback of LED string3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11   | VLED2 | Voltage feedback of LED string2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **PIN FUNCTIONS (continued)**

|       |        | ,                                                                                                                                                                                                                                                                                                                                     |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin#  | Name   | Description                                                                                                                                                                                                                                                                                                                           |

| 12 VI | LED1   | Voltage feed back of LED string1. VLED1, VL ED2, VLED3 and VLED4 corporate for the protection of the LED driv er stage. The maximum voltage of these pins and the voltage difference among these pins are detected for LED stage protection. If the number of LED strings is less than 4, connect the left pins together with others. |

| 13    | A-Dim  | Analog dimming input. $0\sim1.18V$ sets the LED current from 0 to 100%. If not used pull it high to VCC through a $100k\Omega$ resistor.                                                                                                                                                                                              |

| 14    | PWMIN  | PWM Dimming control Input. Apply a 100Hz to 2kHz PWM signal to this pin for PWM dimming                                                                                                                                                                                                                                               |

| 15    | VIN    | Supply Input. Bypass this pin with a ceramic capacitor larger than 0.1µF.                                                                                                                                                                                                                                                             |

| 16    | PWMOUT | Output of the driving signal for the dimming MOSFET.                                                                                                                                                                                                                                                                                  |

| 17 V  | cc     | Power Suppl y for the gat $$ e drive r an d intern al ci rcuit. Bypass t $$ his pi n with $$ a ce ramic capacitor larger than $1\mu F$ .                                                                                                                                                                                              |

| 18    | GL     | Driving signal output, 180 degree phase shifted of GR                                                                                                                                                                                                                                                                                 |

| 19    | GND    | Ground Reference.                                                                                                                                                                                                                                                                                                                     |

| 20    | GR     | Driving signal output, 180 degree phase shifted of GL                                                                                                                                                                                                                                                                                 |

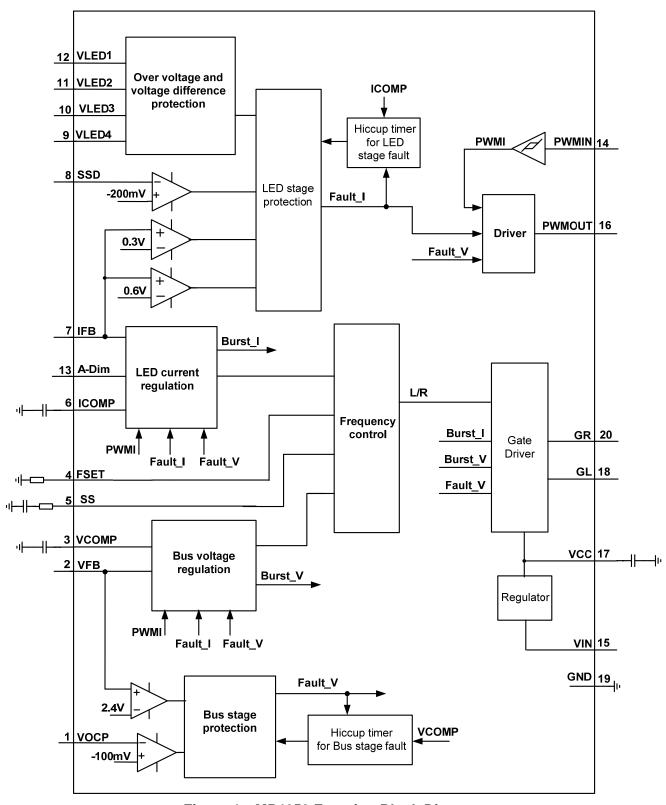

### **FUNCTION BLOCK DIAGRAM**

Figure 1—MP4653 Function Block Diagram

#### **OPERATION**

The MP465 3 is a CC/CV mode L LC TV LED driver, espe cially desig ned for the real LIPS structure for the large size TV LED backlighting. Powered by 9V to 3 0V input supplies, the MP4653 outputs two 180 degree phase shifte d driving signals for the external power stages. Its enhanced 9V gate dr iver provides adequate driving cap ability and can direct ly drive the external MOSFETs through an e xternal gate driving transformer.

The MP4653 employs frequency control for the LLC power stage. Both the LED current and the bus voltage are controlled. Figu re 1 shows the block diagram of MP4653.

#### **Internal Regulator**

The MP46 53 include s an inte rnal linear regulator VCC. It is the supply voltage for the gate driver and also for the internal circuit. The MP4653 fea tures Under Voltage Lockout. The chip is d isabled until V CC exceed s the UVLO threshold.

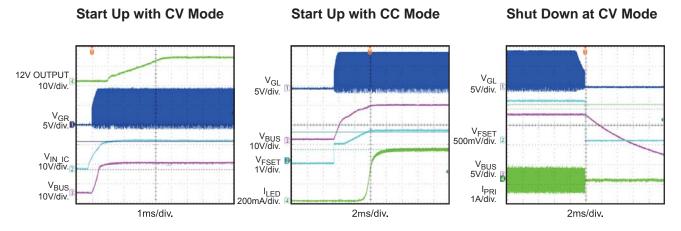

#### **System Startup**

When the MP4653 is powered up, the VCC i s charged up, and when it passe s the UVLO threshold, I C starts up. It resets the voltage control loo p, the cur rent control loop and discharges the soft start capacitor. The MP4653 enjoys a soft start up.

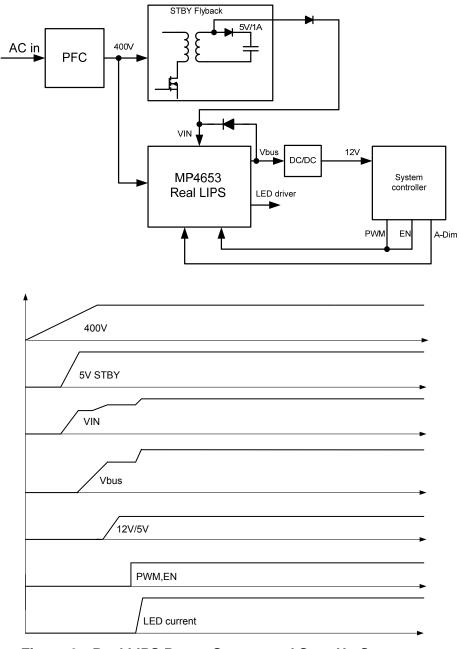

The MP4653 gets a 4.35V in put UVLO threshold, and it can start up directly from the system 5V standby power supply. Please refer to figure 2.

The PWM d imming signal controls the start up of the LED driver stage. The system operates in constant voltage mode and the DC bus voltage is controlled before PWM signal applied.

#### **CC/CV Mode Operation**

The MP46 53 integrat es a const ant voltage control loop (CV) and a constant current control loop (CC). Both the LED current of the LED stage and t he bus volt age of the bus voltage stage are controlled. The PWM dimming signal is used to distinguish these two modes. At PWM on interval, the current con trol loop is effective (CC mode) and the LED current is

regulated. At PWM off interval, the voltage control loop is effective and the DC bus voltage is controlled (CV mode).

For the current control loop for the LED current regulation, the LED current is fed back to IFB pin. The int ernal error amplifier regulates the average val ue of IFB signal to the internal 200mV ref erence voltage. Its output is connected to the external current-loop compensation network on ICOMP pin through an inner switch S1. At PWM on interval, S1 is on, and the output of the error amplifier is connected to the external compensation network on ICOMP pin. The LE D current is regulated by this control loop. At PWM off interval, S1 is turned off, and the compensation network on ICOMP is disconnect ed from the error amplifier and holds its value until next PWM on interval. The output o amplifier is pulled low at PWM off interval.

MP4653 int egrates burst mode for the LED current regulation. Whe n IFB volta ge is higher than 1.1 times of its ref erence voltage and the ICOMP voltage is sufficiently low (which means a highest o perating fre quency), the IC skips some switching cycles until I FB voltage decreases sufficiently.

For the voltage control loop for the bus voltage regulation, the bus voltage is fed b ack on VFB pin. MP4653 automatically samples the VFB voltage at P WM on interval and uses it as the reference f or the volt age control loop. The internal volt age-loop er ror amplifie r regulates the average value of the VFB voltage to this reference voltage at PWM off interval. Its output is con nected to the external voltage-loop compensation network on VCOMP pin through an inner switch S2. At PWM off interval, S2 is on, and the output of the voltage-loop error amplifier is connect ed to th e external compensation network on VCOMP pin. The bus voltage is regulated by this contr ol loop. At PWM on in terval, S2 i s turned off, and the compensation network on VCOMP i disconnected from the error amplifier and holds its value until next PWM off in terval. The output

of the voltage-loop erro r amplifier is pulled low at PWM on interval.

MP4653 also integrat es burst mode for the voltage regulation. When VFB voltage is higher than 1.1 times of the reference voltage and the VCOMP voltage is sufficiently low (which means a highest opera ting frequency), the IC skips some switching cycles until VFB voltage decreases sufficiently.

The operating frequency is controlled by the larger one of the outputs of the current-loop error amplifier and t he voltage-loop error amplifier. A high compensation ou tput voltage gets a low operating frequency.

#### **Dimming Control**

The MP465 3 provides two dimming methods: PWM Di mming Mode and Analog Dimmin g Mode. Applying a digit al PWM signal on the PWMIN pin allows the PWM dimming. The brightness of the LED string is pro portional to the duty cycle of the external PW M signal. A driving signal on PW MOUT pin is output to directly drive the dimming MOSFET, which helps to achieve fast and high contrast ratio PWM dimming.

MP4653 achieves 500: 1 PWM dimming ratio (0.2% minimum PW M dimming duty) at 200 Hz PWM dimming frequency. The PWM dimmin g ratio may decrease with a higher PWM dimming frequency.

A DC analog signal fro m 0V to 1.18V on A-Dim pin dims the LED current amplitude from 0 to 100%.

For PWM a nd analog dimming control, apply the PWM d imming signal on PWMIN pin and apply the analog dimming signal on A-dim pin.

#### **Bus Voltage Stage Protection**

The MP4653 features rich and sma rt protection to increase system reliability. It p rotects the fault condition at both the DC bus voltage stage and the LED driver stage.

The protection for the DC bus voltage stag e includes the over volta ge protection and over current protection (short protection).

The VFB pin senses the bus stage voltage for voltage regulation and also for over voltage

protection. When the VFB pin voltage gets higher than 2.4V for 2 us, IC triggers the Bus Voltage Stage Protection.

The secon dary side current of bus voltage stage is sensed on VOCP pin. When VOCP voltage gets lower than -100mV, IC triggers the Bus Voltage Stage Protection.

At Bus Voltage Stage Protection, the whole gate driving signals are disabled and no power is delivered to the output, including both the DC bus voltage stage and the LED d river stage. The current loop comp ensation no de ICOMP pin and the soft start SS pin are pulled low. The hiccup time r for the bus voltage stage starts. The voltage-loop compensation no de VCOMP pin is d isconnected from the internal amplifie r and holds its value until the fault conditio disappears. A 2 µA current source charges the VCOMP pin capacitor till VCOMP voltage hits 3V, and the n a 2 µA current source discharges VCOMP pin until 0 .45V and then the system recovers.

#### **LED Driver Stage Protection**

The fault p rotection for the LED driver stage includes t he open LED protection, short LED protection, over LED current protection and any point of LED string short to ground protection.

The voltage of the LED strings are sensed on VLED1~VLED4 pins. The maximum value of VLED1~VLED4 and their voltage difference are used for pr otection. When the maximu m value of VLED1~VLED4 gets higher than 2.4V or their voltage difference get la rger than 1 50mV (this value can be adjusted by the ext ernal input resistance on VLED# pins), IC trigg ers the LED Driver Stage Protection.

The LED current feedback IFB is also used for over LED current prote ction. When IFB voltage gets higher than 300mV for 200us or when IFB voltage gets higher than 600mV, I C triggers the LED Driver Stage Protection.

The second ary side cur rent of the LED drive r stage is sensed on S SD pin. When SSD pin voltage gets lower tha n -200mV for 2us, IC triggers the LED Driver Stage Protection.

At the LED Driver Stage Protection, the driving signal for the dimming MOSFET is disabled to

turn off the dimming MOSFET and also to disconnect the LED dri ver stage from the po wer stage. The current loop compensation nod e ICOMP is disconnected from the internal amplifier a nd holds its value u ntil the fa ult condition on the LED driver stage disappears. A 2µA current source charges the ICOMP pin capacitor till ICOMP voltage hits 3V, and then a 2µA current source discharges ICOMP pin until

0.45V and then the LED driver stage recovers.

The gate driving signals for the MOSFETs in the power stage are continuous and the DC bus voltage is regulated at the fault condition of LED driver stage. Therefore, the system power supplies are not influenced by the fault protection of the LED driver stage.

Thermal protection is integrated in MP4653.

Figure 2—Real LIPS Power System and Start Up Sequence

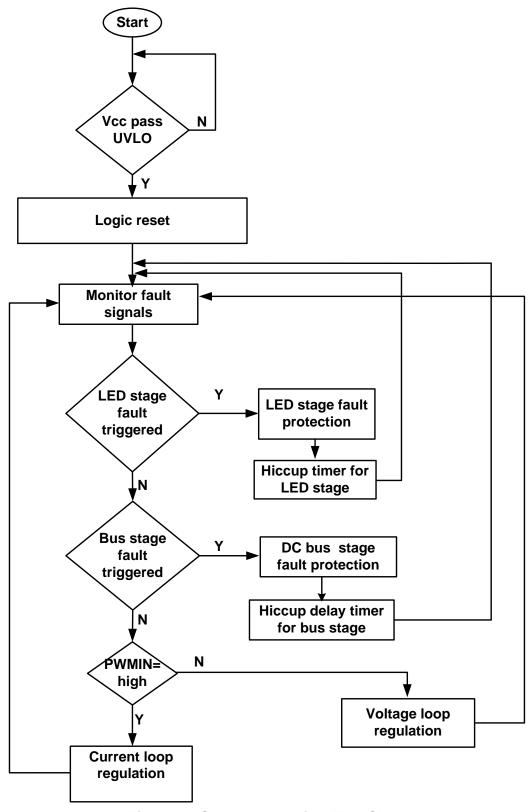

Figure 3—System Operation Flow Chart

### **APPLICATION INFORMATION**

#### Setting the LED Current (Pin7, IFB)

The external LED current sensing resistor sets the maximum LED current (refer to TYPICAL APPLICATION CIRCUIT) and value can be determined using the equation:

$$Rsense = \frac{0.2V}{I_{LED}}$$

The ILED is the total current of the LED strings.

It is recommended a 1k resistor between the IFB pin and the current sensing resistor for sh ort proteciton.

# Setting the minimum/maximum operating frequency (Pin1 SS, Pin2 FSET)

The operating frequency of MP4653 is determined by the sourcing current through SS pin and FSET pin.

$$f_{Qp} = -\frac{21 \cdot .49V}{RR_{SFSET}} - \frac{V_{FSET}}{FSET} \times 1.98 \times 10^9$$

The V <sub>FSET</sub> voltage is the larger value of the outputs of internal amplifiers for voltage loop and current loop. It is in range of 1~2.2V.

The minimum operating frequency is set by:

$$f_{min}' = -\frac{2 \times 1.49 V}{RR_{s-FSET}} = \frac{2.2 V}{r_{SSET}}) \times 1.98 \times 10^9$$

The maximum operating frequency is set by:

$$f_{\text{max}} = -\frac{2 \times 1.49 \text{V}}{\text{RR}_{\text{S\_FSET}}} \quad \frac{1\text{V}}{\text{FSET}}) \times 1.98 \times 10^9$$

# Setting the Soft Start up Frequency and Soft Start Time (Pin1 SS)

The soft start up frequency is:

Usually, the soft start u p frequency could be 1.5 to 3 times of the maximum operating frequency.

The soft st art time is determined by the RC Constant of Rss and  $C_{SS}$ . The soft start t ime could be e stimated with 3 times of the RC Constant:

$$T_{SS} \approx \times R_{SS} \times C_{SS}$$

#### Setting the Voltage Loop Feedback (Pin4 VF B)

The voltage on VFB pin should between 1.2V and 2V at normal operation. Set the voltage feedback divider (R  $_{\text{VFBH}}$  and R  $_{\text{VFBL}}$ ) and make sure the feedback voltage is in this range at normal operation.

$$1.2V < V_{VFB} = \frac{R_{VFBL}}{RR_{BH} + V_{VFBL}} \times V_{bus} < 2V$$

The VFB pin also funct ions as the over voltag e protection for the bus stage. When the voltage on VFB gets higher than 2. 4V, IC triggers bus stage protection.

# Setting Over-Voltage Protection of the LED Stage (Pin9,10,11,12)

The voltage divider sets the over-volta ge protection point (refer to TYPICAL APPLICATION CIRCUIT) through the equation:

$$V_{OVP} = \frac{R_{OVPH} + R_{OVPL}}{R_{OVPI}} \quad 2.4V$$

Normally, the OVP point is setting about 10%-30% higher than the maximum LED voltage.

#### Setting the Voltage Difference Protection of the LED Strings (Pin9,10,11,12)

MP4653 implements the protection when LED string voltage is different from each other, in order to protect the condition that several LEDs in a string are shorted. It is used only for multiple-strings application. The protection point of the voltage difference between LED strings is set by:

$$\Delta V_{\text{pro}}^2 = \frac{RR_{\text{VPH}}^2 + _{\text{OVPL}}}{R1_{\text{VPI}}} \times .4V \times \frac{23k + R_{\text{input}}}{6 \times 23k}$$

Where R<sub>input</sub> is the input resistance of the LED# pin. Adjust the input r esistance to program the protection point.

Application can add a resistor  $R_{\times}$  between the voltage divider and LED# pins to a djust the input resistance.

$$R_{input} = \frac{R_{OVPH} \times R_{OVPL}}{R_{OVPI} + R_{OVPH}} + R_{X}$$

# Setting the Over Current Protection for the bus stage (Pin3 VOCP)

This pin implements the over current protection for the bus stage. The current of the bus stage is sensed to this pin with a negative polarity. When the voltage on this pin is lower than -100mV, the IC triggers the bus stage protection.

$$I_{OCP\_Bus} = \frac{100mV}{R_{VOCP}}$$

Usually, the protection point is aro und 1.5 to 3 times of the normal current of the bus stage.

# Setting the Over Current Protection for the LED stage (Pin8 SSD)

This pin de tects the current throu gh the LED stage with a negative p olarity. When the voltag e on this pin gets lower than -200mV, IC trigge rs LED stage protection.

$$I_{\text{OCP\_LED}} = \frac{200mV}{R_{\text{OCP}}}$$

The over c urrent protection point for the LED stage could usually set at around 1.5 to 2 times of the total current through the LED strings.

# Setting the Voltage Io op compensation (Pin5 VCOMP)

This pin is connected to the output of the inn er error amplifier for the voltage control loop through an internal switch. Place a RC (R  $_{\rm VCOMP}$ , C  $_{\rm VCOMP}$ ) network on this pin for compensating the voltage control loop.

Usually, a ceramic capa citor in range of 47nF to 470nF and a resistor in range of 2k  $\Omega$  to 200k  $\Omega$  is recommended for the compensation.

This pin is also used as the hiccu p mode fault timer. When fault condition in the bus stage occurs, the inner switch which connects this pin to the output of error a mplifier for voltage control loop turns off and a  $2\mu A$  current source will charge this pin to 3V and then discharge it to 0.45V. IC auto recovers after the hiccup timer.

The hiccup delay time is:

$$T_{\text{hiccup\_V}} = \frac{C_{\text{VCOMP}} \times (3V \quad V_{\text{VCOMP}})}{2 \text{A} \mu} \quad \frac{C_{\text{VCOMP}} \times 2.5V}{2 \text{A}}$$

# Setting the current lo op compensation (Pin6 ICOMP)

This pin is connected to the output of the inn er error amplifier for the current control loop through an internal switch. Place a RC (R  $_{\rm ICOMP}$ , C  $_{\rm ICOMP}$ ) network on this pin for the current control loop compensation.

Usually, a ceramic capa citor in range of 47nF to 470nF and a resistor in range of 200  $\Omega$  to 5k  $\Omega$  is recommended for the compensation.

This pin is also used as the hiccu p mode fault timer for the LED stage. When fault condition occurs in the LED stage, the inner switch which connects this pin to the output of the error amplifier for current control loop turns off and a current source will charge this pin to 3V and then discharge it to 0.45V. The control for the LED stage auto recovers after this hiccup timer.

The hiccup delay time is:

$$T_{\text{hiccup}\_I} = \frac{C_{\text{ICOMP}} \times (3V \quad V_{\text{ICOMP0}})}{2 \text{A} \mu} \quad \frac{C_{\text{ICOMP}} \times 2.5 V}{2 A}$$

#### **Analog Dimming (Pin 13, A-Dim)**

This pin is for analo g dimming. Applying a voltage in range of 0V to 1.18V d ims the LED current from 0 to 100%. It has positive polarity for the analog dimming. A ceramic capacitor is recommended on this pin to bypass it.

#### **PWM Dimming input (Pin 14, PWMIN)**

This pin is for PWM dimming input. Applying a PWM dimming signal with frequency in range of 100Hz to 2kHz on this pin. It has positive polarity for the PWM dimming.

At PWM on interval, the LED current is regulated and at PWM off interval, the volta ge control loop for the DC bus functions. The DC bus voltage is regulated at the value of that in PWM on interval.

#### **Supply Input (Pin 15, VIN)**

This pin is the supply input voltage for the I C. Bypass this pin with a 0.1uF or larger ceramic capacitor.

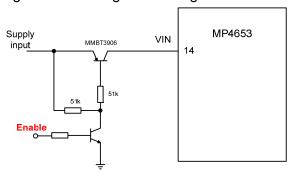

IC starts to work when the VIN voltage is applied. If PWMIN pin is h igh, the LED current control loop is effective and if the PWMIN pin is low, the voltage control loop for the DC bus control is effective. If an "Enable" signal is required to

control the starting operation of the IC, use this "Enable" signal to control this supply input voltage with following circuit in figure 4.

Figure 4—MP4653 Enable control circuit PWM dim ming signal output (Pin 16, PWMOUT)

This pin outputs a PW M dimming signal to drive the external dimming MOSFET (MN) in seri es with the LED string, and achieves fast PWM dimming. Connect a re sistor in ser ies with this pin to adjust the driving speed.

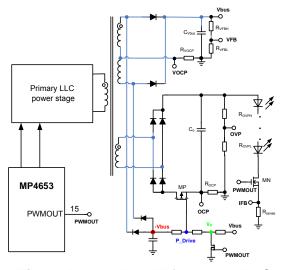

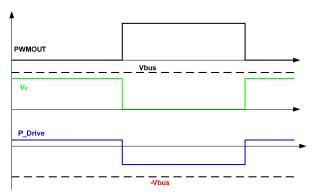

The PWMOUT signal is also used to control the external P-MOS (MP) for protection, as shown in figure 5A. Figure 5B shows the operating scheme of this driving circuit. A negative voltage source (-Vbus) is generated from the secondary winding of DC bus stage. A pulse waveform at "V $_{\rm X}$ " is generated through the PWMOUT signal. By summing the negative voltage source and V $_{\rm X}$ , a pulse wave form with a negative magnitude is generated on "P\_Drive" (the P-MOS gate) and is used to drive the P-MOS.

Figure 5A—PWMOUT for the P MOS Driver

Figure 5B—Scheme of the PWMOUT Driving the P MOS

#### **Gate Driver Supply (Pin 17, VCC)**

This pin su pplies the g ate drive signals GL,GR and PWMOUT. Bypass this pin with a 1uF or larger ceramic capacit or. This pin could also be used to supply an external circuit.

#### Gate Drive Signals (Pin 18,20 GL,GR)

GL and GR provide the driving signal for the power stage. GL and GR are 180 d egree phase shifted gate drive signals. With t he enhanced drive capability, GL and GR can directly drive the external MOSFET in the power st age through a gate driving transformer.

The gate driving transformer also isolates the primary power stage and the secondary control circuit. Place a 2.2nF Y cap between the power stage ground and the reference ground for the control circuit to improve the EMI performance.

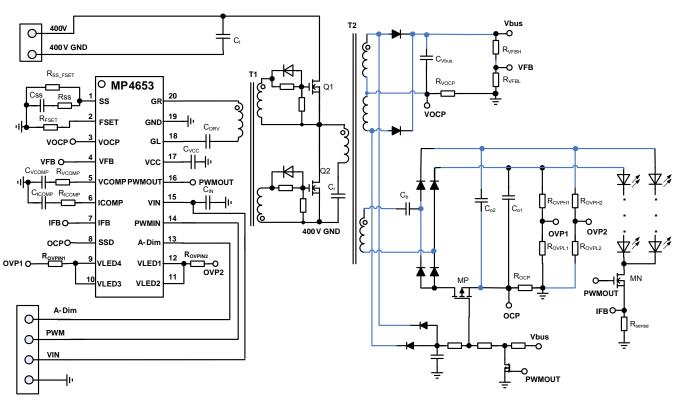

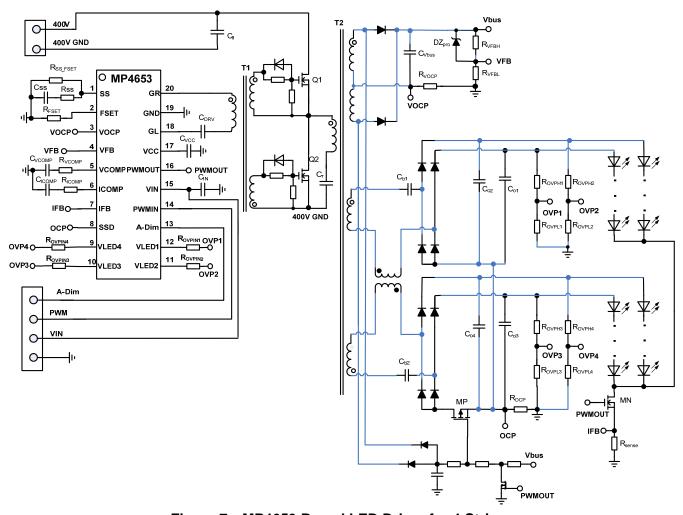

Figure 6—MP4653 Based LED Driver for 2 Strings

Figure 7—MP4653 Based LED Driver for 4 Strings

Please refer to MP4653 application note for the design procedure and example.

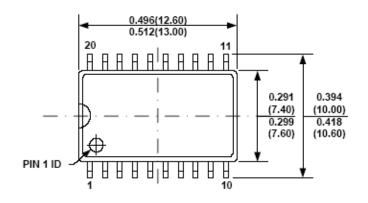

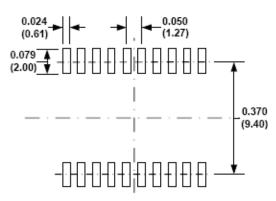

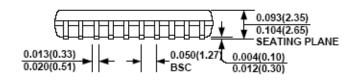

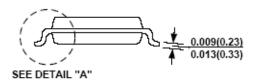

#### PACKAGE INFORMATION

#### SOIC<sub>20</sub>

TOP VIEW

RECOMMENDED LAND PATTERN

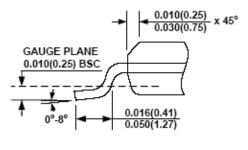

SIDE VIEW

DETAIL "A"

#### NOTE:

- CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-013, VARIATION AC.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.