# Audio Management Integrated Circuit with 2.8 W Class D and LongPlay True Ground Headphone Amplifier

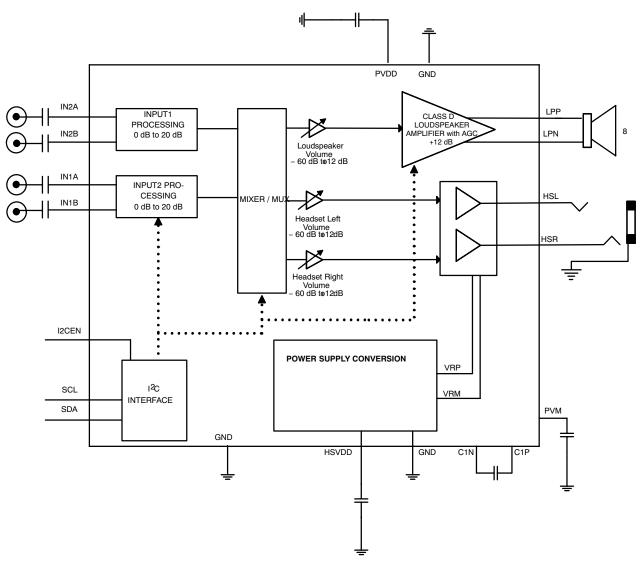

The NCP2704 is a cost effective audio subsystem designed for portable applications such as cellular phones and portable media player. It has been designed to cover the power audio requirements in portable equipment: including a high fidelity Class D speaker amplifier and a Class G equivalent LongPlay true ground headphone amplifier. This patented headphone amplifier circuitry allows the removal of the bulky output capacitors and minimize audio playback current consumption with minimum external components. In addition the user can set the output swing to have enough output dynamic even when a damping resistor is added.

Through a flexible I<sup>2</sup>C interface, NCP2704 can support both single ended and differential types of analog input signal. In both cases, it offers a zero pop noise signature. The same interface allows a user defined architecture with an input control, highly accurate gain setting capability from -60 dB to +12 dB and output control. In addition NCP2704 offers the possibility to reduce the EMI perturbation by lowering the rise and fall times of the Class D outputs (software programmable). The Loudspeaker also amplifier includes an AGC which performs two functions: limiter and non-clipping.

#### **Features**

- Flexible MUX Capability and Volume Control

- Separated Mixer Control Between Louspeaker and Headset

- Support Either Differential or Single-ended Input

- High Sound Quality

- ◆ -100 dB PSRR on Headphone Amplifier

- → -80 dB PSRR on Loudspeaker Amplifier

- 0.02% THD+N at 1 kHz on Headset Amplifier

- 0.1% THD+N at 1 kHz on Loudspeaker Amplifier

- Low EMI Filterless Class D Loudspeaker Amplifier, Programmable High Efficiency or Low EMI Mode

- Programmable AGC: Non-Clipping or Power Limit (Loudspeaker Output)

- Long Play True Ground Headphone Amplifier, Programmable Output Swing (Up to 5 V<sub>pp</sub>)

- I<sup>2</sup>C Control

- Software Shutdown

- No Pop and Click Noise

- TDMA Noise Free

- Thermal and Short-Circuit Protection

#### ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAM

NCP2704 = Specific Device Code A = Assembly Location

Y = Year

WW = Work Week

= Pb-Free Package

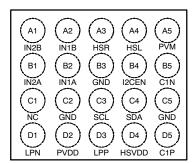

#### **PINOUT**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package

- 20-Bump Chip Scale Package (2.5 x 2.0 mm)

- This is a Pb-Free Device

#### **Typical Applications**

- Cellular Phones

- Portable Media Player

Figure 1. Simplified Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin | Pin Name          | Туре              | Description                                                                                                                                                      |

|-----|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2  | IN1A              | Input             | First audio input. It is paired with IN1B. This pin is configured for single ended or differential types of input, pending on the I <sup>2</sup> C programming.  |

| A2  | IN1B              | Input             | First audio input. It is paired with IN1A. This pin is configured for single ended or differential types of input, pending on the I <sup>2</sup> C programming.  |

| B1  | IN2A              | Input             | Second audio input. It is paired with IN2B. This pin is configured for single ended or differential types of input, pending on the I <sup>2</sup> C programming. |

| A1  | IN2B              | Input             | Second audio input. It is paired with IN2A. This pin is configured for single ended or differential types of input, pending on the I <sup>2</sup> C programming. |

| СЗ  | SCL               | Input             | Clock input for the I <sup>2</sup> C bus.                                                                                                                        |

| C4  | SDA               | Input /<br>Output | Data input for the I <sup>2</sup> C bus.                                                                                                                         |

| В3  | GND               | Power             | Analog ground.                                                                                                                                                   |

| D4  | HSV <sub>DD</sub> | Power             | Power supply dedicated to the charge pump and the headset amplifier. A low ESR ceramic capacitor to ground is required.                                          |

| C5  | GND               | Power             | Power ground dedicated to the charge pump and the headset amplifier.                                                                                             |

| C2  | GND               | Power             | Power ground dedicated to the loudspeaker and the receiver.                                                                                                      |

| А3  | HSR               | Output            | Headset amplifier right output.                                                                                                                                  |

| A4  | HSL               | Output            | Headset amplifier left output.                                                                                                                                   |

| D1  | LPN               | Output            | Loudspeaker negative output.                                                                                                                                     |

| D3  | LPP               | Output            | Loudspeaker positive output.                                                                                                                                     |

| D2  | $PV_{DD}$         | Power             | Power supply. A low ESR ceramic capacitor to ground is required.                                                                                                 |

| B4  | I2CEN             | Input             | I <sup>2</sup> C enable pin                                                                                                                                      |

| D5  | C1P               | Output            | Charge pump flying capacitor positive capacitor.                                                                                                                 |

| B5  | C1N               | Output            | Charge pump flying capacitor negative capacitor.                                                                                                                 |

| A5  | PVM               | Output            | Charge pump output. This is the symmetrical voltage of the power supply applied on the HSV <sub>BAT.</sub> A low ESR ceramic capacitor to ground is required.    |

| C1  | NC                | -                 | Not connected pin                                                                                                                                                |

#### **MAXIMUM RATINGS**

| Rating                                                                     | Symbol            | Value                          | Unit |

|----------------------------------------------------------------------------|-------------------|--------------------------------|------|

| PV <sub>DD</sub> : Power Supply Voltage (Note 1)                           | V <sub>IN</sub>   | -0.3 to + 6.0                  | V    |

| HSV <sub>DD</sub> (Note 1)                                                 | V <sub>IN</sub>   | -0.3 to + 4.5                  | V    |

| Other Pins (Note 1)                                                        | V <sub>YY</sub>   | -0.3 to P <sub>VDD</sub> + 0.3 | V    |

| Human Body Model (HBM) ESD Rating are (Note 2)                             | ESD HBM           | 2000                           | V    |

| Machine Model (MM) ESD Rating are (Note 2)                                 | ESD MM            | 200                            | V    |

| CSP 2.5 x 2 mm package (Notes 6 and 7) Thermal Resistance Junction-to-Case | $R_{\theta JC}$   | Note 7                         | °C/W |

| Operating Ambient Temperature Range                                        | T <sub>A</sub>    | -40 to +85                     | °C   |

| Operating Junction Temperature Range                                       | T <sub>J</sub>    | -40 to +125                    | °C   |

| Maximum Junction Temperature (Note 6)                                      | T <sub>JMAX</sub> | +150                           | °C   |

| Storage Temperature Range                                                  | T <sub>STG</sub>  | -65 to +150                    | °C   |

| Moisture Sensitivity (Note 5)                                              | MSL               | Level 1                        |      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

- Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = 25°C.

According to JEDEC standard JESD22–A108B.

- This device series contains ESD protection and passes the following tests:

Human Body Model (HBM) ± 2.0 kV per JEDEC standard: JESD22–A114 for all pins.

Machine Model (MM) ±200 V per JEDEC standard: JESD22-A115 for all pins.

- Latch up Current Maximum Rating: ±100 mA per JEDEC standard: JESD78 Class II.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J–STD–020A.

- 6. The thermal shutdown set to  $160^{\circ}$ C (typical) avoids irreversible damage on the device due to power dissipation.

- The R<sub>8CA</sub> is dependent of the PCB heat dissipation. The maximum power dissipation (PD) is dependent by the min input voltage, the max output current and external components selected.

$$R_{\theta CA} = \frac{125 - T_A}{P_D} - R_{\theta JC}$$

| Symbol               | Parameter                                 | Conditions                                                                                                                                                                                                                                                                                                                                                                                               | Min | Тур                                  | Max                                     | Unit |

|----------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|-----------------------------------------|------|

| GENERAL              |                                           | •                                                                                                                                                                                                                                                                                                                                                                                                        |     | •                                    |                                         |      |

| PV <sub>DD</sub>     | Supply voltage range                      |                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5 |                                      | 5.5                                     | V    |

| HSV <sub>DD</sub>    | Supply voltage range                      |                                                                                                                                                                                                                                                                                                                                                                                                          | 1.6 |                                      | 3.6                                     | V    |

| I <sub>SD</sub>      | Shutdown current                          | Soft shutdown<br>PV <sub>DD</sub><br>HSV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                   |     | 0.1                                  | 1                                       | μΑ   |

| Iα                   | Quiescent current                         | Headset mode at Ta = 25°C,  PV <sub>DD</sub> = 3.6 V, HSV <sub>DD</sub> = 1.8 V  PV <sub>DD</sub> HSV <sub>DD</sub> Speaker mode at Ta = 25°C,  PV <sub>DD</sub> = 3.6 V, HSV <sub>DD</sub> = 1.8 V  PV <sub>DD</sub> HSV <sub>DD</sub> Headset + Speaker mode at Ta = 25°C, PV <sub>DD</sub> = 3.6 V, HSV <sub>DD</sub> = 1.8 V  PV <sub>DD</sub> HSV <sub>DD</sub> HSV <sub>DD</sub> HSV <sub>DD</sub> |     | 0.1<br>2<br>2.2<br>1.8<br>2.2<br>2.8 | 0.25<br>2.5<br>2.8<br>2.1<br>2.8<br>3.3 | mA   |

| R <sub>IN</sub>      | Input resistance                          |                                                                                                                                                                                                                                                                                                                                                                                                          | 18  | 20                                   | 24                                      | kΩ   |

| CMRR                 | Common mode rejection ratio               | F = 1 kHz, differential input mode                                                                                                                                                                                                                                                                                                                                                                       |     | -80                                  |                                         | dB   |

| T <sub>SD</sub>      | Thermal shutdown temperature              |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 160                                  |                                         | °C   |

| T <sub>SD_hyst</sub> | Thermal shutdown temperature hysteresis   |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 20                                   |                                         | °C   |

| UVLO1                | Undervoltage lockout on PV <sub>DD</sub>  |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 2.2                                  |                                         | V    |

| UVLO1 <sub>hys</sub> | UVLO hysteresis on PV <sub>DD</sub>       |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 150                                  |                                         | mV   |

| UVLO2                | Undervoltage lockout on HSV <sub>DD</sub> |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 1.4                                  |                                         | V    |

| UVLO2 <sub>hys</sub> | UVLO hysteresis on HSV <sub>DD</sub>      |                                                                                                                                                                                                                                                                                                                                                                                                          |     | 100                                  |                                         | mV   |

| VOLUME C             | ONTROL                                    | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                 | •   | •                                    | •                                       |      |

|                      | Digital volume range Loudspeaker          | Minimum gain<br>Maximum gain                                                                                                                                                                                                                                                                                                                                                                             |     | -60<br>12                            |                                         | dB   |

|                      | Digital volume range Headset              | Minimum gain<br>Maximum gain                                                                                                                                                                                                                                                                                                                                                                             |     | -60<br>12                            |                                         | dB   |

|                      | Preamp gain                               | Input 1 or 2<br>INxG = 00<br>INxG = 01<br>INxG = 10<br>INxG = 11                                                                                                                                                                                                                                                                                                                                         |     | 0<br>+6<br>+12<br>+20                |                                         | dB   |

|                      | Maximum gain setting Headset              | INxG = 11 and gain control = 110100                                                                                                                                                                                                                                                                                                                                                                      |     | +32                                  |                                         | dB   |

|                      | Maximum gain setting Speaker              | INxG = 11 and gain control = 100111<br>(speaker amplifier has a gain of<br>+12 dB)                                                                                                                                                                                                                                                                                                                       |     | +44                                  |                                         | dB   |

<sup>8.</sup> Guaranteed by design and characterized.

| Symbol              | Parameter                                                            | Conditions                                                                                                                                                                                                                           | Min | Тур                                 | Max | Unit |

|---------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-----|------|

| LOUDSPEA            | KER                                                                  | •                                                                                                                                                                                                                                    |     | •                                   |     | '    |

| V <sub>OS</sub>     | Absolute Offset Voltage                                              | Inputs AC Grounded                                                                                                                                                                                                                   |     | ± 1                                 |     | mV   |

| R <sub>DS(ON)</sub> | Static drain–source on–state resistance for both P and NMOS (Note x) |                                                                                                                                                                                                                                      |     | 200                                 | 300 | mΩ   |

| Z <sub>SD</sub>     | Output Impedance in Shutdown Mode                                    |                                                                                                                                                                                                                                      |     | 20                                  |     | kΩ   |

| I <sub>BR</sub>     | Current Breaker Threshold                                            |                                                                                                                                                                                                                                      |     | 2                                   |     | Α    |

| F <sub>LP</sub>     | -3 dB Cut off Frequency of the Built in<br>Low Pass Filter           |                                                                                                                                                                                                                                      |     | 30                                  |     | kHz  |

| F <sub>SW1</sub>    | Class D Switching Frequency                                          |                                                                                                                                                                                                                                      |     | 300                                 |     | kHz  |

| T <sub>ON</sub>     | Turn On Time                                                         |                                                                                                                                                                                                                                      |     | 4                                   |     | ms   |

| T <sub>OFF</sub>    | Turn Off Time                                                        | No audio signal and outputs tied to GND                                                                                                                                                                                              |     | 8                                   |     | ms   |

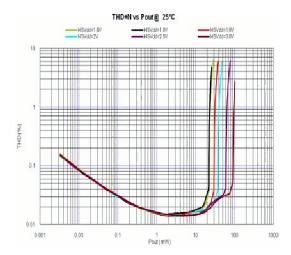

| Po                  | RMS Output Power                                                     | $\begin{aligned} R_L = 8 \ \Omega, \ F = 1 \ kHz, \ THD + N < 1\% \\ PV_{DD} = 2.5 \ V \\ PV_{DD} = 3.0 \ V \\ PV_{DD} = 3.6 \ V \\ PV_{DD} = 4.2 \ V \\ PV_{DD} = 5.0 \ V \end{aligned}$                                            |     | 0.33<br>0.49<br>0.75<br>0.97<br>1.4 |     | W    |

| Po                  | RMS Output Power                                                     | $\begin{aligned} R_L = 8 \ \Omega, \ F = 1 \ kHz, \ THD+N < 10\% \\ PV_{DD} = 2.5 \ V \\ PV_{DD} = 3.0 \ V \\ PV_{DD} = 3.6 \ V \\ PV_{DD} = 4.2 \ V \\ PV_{DD} = 5.0 \ V \end{aligned}$                                             |     | 0.41<br>0.60<br>0.87<br>1.20<br>1.7 |     | W    |

| THD+N               | Total Harmonic Distortion + Noise                                    | $\begin{array}{l} \text{PV}_{\text{DD}} = 5.0 \text{ V, P}_{\text{OUT}} = 1 \text{ W, R}_{\text{L}} = \\ 8 \Omega \\ \text{PV}_{\text{DD}} = 3.6 \text{ V, P}_{\text{OUT}} = 0.35 \text{ W, R}_{\text{L}} = \\ 8 \Omega \end{array}$ |     | 0.1<br>0.1                          |     | %    |

| SNR                 | Signal to Noise Ratio                                                | $PV_{DD}$ = 3.6 V, $P_{OUT}$ = 0.8 W, $R_L$ = 8 $\Omega$                                                                                                                                                                             |     | 94                                  |     | dB   |

| CMRR                | Common Mode Rejection Ratio                                          | $V_{ic}$ = 0.5 V to (V <sub>DD</sub> – 0.8 V)<br>$R_L$ = 8 $\Omega$ , $V_{ripple\ pk-pk}$<br>F = 20 Hz to 20 kHz                                                                                                                     |     | -80                                 |     | dB   |

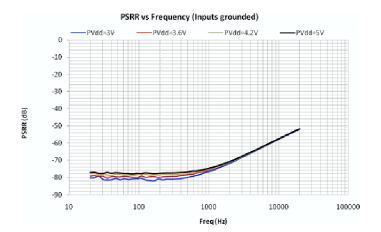

| PSRR                | Power Supply Rejection Ratio                                         | $V_{Pripple\_pk-pk}$ = 200 mV, $R_L$ = 8 $\Omega$ Inputs AC grounded F = 217 Hz, Gain = 0 dB                                                                                                                                         |     | -80                                 |     | dB   |

| η                   | Efficiency                                                           | $R_L = 8 \Omega, F = 1 \text{ kHz}$<br>$PV_{DD} = 3.6 \text{ V}, P_{OUT} = 0.6 \text{ W}$                                                                                                                                            |     | 87                                  |     | %    |

<sup>8.</sup> Guaranteed by design and characterized.

| Symbol           | Parameter                                                                                                 | Conditions                                                                                                                                               | Min | Тур                   | Max   | Unit              |

|------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|-------|-------------------|

| HEADSET          | •                                                                                                         | •                                                                                                                                                        | •   | •                     |       | •                 |

| Vos              | Output offset voltage                                                                                     | Input AC grounded                                                                                                                                        |     | ± 1                   |       | mV                |

| T <sub>WU</sub>  | Turning On time                                                                                           | Slow = 1<br>Slow = 0                                                                                                                                     |     | 1<br>34               |       | ms                |

| V <sub>LP</sub>  | Max Output Swing (peak value) (output in phase) (see LDO programming table, ≤ HSV <sub>DD</sub> − 200 mV) | HSV <sub>DD</sub> = 1.8 V, Headset = 16 $\Omega$<br>HSV <sub>DD</sub> = 2.5 V, Headset = 16 $\Omega$<br>HSV <sub>DD</sub> = 1.8 V, Headset = 32 $\Omega$ |     | 1<br>1.65<br>1.3<br>2 |       | V <sub>peak</sub> |

|                  |                                                                                                           | $HSV_{DD}$ = 2.7 V, Headset = 32 Ω<br>$HSV_{DD}$ = 1.8 V, No load<br>$HSV_{DD}$ = 2.7 V, No load                                                         |     | 1.6<br>2.5            |       |                   |

| P <sub>O</sub>   | Max Output Power                                                                                          | $HSV_{DD}$ = 1.8V, $THD+N$ = 1%<br>$Headset$ = 16 $\Omega$<br>$Headset$ = 32 $\Omega$                                                                    |     | 30<br>26              |       | mW                |

| P <sub>O</sub>   | Max Output Power                                                                                          | $HSV_{DD}$ = 2.5V, $THD+N$ = 1%<br>$Headset$ = 16 $\Omega$<br>$Headset$ = 32 $\Omega$                                                                    |     | 86<br>62              |       | mW                |

|                  | Crosstalk                                                                                                 |                                                                                                                                                          |     | -75                   |       | dB                |

| PSRR             | Power Supply Rejection Ratio                                                                              | Inputs Shorted to Ground Gain = 0 dB F = 217 Hz to 1 kHz                                                                                                 |     | -100                  |       | dB                |

| THD+N            | Total Harmonic Distortion + Noise                                                                         | Headset = 16 $\Omega$<br>P <sub>OUT</sub> = 15 mW, F = 1 kHz                                                                                             |     | 0.015                 |       | %                 |

| THD+N            | Total Harmonic Distortion + Noise                                                                         | Headset = 32 $\Omega$<br>V <sub>OUT</sub> = 400 mV, F = 1 kHz                                                                                            |     | -75                   |       | dB                |

| C <sub>OUT</sub> | Maximum Output Capacitance to Ground                                                                      |                                                                                                                                                          |     | 100                   |       | pF                |

| Z <sub>SD</sub>  | Output Impedance in Shutdown Mode                                                                         |                                                                                                                                                          |     | 25                    |       | kΩ                |

|                  | Channel to channel gain tolerance                                                                         | T <sub>A</sub> = +25 °C, volume at 0 dB                                                                                                                  |     | ±0.3                  | ± 2.5 | %                 |

| F <sub>SW2</sub> | Headset charge pump switching frequency                                                                   | P <sub>O</sub> > 500 μW                                                                                                                                  |     | 1.2                   |       | MHz               |

| F <sub>SW3</sub> | Headset charge pump switching frequency                                                                   | P <sub>O</sub> < 500 μW                                                                                                                                  |     | 150                   |       | KHz               |

| SNR              | Signal to Noise Ratio                                                                                     | $HSV_{DD}$ = 1.8 V, $P_{OUT}$ = 20 mW, $R_L$ = 16 $Ω$                                                                                                    |     | 97                    |       | dB                |

<sup>8.</sup> Guaranteed by design and characterized.

| Symbol                  | Parameter                                 | Conditions | Min                       | Тур | Max                       | Unit |

|-------------------------|-------------------------------------------|------------|---------------------------|-----|---------------------------|------|

| I <sup>2</sup> C INTERF | ACE (Note 8)                              |            |                           |     |                           |      |

| V <sub>IL</sub>         | Low input voltage level                   |            | -0.5                      |     | 0.3 *<br>V <sub>BAT</sub> | V    |

| V <sub>IH</sub>         | High input voltage level                  |            | 0.7 *<br>V <sub>BAT</sub> |     | V <sub>BAT</sub><br>+ 0.5 | V    |

| V <sub>OL</sub>         | Low level output voltage                  |            | 0                         |     | 0.2 *<br>V <sub>BAT</sub> | V    |

| F <sub>CLK-MAX</sub>    | Clock maximum speed                       |            | 400                       |     |                           | kHz  |

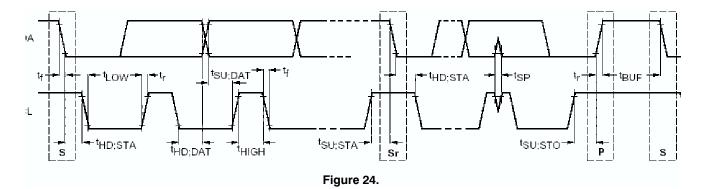

| t <sub>HD-START</sub>   | Hold time (repeated) start condition      |            | 0.6                       |     |                           | μS   |

| t <sub>LOW</sub>        | Low period of SCL clock                   |            | 1.3                       |     |                           | μS   |

| t <sub>HIGH</sub>       | High period of SCL clock                  |            | 0.6                       |     |                           | μS   |

| t <sub>SU-START</sub>   | Setup time for a repeated start condition |            | 0.6                       |     |                           | μs   |

| t <sub>SU-STO</sub>     | Setup time for STOP condition             |            | 0.6                       |     |                           | μS   |

<sup>8.</sup> Guaranteed by design and characterized.

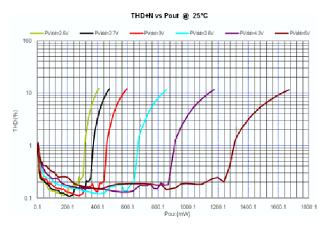

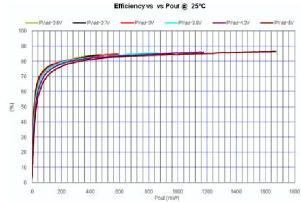

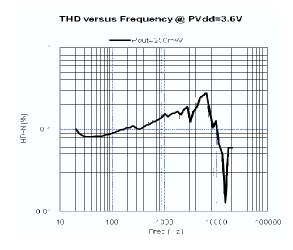

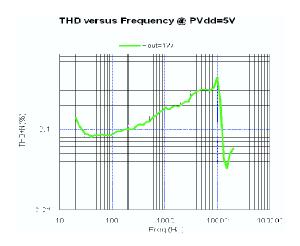

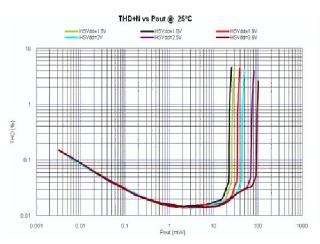

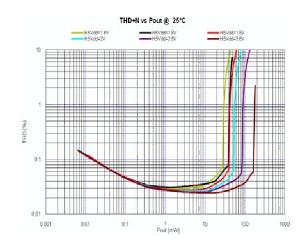

# TYPICAL OPERATING CHARACTERISTICS Loudspeaker

Figure 2. THD+N vs  $\text{P}_{\text{out}},$  8  $\Omega$  load

Figure 3. Efficiency vs Pout

Figure 4. THD+N vs Frequency at P<sub>VDD</sub> = 3.6 V

Figure 5. THD+N vs Frequency at  $P_{VDD} = 5 \text{ V}$

Figure 6. PSRR vs Frequency

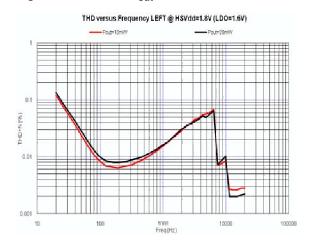

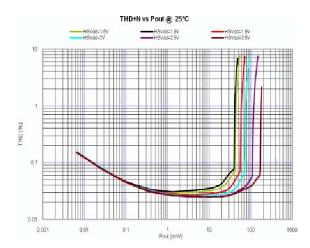

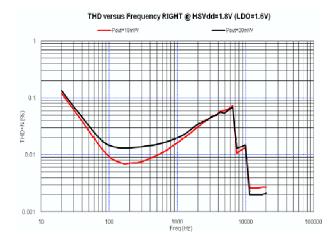

# TYPICAL OPERATING CHARACTERISTICS Headphone

Figure 7. THD+N vs  $\mathbf{P}_{\text{out}},$  32  $\Omega$  Load in Phase

Figure 9. THD+N vs  $\mathbf{P}_{\text{out}}\text{, 32}\;\Omega$  Load Out of Phase

Figure 11. THD+N vs Frequency, 32  $\Omega$  Load in Phase, Left Channel

Figure 8. THD+N vs  $\mbox{P}_{\mbox{out}},$  16  $\Omega$  Load in Phase

Figure 10. THD+N vs  $\text{P}_{\text{out}}\text{, }16~\Omega$  Load Out of Phase

Figure 12. THD+N vs Frequency, 32  $\Omega$  Load in Phase, Right Channel

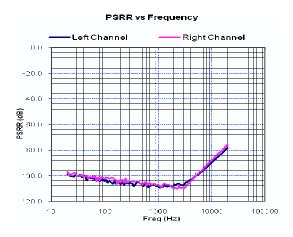

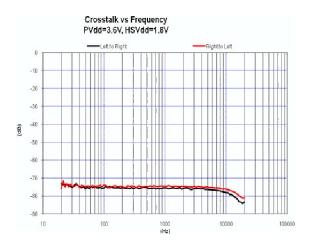

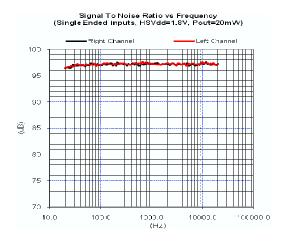

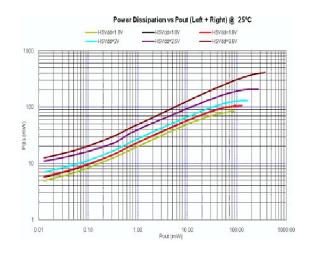

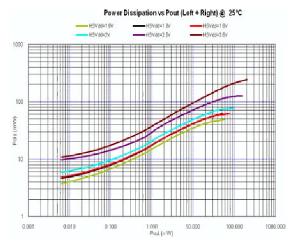

# TYPICAL OPERATING CHARACTERISTICS Headphone

Figure 13. PSRR vs Frequency

Figure 14. Crosstalk vs Frequency

Figure 15. SNR vs Frequency at  $P_{out} = 20 \text{ mW}$

Figure 16. Power Dissipation vs  $\mathbf{P}_{\mathrm{out}}$  with 16  $\Omega$  Load

Figure 17. Power Dissipation vs  $\mathbf{P}_{\text{out}}$  with 32  $\Omega$  Load

#### **DETAIL OPERATING DESCRIPTION**

#### **DETAILED DESCRIPTIONS**

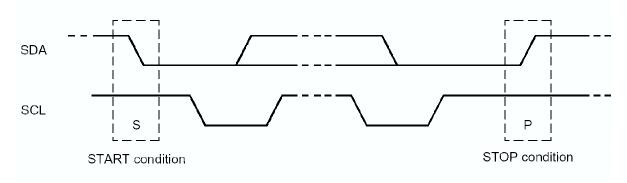

# I<sup>2</sup>C COMPATIBLE INTERFACE

# Start and Stop Conditions

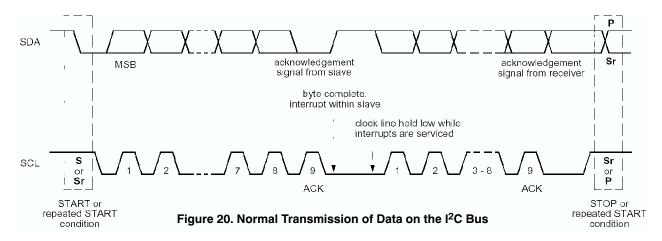

Communication is initiated by HIGH to LOW transition on SDA line while SCL is still high. This signal

configuration defines the START condition (noted S). Communication is terminated when a LOW to HIGH transition occurs on SDA while SCL is high. This defines the STOP condition (noted P).

Figure 18. Start and Stop Bits Configuration on the I<sup>2</sup>C Bus

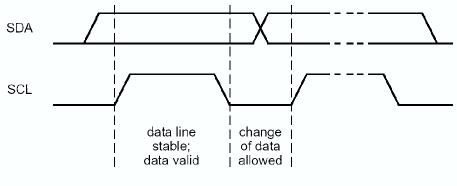

# Data Validity

During normal data transmission, the SDA will not transition during a SCL High.

Figure 19. Data Validity

#### Data transfer on the I<sup>2</sup>C bus

Data communication begins with a Start. The first transmitted Byte is the Slave address (7 bits, MSB first) followed by the Read/Write bit. A "zero" indicates a "write" and a "one" indicates a "read" sequence. The byte is followed by an acknowledgement (mandatory) where the receiver pulls down the SDA line after the last received bit, to indicate that the information was received correctly. The receiver releases the SDA line after the 9<sup>th</sup> SCL pulse. Then the second byte may be transmitted.

More details about Data transfer and Acknowledgement may be found in chapter 7 of "the I<sup>2</sup>C bus specification".

# Note about "repeated Start" (Sr)

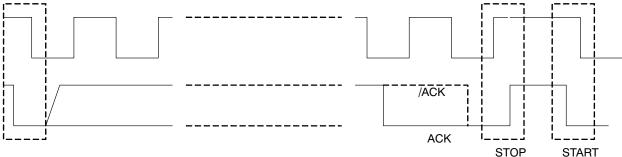

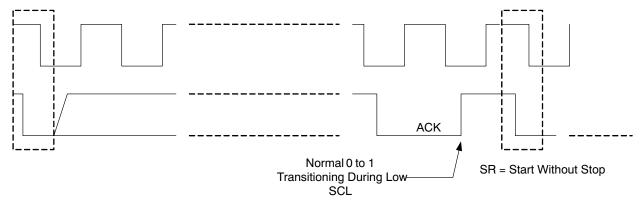

A Sr condition can happen any time during an I<sup>2</sup>C transaction. The SDA line cannot transition while SCL line is in High level state, except for START / STOP and Sr conditions. A Sr condition is a equivalent to a START condition (SDA line transitions from High to Low while SCL is High level). However, a STOP condition is not necessary before a Start. When there is no Stop, the Start is called Sr:

#### **Normal STOP Then START:**

Figure 21.

# Repeated Start (Sr):

First case: SDA transitions normally from 0 to 1 during SCL low state. However, master generates a Start during

SCL high state. This is a Start without stop and is a Sr condition

Figure 22.

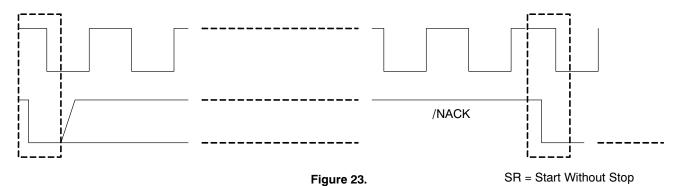

Second case: SDA is already at High state (for example after a /ACK. Then, master generates a Start during SCL high state. This is a Start without stop and is a Sr condition

**Bus Timing**

# NCP2704 I2C ADDRESS

|                                                                                 | I2C Address |   |   |   |   |   |   |  |  |

|---------------------------------------------------------------------------------|-------------|---|---|---|---|---|---|--|--|

| D7         D6         D5         D4         D3         D2         D1         D0 |             |   |   |   |   |   |   |  |  |

| 1                                                                               | 0           | 0 | 0 | 0 | 0 | 1 | Х |  |  |

# **REGISTER MAP**

12 different registers can be addressed through the "Register Address" byte.

| Register |                           | I <sup>2</sup> C Address |    |    |    |    |    |    |    |

|----------|---------------------------|--------------------------|----|----|----|----|----|----|----|

| Number   | Function                  | D7                       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0        | Input Control             | -                        | -  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1        | Speaker Volume<br>Control | -                        | -  | 0  | 0  | 0  | 0  | 0  | 1  |

| 2        | Left Volume Control       | -                        | -  | 0  | 0  | 0  | 0  | 1  | 0  |

| 3        | Right Volume Control      | -                        | -  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4        | Output control            | -                        | -  | 0  | 0  | 0  | 1  | 0  | 0  |

| 5        | LDO Control               | -                        | -  | 0  | 0  | 0  | 1  | 0  | 1  |

| 6        | Status                    | -                        | -  | 0  | 0  | 0  | 1  | 1  | 0  |

| 7        | ACNT                      | -                        | -  | 0  | 0  | 0  | 1  | 1  | 1  |

| 8        | ACONFA                    | -                        | -  | 0  | 0  | 1  | 0  | 0  | 0  |

| 9        | ACONFR                    | -                        | -  | 0  | 0  | 1  | 0  | 0  | 1  |

| 10       | ACONFH                    | -                        | -  | 0  | 0  | 1  | 0  | 1  | 0  |

| 11       | EMI control               | -                        | -  | 0  | 0  | 1  | 0  | 1  | 1  |

| 59       | Reserved*                 | -                        | -  | 1  | 1  | 1  | 0  | 1  | 1  |

| 60       | Reserved*                 | -                        | -  | 1  | 1  | 1  | 1  | 0  | 0  |

| 61       | Reserved*                 | -                        | -  | 1  | 1  | 1  | 1  | 0  | 1  |

| 62       | Reserved*                 | -                        | -  | 1  | 1  | 1  | 1  | 1  | 0  |

| 63       | Reserved*                 | -                        | _  | 1  | 1  | 1  | 1  | 1  | 1  |

<sup>\*</sup>End user should never neither read nor write this register.

# **INPUT CONTROL**

This register allows the setting of the input stage as follows:

INxC sets up the configuration on each input. NCP2704 brings the flexibility to set up each input pair for a differential input signal or two single-ended ones.

- -1 = Inputs are set as differential input with InxA as the positive and InxB as the negative.

- 0 = Inputs are set as stereo single-ended input with InxA as left input and InxB as right input.

| D7 | D6 | D5   | D4   | D3              | D2 | D1 | D0 |

|----|----|------|------|-----------------|----|----|----|

| х  | х  | IN1C | IN2C | IN <sup>-</sup> | 1G | IN | 2G |

# IN1G configures the gain on the first input

| D3  | D2 | IN1G    |

|-----|----|---------|

| 0 0 |    | 0 dB    |

| 0   | 1  | + 6 dB  |

| 1   | 0  | + 12 dB |

| 1   | 1  | + 20 dB |

# IN2G configures the gain on the second input

| D1 | D0 | IN2G    |

|----|----|---------|

| 0  | 0  | 0 dB    |

| 0  | 1  | + 6 dB  |

| 1  | 0  | + 12 dB |

| 1  | 1  | + 20 dB |

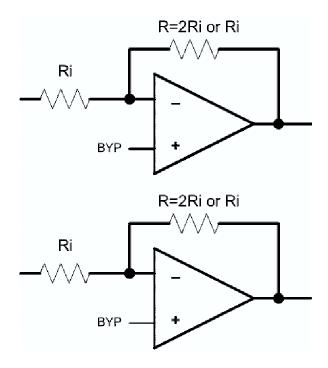

When a single-ended configuration is required, for example a stereo signal, the first internal stage is described on **Figure 25**:

Figure 25. NCP2704 Input Stage for Single-Ended Type of Input

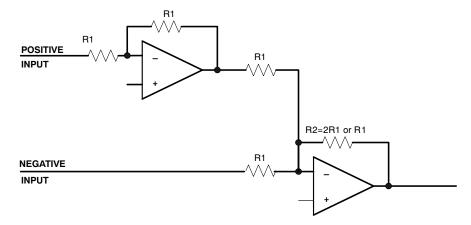

When a differential audio signal is used, the internal first stage is described in **Figure 26**:

Figure 26. NCP2704 Input Stage for Differential Type of Input

# RIGHT, LEFT VOLUME CONTROL

As described in the register "**REGISTER MAP**" section, NCP2704 allows separated volume control for Headset Right, Headset Left.

| D7* | D6* | D5 | D4 | D3      | D2     | D1 | D0 |

|-----|-----|----|----|---------|--------|----|----|

| х   | x   |    |    | GAIN CO | ONTROL |    |    |

<sup>\*</sup>D7 and D6 bits can be either 0 or 1. NCP2704 will only process D5 to D0 to address the targeted gain setting.

| D5 | D4 | D3 | D2 | D1 | D0 | Gain (dB) |

|----|----|----|----|----|----|-----------|

| 0  | 0  | 0  | 0  | 0  | 0  | Mute      |

| 0  | 0  | 0  | 0  | 0  | 1  | -60       |

| 0  | 0  | 0  | 0  | 1  | 0  | -54       |

| 0  | 0  | 0  | 0  | 1  | 1  | -48       |

| 0  | 0  | 0  | 1  | 0  | 0  | -45       |

| 0  | 0  | 0  | 1  | 0  | 1  | -42       |

| 0  | 0  | 0  | 1  | 1  | 0  | -39       |

| 0  | 0  | 0  | 1  | 1  | 1  | -36       |

| 0  | 0  | 1  | 0  | 0  | 0  | -34       |

| 0  | 0  | 1  | 0  | 0  | 1  | -32       |

| 0  | 0  | 1  | 0  | 1  | 0  | -30       |

| 0  | 0  | 1  | 0  | 1  | 1  | -28       |

| 0  | 0  | 1  | 1  | 0  | 0  | -27       |

| 0  | 0  | 1  | 1  | 0  | 1  | -26       |

| 0  | 0  | 1  | 1  | 1  | 0  | -25       |

| 0  | 0  | 1  | 1  | 1  | 1  | -24       |

| 0  | 1  | 0  | 0  | 0  | 0  | -23       |

| 0  | 1  | 0  | 0  | 0  | 1  | -22       |

| 0  | 1  | 0  | 0  | 1  | 0  | -21       |

| 0  | 1  | 0  | 0  | 1  | 1  | -20       |

| 0  | 1  | 0  | 1  | 0  | 0  | -19       |

| 0  | 1  | 0  | 1  | 0  | 1  | -18       |

| 0  | 1  | 0  | 1  | 1  | 0  | -17       |

| 0  | 1  | 0  | 1  | 1  | 1  | -16       |

| 0  | 1  | 1  | 0  | 0  | 0  | -15       |

| 0  | 1  | 1  | 0  | 0  | 1  | -14       |

| 0  | 1  | 1  | 0  | 1  | 0  | -13       |

| 0  | 1  | 1  | 0  | 1  | 1  | -12       |

| 0  | 1  | 1  | 1  | 0  | 0  | -11       |

| 0  | 1  | 1  | 1  | 0  | 1  | -10       |

| 0  | 1  | 1  | 1  | 1  | 0  | -9        |

| 0  | 1  | 1  | 1  | 1  | 1  | -8        |

| 1  | 0  | 0  | 0  | 0  | 0  | -7        |

| 1  | 0  | 0  | 0  | 0  | 1  | -6        |

| 1  | 0  | 0  | 0  | 1  | 0  | -5        |

| 1  | 0  | 0  | 0  | 1  | 1  | -4        |

| 1  | 0  | 0  | 1  | 0  | 0  | -3        |

| D5 | D4 | D3 | D2 | D1 | D0 | Gain (dB) |

|----|----|----|----|----|----|-----------|

| 1  | 0  | 0  | 1  | 0  | 1  | -2        |

| 1  | 0  | 0  | 1  | 1  | 0  | -1        |

| 1  | 0  | 0  | 1  | 1  | 1  | 0         |

| 1  | 0  | 1  | 0  | 0  | 0  | +1        |

| 1  | 0  | 1  | 0  | 0  | 1  | +2        |

| 1  | 0  | 1  | 0  | 1  | 0  | +3        |

| 1  | 0  | 1  | 0  | 1  | 1  | +4        |

| 1  | 0  | 1  | 1  | 0  | 0  | +5        |

| 1  | 0  | 1  | 1  | 0  | 1  | +6        |

| 1  | 0  | 1  | 1  | 1  | 0  | +7        |

| 1  | 0  | 1  | 1  | 1  | 1  | +8        |

| 1  | 1  | 0  | 0  | 0  | 0  | +9        |

| 1  | 1  | 0  | 0  | 0  | 1  | +10       |

| 1  | 1  | 0  | 0  | 1  | 0  | +11       |

| 1  | 1  | 0  | 0  | 1  | 1  | +12       |

As described above, an additional gain setting is possible in the "INPUT CONTROL" register. Thus, final gain setting can go up to 32 dB for the signal applied on the IN1 and IN2 input.

# **SPEAKER VOLUME CONTROL**

As described in the register "REGISTER MAP" section, NCP2704 allows separated volume control for Loudspeaker.

| D7* | D6* | D5 | D4 | D3          | D2        | D1 | D0 |

|-----|-----|----|----|-------------|-----------|----|----|

| х   | x   |    |    | DIGITAL GAI | N CONTROL |    |    |

<sup>\*</sup>D7 and D6 bits can be either 0 or 1. NCP2704 will only process D5 to D0 to address the targeted gain setting.

| D5 | D4 | D3 | D2 | D1 | D0 | Gain (dB) |

|----|----|----|----|----|----|-----------|

| 0  | 0  | 0  | 0  | 0  | 0  | Mute      |

| 0  | 0  | 0  | 0  | 0  | 1  | -60       |

| 0  | 0  | 0  | 0  | 1  | 0  | -54       |

| 0  | 0  | 0  | 0  | 1  | 1  | -48       |

| 0  | 0  | 0  | 1  | 0  | 0  | -45       |

| 0  | 0  | 0  | 1  | 0  | 1  | -42       |

| 0  | 0  | 0  | 1  | 1  | 0  | -39       |

| 0  | 0  | 0  | 1  | 1  | 1  | -36       |

| 0  | 0  | 1  | 0  | 0  | 0  | -34       |

| 0  | 0  | 1  | 0  | 0  | 1  | -32       |

| 0  | 0  | 1  | 0  | 1  | 0  | -30       |

| 0  | 0  | 1  | 0  | 1  | 1  | -28       |

| 0  | 0  | 1  | 1  | 0  | 0  | -27       |

| 0  | 0  | 1  | 1  | 0  | 1  | -26       |

| 0  | 0  | 1  | 1  | 1  | 0  | -25       |

| 0  | 0  | 1  | 1  | 1  | 1  | -24       |

| 0  | 1  | 0  | 0  | 0  | 0  | -23       |

| 0  | 1  | 0  | 0  | 0  | 1  | -22       |

| D5 | D4 | D3 | D2 | D1 | D0 | Gain (dB) |

|----|----|----|----|----|----|-----------|

| 0  | 1  | 0  | 0  | 1  | 0  | -21       |

| 0  | 1  | 0  | 0  | 1  | 1  | -20       |

| 0  | 1  | 0  | 1  | 0  | 0  | -19       |

| 0  | 1  | 0  | 1  | 0  | 1  | -18       |

| 0  | 1  | 0  | 1  | 1  | 0  | -17       |

| 0  | 1  | 0  | 1  | 1  | 1  | -16       |

| 0  | 1  | 1  | 0  | 0  | 0  | -15       |

| 0  | 1  | 1  | 0  | 0  | 1  | -14       |

| 0  | 1  | 1  | 0  | 1  | 0  | -13       |

| 0  | 1  | 1  | 0  | 1  | 1  | -12       |

| 0  | 1  | 1  | 1  | 0  | 0  | -11       |

| 0  | 1  | 1  | 1  | 0  | 1  | -10       |

| 0  | 1  | 1  | 1  | 1  | 0  | -9        |

| 0  | 1  | 1  | 1  | 1  | 1  | -8        |

| 1  | 0  | 0  | 0  | 0  | 0  | -7        |

| 1  | 0  | 0  | 0  | 0  | 1  | -6        |

| 1  | 0  | 0  | 0  | 1  | 0  | -5        |

| 1  | 0  | 0  | 0  | 1  | 1  | -4        |

| 1  | 0  | 0  | 1  | 0  | 0  | -3        |

| 1  | 0  | 0  | 1  | 0  | 1  | -2        |

| 1  | 0  | 0  | 1  | 1  | 0  | -1        |

| 1  | 0  | 0  | 1  | 1  | 1  | 0         |

| 1  | 0  | 1  | 0  | 0  | 0  | +1        |

| 1  | 0  | 1  | 0  | 0  | 1  | +2        |

| 1  | 0  | 1  | 0  | 1  | 0  | +3        |

| 1  | 0  | 1  | 0  | 1  | 1  | +4        |

| 1  | 0  | 1  | 1  | 0  | 0  | +5        |

| 1  | 0  | 1  | 1  | 0  | 1  | +6        |

| 1  | 0  | 1  | 1  | 1  | 0  | +7        |

| 1  | 0  | 1  | 1  | 1  | 1  | +8        |

| 1  | 1  | 0  | 0  | 0  | 0  | +9        |

| 1  | 1  | 0  | 0  | 0  | 1  | +10       |

| 1  | 1  | 0  | 0  | 1  | 0  | +11       |

| 1  | 1  | 0  | 0  | 1  | 1  | +12       |

As described above, an additional gain setting is possible in the "INPUT CONTROL" register. Thus, final gain setting can go up to  $44\ dB$  for the signal applied on the IN1 and IN2 input.

#### **OUTPUT CONTROL**

The NCP2704 embeds one class D loudspeaker amplifier and a true ground headset stereo amplifier (Left and Right). The "INPUT CONTROL" register has defined the Input 1 and 2 configuration (single-ended or differential). The last stage of the audio subsystem defines which between IN1A, IN1B, IN2A, IN2B or a combination is applied to each amplifier.

| D7 | D6    | D5  | D4   | D3          | D2 | D1 | D0 |  |

|----|-------|-----|------|-------------|----|----|----|--|

| x  | Reset | /SD | Slow | Output Mode |    |    |    |  |

#### **POWER ON RESET CONDITIONS**

| D6 | RESET                                            |

|----|--------------------------------------------------|

| 0  | No I <sup>2</sup> C Register Change              |

| 1  | I <sup>2</sup> C Register in Reset Configuration |

The **RESET** function can be set by driving D6 bit to high Level. In that case, all registers are set in the following configuration.

|                                         | Reset Configuration |    |    |    |    |    |    |    |  |

|-----------------------------------------|---------------------|----|----|----|----|----|----|----|--|

| Registers                               | D7                  | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| Input control                           | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Headset right volume control            | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Headset left volume control             | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Loudspeaker volume control              | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Output control                          | 0                   | 0  | х  | 0  | 0  | 0  | 0  | 0  |  |

| LDO control                             | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Status                                  | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |

| AGC control register                    | 0                   | 0  | 1  | 1  | 1  | 1  | 1  | 1  |  |

| AGC configuration register Attack time  | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |

| AGC configuration register Release time | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |

| AGC configuration register Hold time    | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| EMI control                             | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

#### **Reset Functionality and Default State**

Reset configuration will be effective in three different application cases:

- POR: As soon as power supply is detected by NCP2704, all the registers are set in the default configuration.

- RESET bit: It can be done in the Mode control register by setting D6 bit (RESET) to 1. Then Mode Control and Gain Control registers are set in their default state. Once done, RESET bit goes back to 0.

# • RESET Threshold:

When PV<sub>DD</sub> decreases and goes below UVLO threshold (2.2 V), the amplifiers enter in shutdown mode. When PV<sub>DD</sub> goes over UVLO + Hysteresis the amplifiers turn on with the previous configuration.  When HSV<sub>DD</sub> decreases and goes below UVLO threshold (1.3 V), the amplifiers enter in shutdown mode. When HSV<sub>DD</sub> goes over UVLO + Hysteresis the amplifiers turn on with the previous configuration.

#### Shutdown functionality

NCP2704 has an internal software shutdown through bit D5 of the Output control register.

- Software Shutdown: When a software shutdown occurs through D5 bit in the "Output control" register (D5 = 0), the device enter in a low power shutdown mode. In addition all the registers are set in their default state.

- Gain modifications setting

When bit D4 = 0 (default state), volume changes step by step. In this case  $T_{on}$  and  $T_{off}$  = 32 ms and pop and click noise is reduced. When bit D4 = 1,  $T_{on}$  and  $T_{off}$  = 1 ms.

# **OUTPUT CONFIGURATION**

| Conf |    | OUTPUT | MODE 0 |    | OUTPUT CONF                  | IGURATION with IN10 | C = IN2C = 0  |

|------|----|--------|--------|----|------------------------------|---------------------|---------------|

| N°   | D3 | D2     | D1     | D0 | Loudspeaker                  | Left Headset        | Right Headset |

| 0    | 0  | 0      | 0      | 0  | SD                           | SD                  | SD            |

| 1    | 0  | 0      | 0      | 1  | IN1A + IN1B                  | SD                  | SD            |

| 2    | 0  | 0      | 1      | 0  | SD                           | IN1A                | IN1B          |

| 3    | 0  | 0      | 1      | 1  | IN1A + IN1B                  | IN1A                | IN1B          |

| 4    | 0  | 1      | 0      | 0  | IN2A + IN2B                  | SD                  | SD            |

| 5    | 0  | 1      | 0      | 1  | SD                           | IN2A                | IN2B          |

| 6    | 0  | 1      | 1      | 0  | IN2A + IN2B                  | IN2A                | IN2B          |

| 7    | 0  | 1      | 1      | 1  | IN1A + IN1B + IN2A +<br>IN2B | SD                  | SD            |

| 8    | 1  | 0      | 0      | 0  | SD                           | IN1A + IN2A         | IN1B + IN2B   |

| 9    | 1  | 0      | 0      | 1  | IN1A + IN1B + IN2A +<br>IN2B | IN1A + IN2A         | IN1B + IN2B   |

| 10   | 1  | 0      | 1      | 0  | IN1A + IN1B                  | IN2A                | IN2B          |

| 11   | 1  | 0      | 1      | 1  | IN2A + IN2B                  | IN1A                | IN1B          |

| 12   | 1  | 1      | 0      | 0  | SD                           | SD                  | SD            |

| 13   | 1  | 1      | 0      | 1  | SD                           | SD                  | SD            |

| 14   | 1  | 1      | 1      | 0  | SD                           | SD                  | SD            |

| 15   | 1  | 1      | 1      | 1  | SD                           | SD                  | SD            |

| Conf |    | OUTPUT | MODE 1 |    | OUTPUT CONF         | FIGURATION with IN10 | S = IN2C = 1        |

|------|----|--------|--------|----|---------------------|----------------------|---------------------|

| N°   | D3 | D2     | D1     | D0 | Loudspeaker         | Left Headset         | Right Headset       |

| 0    | 0  | 0      | 0      | 0  | SD                  | SD                   | SD                  |

| 1    | 0  | 0      | 0      | 1  | IN1_Diff            | SD                   | SD                  |

| 2    | 0  | 0      | 1      | 0  | SD                  | IN1_Diff             | IN1_Diff            |

| 3    | 0  | 0      | 1      | 1  | IN1_Diff            | IN1_Diff             | IN1_Diff            |

| 4    | 0  | 1      | 0      | 0  | IN2_Diff            | SD                   | SD                  |

| 5    | 0  | 1      | 0      | 1  | SD                  | IN2_Diff             | IN2_Diff            |

| 6    | 0  | 1      | 1      | 0  | IN2_Diff            | IN2_Diff             | IN2_Diff            |

| 7    | 0  | 1      | 1      | 1  | IN1_Diff + IN2_Diff | SD                   | SD                  |

| 8    | 1  | 0      | 0      | 0  | SD                  | IN1_Diff + IN2_Diff  | IN1_Diff + IN2_Diff |

| 9    | 1  | 0      | 0      | 1  | IN1_Diff + IN2_Diff | IN1_Diff + IN2_Diff  | IN1_Diff + IN2_Diff |

| 10   | 1  | 0      | 1      | 0  | IN1_Diff            | IN2_Diff             | IN2_Diff            |

| 11   | 1  | 0      | 1      | 1  | IN2_Diff            | IN1_Diff             | IN1_Diff            |

| 12   | 1  | 1      | 0      | 0  | SD                  | SD                   | SD                  |

| 13   | 1  | 1      | 0      | 1  | SD                  | SD                   | SD                  |

| 14   | 1  | 1      | 1      | 0  | SD                  | SD                   | SD                  |

| 15   | 1  | 1      | 1      | 1  | SD                  | SD                   | SD                  |

| Conf |    | OUTPUT | MODE 2 |    | OUTPUT CONFIG | URATION with IN1C = | 1 and IN2C = 0 |

|------|----|--------|--------|----|---------------|---------------------|----------------|

| N°   | D3 | D2     | D1     | D0 | Loudspeaker   | Left Headset        | Right Headset  |

| 0    | 0  | 0      | 0      | 0  | SD            | SD                  | SD             |

| 1    | 0  | 0      | 0      | 1  | IN1_Diff      | SD                  | SD             |

| 2    | 0  | 0      | 1      | 0  | SD            | IN1_Diff            | IN1_Diff       |

| 3    | 0  | 0      | 1      | 1  | IN1_Diff      | IN1_Diff            | IN1_Diff       |

| 4    | 0  | 1      | 0      | 0  | IN2A + IN2B   | SD                  | SD             |

| 5    | 0  | 1      | 0      | 1  | SD            | IN2A                | IN2B           |

| 6    | 0  | 1      | 1      | 0  | IN2A + IN2B   | IN2A                | IN2B           |

| 7    | 0  | 1      | 1      | 1  | SD            | SD                  | SD             |

| 8    | 1  | 0      | 0      | 0  | SD            | SD                  | SD             |

| 9    | 1  | 0      | 0      | 1  | SD            | SD                  | SD             |

| 10   | 1  | 0      | 1      | 0  | IN1_Diff      | IN2A                | IN2B           |

| 11   | 1  | 0      | 1      | 1  | IN2A + IN2B   | IN1_Diff            | IN1_Diff       |

| 12   | 1  | 1      | 0      | 0  | SD            | SD                  | SD             |

| 13   | 1  | 1      | 0      | 1  | SD            | SD                  | SD             |

| 14   | 1  | 1      | 1      | 0  | SD            | SD                  | SD             |

| 15   | 1  | 1      | 1      | 1  | SD            | SD                  | SD             |

| Conf |    | OUTPUT | MODE 3 |    | OUTPUT CONFIGURATION with IN1C = 0 and IN2C = 1 |              |               |  |

|------|----|--------|--------|----|-------------------------------------------------|--------------|---------------|--|

| N°   | D3 | D2     | D1     | D0 | Loudspeaker                                     | Left Headset | Right Headset |  |

| 0    | 0  | 0      | 0      | 0  | SD                                              | SD           | SD            |  |

| 1    | 0  | 0      | 0      | 1  | IN1A + IN1B                                     | SD           | SD            |  |

| 2    | 0  | 0      | 1      | 0  | SD                                              | IN1A         | IN1B          |  |

| 3    | 0  | 0      | 1      | 1  | IN1A + IN1B                                     | IN1A         | IN1B          |  |

| 4    | 0  | 1      | 0      | 0  | IN2_Diff                                        | SD           | SD            |  |

| 5    | 0  | 1      | 0      | 1  | SD                                              | IN2_Diff     | IN2_Diff      |  |

| 6    | 0  | 1      | 1      | 0  | IN2_Diff                                        | IN2_Diff     | IN2_Diff      |  |

| 7    | 0  | 1      | 1      | 1  | SD                                              | SD           | SD            |  |

| 8    | 1  | 0      | 0      | 0  | SD                                              | SD           | SD            |  |

| 9    | 1  | 0      | 0      | 1  | SD                                              | SD           | SD            |  |

| 10   | 1  | 0      | 1      | 0  | IN1A + IN1B                                     | IN2_Diff     | IN2_Diff      |  |

| 11   | 1  | 0      | 1      | 1  | IN2_Diff                                        | IN1A         | IN1B          |  |

| 12   | 1  | 1      | 0      | 0  | SD                                              | SD           | SD            |  |

| 13   | 1  | 1      | 0      | 1  | SD                                              | SD           | SD            |  |

| 14   | 1  | 1      | 1      | 0  | SD                                              | SD           | SD            |  |

| 15   | 1  | 1      | 1      | 1  | SD                                              | SD           | SD            |  |

#### AGC CONTROL

The AGC function is to protect the speaker from damage due to exceeded output power. The function limits the output power without deteriorating the audio quality.

# AGC CONTROL REGISTER (ACNT)

This register allows controlling the AGC setup.

| D7   | D6   | D5     | D4     | D3     | D2     | D1     | D0     |      |

|------|------|--------|--------|--------|--------|--------|--------|------|

| AGCE | NC/L | PWR(2) | PWR(1) | PWR(0) | THD(2) | THD(1) | THD(0) | ACNT |

THD(2-0): Define the maximum distortion level acceptable in non-clipping mode.

| THD Bit | Maximum THDN level |

|---------|--------------------|

| 000     | 1%                 |

| 001     | 2%                 |

| 010     | 4%                 |

| 011     | 6%                 |

| 100     | 8%                 |

| 101     | 10%                |

| 110     | 15%                |

| 111     | 20%                |

PWR(2-0): Define the maximum peak voltage in output of the amplifier in case of limiter mode.

| PWR Bit | V <sub>peakmax</sub> (V) |

|---------|--------------------------|

| 000     | 0.5                      |

| 001     | 1                        |

| 010     | 1.5                      |

| 011     | 2                        |

| 100     | 2.5                      |

| 101     | 3                        |

| 110     | 3.5                      |

| 111     | 4                        |

NC/L: Non-clipping mode and limiter mode selection bit.

- 0 = Non-clipping mode.

- 1 = Limiter mode.

AGCE: Activate or disable the AGC function bit.

- 0 = AGC disable.

- 1 = AGC enable.

# AGC CONFIGURATION REGISTER (ACONFA-ACONFR-ACONFH)

This register controls the AGC configuration.

| D7* | D6* | D5   | D4   | D3   | D2   | D1   | D0   |        |

|-----|-----|------|------|------|------|------|------|--------|

| ×   | х   | A(5) | A(4) | A(3) | A(2) | A(1) | A(0) | ACONFA |

| ×   | х   | R(5) | R(4) | R(3) | R(2) | R(1) | R(0) | ACONFR |

| х   | х   | H(5) | H(4) | H(3) | H(2) | H(1) | H(0) | ACONFH |

A(5-0): Define the attack time.

| A(5-0) | ms/0.5 dB     | ms/6 dB |

|--------|---------------|---------|

| 00000  | Class D clock |         |

| 00001  | 0.1067        | 1.28    |

| 00010  | 0.2134        | 2.56    |

| 00011  | 0.3201        | 3.84    |

|        | 0.1067ms/step |         |

| 11111  | 6.722         | 80.66   |

Attack time is defined as the minimum time between two gain decrease.

R(5-0): Define the release time.

| R(5-0) | s/0.5 dB      | s/6 dB |

|--------|---------------|--------|

| 00000  | Class D clock |        |

| 00001  | 0.0137        | 0.1644 |

| 00010  | 0.0274        | 0.3288 |

| 00011  | 0.0411        | 0.4932 |

|        | 0.0137s/step  |        |

| 11111  | 0.8631        | 10.36  |

Release time is defined as the minimum time between two gain increase.

H(5-0): Define the hold time.

| H(5-0) | Timer Hold (s) |

|--------|----------------|

| 00000  | Hold time off  |

| 00001  | 0.0137         |

| 00010  | 0.0274         |

| 00011  | 0.0411         |

|        | 0.0137s/step   |

| 11111  | 0.8631         |

Hold time is defined as the minimum time between a gain increase after a gain decrease.

#### **EMI CONTROL**

The EMI control register sets the rising and falling edges of the Class D speaker outputs. This register gives the possibility to the user to have the best efficiency by choosing the lowest value, or reduce the EMI perturbation by increasing it. By default the programming value sets the fastest time to have the best efficiency.

| D7 | D6 | D5 | D4 | D3          | D2 | D1 | D0 |

|----|----|----|----|-------------|----|----|----|

| Х  | х  | х  | х  | EMI Control |    |    |    |

| D3 | D2 | D1 | D0 | Value t <sub>r</sub> and t <sub>f</sub> (ns) |

|----|----|----|----|----------------------------------------------|

| 0  | 0  | 0  | 0  | 20                                           |

| 0  | 0  | 0  | 1  | 15                                           |

| 0  | 0  | 1  | 0  | 10                                           |

| 0  | 0  | 1  | 1  | 5                                            |

| 0  | 1  | 0  | 0  | 1                                            |

| 0  | 1  | 0  | 1  | Reserved                                     |

| 0  | 1  | 1  | 0  | Reserved                                     |

| 0  | 1  | 1  | 1  | Reserved                                     |

| 1  | 0  | 0  | 0  | Reserved                                     |

| 1  | 0  | 0  | 1  | Reserved                                     |

| 1  | 0  | 1  | 0  | Reserved                                     |

| 1  | 0  | 1  | 1  | Reserved                                     |

| 1  | 1  | 0  | 0  | Reserved                                     |

| 1  | 1  | 0  | 1  | Reserved                                     |

| 1  | 1  | 1  | 0  | Reserved                                     |

| 1  | 1  | 1  | 1  | Reserved                                     |

# **HEADSET SUPPLY VOLTAGE AND LDO SETTING**

Apply a supply voltage from 1.6~V to 3.6~V to the pin  $HPV_{DD}$ . The internal signal VRP and VRM will be the output of an internal converter set by the LDO control register.

| D7 | D6 | D5 | D4 | D3                  | D2 | D1 | D0 |

|----|----|----|----|---------------------|----|----|----|

| х  | х  | х  | х  | Internal LDO Output |    |    |    |

The LDO control register bits (D3 to D0) set VRP and VRM.

| D3 | D2 | D1 | D0 | Internal LDO Output<br>V <sub>peak</sub> |

|----|----|----|----|------------------------------------------|

| 0  | 0  | 0  | 0  | 1.3                                      |

| 0  | 0  | 0  | 1  | 1.4                                      |

| 0  | 0  | 1  | 0  | 1.5                                      |

| 0  | 0  | 1  | 1  | 1.6                                      |

| 0  | 1  | 0  | 0  | 1.7                                      |

| 0  | 1  | 0  | 1  | 1.8                                      |

| 0  | 1  | 1  | 0  | 1.9                                      |

| 0  | 1  | 1  | 1  | 2.0                                      |

| 1  | 0  | 0  | 0  | 2.1                                      |

| 1  | 0  | 0  | 1  | 2.2                                      |

| 1  | 0  | 1  | 0  | 2.3                                      |

| D3 | D2 | D1 | D0 | Internal LDO Output<br>V <sub>peak</sub> |

|----|----|----|----|------------------------------------------|

| 1  | 0  | 1  | 1  | 2.4                                      |

| 1  | 1  | 0  | 0  | 2.5                                      |

| 1  | 1  | 0  | 1  | 2.6                                      |

| 1  | 1  | 1  | 0  | 2.7                                      |

| 1  | 1  | 1  | 1  | 2.8                                      |

This function helps to increase the output dynamic when external damping resistors are used.

#### **STATUS REGISTER**

This register gives the status of the fault which can occur in the NCP2704.

| D7 | D6 | D5    | D4     | D3     | D2     | D1     | D0 |

|----|----|-------|--------|--------|--------|--------|----|

| х  | x  | WSLDO | SC_LPP | SC_LPN | SC_HSL | SC_HSR | х  |

**D1**: This bit indicates that the current limitation of the pin HSR is activated (D1 = 1). It is automatically reset to 0 when the fault disappears.

**D2**: This bit indicates that the current limitation of the pin HSL is activated (D2 = 1). It is automatically reset to 0 when the fault disappears.

**D3**: This bit indicates that the current limitation of the pin LPN is activated (D3 = 1). It is automatically reset to 0 when the fault disappears.

**D4**: This bit indicates that the current limitation of the pin LPP is activated (D4 = 1). It is automatically reset to 0 when the fault disappears.

**D5**: This bit indicates that a wrong setting on the LDO control register has been done. This fault occurs when LDO setting >  $HSV_{DD} - 200 \text{ mV}$ . It is automatically reset to 0 when the fault disappears.

#### **Components Selection**

#### Input Capacitor Selection

The input coupling capacitor blocs the DC voltage at the amplifier input. This capacitor creates a high–pass filter with  $R_{in}$  (20 k $\Omega$ ).

The size of the capacitor must be large enough to couple in low frequencies without severe attenuation in the audio bandwith (20 Hz - 20 kHz).

The cut off frequency for the input high-pass filter is :  $F_c = 1 / (2\eta R_{in}C_{in})$ .

#### Charge Pump Capacitor Selection

Use ceramic capacitor with low ESR for better performances. X5R / X7R capacitor is recommended.

The flying capacitor serves to transfer charge during the generation of the negative voltage. Connect CFly as close as possible to CPP and CPM.

The PVM capacitor must be equal at least to the CFly capacitor to allow maximum transfer charge. Connect CPVM as close as possible to the PVM pin.

A value of 1 µF is recommended.

The following table suggests typical value and manufacturer:

| Value | Reference        | Package | Manufacturer |

|-------|------------------|---------|--------------|

| 1 μF  | C1005X5R0J105K   | 0402    | TDK          |

| 1 μF  | GRM155R60J105K16 | 0402    | Murata       |

Lower value of capacitors can be used but the maximum output power is reduced and the device may not operate to specifications.

# Long Play True Ground Headphone Power Supply Decoupling Capacitor

The headphone amplifier requires the adequate decoupling capacitor in order to guarantee the best operation in terms of audio performances. Use X5R / X7R ceramic capacitor and place it close to the HSVDD pin. A value of 1  $\mu$ F is recommended.

#### Class D Power Supply Decoupling Capacitor

The Class D amplifier requires an adequate decoupling amplifier in order to guarantee the best operation in terms of audio performances. Use X5R / X7R ceramic capacitor and place it close to PVDD pin in order to reduce high frequency transient spikes due to parasitic inductance. A value of  $4.7 \, \mu F$  is recommended.

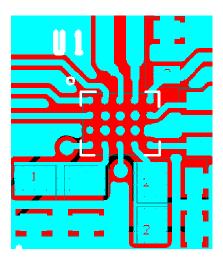

#### **Layout Recommendations**

For efficiency, noise and EMI standpoints, it is strongly recommended to use a power and ground plane in order to reduce parasitic resistance and inductance.

For the same reason, it is strongly recommended for the Class D amplifier to keep the output traces short and well shielded in order to avoid them acting as an antenna.

Route audio signal (input pins and HSL / HSR) far from HSVDD, CPP, CPM, PVM, PVDD, LPP, and LPN to avoid any perturbation due to the switching.

Figure 27. PCB Layout Example

#### **ORDERING INFORMATION**

| Device        | Package                                | Shipping <sup>†</sup> |  |

|---------------|----------------------------------------|-----------------------|--|

| NCP2704FCCT1G | CSP - 20 - 2.5 x 2.0 mm<br>(Pb - Free) | 3000 / Tape & Reel    |  |

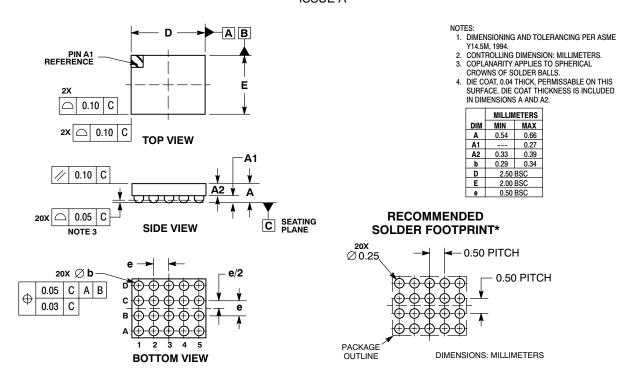

#### PACKAGE DIMENSIONS

# **20 PIN FLIP-CHIP, 2.5x2.0, 0.5P**CASE 499BH-01 ISSUE A

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and lill are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT: