FAIL-SAFE THROUGH INNOVATION

# SD705/ SD706/ SD707/ SD708 – INERTIAL MODULE SINGLE AXIS IN PLANE OR OUT OF PLANE GYROSCOPE PRODUCT DATASHEET

Date: 01.10.2010

Revision: 1.9

TYP Micro-machined Integrated Inertial Module with Single Axis In-

Plane or Out-of-Plane Gyroscope

DEVICE NAME SD705 / SD706/ SD707/ SD708

PACKAGE QFN 40, 6x6mm

© 2010. Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

Any enquiries relating to this document or its contents should be addressed in the first instance to:

SensorDynamics AG Schloß Eybesfeld 1e 8403 Graz-Lebring. Austria.

Tel I +43-(0)3182-40160 Fax I +43-(0) 3182-40160-70 Mail I info@sensordynamics.cc

#### **APPLICATIONS**

The high performance level, mechanical robustness and the wide operating temperature range make the SD70x Inertial Module best suitable for several applications like:

- Navigational systems

- Platform stabilization

- High end toys (e.g. helicopters)

- Image stabilization

- Motion control

#### **FEATURES**

- Tiny QFN40 package of only 6x6x2 mm<sup>3</sup>

- Temperature operating range -40°C to +85°C

- Fully calibrated over the whole operating temperature range

- Continuously working self diagnosis

- Sensitive gyroscope axis either in-plane or out-of-plane

- Simultaneously two measurement ranges of ±100°/s and ±300°/s

- Provide over range up to ±128°/s and ±512°/s, respectively

- Available as 3.3V or 5V version

#### **GENERAL DESCRIPTION**

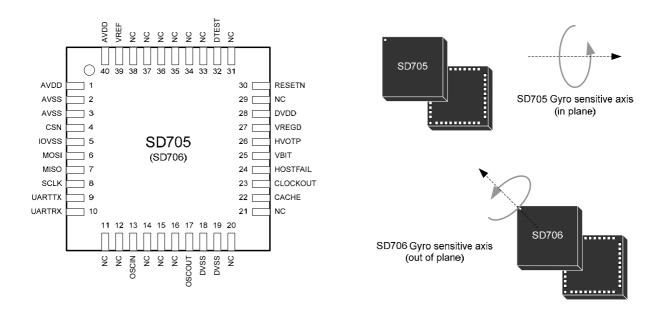

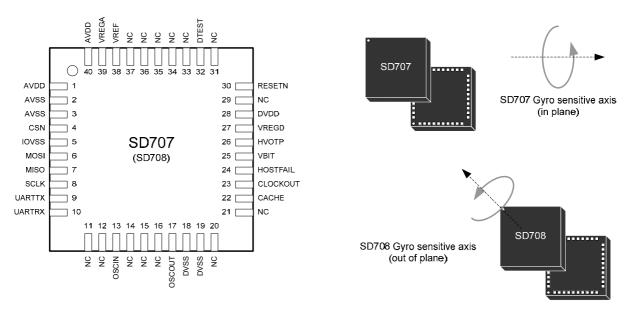

The SD70x module integrates a high performance sensor element and a mixed signal ASIC within a 40 pins QFN plastic package. The SD705 and SD707 are sensitive to in plane angular velocities (parallel to the PCB, X-axis), while the SD706 and SD708 are sensitive to out of plane angular velocities (perpendicular to the PCB, Z-axis). The SD705 and SD706 are for 3.3V operation and the SD707 and SD708 for 5V operation.

| PART NAME | GYROSCOPE AXIS | SUPPLY VOLTAGE |

|-----------|----------------|----------------|

| SD705     | Χ              | 3.3V           |

| SD706     | Z              | 3.3V           |

| SD707     | Χ              | 5V             |

| SD708     | Z              | 5V             |

The sensor element is manufactured in a surface micromachining process and encapsulated in a first level packaging technique. The sensor module provides a digital rate output via an integrated serial peripheral interface (SPI).

The SD70x is designed to provide a high signal-to-noise ratio with excellent performance over temperature. Two measurement ranges are available simultaneously: ±128 °/sec with 10Hz bandwidth and ±512 °/sec with 75Hz bandwidth.

The micro-machined gyroscope element exploits the principle of the Coriolis Effect and a capacitive-based sensing system. Rotation of the sensor around the sensitive axis causes a secondary movement of an oscillating silicon structure resulting in a capacitance change. The ASIC detects and transforms these changes in capacitance into a digital output signal, which is proportional to the angular rate.

The inertial module comes fully calibrated with the calibration data stored in non-volatile memory.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

#### **CONTENTS**

| 1. | Gen          | eraleral                              | 7   |

|----|--------------|---------------------------------------|-----|

|    | 1.1.         | Absolute Maximum Ratings              | . 7 |

|    | 1.2.         | Normal Operating Range                | . 7 |

|    | 1.3.         | Package                               | . 8 |

|    | 1.4.         | Marking                               | . 9 |

|    | 1.5.         | Reflow Solder Profile                 | 10  |

|    | 1.6.         | Self Diagnosis Concept                | 11  |

| 2  | SD7          | 05/SD706 Interface definition         | 12  |

|    | 2.1.         | Pin Description                       |     |

|    | 2.2.         | Application Circuit                   |     |

|    |              |                                       |     |

| 3. |              | 07/8 Interface definition             |     |

|    | 3.1.         | Pin Description                       |     |

|    | 3.2.         | Application Circuit                   | 18  |

| 4. | Cloc         | k source                              | 20  |

|    | 4.1.         | General                               | 20  |

|    | 4.2.         | Internal oscillator circuit schematic | 20  |

| 5. | Elec         | trical and Physical Characteristics   | 21  |

|    | 5.1.         | Operation and performance parameters  |     |

| 6. | CDL          |                                       |     |

|    | 6.1.         | Communication                         |     |

|    | 6.2.         |                                       |     |

|    | 6.2.<br>6.3. | ReadRate Opcode (0x01)                |     |

|    | 6.4.         | ReadStatus Opcode (0x02)              |     |

|    |              | AsicOperation Opcode (0x0B)           |     |

|    | 6.5.         | ReadDiagBuf Opcode (0x0D)             |     |

|    | 6.6.         | SPI commands types                    |     |

|    | 6.8.         | CRC SPI Phase and Palarity            |     |

|    | 6.9.         | SPI Phase and Polarity                |     |

|    | 6.10.        | SPI Timing specification              | 59  |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## 1. General

# 1.1. Absolute Maximum Ratings

Stress levels exceeding the values listed here may cause permanent damage to the device.

**Environmental Specification**

| PARAMETER                                | MIN  | MAX  | UNIT | CONDITION      |

|------------------------------------------|------|------|------|----------------|

| SD705, SD706 Supply Voltage              | -0.5 | 4.6  | V    |                |

| SD707, SD708 Supply Voltage              | -0.5 | 6.0  |      |                |

| Storage temperature                      | -40  | 125  | ° C  |                |

| Package Drop Survival (AEC-Q100)         |      | 1.2  | m    | unpowered      |

| SD705, SD707 Mechanical shock survival** |      | 2000 | g    | unpowered      |

| half sine according JESD22-B104C         |      | 1500 | g    | powered        |

| SD706, SD708 Mechanical shock survival** |      | TBD  | g    | unpowered      |

| half sine according JESD22-B104C         |      | TBD  | g    | powered        |

| ESD*                                     | 2    |      | kV   | HBM at any pin |

<sup>\*</sup> The SD70x Inertial module is rated to 2kV using the Human Body Model (HBM). Although this product features patented or proprietary protection circuitry against electrostatic discharge (ESD) damage may occur if devices are subjected to high-energy ESD pulses. Therefore, proper precaution has to be taken to avoid performance degradation or loss of functionality.

<sup>\*\*</sup> Drops onto hard surfaces can cause shocks of greater than 2000g and exceed the absolute maximum rating of the device. Care should be exercised in handling to avoid damage.

# 1.2. Normal Operating Range

The operation range specifies the electrical and environmental conditions of operation where all specified characteristics have to be fulfilled.

**Environmental Specification**

| PARAMETER                       | MIN | MAX | UNIT      | CONDITION |

|---------------------------------|-----|-----|-----------|-----------|

| Ambient temperature             | -40 | 85  | ° C       |           |

| Ambient temperature change rate | -5  | 5   | ° C / min |           |

The minimum operational Lifetime is 17 000 h in powered state, the total Lifetime is minimum 17 years.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

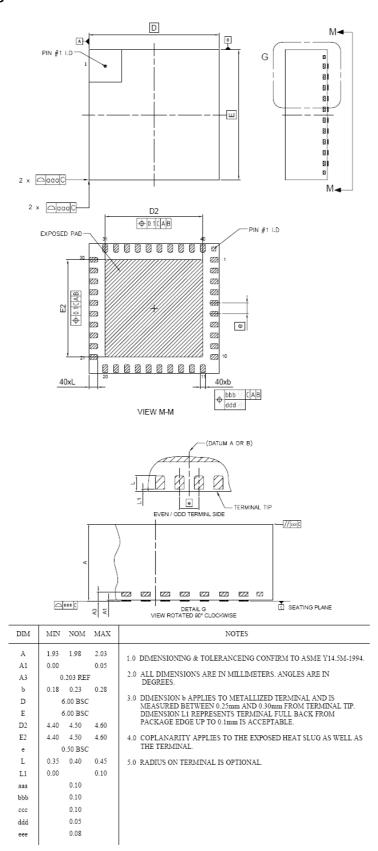

# 1.3. Package

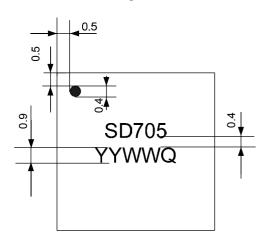

# 1.4. Marking

Drawing 1: dimensions and positioning of the marking in mm

| FIELD                  | LINE | DIGITS | FIELD DESCRIPTION          | MARKING                          |

|------------------------|------|--------|----------------------------|----------------------------------|

| •                      |      |        | Pin 1 indicator            |                                  |

| Product No.<br>(SDabc) | 1    | 5      | SensorDynamics Product No. | SD705<br>SD706<br>SD707<br>SD708 |

| Date code              | 2    | 4      | Date Code YYWW             | [YYWW]                           |

| Manufacturer           | 2    | 1      | Manufacturer code          |                                  |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

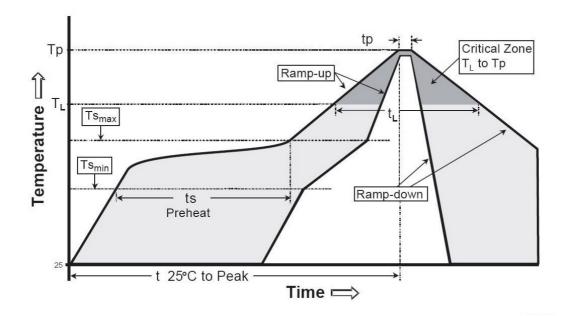

## 1.5. Reflow Solder Profile

Packaging concept, technology and materials are selected to allow for up to three solder cycles according to lead free solder profile with peak temperature of +245 °C, as described in the figure and tables below.

| PROFILE FEATURES                                  | VALUE / CONDITION |

|---------------------------------------------------|-------------------|

| Profile type                                      | Pb-free assembly  |

| Average Rump-Up rate (Ts <sub>max</sub> to Tp)    | max 3 °C/s        |

| Preheat                                           |                   |

| Temperature min (Tsmin)                           | 150 °C            |

| Temperature max (Ts <sub>max</sub> )              | 200 °C            |

| Time (ts)                                         | 60-180 s          |

| Time maintained above:                            |                   |

| Temperature min (T <sub>L</sub> )                 | 217 °C            |

| Time (t <sub>L</sub> )                            | 60-150 s          |

| peak temperature                                  |                   |

| Peak/classification temperature (Tp)              | 245°C             |

| time within 5°C from actual peak temperature (tp) | 20-40 s           |

| time above T <sub>solidus</sub> (min. 217 °C)     | min. 90 s         |

| Cooling                                           |                   |

| ramp-down rate                                    | max 6 °C/s        |

| General                                           |                   |

| time 25 °C to peak temperature                    | max. 480 s        |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

# 1.6. Self Diagnosis Concept

The inertial module accomplishes a continuously working self diagnosis of the gyroscope. There is no need to switch to a certain diagnosis mode. If a failure of the gyroscope is detected a dedicated status flag (BIT\_N, see section 6.1.2) in the measurement data telegram is set to "1". If the failure is just temporary, e.g. due to a mechanical shock, the BIT\_N is reset to "0" automatically. If the BIT\_N remains "1" even after resetting the sensor a permanent damage must be considered.

# 2. SD705/SD706 Interface definition

# 2.1. Pin Description

The pin out includes digital/analog supply and ground, digital inputs and outputs for data and test signals. The following schematic depicts the pin assignment of the QFN package.

Fig. 2: Pin out of SD705/6 inertial module in QFN package

The pins are assigned according to the following table:

| PIN    | TYPE | NAME     | NOTES                                               |

|--------|------|----------|-----------------------------------------------------|

| 1      | S    | AVDD     | 3.3V analog power supply                            |

| 2, 3   | G    | AVSS     | analog ground                                       |

| 4      | 1    | CSN      | SPI interface (Chip Select, active low)             |

| 5      | G    | IOVSS    | IO ground                                           |

| 6      | I    | MOSI     | SPI interface (Master Output Slave Input)           |

| 7      | 0    | MISO     | SPI interface (Master Input Slave Output)           |

| 8      | I    | SCLK     | SPI interface (Spi Clock)                           |

| 9      | 0    | UARTTX   | Reserved                                            |

| 10     | 1    | UARTRX   | Reserved                                            |

| 11, 12 | NC   | NC       | not connected                                       |

| 13     | I, A | OSCIN    | Ext. quartz connection or ext. clock input          |

| 14-16  | NC   | NC       | not connected                                       |

| 17     | Α    | OSCOUT   | Ext. quartz connection                              |

| 18, 19 | G    | DVSS     | digital ground                                      |

| 20, 21 | NC   | NC       | not connected                                       |

| 22     | I/O  | CACHE    | Reserved                                            |

| 23     | 0    | CLOCKOUT | Clock output (for driving other components)         |

| 24     | 0    | HOSTFAIL | Alarm for handshaking with host                     |

| 25     | 0    | BIT      | Built In Test ("high" means all ok)                 |

| 26     | S    | HVOTP    | Embedded OTP power supply                           |

| 27     | Α    | VREGD    | 1.8V regulated voltage, requires 100nF external cap |

© 2010. Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## Leading in micro and wireless sensor products

| 28    | S  | DVDD   | 3.3V digital power supply                             |  |  |  |

|-------|----|--------|-------------------------------------------------------|--|--|--|

| 29    | NC | NC     | not connected                                         |  |  |  |

| 30    | 1  | RESETN | Reset_n (active low)                                  |  |  |  |

| 31    | NC | NC     | not connected                                         |  |  |  |

| 32    | I  | DTEST  | Reserved                                              |  |  |  |

| 33-38 | NC | NC     | not connected                                         |  |  |  |

| 39    | Α  | VREF   | analog voltage reference, requires 100nF external cap |  |  |  |

| 40    | S  | AVDD   | 3.3V analog power supply                              |  |  |  |

#### Legend:

| SYMBOL | DESCRIPTION          |

|--------|----------------------|

| I      | Digital Input        |

| 0      | Digital Output       |

| I/O    | Digital Input/Output |

| Α      | Analog               |

| S      | Supply               |

| G      | Ground               |

| NA     | Not applicable       |

| NC*    | Not connected        |

|        |                      |

<sup>\*</sup> NC pins are not connected internally. They can be modelled as an open circuit.

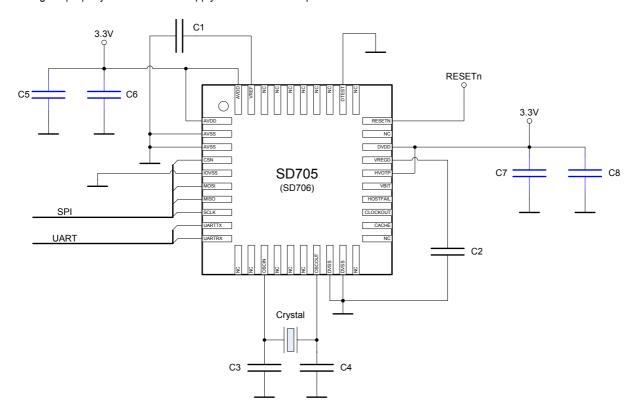

# 2.2. Application Circuit

A few external components are needed as shown in the next picture. The blue capacitors can be omitted if the supply voltage is properly filtered and the supply source has low impedance.

Fig. 3: Application circuit for integrated gyro module SD705/6.

#### **External Components:**

| External | External Components. |         |       |      |                                                                  |  |  |  |  |

|----------|----------------------|---------|-------|------|------------------------------------------------------------------|--|--|--|--|

| #        | TYPE                 | NAME    | VALUE | UNIT | NOTES                                                            |  |  |  |  |

| 1        | Сар                  | C1      | 100   | nF   | Mandatory.                                                       |  |  |  |  |

| 2        | Cap                  | C2      | 100   | nF   | Mandatory.                                                       |  |  |  |  |

| 3        | Cap                  | C3      | 10    | pF   | Board parasitic capacitance on OSCIN should be kept below 1pF    |  |  |  |  |

| 4        | Cap                  | C4      | 10    | pF   | Board parasitic capacitance on OSCOUT should be kept below 1pF   |  |  |  |  |

| 5        | Crystal              | CRYSTAL | 12.0  | MHz  | Mandatory. See below for further requirements of quartz crystal. |  |  |  |  |

| 6        | Cap                  | C5      | 100   | nF   | Optional. Required for not stabilized power supplies.            |  |  |  |  |

| 7        | Сар                  | C6      | 470   | pF   | Optional. Required for not stabilized power supplies.            |  |  |  |  |

| 8        | Cap                  | C7      | 470   | pF   | Optional. Required for not stabilized power supplies.            |  |  |  |  |

| 9        | Cap                  | C8      | 100   | nF   | Optional. Required for not stabilized power supplies.            |  |  |  |  |

#### Quartz Crystal Requirements:

| PARAMETER     | MNEMONIC                        | MIN  | TYP  | MAX | UNIT | NOTES                                 |

|---------------|---------------------------------|------|------|-----|------|---------------------------------------|

| ESR           | Equivalent Series<br>Resistance |      |      | 150 | Ω    |                                       |

| Cload         | Load Capacitance                |      | 10   | 15  | pF   |                                       |

| Driving Level | DrvLevel                        |      | 10   |     | μW   |                                       |

| Fres          | Resonant frequency              |      | 12.0 |     | MHz  |                                       |

| FreqTol       | Frequency Tolerance             | -0.3 |      | 0.3 | %    | Maximum over lifetime and temperature |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

#### Digital I/O Requirements:

| Digital if a reduitation. |                                   |      |     |      |                                                     |  |  |  |  |

|---------------------------|-----------------------------------|------|-----|------|-----------------------------------------------------|--|--|--|--|

| PARAM                     | DESCRIPTION                       | MIN  | MAX | UNIT | NOTES                                               |  |  |  |  |

| Vil                       | Digital input low voltage level   | -0.3 | 0.8 | V    |                                                     |  |  |  |  |

| Vih                       | Digital input high voltage level  | 2.0  | 5.5 | V    | 5V tolerant                                         |  |  |  |  |

| Vol                       | Digital output low voltage level  |      | 0.4 | V    | 4mA current for CLOCKOUT, 2mA for the other outputs |  |  |  |  |

| Voh                       | Digital output high voltage level | 2.4  |     | V    | 4mA current for CLOCKOUT, 2mA for the other outputs |  |  |  |  |

#### Pin 23 CLOCKOUT (digital output)

This Pin is by default disabled (high impedance). It can be enabled at end of production line (OTP) to provide the system clock to an external device.

#### Pin 24 Host Failure (digital output)

The Inertial Module contains a digital output (HOSTFAIL) for signalling a failure of the host  $\mu$ C detected by intelligent watchdog procedure between inertial module and host  $\mu$ C. Please contact SensorDynamics for more details on the intelligent watchdog functionality.

#### Pin 25 BIT (digital output)

The Inertial Module contains a digital output (BIT) for signalling an internal failure detected by embedded failsafe checks system. This signal is active low: when BIT voltage is low (Vol) an error is present in the module.

#### Pin 27 VREGD (analog output)

The Inertial Module generates an internally regulated voltage (1.8V) that requires external filtering by a 100nF capacitance.

#### Pin 30 RESETN

RESETN is active low. When RESETN is low (Vil) the device is under reset. When RESETN is high (Vih) the device is in functional mode, if powered.

Case 1: customer application needs to reset the device on demand.

In this case RESETN has to be driven by external device/controller.

Case 2: customer application doesn't need to reset the device on demand.

RESETN can be either connected directly to power supply (3.3V) or pulled-up to 3.3V through dedicated resistor. SD705/6 will be automatically reset by internal POR circuitry at every power-up sequence.

#### Pin 39 VREF (analog output)

The Inertial Module generates an internal voltage reference (1.5V) that requires external filtering by a 100nF capacitance.

# 3. SD707/8 Interface definition

# 3.1. Pin Description

The pin out includes digital/analog supply and ground, digital inputs and outputs for data and test signals. The following schematic depicts the pin assignment of the QFN package.

Fig. 4: Pin out of SD707/8 inertial module in QFN package

The pins are assigned according to the following list:

| PIN    | TYPE | NAME     | NOTES                                               |

|--------|------|----------|-----------------------------------------------------|

| 1      | S    | AVDD     | 3.3V analog power supply                            |

| 2, 3   | G    | AVSS     | analog ground                                       |

| 4      | I    | CSN      | SPI interface (Chip Select, active low)             |

| 5      | G    | IOVSS    | IO ground                                           |

| 6      |      | MOSI     | SPI interface (Master Output Slave Input)           |

| 7      | 0    | MISO     | SPI interface (Master Input Slave Output)           |

| 8      |      | SCLK     | SPI interface (Spi Clock)                           |

| 9      | 0    | UARTTX   | Reserved                                            |

| 10     |      | UARTRX   | Reserved                                            |

| 11, 12 | NC   | NC       | not connected                                       |

| 13     | I, A | OSCIN    | Ext. quartz connection or ext. clock input          |

| 14-16  | NC   | NC       | not connected                                       |

| 17     | Α    | OSCOUT   | Ext. quartz connection                              |

| 18, 19 | G    | DVSS     | digital ground                                      |

| 20, 21 | NC   | NC       | not connected                                       |

| 22     | I/O  | CACHE    | Reserved                                            |

| 23     | 0    | CLOCKOUT | Clock output (for driving other components)         |

| 24     | 0    | HOSTFAIL | Alarm for handshaking with host                     |

| 25     | 0    | BIT      | Built In Test ("high" means all ok)                 |

| 26     | S    | HVOTP    | Embedded OTP power supply                           |

| 27     | Α    | VREGD    | 1.8V regulated voltage, requires 100nF external cap |

| 28     | S    | DVDD     | 3.3V digital power supply                           |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## Leading in micro and wireless sensor products

| 29    | NC | NC     | not connected                                        |

|-------|----|--------|------------------------------------------------------|

| 30    | I  | RESETN | Reset_n (active low)                                 |

| 31    | NC | NC     | not connected                                        |

| 32    | 1  | DTEST  | Reserved                                             |

| 33-37 | NC | NC     | not connected                                        |

| 38    | Α  | VREF   | Analog regulator output, requires 100nF external cap |

| 39    | Α  | VREGA  | 5V regulated voltage, requires 100nF external cap    |

| 40    | S  | AVDD   | 3.3V analog power supply                             |

#### Legend:

| SYMBOL | DESCRIPTION          |

|--------|----------------------|

| ļ      | Digital Input        |

| 0      | Digital Output       |

| I/O    | Digital Input/Output |

| Α      | Analog               |

| S      | Supply               |

| G      | Ground               |

| NA     | Not applicable       |

| NC*    | Not connected        |

|        |                      |

<sup>\*</sup> NC pins are not connected internally. They can be modeled as an open circuit.

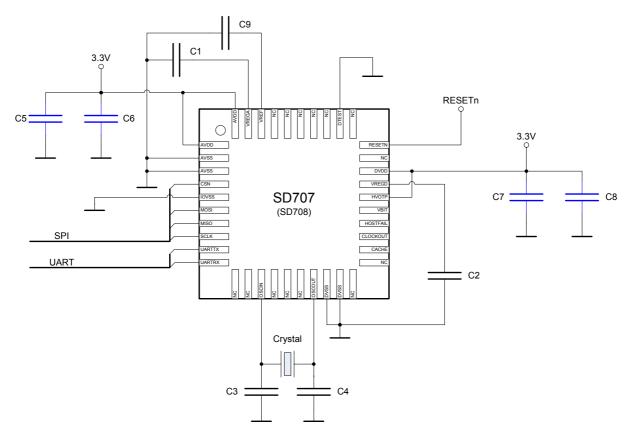

# 3.2. Application Circuit

A few external components are needed as shown in the next picture. The blue capacitors can be omitted if the supply voltage is properly filtered and the supply source has low impedance.

Fig. 5: Application circuit for integrated gyro module SD707/8.

#### **External Components:**

| #  | TYPE    | NAME    | VALUE | UNIT | NOTES                                                           |

|----|---------|---------|-------|------|-----------------------------------------------------------------|

| 1  | Сар     | C1      | 100   | nF   | Mandatory.                                                      |

| 2  | Сар     | C2      | 100   | nF   | Mandatory.                                                      |

| 3  | Сар     | C3      | 10    | pF   | Board parasitic capacitance on OSCIN should be kept below 1pF   |

| 4  | Сар     | C4      | 10    | pF   | Board parasitic capacitance on OSCOUT should be kept below 1pF  |

| 5  | Crystal | CRYSTAL | 12.0  | MHz  | Mandatory. See below for further requirements of quartz crystal |

| 6  | Сар     | C5      | 100   | nF   | Optional. Required for not stabilized power supplies.           |

| 7  | Сар     | C6      | 470   | pF   | Optional. Required for not stabilized power supplies.           |

| 8  | Сар     | C7      | 470   | pF   | Optional. Required for not stabilized power supplies.           |

| 9  | Сар     | C8      | 100   | nF   | Optional. Required for not stabilized power supplies.           |

| 10 | Сар     | C9      | 100   | nF   | Mandatory.                                                      |

## Quartz Crystal Requirements:

| PARAMETER MNEMONIC |                                 | MIN  | TYP  | MAX | UNIT | NOTES                                 |

|--------------------|---------------------------------|------|------|-----|------|---------------------------------------|

| ESR                | Equivalent Series<br>Resistance |      |      | 150 | Ω    |                                       |

| Cload              | Load Capacitance                |      | 10   | 15  | pF   |                                       |

| Driving Level      | DrvLevel                        |      | 10   |     | μW   |                                       |

| Fres               | Resonant frequency              |      | 12.0 |     | MHz  |                                       |

| FreqTol            | Frequency Tolerance             | -0.3 |      | 0.3 | %    | Maximum over liferime and temperature |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

#### Digital I/O Requirements:

| PARAMETER | DESCRIPTION                       | MIN  | MAX | UNIT | NOTES                                                  |

|-----------|-----------------------------------|------|-----|------|--------------------------------------------------------|

| Vil       | Digital input low voltage level   | -0.3 | 1   | V    |                                                        |

| Vih       | Digital input high voltage level  | 4    | 5.5 | V    |                                                        |

| Vol       | Digital output low voltage level  | -    | 0.4 | V    | 4mA current for CLOCKOUT, 2mA for the other outputs    |

| Voh       | Digital output high voltage level | 4.4  | -   | V    | 4mA current for CLOCKOUT,<br>2mA for the other outputs |

#### Pin 23 CLOCKOUT (digital output)

This Pin is by default disabled (high impedance). It can be enabled at end of production line (OTP) to provide the system clock to an external device.

#### Pin 24 Host Failure (digital output)

The Inertial Module contains a digital output (HOSTFAIL) for signalling a failure of the host  $\mu$ C detected by intelligent watchdog procedure between inertial module and host  $\mu$ C. Please contact SensorDynamics for more details on the intelligent watchdog functionality.

#### Pin 25 BIT (digital output)

The Inertial Module contains a digital output (BIT) for signalling an internal failure detected by embedded failsafe checks system. This signal is active low: when BIT voltage is low (Vol) an error is present in the module.

#### Pin 27 VREGD (analog output)

The Inertial Module generates an internally regulated voltage (1.8V) that requires external filtering by a 100nF capacitance.

#### Pin 30 RESETN

RESETN is active low. When RESETN is low (Vil) the device is under reset. When RESETN is high (Vih) the device is in functional mode, if powered.

Case 1: customer application needs to reset the device on demand.

In this case RESETN has to be driven by external device/controller.

Case 2: customer application doesn't need to reset the device on demand.

RESETN can be either connected directly to power supply (3.3V) or pulled-up to 3.3V through dedicated resistor. SD707/8 will be automatically reset by internal POR circuitry at every power-up sequence.

#### Pin 38 VREF (analog output)

The Inertial Module generates an internal voltage reference (1.5V) that requires external filtering by a 100nF capacitance.

#### Pin 39 VREGA (analog output)

The Inertial Module generates an internally regulated voltage (3.3V) that requires external filtering by a 100nF capacitance.

## 4. Clock source

## 4.1. General

SD recommends using a 12 MHz quartz for SD705/6/7/8 as indicated in the application circuits. Alternatively an external 12 MHz ceramic resonator can be used instead of the quartz:

## Ceramic resonator requirements

| PARAMETER | MNEMONIC                        | MIN | TYP | MAX | UNIT | NOTES                                                                                               |

|-----------|---------------------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------|

| ESR       | Equivalent Series<br>Resistance |     |     | 150 | Ω    | Also specified as Resonant Impedance                                                                |

| Cload     | Load Capacitance                |     | 10  | 15  | pF   | Additional capacitor not required if the load capacitor embedded in the ceramic resonator component |

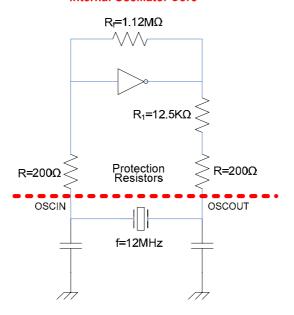

## 4.2. Internal oscillator circuit schematic

The following figure shows a schematic diagram of the internal oscillator circuit implemented in SD705 and SD706 products, with the indication of the nominal values of the resistances.

#### Internal Oscillator Core

A maximum tolerance of 20% has to be considered for the actual value of the internal resistances.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

# 5. Electrical and Physical Characteristics

# 5.1. Operation and performance parameters

**Operation Specification**

| PARAMETER                   | MIN  | TYP | MAX   | UNIT  | CONDITION                       |

|-----------------------------|------|-----|-------|-------|---------------------------------|

| Supply voltage SD705, SD706 | 3.1  |     | 3.5   | V     |                                 |

| Supply voltage SD707, SD708 | 4.75 |     | 5.25  | V     |                                 |

| Supply current SD705, SD706 |      | 16  |       | mA    |                                 |

| Supply current SD707, SD708 |      | 18  |       | mA    |                                 |

| Start up time               |      |     | 400   | ms    | incl. Start up checks           |

| SPI Communication Speed     | 100  |     | 10000 | kHz   | 64 bits telegram (see appendix) |

| Total mass                  |      |     | 0.2   | grams |                                 |

**Gyro Performance Specification \***

| PARAMETER                            | MR1    | MR2            | UNIT        | CONDITION                              |

|--------------------------------------|--------|----------------|-------------|----------------------------------------|

| Measurement range                    | ± 100  | ± 300          | °/s         |                                        |

| Resolution                           | 0.0039 | 0.0156         | (°/s)/LSB   | true 16 bit                            |

| RMS noise                            | 0.07   | 0.2            | °/s         | typical                                |

| Bandwidth (-3dB)                     | 10     | 75             | Hz          | ± 25%                                  |

| Zero rate bias                       | 0 ±    | - 0.5          | °/s         | typical                                |

| Temperature drift zero rate bias     | ±      | <del>-</del> 2 | °/s         | typical                                |

| Sensitivity error                    | ±      | 2.5            | %           | typical over temp                      |

| Linearity error                      | ±      | <u>:</u> 1     | %           | versus best fit                        |

| Micro linearity                      | ±      | 10             | %           |                                        |

| Cross Axis Sensitivity               | ±      | 2.0            | %           | against angular rates about other axes |

| In run drift of rate bias            | ±      | <u>:</u> 1     | °/s         | during 5 min<br>after start-up at RT   |

| Digital value range                  | ± 128  | ± 512          | °/s         | 16 bit message                         |

| Total zero rate error                | ±      | 3.0            | °/s         |                                        |

| Zero rate temperature drift velocity | ±      | 0.2            | (°/s) / min | ± 5 K/min maximum temperature shift    |

| Phase response @ 5 Hz                | -      | 18             | ۰           |                                        |

| Signal Update time                   |        | 1              | ms          | SPI message                            |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

| PARAMETER                      | MR1   | MR2   | UNIT  | CONDITION                                                        |

|--------------------------------|-------|-------|-------|------------------------------------------------------------------|

| Acceleration Cross Sensitivity | 0.    | .1    | °/s/g | during/after 10 ms half-sine:<br>@ 10g, 25g, 50g,100g            |

| Output value on over-range     | ± 128 | ± 512 | °/s   |                                                                  |

| Recovery time after over-range | 5     | 0     | ms    | normal operation after<br>300 °/s for MR1 and<br>900 °/s for MR2 |

| Recovery time after shock      | 5     |       | ms    | For shocks up to 50g, 10 ms                                      |

| Temperature signal tolerance   | ±     | 10    | K     | SPI message                                                      |

<sup>\*</sup> The figures in the table are for nominal supply voltage (3.3V for SD705/706 and 5V for SD707/708)

## **Definitions and Explanations:**

# **Supply Current**

The specified value represents the maximum current consumption under all operating conditions. Its value is given by the sum of the currents going through the pins AVDD and DVDD.

## Startup time

The startup time is the elapsed time between power up (reset) and the transition to locked status.

## Measurement Range

The measurement range is the range of rotation conditions where the module works according to the specified performance.

#### Resolution

The physical resolution is the minimum representable value.

#### RMS noise

Standard deviation of the rate output, computed on at least 500 readings, collected on a time interval of 5s, with zero input rate applied, and according to the formula:

$$OutputNoise = \sqrt{\frac{1}{N} \sum_{1}^{N} \left(OutputSignal - \overline{OutputSignal}\right)^{2}}$$

where  $N \ge 500$  and OutputSignal denotes the average over all collected samples of the rate output signal.

## Noise density

The noise density is the spectral density at a given frequency, measured with a filter of 1 Hz noise bandwidth. Given the RMS noise as defined above, the noise density is given by:

$$Dnoise = OutputNoise / \sqrt{Filter\_band}$$

where  $Filter\_band$  is the bandwidth in Hz of the relevant filter.

#### Bandwidth

The bandwidth is the frequency at which the output rate is attenuated by -3dB compared to the DC value. The bandwidth is programmable at ROM level.

#### Zero rate bias

Maximum deviation from zero rate output signal at zero physical input rate, acceptable after calibration at RT (= 25 °C ±5 °C) and after the manufacturing process (populating, soldering). The bias is computed as the average of at least 500 samples, collected after the signal is valid for 5 sec.

#### Temperature drifts zero rate bias

Maximum deviation of rate output at zero physical input rate over the full temperature range. The bias is computed as the average of at least 500 samples, collected after the signal is valid for 5 sec.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## Sensitivity error

The sensitivity error is the maximum deviation between ideal sensitivity and the linear best fit measured in 5°/s steps from  $\Omega_{\text{min}}$  to  $\Omega_{\text{max}}$  (-100 °/s to + 100°/s) for MR1, respectively measured in 20°/s steps from  $\Omega_{\text{min}}$  to  $\Omega_{\text{max}}$  (-300 °/s to + 300 °/s) for MR2. For both ranges the sensitivity error is given by the following formula:

$$SensError = 100 \bullet \left( \frac{Slope_{computed}}{Slope_{ideal}} - 1 \right)$$

where  $Slope_{ideal} = 1$ .

## Linearity error

The linearity error is the maximum deviation of the rate measured between (-100 °/s to + 100°/s) in 5°/s steps (resp. between -300 °/s to + 300 °/s in 20°/s steps for MR2) from the value obtained by linear best fit, divided by  $\Omega_{\text{max}}$  = 100 °/s (resp.  $\Omega_{\text{max}}$  = 300 °/s for MR2):

$$Le = Max \left\{ \frac{YR(\Omega_{i}) - YR_{best\_fit}(\Omega_{i})}{\Omega_{\max}} \middle| \Omega_{i} \in \left\{ -\Omega_{\max}, -\Omega_{\max} + step^{\circ}/s, ..., \Omega_{\max} - step^{\circ}/s, \Omega_{\max} \right\} \right\} \bullet 100$$

## Cross axis sensitivity

This is the sensitivity of the module to angular rates applied to the non-sensitive axes, which are perpendicular to the sensitive axis and where the module is mounted with negligible angle error to a defined reference mark of the housing. The cross axis sensitivity is then defined as the percentage of the off-axis input rate around (along) the non-sensitive axes seen at the output. The specified limit refers to an applied rate of  $\pm 900^{\circ}$ /s.

## Signal update time

The signal update time is the time elapsed between the start of one data transmission and the next. The specified value is guaranteed by design. Note: data transmission time must be much shorter than the signal update time (see SPI communication speed limits in the table above).

## **Temperature Signal Tolerance**

The temperature signal is provided by a silicon temperature sensor integrated into the ASIC. The temperature signal tolerance indicates the maximum error between the environment temperature and the temperature of the silicon.

## Micro linearity

The micro linearity MLe error is the maximum deviation of the gradient between two adjacent rates from the gradient  $Slop_{e_{sst}\ fit}$  of the linear best fit  $YR_{best}\ fit$  (·)

$$MLe = Max \left\{ \frac{YR(\Omega_i + step^{\circ}/s) - YR(\Omega_i)}{step^{\circ}/s \bullet Slope_{bes\bar{t}\_fit}} - 1 \middle| \Omega_i \in \left\{ -\Omega_{\max}, -\Omega_{\max} + step^{\circ}/s, ..., \Omega_{\max} - step^{\circ}/s \right\} \right\} \bullet 100$$

## Recovery time after over-range

The recovery time is the time elapsed between the instant when the physical applied rate enters the measurable range (from an out of range value) and the time when the circuit delivers a rate output value within specifications.

#### In-run drift of rate bias

This is the maximum drift of the rate output within the first 5 minutes after power-on at constant ambient temperature and zero rate applied, compared to the bias value measured at the end of the startup. During these 5 min, the rate output is recorded at intervals of 10ms or less and the bias is computed using a moving average of 128 samples.

© 2010. Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## Zero rate temperature drift velocity

Maximum rate drift under worst case temperature change 5 K/min, i.e. at maximum heat up or cool down rate.

#### Total zero rate error

Maximum deviation of zero rate output at zero physical input rate including all errors from temperature, power supply, ageing, and other.

#### Phase response

This parameter refers to the maximum phase shift between physical input rate (sinusoidal signal with 5Hz frequency) and the corresponding output rate signal.

Additional phase shifts due to communication time via SPI (and additionally e.g. CAN in the application) have to be taken into consideration.

## Output value on over-range

Under applied physical angular rates exceeding the specified range, the value of the rate output saturates at the maximum value ( $\pm 128$ °/s for MR1 and  $\pm 512$ °/s for MR2, with the sign depending on the direction of the rate applied) and stays in saturation up to physical rates of  $\pm 900$ °/s.

## Recovery time after shock

The recovery time after shock defines the maximum time allowed to the gyro module to return in normal operating conditions, after the decay of a half-sine shock excitation of 50g amplitude and 10ms duration. The "normal operating conditions" is the state in which all the module parameters are in agreement with the present specification.

## Acceleration cross sensitivity / vibration susceptibility

To avoid erroneous output signals under automotive operation conditions, the gyro module offers special shock and vibration resistivity. The requirements are based on the ISO standard 16750-3 for passenger cars. The power spectral density of the relevant vibration on gyro module level is given by

| f / Hz | g² / Hz |

|--------|---------|

| 10     | 0.21    |

| 55     | 0.21    |

| 1000   | 0.015   |

As equivalent total acceleration 6.9 g is assumed. The signal deterioration does not exceed  $\pm$  2 °/s offset shift and 1.5 °/s rms noise level under these vibration levels.

In the frequency range 0 Hz to 10 kHz the acceleration cross sensitivity of the sensor element is less than  $0.01 \, (^{\circ}/s)/(m/s^2)$  for static and dynamic accelerations.

# Acceleration cross sensitivity / Shock sensitivity

The acceleration cross sensitivity limits the maximum allowed rate output change related to static and dynamic linear accelerations. It is defined as the rate output change divided by the applied acceleration amplitudes for the defined test shock pulses with half sine waves of 10 ms duration and with amplitudes of 10 g, 25 g, 50 g, and 100 g.

No sticking effects of the moving MEMS structures occur under high shock levels like direct impact or drop from 1.2m onto concrete floor according to the standard automotive drop test requirements.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

## 6. SPI Communication

#### 6.1. General information

The SD70x SPI communication channel allows the host to get information of various types from the ASIC. Physical settings of the communication need **phase** to be set to 1 and **polarity** to 0. Some more words about phase and polarity can be found at the end of this document. The SPI communication is managed according to a **master-slave** paradigm where the host always acts as the master and the ASIC as the slave. The SPI communication must conform to a **protocol** obeying to the following rules:

- The communication can be thought as based on a per-session mode: the master (host) starts a session by sending a message to the slave (ASIC) which in turn replies with the answer related to the query received in the previous session. The very first answer since can not rely on a previous one is simply the state (see below) of the ASIC. The ASIC answer ends the session.

- All messages (in both directions) are fixed size (64 bits);

- All messages (in both directions) are formatted accordingly to the following overall structure:

General message structure

| By  | te 7 | Byt | te 6 | Byt | Byte 5 Byte 4 |         | te 4 | Ву | te 3 | Byte 2 |    | Byte 1 |     | Byte 0 |   |

|-----|------|-----|------|-----|---------------|---------|------|----|------|--------|----|--------|-----|--------|---|

| 63  | 56   | 55  | 48   | 47  | 40            | 39      | 32   | 31 | 24   | 23     | 16 | 15     | 8   | 7      | 0 |

| Hir | nfo1 | Hin | fo2  |     |               | Payload |      |    |      |        |    | Tir    | nfo |        |   |

- Bit-order: bit 63 is the first one sent, bit 0 the last one.

- Hinfo1, Hinfo2 and Tinfo are mandatory fields for all message types. Payload is the portion specifically arranged for any particular message.

#### 6.1.1. Hinfo1

Hinfo1 content adheres to the following structure:

## Command sent by the Host

| Hinfo1 (F | RX by SPH | nterface) |       |       |        |       |       |

|-----------|-----------|-----------|-------|-------|--------|-------|-------|

| bit 7     | bit 6     | bit 5     | bit 4 | bit 3 | bit 2  | bit 1 | bit 0 |

|           | Acnt      |           |       |       | Opcode |       |       |

*Acnt* is a counter incremented by 1 at each sent telegram. Its value can be checked by the ASIC. The host must increment this value every telegram sending (modulo 8: after "111" the counter restarts from 0).

Opcode: This field tells the ASIC which action has to be performed (it is the command code).

#### Answer sent by the ASIC

| _Hinfo1 (T | Hinfo1 (TX by SPI Interface)                    |  |                                            |  |  |  |  |  |

|------------|-------------------------------------------------|--|--------------------------------------------|--|--|--|--|--|

| bit 7      | bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 |  |                                            |  |  |  |  |  |

|            | Acnt                                            |  | Opcode                                     |  |  |  |  |  |

| HW         |                                                 |  | HW(STATB, RATE) or Register(iWDOGB, DIAGB) |  |  |  |  |  |

Acnt: this value is incremented modulo 8 every telegram sending.

Opcode: The value of this field is the opcode of the telegram which this answer is related to.

© 2010. Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

#### 6.1.2. Hinfo2

For the purposes of this document, the host has not to take care of this field (it can be filled with 0). Hinfo2 content from the ASIC adheres to the following structure:

## Answer sent by the ASIC

# Hinfo2 (TX by SPI Interface)

| bit 7 | bit 6 | bit 5          | bit 4    | bit 3    | bit 2 | bit 1         | bit 0 |

|-------|-------|----------------|----------|----------|-------|---------------|-------|

| BIT_N | LMS   | Diag_Buf_valid | iWD      | WARN     |       | SW status     |       |

| Input | HW    | HW             | reserved | reserved | А     | PB register/H | /W    |

Here is a summarized description of the fields as filled by the ASIC. It is beyond the purposes of this document to deeply explain the meaning of each field.

| BIT_N          | Set by the hardware.                                                                   |

|----------------|----------------------------------------------------------------------------------------|

|                | BIT_N=0 no internal failure (Physical pin BIT=1).                                      |

|                | BIT_N=1 internal failure (Physical pin BIT=0).                                         |

| LMS            | Set by the hardware.                                                                   |

|                | LMS=1 CRC or Frame error in previous telegram.                                         |

|                | LMS=0 no errors in previous telegram.                                                  |

| Diag_Buf_valid | Set by the hardware. Reserved.                                                         |

| iWD            | Set by the hardware. Reserved.                                                         |

| WARN           | Set by the hardware. Reserved                                                          |

| SW status      | Current status of the software application. Possible status values are reported in the |

|                | table below                                                                            |

| SW Status        | Value | Description                                                                                                                                                                                      |

|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InitMode         | 0x00  | System initialization phase. Check of self diagnosis functions started.  SPI SW commands not available.  BIT_N is forced to 1 (fail); rate values are not meaningful.                            |

| ReadyForSpi      | 0x01  | All SPI commands available. BIT_N is forced to 1 (fail); rate values are not meaningful.                                                                                                         |

| ReadyForFsEnable | 0x02  | Check of self diagnosis functions completed. Agc/pll lock still not reached. BIT_N is forced to 1 (fail); rate values are not meaningful.                                                        |

| NormalMode       | 0x03  | First agc/pll lock reached. BIT_N is "0" if the self-diagnosis does not detect any failure. Rate values are valid if BIT_N = 0.                                                                  |

| Rreserved        | 0x04  | -                                                                                                                                                                                                |

| Reserved         | 0x05  | -                                                                                                                                                                                                |

| Overrun error    | 0x06  | This value is directly imposed by the hardware in case of SPI overrun errors (a SW command has been received too early, while previous SW command was still in progress, so it will be ignored). |

| ResetOngoing     | 0x07  | The ASIC is going to perform an auto-reset in no more than 25 ms.                                                                                                                                |

## 6.1.3. Tinfo

Tinfo contains the cyclic redundancy (CRC) code of the telegram. The host and the ASIC use the same algorithm to compute the CRC. The algorithm used is explained near the end of this document.

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

# 6.2. ReadRate Opcode (0x01)

This command is used to get rate and temperature values from the ASIC.

## Command sent by the Host

| byte 7 | byte 6 | byte 5   | byte 4   | byte 3   | byte 2   | byte 1   | byte 0 |

|--------|--------|----------|----------|----------|----------|----------|--------|

| 63 56  | 65 48  | 47 40    | 39 32    | 31 24    | 23 16    | 15 8     | 7 0    |

| Hinfo1 | Hinfo2 | Reserved | Reserved | Reserved | Reserved | Reserved | Tinfo  |

All 'Reserved' fields can be filled with 0es.

Example of a rate telegram (bytes are space separated and in hexadecimal format):

21 00 00 00 00 00 00 38

## Answer sent by the ASIC

| byte 7 | byte 6 | byte 5 | byte 4         | byte 3  | byte 2         | byte 1  | byte 0 |

|--------|--------|--------|----------------|---------|----------------|---------|--------|

| 63 56  | 65 48  | 47 40  | 39 32          | 31 24   | 23 16          | 15 8    | 7 0    |

| Hinfo1 | Hinfo2 | Temp   | RateMR1<br>MSB | RateMR1 | RateMR2<br>MSB | RateMR2 | Tinfo  |

*Temp* type is an unsigned integer over 8 bits. It reports the temperature in °C (T°) according to the following formula:

$$T^{\circ}$$

(°C) =  $Temp$  – 80 °C

RateMR1/ RateMR2 are signed integers over 16 bits. They report the angular speed in °/s, according to the following formulas:

RateMR1 (°/s) = RateMR1 / 256 RateMR2 (°/s) = RateMR2 / 64

# 6.3. ReadStatus Opcode (0x02)

This command is used to get the current status of the self-diagnosis..

#### Command sent by the Host

| byte 7 | byte 6 | byte 5   | byte 4   | byte 3   | byte 2   | byte 1   | byte 0 |

|--------|--------|----------|----------|----------|----------|----------|--------|

| 63 56  | 65 48  | 47 40    | 39 32    | 31 24    | 23 16    | 15 8     | 7 0    |

| Hinfo1 | Hinfo2 | Reserved | Reserved | Reserved | Reserved | Reserved | Tinfo  |

All 'Reserved' fields can be filled with 0es.

Example of a status telegram (bytes are space separated and in hexadecimal format):

02 00 00 00 00 00 00 B0

## Answer sent by the ASIC

| byte 7 | byte 6          | byte 5 | byte 4 | byte 3 | byte 2 | byte 1            | byte 0 |

|--------|-----------------|--------|--------|--------|--------|-------------------|--------|

| 63 56  | 65 48           | 47 40  | 39 32  | 31 24  | 23 16  | 15 8              | 7 0    |

| Hinfo1 | Hinfo2          |        | Statu  | ısInfo |        | HWInfo (reserved) | Tinfo  |

|        |                 | MSB    |        |        | LSB    |                   |        |

|        | StatusInfo bits | 31 24  | 23 16  | 15 8   | 7 0    |                   |        |

*StatusInfo* is an unsigned integer over 32 bits. The *StatusInfo* bits are related to the current status (real-time) of the internal self-diagnosis functions. The meaning of the status bits is listed in the following table:

|         | Bit pos                    | sition                            |                |                          |                          |

|---------|----------------------------|-----------------------------------|----------------|--------------------------|--------------------------|

|         | in SPI<br>telegram<br>0x02 | in 32-bits<br>Status<br>Info word | short bit name | Event source description | example in<br>alarm word |

|         | 16                         | 0                                 | -              | reserved                 | 0x00000001               |

| 1 1     | 17                         | 1                                 | -              | reserved                 | 0x00000002               |

| 1 1     | 18                         | 2                                 | -              | reserved                 | 0x00000004               |

|         | 19                         | 3                                 | -              | reserved                 | 0x00000008               |

|         | 20                         | 4                                 | -              | reserved                 | 0x00000010               |

|         | 21                         | 5                                 | -              | reserved                 | 0x00000020               |

|         | 22                         | 6                                 | -              | reserved                 | 0x00000040               |

| sonrces | 23                         | 7                                 | pll_fail       | PLL_lock_error           | 0x00000080               |

| [일      | 24                         | 8                                 | -              | reserved                 | 0x00000100               |

| ᅵᇙᅵ     | 25                         | 9                                 | agc_fail       | AGC_lock_error           | 0x00000200               |

| %       | 26                         | 10                                | -              | reserved                 | 0x00000400               |

| ≩       | 27                         | 11                                | -              | reserved                 | 0x00000800               |

|         | 28                         | 12                                | -              | reserved                 | 0x00001000               |

|         | 29                         | 13                                | -              | reserved                 | 0x00002000               |

|         | 30                         | 14                                | -              | reserved                 | 0x00004000               |

|         | 31                         | 15                                | -              | reserved                 | 0x00008000               |

|         | 32                         | 16                                | -              | reserved                 | 0x00010000               |

|         | 33                         | 17                                | -              | reserved                 | 0x00020000               |

|         | 34                         | 18                                | -              | reserved                 | 0x00040000               |

|         |                            |                                   |                |                          |                          |

|         | 35                         | 19                                | -              | reserved                 | 0x00080000               |

|         | 36                         | 20                                | -              | reserved                 | 0x00100000               |

|         | 37                         | 21                                | otp_fail       | OTP check routine        | 0x00200000               |

|         | 38                         | 22                                | -              | reserved                 | 0x00400000               |

| sources | 39                         | 23                                | -              | reserved                 | 0x00800000               |

| JL C    | 40                         | 24                                | -              | reserved                 | 0x01000000               |

| 301     | 41                         | 25                                | =              | reserved                 | 0x02000000               |

| >       | 42                         | 26                                | -              | reserved                 | 0x04000000               |

| SW      | 43                         | 27                                | -              | reserved                 | 0x08000000               |

|         | 44                         | 28                                | -              | reserved                 | 0x10000000               |

|         | 45                         | 29                                | -              | reserved                 | 0x20000000               |

|         | 46                         | 30                                | -              | reserved                 | 0x40000000               |

|         | 47                         | 31                                | -              | reserved                 | 0x80000000               |

Example of answer from the ASIC 82 03 02 00 00 00 50 D1

# 6.4. AsicOperation Opcode (0x0B)

This is the general telegram format that can be used for several subcommands, obtained by specifying different action types.

Command sent by the Host

| byte 7 | byte 6 | byte 5     | byte 4 | byte 3 | byte 2 | byte 1 | byte 0 |

|--------|--------|------------|--------|--------|--------|--------|--------|

| 63 56  | 65 48  | 47 40      | 39 32  | 31 24  | 23 16  | 15 8   | 7 0    |

| Hinfo1 | Hinfo2 | ActionType |        |        |        |        | Tinfo  |

ActionType: one of the following available actions

| Action Type | Short name      | Description                                          |

|-------------|-----------------|------------------------------------------------------|

| 0x00        | ReadSysParam    | Reserved for production tests.                       |

| 0x01        | ReadOtp         | Reserved for production tests.                       |

| 0x30        | ReadVersionInfo | Read version information.                            |

| 0x40        | Reserved        | Reserved                                             |

| 0x50        | Reserved        | Reserved                                             |

| 0x70        | SetSpiPhPo      | Set new phase and polarity for the SPI interface     |

| 0x80        | TriggerReset    | Trigger an auto-reset of the asic in the next 25 ms. |

The meaning of the other bytes is related to the action type. Telegram format for each different action type is detailed after this general format description.

Answer sent by the ASIC

|        |        | . •                |          |          |          |          |        |

|--------|--------|--------------------|----------|----------|----------|----------|--------|

| byte 7 | byte 6 | byte 5             | _ byte 4 | _ byte 3 | _ byte 2 | _ byte 1 | byte 0 |

| 63 56  | 65 48  | 47 40              | 39 32    | 31 24    | 23 16    | 15 8     | 7 0    |

| Hinfo1 | Hinfo2 | ActionType<br>Echo |          |          |          |          | Tinfo  |

ActionTypeEcho: echo of the ActionType related to this answer.

The meaning of the other bytes is related to the action type. Telegram format for each different action type is detailed after this general format description.

# 6.4.1. AsicOperation (0x30): ReadVersionInfo (action type 0x30)

This command is used to read the values of several identifiers related to the version of HW and SW. The details are shown in the table below. Some of the following entries are intended for production/debug only and are not detailed here.

| Offset | Short name         | Description                                    |

|--------|--------------------|------------------------------------------------|

| 0      | Sysparam_layout_id | Value of SYSPARAM_LAYOUT_ID system parameter   |

| 1      | Sysparam_family_id | Value of SYSPARAM_FAMILY_ID system parameter   |

| 2      | Sysparam_sub_id    | Value of SYSPARAM_SUB_ID system parameter      |

| 3      | Filter_version_id  | Version of the dspbank config file             |

| 4      | Asic_redo_id       | Asic identifier embedded in the ASIC hardware. |

| 5      | App_name_id        | Firmware application identifier                |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

| 6  | App_primary_id         | Firmware application primary ID   |  |  |

|----|------------------------|-----------------------------------|--|--|

| 7  | App_secondary_id       | Firmware application secondary ID |  |  |

| 8  | Module_id byte 0 (msb) | Module ID identifier              |  |  |

| 9  | Module_id byte 1       |                                   |  |  |

| 10 | Module_id byte 2       |                                   |  |  |

| 11 | Module_id byte 3 (Isb) |                                   |  |  |

| 12 | Trimming_version_id    | Trimming firmware version         |  |  |

Command sent by the Host

| byte 7 | byte 6 | byte 5 | byte 4 | byte 3 | byte 2 | byte 1   | byte 0 |

|--------|--------|--------|--------|--------|--------|----------|--------|

| 63 56  | 65 48  | 47 40  | 39 32  | 31 24  | 23 16  | 15 8     | 7 0    |

| Hinfo1 | Hinfo2 | 0x30   | Offs   | Offset |        | Reserved | Tinfo  |

|        |        |        | msb    | lsb    |        |          |        |

Offset is the 16 bits start address offset of the version bytes to be read (related to the beginning of the internal xdata variable that hosts all the version data structure).

All 'Reserved' fields can be filled with 0es.

Example of a ReadVersionInfo telegram (bytes are space separated and in hexadecimal format): 0B 00 30 00 08 00 00 1C

Answer sent by the ASIC

| byte 7 | _ byte 6 | _ byte 5 _ | byte 4                      | byte 3                        | byte 2                        | byte 1                        | _byte 0 |

|--------|----------|------------|-----------------------------|-------------------------------|-------------------------------|-------------------------------|---------|

| 63 56  | 65 48    | 47 40      | 39 32                       | 31 24                         | 23 16                         | 15 8                          | 7 0     |

| Hinfo1 | Hinfo2   | 0x30       | Version<br>byte<br>[Offset] | Version<br>byte<br>[Offset+1] | Version<br>byte<br>[Offset+2] | Version<br>byte<br>[Offset+3] | Tinfo   |

*Version* bytes are 4 bytes from the internal version data structure.

*Note*: only the values related to the version data reported in the table are meaningful. Values related to offsets greater than the dimension of version data structure are undefined and can be ignored.

Example of answer from the ASIC CB 23 30 00 00 01 22 7C

# 6.4.2. AsicOperation (0x0B): SetSpiPhPo (action type 0x70)

This command is used to change on the fly the phase and polarity (Ph/Po) settings of the ASIC SPI interface. Request telegram (containing MOSI command) must be exchanged with the current (old) settings, while answer telegram (containing MISO answer) must be exchanged using the new settings.

Note: the required PH-PO settings can be directly programmed into OTP parameters, so this command should not be needed. Anyway it is provided for more complex situations where the host wants to decide at run-time which are the preferred settings to be used.

Command sent by the Host

| byte 7 | byte 6 | byte 5 | byte 4    | byte 3 | byte 2 | byte 1   | byte 0 |

|--------|--------|--------|-----------|--------|--------|----------|--------|

| 63 56  | 65 48  | 47 40  | 39 32     | 31 24  | 23 16  | 15 8     | 7 0    |

| Hinfo1 | Hinfo2 | 0x70   | 0x2B      | 0xCA   | PhPo   | Reserved | Tinfo  |

|        |        |        | ActionKey | PhPo   |        |          |        |

|        |        |        | msb       | lsb    |        |          |        |

<sup>© 2010.</sup> Proprietary data. All rights reserved by SensorDynamics AG Entwicklungs- und Produktionsgesellschaft (below SD) including the right to file industrial property rights. SD retains the sole power of distribution, such as reproduction, copying, distribution, adaptation, merger and translation. Reproduction, copying, distribution, adaptation, merger and translation, in part or whole, without the prior written consent of SD, is prohibited. The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics.

#### Leading in micro and wireless sensor products

ActionKeyPhPo is the 16 bits key that must be provided to prevent unintentional Ph/Po changes. The expected key is 0x2BCA. In case of different key value the command will be rejected and the Ph-Po settings will not be changed.

PhPo: Bit 1 : SPI phase (0=sample on first edge, 1=sample on second edge)

Bit 0 : SPI polarity (logic value of SCLK when idle)

See dedicated section about SPI phase and polarity.

All 'Reserved' fields can be filled with 0es.

Example of a SetSpiPhPo telegram (bytes are space separated and in hexadecimal format): 0B 00 70 2B CA 02 00 D4

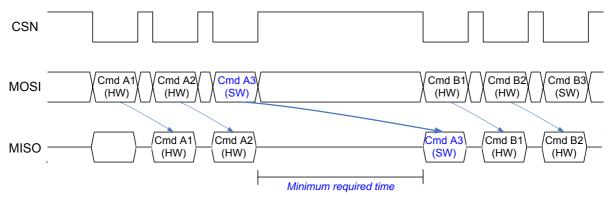

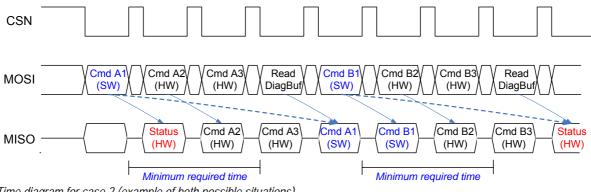

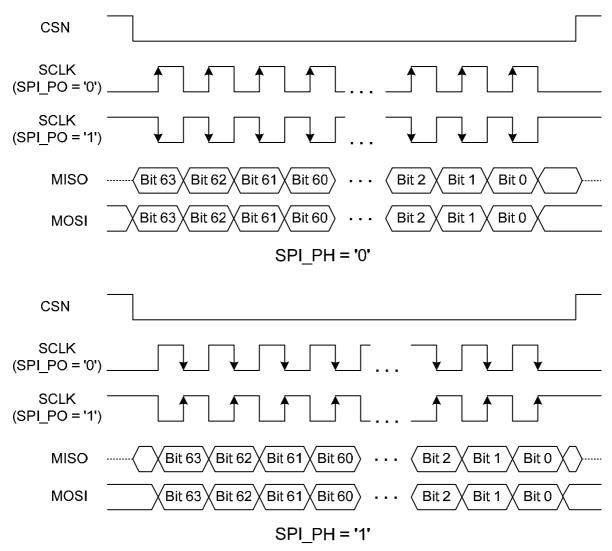

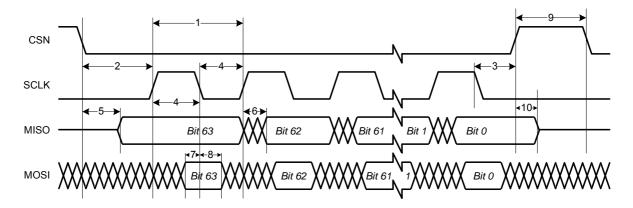

#### Answer sent by the ASIC