# **SPT5320**

### 12-BIT, 160 MWPS D/A CONVERTER

### ADVANCE INFORMATION

### **FEATURES**

- 12-bit, 160 MWPS digital-to-analog converter

- ±1.0 LSB INL; ±0.5 LSB DNL

- +2.7 V to +5.5 V operation for digital supplies

- High wideband spurious free dynamic range

- Low glitch impulse 5 pV-s

- Low power: ≤100 mW @ +3.0 V digital supply

- Internal voltage reference

- · Powerdown mode

### **APPLICATIONS**

- · Broadband modems

- · Wireless local loops

- · Cellular and PCS basestations

- Head-end broadcast video transmission systems

- · Professional broadcast video equipment

- Communications test equipment

- · Direct digital synthesis

### **DESCRIPTION**

The SPT5320 is a 12-bit, 160 MWPS digital-to-analog converter designed primarily for RF communications and instrumentation applications. It provides excellent spurious performance operation at the lowest possible cost. The digital power supply can range from +2.7 V to +5.5 V.

The SPT5320 operates at an industrial temperature range of -40 °C to +85 °C and is available in 28-lead SOIC or SSOP-equivalent packages.

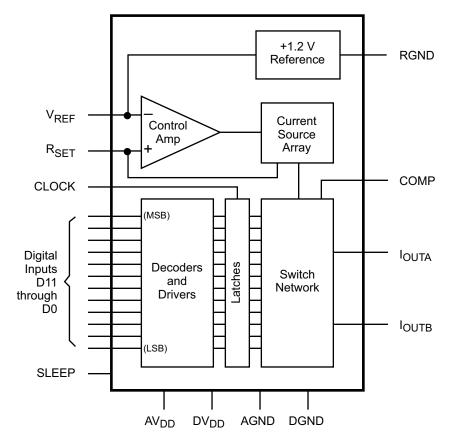

### **BLOCK DIAGRAM**

## Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: 719-528-2300 Fax: 719-528-2370 Web Site: http://www.spt.com e-mail: sales@spt.com

## ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

| Supply Voltages                     |                                             | Output                                                                         |

|-------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------|

| AV <sub>DD</sub>                    |                                             | I <sub>OUTA</sub> , I <sub>OUTB</sub> Current                                  |

| DV <sub>DD</sub>                    |                                             | I <sub>OUTA</sub> , I <sub>OUTB</sub> Voltage –1.0 to AV <sub>DD</sub> + 0.3 V |

| AGND, DGND, RGND                    |                                             | Temperature                                                                    |

| AGND – DGND                         | ±300 mV                                     | Operating Temperature –40 to +85 °C                                            |

|                                     |                                             |                                                                                |

| Input Voltages                      |                                             | Junction Temperature +175 °C                                                   |

| Digital Inputs                      | 0.3 V to DV <sub>DD</sub> + 0.3 V           | Lead Temperature, (soldering 10 seconds) +300 °C                               |

| V <sub>REF</sub> , R <sub>SET</sub> | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ | Storage Temperature –65 to +150 °C                                             |

| COMP                                | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |                                                                                |

Note 1: Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied conditions in typical applications.

### **ELECTRICAL SPECIFICATIONS**

$T_A \!\!=\!\! T_{MIN}$  to  $T_{MAX},\, AV_{DD} \!\!=\!\! DV_{DD} \!\!=\!\! +5.0$  V, unless otherwise specified.

| PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                            | TEST<br>CONDITIONS                         | TEST<br>LEVEL | MIN  | SPT5320<br>TYP                                              | MAX                                     | UNITS                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------|------|-------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|

| DC Performance Resolution Differential Linearity Differential Linearity Integral Linearity Integral Linearity Offset Error                                                                                                                                                                                                                                                                            | 25 °C<br>Full Temp.<br>25 °C<br>Full Temp. |               |      | 12<br>±0.5<br>±1.0<br>±1.0<br>±2.0                          | ±0.025                                  | Bits<br>LSB<br>LSB<br>LSB<br>LSB<br>W FS                                        |

| Gain Error (without internal refere Gain Error (with internal reference Full-Scale Output Current Output Compliance Voltage Equivalent Output Resistance Gain Error Tempco Zero-Scale Offset Error Output Capacitance Offset Drift Gain Drift (without internal reference)                                                                                                                            | )<br>ce)                                   |               | -1.0 | ±2<br>±1<br>20.48<br>>100<br>tbd<br>5<br>tbd<br>±50<br>±100 | ±0.025<br>±10<br>±10<br>+1.25<br>±0.025 | % FS<br>% FS<br>mA<br>V<br>kΩ<br>PPM/°C<br>% FS<br>pF<br>ppm FS/°C<br>ppm FS/°C |

| Dynamic Performance  Maximum Output Update Rate Output Settling Time (to 0.1%) Output Propagation Delay Glitch Impulse Output Rise Time (10% to 90%) Output Fall Time (10% to 90%) Output Noise (I <sub>OUTFS</sub> = 10 mA) Spurious Free Dynamic Range to $f_{CLK} = 50 \text{ MHz}; f_{OUT} = 20 \text{ MHz}$ $f_{CLK} = 160 \text{ MHz}; f_{OUT} = 20 \text{ MHz}$ Spurious Free Dynamic Range wi | :<br>Iz<br>Iz<br>thin a Window             |               |      | 160<br>25<br>tbd<br>5<br>tbd<br>tbd<br>25<br>67<br>67<br>63 | 35<br>50                                | MWPS ns ns pV-s ns ns pA/√Hz dBc dBc dBc dBc                                    |

| $f_{\rm CLK}$ = 50 MHz; $f_{\rm OUT}$ = 5 MHz; $f_{\rm CLK}$ = 100 MHz; $f_{\rm OUT}$ = 5 MHz Multitone Power Ratio (8 Tones at $f_{\rm CLK}$ = 20 MHz; $f_{\rm OUT}$ = 2.00 to                                                                                                                                                                                                                       | r; 4 MHz Span<br>110 kHz Spacing)          |               |      | 86<br>86<br>75                                              |                                         | dBc<br>dBc<br>dBc                                                               |

2

SPT5320

8/24/00

·

### **ELECTRICAL SPECIFICATIONS**

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = DV_{DD} = +5.0$  V, unless otherwise specified.

| PARAMETERS                                                                                                                                                                                                                                                                                                                                                | TEST<br>CONDITIONS                      | TEST<br>LEVEL | MIN                                       | SPT5320<br>TYP                                     | MAX                                             | UNITS                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------------|------------------------------------------------------|

| Power Supply Requirements  Analog Supply Voltage AV <sub>DD</sub> Digital Supply Voltage DV <sub>DD</sub> Analog Supply Current Digital Supply Current Supply Current Sleep Mode Power Dissipation At +3 V Supplies and 10 m. At +5 V Supplies and 10 m. Power Supply Rejection Ratio Power Supply Rejection Ratio                                        | A Current Output<br>(AV <sub>DD</sub> ) |               | 4.5<br>2.7                                | tbd<br>tbd<br>tbd<br>100<br>300<br>±0.02<br>±0.002 | 5.5<br>5.5<br>tbd<br>tbd<br>5<br>±0.2<br>±0.025 | V<br>V<br>MA<br>MA<br>MA<br>MW<br>WFS/V              |

| Reference Reference Voltage Reference Output Current Reference Input Compliance I Small Signal Bandwidth Reference Voltage Drift                                                                                                                                                                                                                          |                                         |               | 0.1                                       | 1.20<br>tbd<br>tbd<br>±50                          | 1.25                                            | V<br>V<br>MHz<br>ppm/°C                              |

| Digital Inputs  Logic "1" Voltage (DV <sub>DD</sub> = +3 \ Logic "0" Voltage (DV <sub>DD</sub> = +5 \ Logic "1" Voltage (DV <sub>DD</sub> = +5 \ Logic "0" Voltage (DV <sub>DD</sub> = +5 \ Logic "0" Current Logic "0" Current Input Capacitance Input Setup Time - t <sub>S</sub> Input Hold Time - t <sub>H</sub> Latch Pulse Width - t <sub>LPW</sub> | Ý)<br>()                                |               | 2.1<br>3.5<br>-10<br>-10<br>2<br>2<br>tbd | 3<br><1<br><1                                      | 0.9<br>1.3<br>+10<br>+10<br>5                   | V<br>V<br>V<br>V<br>µA<br>µA<br>pF<br>ns<br>ns<br>ns |

#### **TEST LEVEL CODES** TEST LEVEL **TEST PROCEDURE** All electrical characteristics are subject 100% production tested at the specified temperature. to the following conditions: 100% production tested at $T_A$ = +25 °C, and sample tested at the Ш specified temperatures. All parameters having min/max specifications are guaranteed. The Test Level Ш QA sample tested only at the specified temperatures. column indicates the specific device IV Parameter is guaranteed (but not tested) by design and characterizatesting actually performed during protion data. duction and Quality Assurance inspection. Any blank section in the data V Parameter is a typical value for information purposes only. column indicates that the specification ۷I 100% production tested at $T_A = +25$ °C. Parameter is guaranteed over is not tested at the specified condition. specified temperature range.

3

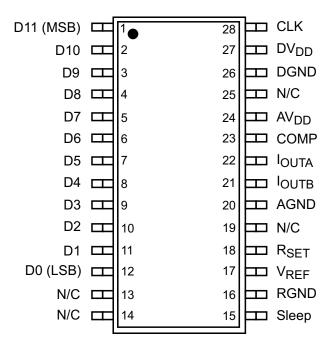

### PIN ASSIGNMENTS

### PIN FUNCTIONS

| Name                     | Function                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ANALOG OUTPUTS           |                                                                                                                                                                                                                                     |  |  |  |  |

| I <sub>OUTA</sub>        | DAC current output.                                                                                                                                                                                                                 |  |  |  |  |

| I <sub>OUTB</sub>        | Complementary current output.                                                                                                                                                                                                       |  |  |  |  |

| DIGITAL INPUTS           |                                                                                                                                                                                                                                     |  |  |  |  |

| D0-D11                   | Digital Inputs (D0 is the LSB)                                                                                                                                                                                                      |  |  |  |  |

| Sleep                    | Sleep mode pin. Active high. Contains active pull-down resistor.                                                                                                                                                                    |  |  |  |  |

| CLK                      | Clock input pin. Data is latched on the rising edge.                                                                                                                                                                                |  |  |  |  |

| REFERENCE & COMPENSATION |                                                                                                                                                                                                                                     |  |  |  |  |

| RGND                     | Reference ground when using internal 1.2 V reference. Connect to AV <sub>DD</sub> to disable internal reference.                                                                                                                    |  |  |  |  |

| V <sub>REF</sub>         | Reference input/output. Serves as an input when internal reference is disabled. Serves as a 1.2 V reference output when internal reference is enabled. Requires a 0.1 µF capacitor tied to AGND when internal reference is enabled. |  |  |  |  |

| R <sub>SET</sub>         | Full-scale current output adjustment.                                                                                                                                                                                               |  |  |  |  |

| COMP                     | Internal bias node for switch driver circuitry. Use 0.1 µF capacitor tied to AGND.                                                                                                                                                  |  |  |  |  |

| POWER                    |                                                                                                                                                                                                                                     |  |  |  |  |

| AGND                     | Analog Supply Return.                                                                                                                                                                                                               |  |  |  |  |

| DGND                     | Digital Supply Return.                                                                                                                                                                                                              |  |  |  |  |

| $AV_{DD}$                | Analog +4.5 to +5.5 V supply.                                                                                                                                                                                                       |  |  |  |  |

| $DV_DD$                  | Digital +2.7 to +5.5 V supply.                                                                                                                                                                                                      |  |  |  |  |

| N/C                      | No connect.                                                                                                                                                                                                                         |  |  |  |  |

|                          |                                                                                                                                                                                                                                     |  |  |  |  |

### ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE             |

|-------------|-------------------|---------------------|

| SPT5320SIS  | −40 °C to +85 °C  | 28L SOIC            |

| SPT5320SIR  | −40 °C to +85 °C  | 28L SSOP Equivalent |

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby expressly granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING – LIFE SUPPORT APPLICATIONS POLICY – SPT products should not be used within Life Support Systems without the specific written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can be reasonably expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to device failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.

SPT5320

4