AN10935 Using SDR/DDR SDRAM memories with LPC32xx Rev. 2 – 11 October 2010 Ap

**Application note**

#### **Document information**

| Info     | Content                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| Keywords | LPC32x0, LPC32xx, LPC3220, LPC3230, LPC3240, LPC3250, SDR, SDRAM, DDR                                                         |

| Abstract | This application note covers hardware related issues for interfacing SDR or DDR SDRAMs to the LPC32xx family microcontroller. |

#### **Revision history**

| Rev | Date     | Description                |

|-----|----------|----------------------------|

| 2   | 20101011 | • Add <u>Section 2.4</u> . |

|     |          | • Updated <u>Table 6</u> . |

|     |          | • Updated <u>Table 7</u> . |

| 1   | 20100603 | Initial version            |

## **Contact information**

For additional information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN10935

All information provided in this document is subject to legal disclaimers.

## 1. Introduction

NXP's LPC32x0 32-bit microcontroller was designed for embedded applications requiring high performance and low power consumption. The LPC32x0 is based on the ARM926EJ-S CPU core with a Vector Floating Point co-processor, and a large set of standard peripherals. The basic ARM926EJ-S CPU Core implementation uses Harvard architecture with a 5-stage pipeline, and has one 32 kB instruction cache and one 32 kB data cache. The ARM926EJ-S core also has an integral Memory Management Unit (MMU) to provide the virtual memory capabilities required to support the multi-programming demands of modern operating systems. The LPC32x0 comes with internal static memory ranging between 128 kB to 256 kB. While this is enough memory for some embedded applications, many applications require larger amounts of memory. The LPC32x0 has an integrated External Memory Controller (EMC) for interfacing to external memories.

The LPC32x0 EMC is an ARM PrimeCell MultiPort Memory Controller peripheral offering support for asynchronous static memory devices such as RAM, ROM and Flash, as well as dynamic memories such as Single Data Rate (SDR) and Double Data Rate (DDR) SDRAM. For external memory of 2 MB or larger the most practical memories to use today are SDR or DDR SDRAM.

This application note will focus on connectivity, initialization and board layout guidelines when using SDR and DDR memories with the LPC32x0.

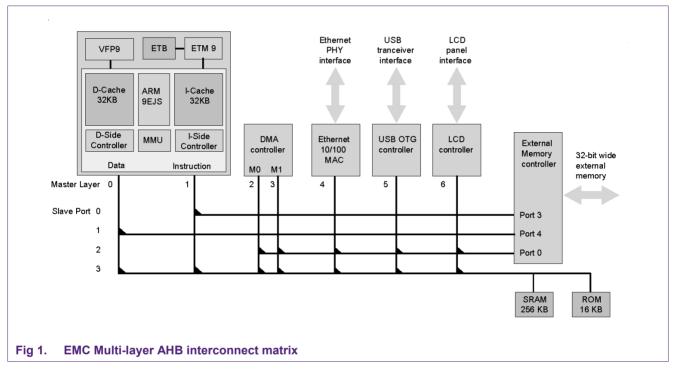

## 2. External memory controller

The LPC32x0 uses an expanded AMBA high-performance bus (AHB) architecture known as Multi-layer AHB. A Multi-layer AHB replaces the request/grant and arbitration mechanism used in a simple AHB with an interconnect matrix that moves arbitration out toward the slave devices. Within the interconnect matrix each slave port has its own arbitration block. Thus, if a CPU and a DMA controller want access to the same memory, the interconnect matrix arbitrates between the two when granting access to the memory. The LPC32x0 has seven AHB masters: the CPU data bus, CPU instruction bus, two general purpose DMA masters, Ethernet controller, USB controller, and LCD controller. The AHB masters access external memory through the EMC on one of three AHB slave ports. A block diagram of how the LPC32x0 bus masters connect to the EMC through the Multi-layer AHB interconnect matrix is shown in Fig 1. The EMC translates AHB master requests on the slave AHB ports for access to external memory into commands and data transactions that follow the selected memory protocol.

## 2.1 EMC pins

The EMC supports an SDR SDRAM memory bus of either 16 or 32-bits wide or DDR SDRAM bus of 16 bits. Additional signals are required for DDR SDRAM, which are brought out on the same pins as EMC\_D[16:18]. In DDR mode, EMC\_D bits 19 through 31 may be used as additional parallel I/O pins P3[12:0]. The function of each EMC pin for static memory, SDR SDRAM and DDR SDRAM is shown in Table 1. The EMC supports mixing static memory devices with either SDR SDRAM or DDR SDRAM on the same system memory bus. The static memory data bus width may be 8-bit, 16-bit or 32-bit when mixed with SDR SDRAM, but is limited to 8-bit or 16-bit when mixed with DDR SDRAM are not allowed to be mixed on the EMC bus.

AN10935

| EMC Interface Pin(s)            | Static RAM function         | SDR SDRAM function                   | DDR SDRAM function                   |

|---------------------------------|-----------------------------|--------------------------------------|--------------------------------------|

| EMC_A[00] - EMC_A[12]           | Address bus, bits 0 to 12   | Address bus, bits 0 to 12            | Address bus, bits 0 to 12            |

| EMC_A[13]                       | Address bus, bit 13         | Address bus, BA 0                    | Address bus, BA 0                    |

| EMC_A[14]                       | Address bus, bit 14         | Address bus, BA 1                    | Address bus, BA 1                    |

| EMC_A[15] - EMC_A[23]           | Address bus, bit 15 to 23   | -                                    | -                                    |

| EMC_D[00] - EMC_D[15]           | Data bus, bits 0 to 15      | Data bus, bits 0 to 15               | Data bus, bits 0 to 15               |

| EMC_D[16]/EMC_DQS0              | Data bus, bit 16            | Data bus, bit 16                     | Data strobe, lower byte              |

| EMC_D[17]/EMC_DQS1              | Data bus, bit 17            | Data bus, bit 17                     | Data strobe, upper byte              |

| EMC_D[18]/EMC_CLK_N             | Data bus, bit 18            | Data bus, bit 18                     | Inverted SDRAM clock                 |

| EMC_D[19] - EMC_D[31]           | Data bus bits 19 through 31 | Data bus bits 19 through 31          | P3[12:0]                             |

| EMC_OE_N                        | SRAM Output Enable          | -                                    | -                                    |

| EMC_BLS[0] - EMC_BLS[3]         | SRAM byte lane select 0-3   | -                                    | -                                    |

| EMC_CS[0]_N - EMC_CS[3]_N       | SRAM chip select 0-3        | -                                    | -                                    |

| EMC_WR_N                        | SRAM write strobe           | SDRAM write strobe                   | SDRAM write strobe                   |

| EMC_CLK                         | -                           | SDRAM clock                          | SDRAM clock                          |

| EMC_CLKIN                       | -                           | SDRAM clock feedback                 | -                                    |

| EMC_CKE                         | -                           | SDRAM clock enable                   | SDRAM clock enable                   |

| EMC_DYCS[0]_N,<br>EMC_DYCS[1]_N | -                           | SDRAM chip select 0-1                | SDRAM chip select 0-1                |

| EMC_CAS_N                       | -                           | SDRAM column<br>address strobe       | SDRAM column<br>address strobe       |

| EMC_RAS_N                       | -                           | SDRAM row<br>address strobe          | SDRAM row<br>address strobe          |

| EMC_DQM[0] - EMC_DQM[3]         | -                           | SDRAM byte write mask<br>0 through 3 | SDRAM byte write mask<br>0 through 3 |

#### Table 1. EMC pins in SRAM, SDR and DDR operating modes

## 2.2 Maximum system SDRAM memory

The LPC32x0 supports two dynamic memory chip selects. EMC DYCS[1:0] N. Each chip select addresses 512 MB. However, the largest density SDRAM device supported by the EMC is limited by 13 row address bits (8K rows), making the largest compatible SDRAM devices the 1 Gbit device configured as 32M x 32 or 512 Mbit configured as 16M x 32, 32M x 16 or 64M x 8. Using these compatible SDRAM configurations the maximum amount of SDRAM that can be physically supported per chip select is limited to 256 MB, 128 MB or 64 MB depending on the data width of the SDRAM device(s) and the total bus width of the system memory. The LPC32xx EMC supports a 32-bit system memory bus for SDR, but supports only a 16-bit system memory bus for DDR. Using DDR will limit the memory to half that of a comparable SDR system. Mobile SDR and Mobile DDR SDRAM devices are not produced in x8 data width, hence using Mobile/Low Power SDRAM (1.8 V) will limit the system memory to half that of a comparable standard SDRAM (2.5 V/3.3 V) system. The maximum SDR memory configurations per chip select is shown in Table 2, and the maximum DDR configurations per chip select are shown in Table 3. A system using both chip selects will support twice the memory listed in Table 2 or Table 3. The SDRAM address ranges are shown using x8, x16 and x32 memory devices in Table 4.

| 32-bit System Me     | mory SDR SDRAM |                        |                 |                   |

|----------------------|----------------|------------------------|-----------------|-------------------|

| Memory type          | Example SDRAM  | SDRAM density          | Devices<br>used | Maximum<br>memory |

| Standard (3.3 V)     | MT48LC64M8A2P  | 512 Mbit (64M x 8)     | 4               | 256 MB            |

| Low power<br>(1.8 V) | MT48H32M16LFBF | 512 Mbit (32M x<br>16) | 2               | 128 MB            |

| Low power<br>(1.8 V) | H55S1G22MFP    | 1 Gbit (32M x 32)      | 1               | 128 MB            |

| 16-bit System Me     | mory SDR SDRAM |                        |                 |                   |

| Memory type          | Example SDRAM  | SDRAM density          | Devices<br>used | Maximum<br>memory |

| Standard (3.3 V)     | MT48LC64M8A2P  | 512 Mbit (64M x 8)     | 2               | 128 MB            |

| Low power<br>(1.8 V) | MT48H32M16LFBF | 512 Mbit (32M x<br>16) | 1               | 64 MB             |

#### Table 2. Maximum SDR SDRAM per chip select

#### Table 3. Maximum DDR SDRAM per chip select

16 bit System Memory DDB SDBAN

| To-bit System we     | HIORY DDK SDKAW |                        |              |                   |

|----------------------|-----------------|------------------------|--------------|-------------------|

| Memory type          | Example SDRAM   | SDRAM density          | Devices used | Maximum<br>memory |

| Standard (2.5 V)     | MT46V64M8P      | 512 Mbit (64M x 8)     | 2            | 128 MB            |

| Low power<br>(1.8 V) | MT46H32M16LFBF  | 512 Mbit (32M x<br>16) | 1            | 64 MB             |

| Chip select   | AHB Address                | -                               |                                | Address range<br>X32 System da  | y)                              |                                |

|---------------|----------------------------|---------------------------------|--------------------------------|---------------------------------|---------------------------------|--------------------------------|

|               |                            | 512 Mbit<br>SDRAM<br>(32M x 16) | 512 Mbit<br>SDRAM<br>(64M x 8) | 512 Mbit<br>SDRAM<br>(16M x 32) | 512 Mbit<br>SDRAM<br>(32M x 16) | 512 Mbit<br>SDRAM<br>(64M x 8) |

|               |                            | 64 MB                           | 128 MB                         | 64 MB                           | 128 MB                          | 256 MB                         |

| EMC_DYCS[1]_N | 0xBFFF FFFF<br>0xA000 0000 | 0xA3FF FFFF<br>0xA000 0000      | 0xA7FF FFFF<br>0xA000 0000     | 0xA3FF FFFF<br>0xA000 0000      | 0xA7FF FFFF<br>0xA000 0000      | 0xAFFF FFFF<br>0xA000 0000     |

| EMC_DYCS[0]_N | 0x9FFF FFFF<br>0X8000 0000 | 0x83FF FFFF<br>0x8000 0000      | 0x87FF FFFF<br>0x8000 0000     | 0x83FF FFFF<br>0x8000 0000      | 0x87FF FFFF<br>0x8000 0000      | 0x8FFF FFFF<br>0x8000 0000     |

#### Table 4. Physical SDRAM address mapping

### 2.3 Contiguous SDRAM across EMC\_DYCS0 and EMC\_DYCS1

Sometimes to have enough system memory both EMC\_DYCS0 and EMC\_DYCS1 must be used. Since the physical SDRAM addressing range will always be smaller than the AHB address range allotted to EMC\_DYCS0, as shown in <u>Table 4</u>, the physical SDRAM will have mirrored address ranges across the full EMC\_DYCS0 space. To make the memory appear contiguous the EMC\_DYCS0 SDRAM can be addressed at the largest mirrored address space. For example if a 32Mx16 Mobile DDR were placed on each EMC\_DYCSx, the contiguous address range for the combined memories would be 0x9C00 0000 to 0xA3FF FFFF.

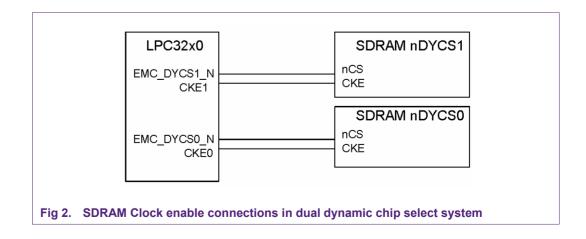

#### 2.4 SDRAM clock enable when using EMC\_DYCS0 and EMC\_DYCS1

For systems using both chip selects, EMC\_DYCS0\_N and EMC\_DYCS1\_N, the LPC32x0 signal CKE0 should be connected to all SDRAMs on EMC\_DYC0\_N and signal CKE1 should be connected to all SDRAMs on EMC\_DYC1\_N as shown in Fig 2. This will enable SDRAMs on both chip selects to be placed in self-refresh mode, and will allow use of the Dynamic memory clock enable bit in the EMCDynamicControl register to negate clock enable of an idle dynamic chip select to reduce overall system power. This applies to SDRAM, Mobile SDRAM, DDR and Mobile DDR alike.

## 2.5 SDR SDRAM connections

The LPC32x0 EMC supports either a 16-bit wide or 32-bit wide system SDR SDRAM bus. The system SDR SDRAM bus may be constructed with:

- one 32-bit wide SDR SDRAM

- one or two 16-bit wide SDR SDRAMs

- two or four 8-bit wide SDR SDRAMs

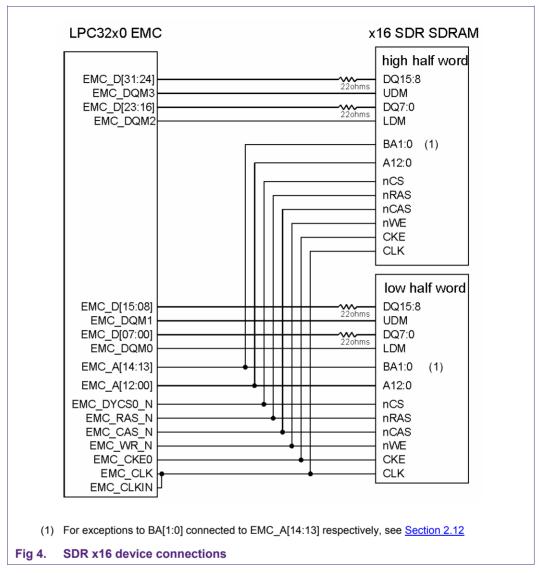

Connections to a single x32 SDR SDRAM is shown in Fig 3. Using a single x32 SDR the maximum memory for each EMC\_DYCS[1:0]\_N is 64 MB (16M x 32). A 32-bit system data bus using two x16 SDR SDRAMs is shown in Fig 4. Using two x16 SDRs the maximum memory for each EMC\_DYCS[1:0]\_N is 128 MB (two 32M x 16). Using four x8 SDRs the maximum memory for each EMC\_DYCS[1:0]\_N is 256 MB (four 64M x 8).

|        | LPC32x0 EMC                                                                                                                                            | C x32                                                                                                                                                   | 2 SDR SDRAM                                                                     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|        | LPC32x0 EMC<br>EMC_D[31]<br>EMC_D[24]<br>EMC_DQM3<br>EMC_D[23]<br>EMC_D[16]<br>EMC_DQM2<br>EMC_D[15]<br>EMC_D[08]<br>EMC_DQM1<br>EMC_DQM1<br>EMC_D[07] | 220hms<br>220hms<br>220hms<br>220hms<br>220hms<br>220hms<br>D<br>220hms<br>D<br>220hms<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D | 2 SDR SDRAM<br>Q31<br>Q24<br>QM3<br>Q23<br>Q16<br>QM2<br>Q15<br>Q8<br>QM1<br>Q7 |

|        | EMC_D[00]<br>EMC_DQM0                                                                                                                                  | 220hms D                                                                                                                                                | Q0<br>QM0                                                                       |

|        | EMC_A[14]<br>EMC_A[13]<br>EMC_A[12]<br>EMC_A[00]<br>EMC_DYCS0_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CKE0<br>EMC_CLK<br>EMC_CLK               | B/<br>A<br>:<br>:<br>A(                                                                                                                                 | A1 (1)<br>A0 (1)<br>12<br>0<br>CS<br>RAS<br>CAS<br>ME<br>KE<br>LK               |

| (1)    | For exceptions to B                                                                                                                                    | BA[1:0] connected to EMC_A[14:13] respectively, s                                                                                                       | see Section 2.12                                                                |

| Fig 3. | SDR x32 device                                                                                                                                         | connections                                                                                                                                             |                                                                                 |

#### 2.5.1 Routing rules for SDR SDRAM

When using multiple SDR SDRAM configurations it is best to place all memories near each other and route address, control and clock signals in a "Y" topology. Keep as much of the overall trace length in the trunk of the "Y" as possible, and the length to each device after the split as short as possible. Match the trace length to each device to within 0.3".

Rule 1: match EMC\_Data[7:0], EMC\_DQM0 to within 0.3 inches of each other.

Rule 2: match EMC\_Data[15:8], EMC\_DQM1 to within 0.3 inches of each other.

Rule 3: match EMC\_Data[23:16], EMC\_DQM2 to within 0.3 inches of each other.

Rule 4: match EMC\_Data[31:24], EMC\_DQM3 to within 0.3 inches of each other.

Rule 5: match signal groups from rule 1 through rule 4 to within 1.0 inches of each other.

Rule 6: match EMC\_CLK to within +-0.30 inches of signal groups rule 1 through rule 4.

Rule 7: match EMC\_A[14:0], EMC\_RAS, EMC\_CAS, EMC\_DYCS[1:0]\_N, EMC\_WR\_N, EMC\_CKE[1:0] to within +- 0.500 inches of EMC\_CLK.

## 2.5.2 Function of EMC\_CLKIN pin

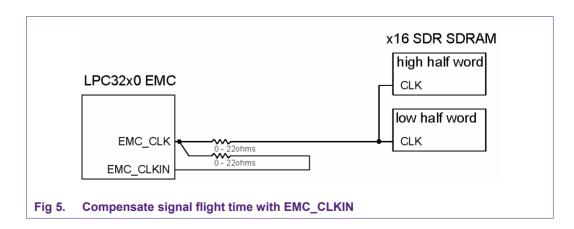

The EMC\_CLKIN pin is the MPMC data-in-clock during SDR SDRAM reads. After a SDR SDRAM read command is issued, the MPMC will latch burst data on the rising edge of EMC\_CLKIN after the number of CAS latency clock cycles has elapsed (see UM EMCDynamicRasCas). An external clock pin provides a way to compensate for signal flight delay times when the SDR SDRAM is placed far enough from the LPC32x0 that data being read does not arrive in time to meet the EMC SDR SDRAM tsu(D) data input set-up time for the tck EMC\_CLK period. Most embedded system designs can tie EMC\_CLKIN (bga ball T4) directly to the EMC\_CLK pin (bga ball T3).

Here's an example of how long the traces can be before needing to route EMC\_CLKIN differently than just connecting directly to the adjacent EMC\_CLK pin.

Example Parameters:

- SDR SDRAM maximum access time = 5.4 ns (SDRAM datasheet)

- LPC32x0 tsu(D) data in set-up time = 0.6 ns

- EMC-CLK period tck = 7.5 ns; (133 MHz)

The allowed combined flight time and board signal jitter must be less than the EMC\_CLK period minus the combined SDRAM access time and LPC32x0 data in set-up time. Therefore, flight + jitter = 7.5 ns - 6 ns = 1.5 ns. Reserving 300 ps for jitter leaves 1.2 ns for round trip flight time. Assuming the signal travels on the PCB at 167 ps/inch we can have a total trace length of 600 ps/167 ps = 3.6 inches between the LPC32x0 and the SDR SDRAM. The allowable trace length without compensation will increase as the EMC\_CLK period increases. With an EMC\_CLK period of 9.6 ns (104 MHz), the allowable trace length would be 9.9 inches.

#### 2.5.2.1 EMC\_CLKIN to compensate for long flight times

To compensate flight delay times longer than will work for a given tck period and SDR SDRAM access time, the EMC\_CLK is split routed with equal length traces to the SDR SDRAM and EMC\_CLKIN each with a series source termination, as shown in Fig 5. The series termination resistor value is dependent on the PCB trace characteristic impedance. The 0 ohm termination is used when the trace impedance is near 50 ohms, while 22 ohms is used when trace impedance is near 75 ohms. The extra trace length to EMC\_CLKIN compensates for one way signal flight time. So the example above would now meeting timing with up to 7.2 inches of trace length with tck = 7.5 ns.

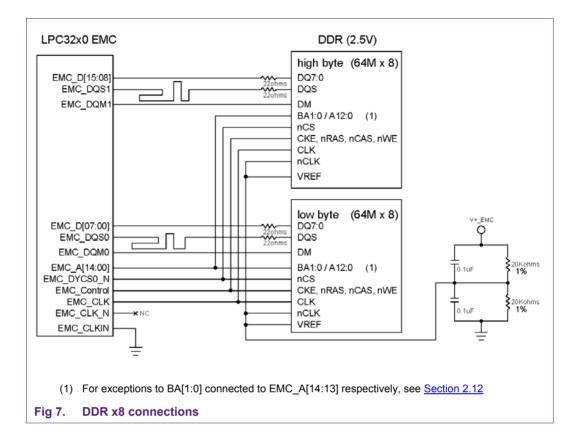

## 2.6 DDR SDRAM connections

The LPC32x0 EMC supports only a 16-bit wide system DDR SDRAM bus. The system DDR SDRAM bus may be constructed with:

- one 16-bit wide DDR SDRAM

- two 8-bit wide DDR SDRAMs

Connections to a single x16 DDR SDRAM are shown in Fig 6. Using a single x16 DDR, the maximum memory for each EMC\_DYCS[1:0]\_N is 64 MB (32M x 16). A 16-bit system data bus using two x8 DDR SDRAMs is shown in Fig 7. Using two x8 DDRs, the maximum memory for each EMC\_DYCS[1:0]\_N is 128 MB (two 64M x 8). Connections to a single x16 Mobile DDR SDRAM is shown in Fig 8. Please see the LPC32xx errata DDR.1 for using a single ended clock with 2.5V DDR, and DDR.2 for routing DQSx to increase DDR Dx to DQx data output set-up time. The Errata sheet can be found at http://www.nxp.com/documents/errata\_sheet/ES\_LPC3250.pdf.

| LPC32x0 EMC                                                                                                                                                         |                                                           | DDR (2.5V)                                                                                          |                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| EMC_D[15]<br>EMC_D[08]<br>EMC_DQM1<br>EMC_DQS1                                                                                                                      | 22ohms<br>22ohms<br>22ohms<br>22ohms<br>22ohms            | DQ15<br>DQ8<br>UDM<br>UDQS                                                                          |                                                                           |

| EMC_D[07] -<br>EMC_D[00] -<br>EMC_DQM0-<br>EMC_DQS0 -                                                                                                               | 22ohms<br>22ohms<br>22ohms<br>22ohms<br>22ohms            | DQ7<br>DQ0<br>LDM<br>LDQS                                                                           |                                                                           |

| EMC_A[14]<br>EMC_A[13]<br>EMC_A[12]<br>EMC_A[00]<br>EMC_DYCS0_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CKE0<br>EMC_CKE0<br>EMC_CLK<br>EMC_CLK_N<br>EMC_CLKIN | × NC                                                      | BA1 (1)<br>BA0 (1)<br>A12<br>A0<br>nCS<br>nRAS<br>nCAS<br>nCAS<br>nWE<br>CKE<br>CLK<br>nCLK<br>VREF | V+_EMC<br>0.1uF<br>0.1uF<br>0.1uF<br>1%<br>20Kohms<br>1%<br>20Kohms<br>1% |

| .,                                                                                                                                                                  | tions to BA[1:0] connected to EMC_A[14 device connections | :13] respectively,                                                                                  | see <u>Section 2.12</u>                                                   |

#### Using SDR/DDR SDRAM memories with LPC32xx

| LPC32x0 EMC                                                                                                                                                                                                                                                                      | N                                                                  | lobile DDR (1.8V)                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| EMC_D[15]<br>EMC_D[08]<br>EMC_DQM1<br>EMC_DQS1<br>EMC_DQS1<br>EMC_D[00]<br>EMC_DQ00<br>EMC_DQM0<br>EMC_DQS0<br>EMC_A[14]<br>EMC_A[13]<br>EMC_A[13]<br>EMC_A[12]<br>:<br>EMC_A[12]<br>:<br>EMC_A[10]<br>EMC_DYCS0_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CAS_N<br>EMC_CKE0<br>EMC_CLK | 22ohms<br>22ohms<br>22ohms<br>22ohms<br>22ohms<br>22ohms<br>22ohms | DQ15<br>DQ8<br>UDM<br>UDQS<br>DQ7<br>DQ0<br>LDM<br>LDQS<br>BA1 (1)<br>BA0 (1)<br>A12<br>A0<br>nCS<br>nRAS<br>nCAS<br>nVE<br>CKE<br>CLK<br>nCLK |

| (1) For exceptions to BA[                                                                                                                                                                                                                                                        | <br>[1:0] connected to EMC_A[14:13] respectivel                    | y, see <u>Section 2.12</u>                                                                                                                     |

| Fig 8. Mobile DDR x16 d                                                                                                                                                                                                                                                          | evice connections                                                  |                                                                                                                                                |

## 2.7 Routing rules for DDR SDRAM

When using multiple DDR SDRAM configurations it is best to place all memories near each other and route address, control and clock signals in a "Y" topology with as much of the overall trace length in the trunk of the "Y" keeping the length to each device after the split as short as possible while matching trace length to each device within 0.15". Please see the LPC32xx Errata DDR.2 for routing DQSx to increase DDR Dx to DQx data output set-up time.

Rule 1: match EMC\_Data[7:0], EMC\_DQM0 to within 0.15 inches of each other.

Rule 1a: EMC\_DQS0, should be a minimum of 2.0" longer, but not more than 4.0" longer than EMC\_Data[7:0], EMC\_DQM0.

Rule 2: match EMC\_Data[15:8], EMC\_DQM1 to within 0.15 inches of each other.

Rule 2a: EMC\_DQS1 should be a minimum of 2.0" longer, but not more than 4.0" longer than EMC\_Data[15:8], EMC\_DQM1.

Rule 3: match signal groups from rule 1 and rule 2 to within 0.50 inches of each other.

Rule 4: match EMC\_CLK and DDR\_NCLK to within +-0.30 inches of signal groups from rule 1 and rule 2. EMC\_CLK and DDR\_NCLK together make a differential pair and

should be matched length to within 0.150 inches of each other. Note: please see the LPC32xx Errata DDR.1 for using a single ended clock for 2.5V DDR.

Rule 5: match EMC\_A[14:0], EMC\_RAS, EMC\_CAS, EMC\_DYCS[1:0]\_N, EMC\_WR\_N, EMC\_CKE[1:0] to within +- 0.500 inches of EMC\_CLK.

#### 2.7.1 Function of EMC\_CLKIN pin

EMC\_CLKIN is not used for DDR SDRAM configurations and should be tied to gnd or VDD\_EMC.

## 2.8 SDRAM layout optimization

Configuring the system memory using a single chip select for SDRAM instead of two dynamic chip selects will help keep the routing for DQ[31:0], DQM[3:0] and DQS[1:0] signals point to point, a good topology for signal integrity. For example, placing two 512 Mbit (64M x 8) DDR devices on a single chip select for 128 MB of system memory is more desirable than building the same system using two chip selects, each with a 512 Mbit (32M x 16) device.

### 2.9 Shared bus placement for SDRAM and Static memory devices

It is best if the SDR/DDR SDRAM is routed point-to-point between the LPC3250. If the LPC3250 EMC bus is shared between SDRAM and static memory, NOR Flash, or memory mapped IO devices, it is recommended to buffer the static memory and memory mapped IO devices keeping just the SDRAM memory and buffer directly connected to the LPC3250. When it is necessary to have an additional device on the EMC bus it is recommended to place the LPC32xx at one extreme on the bus and the SDRAM at the other extreme. The additional NOR Flash or buffer should be place nearer to the SDRAM and the bus routed in daisy chain fashion with stubs no longer than 0.3".

## 2.10 Address mapping between AHB address and SDR/DDR SDRAM

The SDRAM memory is arranged in a XY grid pattern of rows and columns. First, the row address is sent to the memory chip and latched, then the column address is sent in a similar fashion. This row and column-addressing scheme (called multiplexing) allows a large memory address to use fewer pins. The EMC uses EMCDynamicConfig register Address Mapping (AM) field to map the AHB address for a specific SDRAM bank, row and column configuration. The value for the EMCDynamicConfig AM field, for each SDRAM configuration, is found in the LPC32xx User Manual "UM10326" Table 115 Address mapping. The EMC uses the AM field bits 13:12 to determine the order in which the SDRAM bank, row and column address bits are mapped to the AHB address bits. The EMC will always map the least significant AHB address bits to the SDRAM column address. When the AM field bits 13:12 = 0b01 (low-power mapping) the SDRAM row address is mapped to the next significant group of AHB address bits and the SDRAM bank address bits are mapped to the most significant AHB address bits. This is also referred to as Bank-Row-Column (BRC) mapping. When AM field bits 13:12 = 0b00 (high performance mapping) the SDRAM bank address bits are mapped to the next significant AHB address bits after the column address and the SDRAM row address is mapped to the most significant AHB address bits. This is also referred to as Row-Bank-Column (RBC) mapping. The detailed AHB address mapping for 16-bit system memory data bus is shown in Table 5 and Table 6. The detailed AHB address mapping for 32-bit system memory data bus is shown in Table 7 and Table 8. Each EMC DYNCS[1:0] N has its own EMCDynamicConfig register, so each chip select may use a different SDRAM

density with different row and column configuration. The MPMC maps the SDRAM Auto precharge bit to EMC\_A10 during SRAM read, write and precharge commands.

#### Table 5. 16-bit wide system data bus high performance AHB address mapping to SDRAM pins (RBC)

#### 16-bit wide system data bus high performance AHB address mapping to SDRAM pins (Row, Bank, Column)

2 MB using 16-bit wide device 16 Mbit SDR/DDR SDRAM (1M x 16) RBC (banks = 2, rows = 11, columns = 8)

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12    | 11             | 10         | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

|----------------------------------|-----------|-----------|-------|----------------|------------|--------|--------|--------|-------|---------------|---------------|------|-------|------------|----|

| AHB address to row address       | 9         | -         | -     | -              | 20         | 19     | 18     | 17     | 16    | 15            | 14            | 13   | 12    | 11         | 10 |

| AHB address to column address    | 9         | -         | -     | -              | AP         | -      | -      | 8      | 7     | 6             | 5             | 4    | 3     | 2          | 1  |

| SDRAM device connections         | BA        | -         | -     | -              | 10/AP      | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| 4 MB using two 8-bit wide device | es 16 Mbi | t SDR/DI  | DR SD | RAM            | (2M x 8) R | BC (b  | anks   | ; = 2, | row   | /s = '        | 11, c         | olur | nns   | = 9)       |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12    | 11             | 10         | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| AHB address to row address       | -         | 10        | -     | -              | 21         | 20     | 19     | 18     | 17    | 16            | 15            | 14   | 13    | 12         | 11 |

| AHB address to column address    | -         | 10        | -     | -              | AP         | -      | 9      | 8      | 7     | 6             | 5             | 4    | 3     | 2          | 1  |

| SDRAM device connections         | -         | BA        | -     | -              | 10/AP      | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| 8 MB using 16-bit wide device 64 | Mbit SD   | R/DDR S   | DRAN  | <b>1 (4M</b> : | x 16) RBC  | (banl  | (s = 4 | 4, ro  | ws =  | • <b>12</b> , | colu          | Imns | s = 8 | )          |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12    | 11             | 10         | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| AHB address to row address       | 9         | 10        | -     | 22             | 21         | 20     | 19     | 18     | 17    | 16            | 15            | 14   | 13    | 12         | 11 |

| AHB address to column address    | 9         | 10        | -     | -              | AP         | -      | -      | 8      | 7     | 6             | 5             | 4    | 3     | 2          | 1  |

| SDRAM device connections         | BA1       | BA0       | -     | -              | 10/AP      | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| 16 MB using two 8-bit wide devic | ces 64 Mb | oit SDR/E | DDR S | DRAM           | I (8M x 8) | RBC (  | bank   | s = 4  | 4, ro | ws =          | • <b>12</b> , | colu | imns  | ; = 9)     | )  |

| 16 MB using 16-bit wide device 1 | 28 Mbit S | SDR/DDF   |       | AM (8          | M x 16) RE | BC (ba | anks   | = 4,   | row   | s = 1         | 2, co         | olum | ins = | <b>9</b> ) |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12    | 11             | 10         | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

| AHB address to row address       | 11        | 10        | -     | 23             | 22         | 21     | 20     | 19     | 18    | 17            | 16            | 15   | 14    | 13         | 12 |

| AHB address to column address    | 11        | 10        | -     | -              | AP         | -      | 9      | 8      | 7     | 6             | 5             | 4    | 3     | 2          | 1  |

| SDRAM device connections         | BA1       | BA0       | -     | -              | 10/AP      | 9      | 8      | 7      | 6     | 5             | 4             | 3    | 2     | 1          | 0  |

|                                  |           |           |       |                |            |        |        |        |       |               |               |      |       |            |    |

AN10935

| Table 5. 16-bit wide system data        | bus hig  | h perfor | mance | AHB   | address    | mappi   | ng to | SDI   | RAM   | pin          | s (RI | 3C) . | cor   | ntinu | ed  |

|-----------------------------------------|----------|----------|-------|-------|------------|---------|-------|-------|-------|--------------|-------|-------|-------|-------|-----|

| 32 MB using two 8-bit wide devic        | es 128 N | /bit SDR | /DDR  | SDRA  | M (16M x   | 8) RB(  | C (ba | nks   | = 4,  | row          | s = 1 | 2, co | olum  | ns =  | 10) |

| LPC address pin, EMC_A[14:0]            | 14       | 13       | 12    | 11    | 10         | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| AHB address to row address              | 11       | 12       | -     | 24    | 23         | 22      | 21    | 20    | 19    | 18           | 17    | 16    | 15    | 14    | 13  |

| AHB address to column address           | 11       | 12       | -     | -     | AP         | 10      | 9     | 8     | 7     | 6            | 5     | 4     | 3     | 2     | 1   |

| SDRAM device connections                | BA1      | BA0      | -     | -     | 10/AP      | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| 32 MB using 16-bit wide device 2        | 56 Mbit  | SDR/DDI  | R SDR | AM (1 | 6M x 16) I | RBC (b  | banks | s = 4 | , rov | vs =         | 13, ( | colu  | mns   | = 9)  |     |

| LPC address pin, EMC_A[14:0]            | 14       | 13       | 12    | 11    | 10         | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| AHB address to row address              | 11       | 10       | 24    | 23    | 22         | 21      | 20    | 19    | 18    | 17           | 16    | 15    | 14    | 13    | 12  |

| AHB address to column address           | 11       | 10       | -     | -     | AP         | -       | 9     | 8     | 7     | 6            | 5     | 4     | 3     | 2     | 1   |

| SDRAM device connections                | BA1      | BA0      | -     | -     | 10/AP      | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| 64 MB using 16-bit wide device 5        | 12 Mbit  | SDR/DDI  | R SDR | AM (3 | 2M x 16) I | RBC (k  | banks | s = 4 | , rov | vs =         | 13, ( | colu  | mns   | = 10  | )   |

| 64 MB using two 8-bit wide devic        | es 256 N | /bit SDR | /DDR  | SDRA  | M (32M x   | 8) RB(  | C (ba | nks   | = 4,  | row          | s = 1 | 3, co | olum  | ns =  | 10) |

| LPC address pin, EMC_A[14:0]            | 14       | 13       | 12    | 11    | 10         | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| AHB address to row address              | 11       | 12       | 25    | 24    | 23         | 22      | 21    | 20    | 19    | 18           | 17    | 16    | 15    | 14    | 13  |

| AHB address to column address           | 11       | 12       | -     | -     | AP         | 10      | 9     | 8     | 7     | 6            | 5     | 4     | 3     | 2     | 1   |

| SDRAM device connections                | BA1      | BA0      | -     | -     | 10/AP      | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| 128 MB using two 8-bit wide devi<br>11) | ces 512  | Mbit SD  | R/DDF | SDR   | AM (64M )  | k 8) RE | BC (b | anks  | s = 4 | , <b>rov</b> | vs =  | 13, ( | colui | nns   | =   |

| LPC address pin, EMC_A[14:0]            | 14       | 13       | 12    | 11    | 10         | 9       | 8     | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0   |

| AHB address to row address              | 13       | 12       | 26    | 25    | 24         | 23      | 22    | 21    | 20    | 19           | 18    | 17    | 16    | 15    | 14  |

| AHB address to column address           | 13       | 12       | -     | 11    | AP         | 10      | 9     | 8     | 7     | 6            | 5     | 4     | 3     | 2     | 1   |

|                                         |          |          |       |       |            |         |       |       |       |              |       |       |       |       |     |

| Table 6.16-bit wide system d16-bit wide system data bus low |           |          |       |       |            | Ŭ       |        |        |       | •      | 1     | <b>n</b> ) |        |        |    |

|-------------------------------------------------------------|-----------|----------|-------|-------|------------|---------|--------|--------|-------|--------|-------|------------|--------|--------|----|

| 2 MB using 16-bit wide device 1                             |           |          |       |       |            |         |        |        |       |        |       |            | s = 8] | )      |    |

| LPC address pin, EMC_A[14:0]                                | 14        | 13       | 12    | 11    | 10         | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| AHB address to row address                                  | -         | 20       | -     | -     | 19         | 18      | 17     | 16     | 15    | 14     | 13    | 12         | 11     | 10     | 9  |

| AHB address to column address                               | -         | 20       | -     | -     | AP         | -       | -      | 8      | 7     | 6      | 5     | 4          | 3      | 2      | 1  |

| SDRAM device connections                                    | -         | BA       | -     | -     | 10/AP      | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| 4 MB using two 8-bit wide devic                             | es 16 Mb  | it SDR/D | DR SD | RAM   | (2M x 8) E | BRC (b  | anks   | s = 2, | , row | /s = ' | 11, c | olun       | nns    | = 9)   |    |

| LPC address pin, EMC_A[14:0]                                | 14        | 13       | 12    | 11    | 10         | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| AHB address to row address                                  | 21        | -        | -     | -     | 20         | 19      | 18     | 17     | 16    | 15     | 14    | 13         | 12     | 11     | 10 |

| AHB address to column address                               | 21        | -        | -     | -     | AP         | -       | 9      | 8      | 7     | 6      | 5     | 4          | 3      | 2      | 1  |

| SDRAM device connections                                    | BA        | -        | -     | -     | 10/AP      | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| 8 MB using 16-bit wide device 6                             | 4 Mbit S  | DR/DDR   | SDRAM | И (4M | x 16) BR(  | C (banl | ks = 4 | 4, ro  | ws =  | 12,    | colu  | imns       | s = 8  | )      | •  |

| LPC address pin, EMC_A[14:0]                                | 14        | 13       | 12    | 11    | 10         | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| AHB address to row address                                  | 21        | 22       | -     | 20    | 19         | 18      | 17     | 16     | 15    | 14     | 13    | 12         | 11     | 10     | 9  |

| AHB address to column address                               | 21        | 22       | -     | -     | AP         | -       | -      | 8      | 7     | 6      | 5     | 4          | 3      | 2      | 1  |

| SDRAM device connections                                    | BA1       | BA0      | -     | -     | 10/AP      | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| 16 MB using 16-bit wide device                              | 128 Mbit  | SDR/DD   | R SDR | AM (8 | M x 16) B  | RC (ba  | anks   | = 4,   | row   | s = 1  | 2, co | olum       | ins =  | : 9)   |    |

| 16 MB using two 8-bit wide devi                             | ices 64 M | bit SDR/ | DDR S | DRAN  | / (8M x 8) | BRC (   | bank   | (s = 4 | 4, ro | ws =   | 12,   | colu       | imns   | ; = 9) | )  |

| LPC address pin, EMC_A[14:0]                                | 14        | 13       | 12    | 11    | 10         | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| AHB address to row address                                  | 23        | 22       | -     | 21    | 20         | 19      | 18     | 17     | 16    | 15     | 14    | 13         | 12     | 11     | 10 |

| AHB address to column address                               | 23        | 22       | -     | -     | AP         | -       | 9      | 8      | 7     | 6      | 5     | 4          | 3      | 2      | 1  |

| SDRAM device connections                                    | BA1       | BA0      | -     | -     | 10/AP      | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

| 32 MB using 16-bit wide device                              | 256 Mbit  | SDR/DD   | R SDR | AM (1 | 6M x 16)   | BRC (b  | bank   | s = 4  | , rov | vs =   | 13, ( | colu       | mns    | = 9)   |    |

| LPC address pin, EMC_A[14:0]                                | 14        | 13       | 12    | 11    | 10         | 9       | 8      | 7      | 6     | 5      | 4     | 3          | 2      | 1      | 0  |

|                                                             | 00        | 24       | 22    | 21    | 20         | 19      | 18     | 17     | 16    | 15     | 14    | 13         | 12     | 11     | 40 |

| AHB address to row address                                  | 23        | 24       | 22    | 21    | 20         |         | -      |        |       |        |       |            | 14     |        | 10 |

| AHB address to row address<br>AHB address to column address | 23        | 24       | -     | -     | AP         | -       | 9      | 8      | 7     | 6      | 5     | 4          | 3      | 2      | 10 |

AN10935

| Table 6. 16-bit wide system data                                                                              | bus low  | -power   | AHB a | ddres | s mapping | g to SI | ORAN  | / pir | ıs (E | BRC) | co    | ontin | ued  |      |     |

|---------------------------------------------------------------------------------------------------------------|----------|----------|-------|-------|-----------|---------|-------|-------|-------|------|-------|-------|------|------|-----|

| 32 MB using two 8-bit wide devic                                                                              | es 128 N | Ibit SDR | /DDR  | SDRA  | M (16M x  | 8) BR(  | C (ba | nks   | = 4,  | row  | s = 1 | 2, co | olum | ns = | 10) |

| LPC address pin, EMC_A[14:0]                                                                                  | 14       | 13       | 12    | 11    | 10        | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

| AHB address to row address                                                                                    | 23       | 24       | -     | 22    | 21        | 20      | 19    | 18    | 17    | 16   | 15    | 14    | 13   | 12   | 11  |

| AHB address to column address                                                                                 | 23       | 24       | -     | -     | AP        | 10      | 9     | 8     | 7     | 6    | 5     | 4     | 3    | 2    | 1   |

| SDRAM device connections                                                                                      | BA1      | BA0      | -     | -     | 10/AP     | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

| 64 MB using 16-bit wide device 512 Mbit SDR/DDR SDRAM (32M x 16) BRC (banks = 4, rows = 13, columns = 10)     |          |          |       |       |           |         |       |       |       |      |       |       |      |      |     |

| 64 MB using two 8-bit wide devic                                                                              | es 256 N | lbit SDR | /DDR  | SDRA  | M (32M x  | 8) BR(  | C (ba | nks   | = 4,  | row  | s = 1 | 3, co | olum | ns = | 10) |

| LPC address pin, EMC_A[14:0]                                                                                  | 14       | 13       | 12    | 11    | 10        | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

| AHB address to row address                                                                                    | 25       | 24       | 23    | 22    | 21        | 20      | 19    | 18    | 17    | 16   | 15    | 14    | 13   | 12   | 11  |

| AHB address to column address                                                                                 | 25       | 24       | -     | -     | AP        | 10      | 9     | 8     | 7     | 6    | 5     | 4     | 3    | 2    | 1   |

| SDRAM device connections                                                                                      | BA1      | BA0      | -     | -     | 10/AP     | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

| 128 MB using two 8-bit wide devices 512 Mbit SDR/DDR SDRAM (64M x 8) BRC (banks = 4, rows = 13, columns = 11) |          |          |       |       |           |         |       |       |       |      |       |       |      |      |     |

| LPC address pin, EMC_A[14:0]                                                                                  | 14       | 13       | 12    | 11    | 10        | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

| AHB address to row address                                                                                    | 25       | 26       | 24    | 23    | 22        | 21      | 20    | 19    | 18    | 17   | 16    | 15    | 14   | 13   | 12  |

| AHB address to column address                                                                                 | 25       | 26       | -     | 11    | AP        | 10      | 9     | 8     | 7     | 6    | 5     | 4     | 3    | 2    | 1   |

| SDRAM device connections                                                                                      | BA1      | BA0      | -     | -     | 10/AP     | 9       | 8     | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0   |

Table 7.

32-bit wide system data bus high performance AHB address mapping to SDRAM pins (RBC)

32-bit wide system data bus high performance AHB address mapping to SDRAM pins (Row, Bank, Column)

| 4 MB using two 16-bit wide devic | es 16 | Mbit SDR | SDRAM | /I (1M | x 16) R | BC (ban | ks = | 2, ro | ows : | = 11, | , colı | umn | s = 8 | ) |   |

|----------------------------------|-------|----------|-------|--------|---------|---------|------|-------|-------|-------|--------|-----|-------|---|---|

| LPC address pin, EMC_A[14:0]     | 14    | 13       | 12    | 11     | 10      | 9       | 8    | 7     | 6     | 5     | 4      | 3   | 2     | 1 | 0 |

| AHB address to row address       | -       | 10     | -     | -     | 21       | 20      | 19     | 18   | 17    | 16    | 15  | 14   | 13 | 12 | 11 |

|----------------------------------|---------|--------|-------|-------|----------|---------|--------|------|-------|-------|-----|------|----|----|----|

| AHB address to column address    | -       | 10     | -     | -     | AP       | -       | -      | 9    | 8     | 7     | 6   | 5    | 4  | 3  | 2  |

| SDRAM device connections         | -       | BA     | -     | -     | 10/AP    | 9       | 8      | 7    | 6     | 5     | 4   | 3    | 2  | 1  | 0  |

| 8 MB using 32-bit wide device 64 | Mbit SD | R SDRA | M (2M | x 32) | RBC (bar | nks = 4 | l, rov | /s = | 11, c | colur | nns | = 8) |    |    | ·  |

| LPC address pin, EMC_A[14:0]     | 14      | 13     | 12    | 11    | 10       | 9       | 8      | 7    | 6     | 5     | 4   | 3    | 2  | 1  | 0  |

| AHB address to row address       | 11      | 10     | -     | -     | 22       | 21      | 20     | 19   | 18    | 17    | 16  | 15   | 14 | 13 | 12 |

| AHB address to column address    | 11      | 10     | -     | -     | AP       | -       | -      | 9    | 8     | 7     | 6   | 5    | 4  | 3  | 2  |

| SDRAM device connections         | BA1     | BA0    |       | _     | 10/AP    | 9       | 8      | 7    | 6     | 5     | 4   | 3    | 2  | 1  | 0  |

|                                  |           |           |        |        |             | (1      |        |               |       |       |       |       |       |      |    |

|----------------------------------|-----------|-----------|--------|--------|-------------|---------|--------|---------------|-------|-------|-------|-------|-------|------|----|

| 8 MB using four 8-bit wide devic | es 16 Mt  | oit SDR S | SDRAN  | 1 (2M  | x 8) RBC    | (banks  | = 2,   | row           | s = 1 | 1, C  | olum  | ins = | = 9)  |      |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12     | 11     | 10          | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address       | 11        | -         | -      | -      | 22          | 21      | 20     | 19            | 18    | 17    | 16    | 15    | 14    | 13   | 12 |

| AHB address to column address    | 11        | -         | -      | -      | AP          | -       | 10     | 9             | 8     | 7     | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections         | BA        | -         | -      | -      | 10/AP       | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| 16 MB using 32-bit wide device 1 | 28 Mbit   | SDR SD    | RAM (4 | 4M x 3 | 82) RBC (I  | oanks : | = 4, r | ows           | = 12  | 2, co | lumr  | ıs =  | 8)    |      |    |

| 16 MB using two 16-bit wide dev  | ices 64 l | Mbit SDF  | R SDRA | AM (41 | VI x 16) RE | BC (bai | nks =  | = 4, r        | ows   | = 12  | 2, co | lumr  | ıs =  | 8)   |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12     | 11     | 10          | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address       | 11        | 10        | -      | 23     | 22          | 21      | 20     | 19            | 18    | 17    | 16    | 15    | 14    | 13   | 12 |

| AHB address to column address    | 11        | 10        | -      | -      | AP          | -       | -      | 9             | 8     | 7     | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections         | BA1       | BA0       | -      | -      | 10/AP       | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| 32 MB using 32-bit wide device 2 | 256 Mbit  | SDR SD    | RAM (8 | BM x 3 | 82) RBC (I  | oanks : | = 4, r | ows           | = 12  | , co  | lumr  | ıs =  | 9)    |      |    |

| 32 MB using two 16-bit wide dev  | ices 128  | Mbit SD   | R SDR  | RAM (8 | 3M x 16) F  | RBC (ba | anks   | = 4,          | row   | s = 1 | 2, c  | olum  | nns = | = 9) |    |

| 32 MB using four 8-bit wide devi | ces 64 N  | Ibit SDR  | SDRA   | M (8N  | I x 8) RBC  | ; (bank | s = 4  | , <b>ro</b> v | vs =  | 12, 0 | colu  | mns   | = 9)  |      |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12     | 11     | 10          | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address       | 11        | 12        | -      | 24     | 23          | 22      | 21     | 20            | 19    | 18    | 17    | 16    | 15    | 14   | 13 |

| AHB address to column address    | 11        | 12        | -      | -      | AP          | -       | 10     | 9             | 8     | 7     | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections         | BA1       | BA0       | -      | -      | 10/AP       | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| 32 MB using 32-bit wide device 2 | 256 Mbit  | SDR SD    | RAM (  | 8M x 3 | 82) RBC (I  | oanks : | = 4, r | ows           | = 13  | , co  | lumr  | ıs =  | 8)    |      |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12     | 11     | 10          | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address       | 11        | 10        | 24     | 23     | 22          | 21      | 20     | 19            | 18    | 17    | 16    | 15    | 14    | 13   | 12 |

| AHB address to column address    | 11        | 10        | -      | -      | AP          | -       | -      | 9             | 8     | 7     | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections         | BA1       | BA0       | -      | -      | 10/AP       | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| 64 MB using 32-bit wide devices  | 512 Mbi   | t SDR S   | DRAM   | (16M   | x 32) RBC   | ; (bank | s = 4  | , <b>ro</b> v | vs =  | 13, ( | colu  | mns   | = 9)  |      |    |

| 64 MB using two 16-bit wide dev  | ices 256  | Mbit SE   |        | RAM (1 | I6M x 16)   | RBC (I  | bank   | s = 4         | , rov | vs =  | 13,   | colu  | mns   | = 9) |    |

| LPC address pin, EMC_A[14:0]     | 14        | 13        | 12     | 11     | 10          | 9       | 8      | 7             | 6     | 5     | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address       | 11        | 12        | 25     | 24     | 23          | 22      | 21     | 20            | 19    | 18    | 17    | 16    | 15    | 14   | 13 |

| AHB address to column address    | 11        | 12        | -      | -      | AP          | -       | 10     | 9             | 8     | 7     | 6     | 5     | 4     | 3    | 2  |

|                                  |           |           |        |        |             |         |        |               |       |       |       |       |       |      |    |

AN10935

| Table 7. 32-bit wide system data                                                                          | bus hig   | h perforr | nance  | AHB    | address r  | nappi  | ng to  | SD    | RAM   | pin    | s (RI | 3C)   | .con | tinu  | ed |

|-----------------------------------------------------------------------------------------------------------|-----------|-----------|--------|--------|------------|--------|--------|-------|-------|--------|-------|-------|------|-------|----|

| 64 MB using four 8-bit wide devic                                                                         | es 128 N  | /bit SDR  | SDR/   | AM (10 | 6M x 8) RE | BC (ba | nks    | = 4,  | rows  | s = 1: | 2, co | lum   | ns = | 10)   |    |

| LPC address pin, EMC_A[14:0]                                                                              | 14        | 13        | 12     | 11     | 10         | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| AHB address to row address                                                                                | 13        | 12        | -      | 25     | 24         | 23     | 22     | 21    | 20    | 19     | 18    | 17    | 16   | 15    | 14 |

| AHB address to column address                                                                             | 13        | 12        | -      | -      | AP         | 11     | 10     | 9     | 8     | 7      | 6     | 5     | 4    | 3     | 2  |

| SDRAM device connections                                                                                  | BA1       | BA0       | -      | -      | 10/AP      | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| 128 MB using 32-bit wide device                                                                           | 1 Gbit S  | DR SDR    | AM (32 | 2M x 3 | 2) RBC (b  | anks = | = 4, r | ows   | = 13  | , co   | lumr  | ıs =  | 10)  |       | ·  |

| 128 MB using two 16-bit wide dev                                                                          | vices 512 | 2 Mbit SE | OR SD  | RAM (  | (32M x 16) | RBC    | (ban   | ks =  | 4, ro | ows    | = 13  | , col | umn  | s = 1 | 0) |

| 128 MB using four 8-bit wide dev                                                                          | ices 256  | Mbit SD   | R SDF  | RAM (  | 32M x 8) R | BC (b  | anks   | ; = 4 | , row | /s = ' | 13, c | olur  | nns  | = 10) | )  |

| LPC address pin, EMC_A[14:0]                                                                              | 14        | 13        | 12     | 11     | 10         | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| AHB address to row address                                                                                | 13        | 12        | 26     | 25     | 24         | 23     | 22     | 21    | 20    | 19     | 18    | 17    | 16   | 15    | 14 |

| AHB address to column address                                                                             | 13        | 12        | -      | -      | AP         | 11     | 10     | 9     | 8     | 7      | 6     | 5     | 4    | 3     | 2  |

| SDRAM device connections                                                                                  | BA1       | BA0       | -      | -      | 10/AP      | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| 256MB using four 8-bit wide devices 512 Mbit SDR SDRAM (64M x 8) RBC (banks = 4, rows = 13, columns = 11) |           |           |        |        |            |        |        |       |       |        |       |       |      |       |    |

| LPC address pin, EMC_A[14:0]                                                                              | 14        | 13        | 12     | 11     | 10         | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| AHB address to row address                                                                                | 13        | 14        | 27     | 26     | 25         | 24     | 23     | 22    | 21    | 20     | 19    | 18    | 17   | 16    | 15 |

| AHB address to column address                                                                             | 13        | 14        | -      | 12     | AP         | 11     | 10     | 9     | 8     | 7      | 6     | 5     | 4    | 3     | 2  |

| SDRAM device connections                                                                                  | BA1       | BA0       | -      | -      | 10/AP      | 9      | 8      | 7     | 6     | 5      | 4     | 3     | 2    | 1     | 0  |

| Table 8. | 32-bit wide system data bus low-power AHB address mapping to SDRAM pins (BRC) |   |

|----------|-------------------------------------------------------------------------------|---|

|          |                                                                               | _ |

| 32-bit wide system data bus low-power AHB address mapping to SDRAM pins (Bank, Row, Column)                                                                                                                                                                             |    |    |    |    |       |    |    |    |    |    |    |    |    |    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|-------|----|----|----|----|----|----|----|----|----|----|

| 4 MB using two 16-bit wide device 16 Mbit SDR SDRAM (1M x 16) BRC (banks = 2, rows = 11, columns = 8)         LPC address pin, EMC A[14:0]       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0 |    |    |    |    |       |    |    |    |    |    |    |    |    |    |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                                                                            | 14 | 13 | 12 | 11 | 10    | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| AHB address to row address                                                                                                                                                                                                                                              | 21 | -  | -  | -  | 20    | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 |

| AHB address to column address                                                                                                                                                                                                                                           | 21 | -  | -  | -  | AP    | -  | -  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  |

| SDRAM device connections                                                                                                                                                                                                                                                | BA | -  | -  | -  | 10/AP | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Table 8. 32-bit wide system data                                                                                                                                                                               | bus low   | -power A   | HB a  | ddres  | s mapping   | to SI  | ORAN          | / pir         | ıs (B | RC)           | co    | ntin  | ued   |      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-------|--------|-------------|--------|---------------|---------------|-------|---------------|-------|-------|-------|------|----|

| 8 MB using 32-bit wide device 64                                                                                                                                                                               | Mbit SD   |            | M (2M | x 32)  | BRC (ban    | ks = 4 | , <b>ro</b> v | /s =          | 11, c | olur          | nns   | = 8)  |       |      |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                   | 14        | 13         | 12    | 11     | 10          | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address                                                                                                                                                                                     | 21        | 22         | -     | -      | 20          | 19     | 18            | 17            | 16    | 15            | 14    | 13    | 12    | 11   | 10 |

| AHB address to column address                                                                                                                                                                                  | 21        | 22         | -     | -      | AP          | -      | -             | 9             | 8     | 7             | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections                                                                                                                                                                                       | BA1       | BA0        | -     | -      | 10/AP       | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| 8 MB using four 8-bit wide device                                                                                                                                                                              | es 16 Mb  | it SDR S   | DRAM  | (2M)   | ( 8) BRC (I | banks  | = 2,          | row           | s = 1 | 1, co         | olum  | nns = | = 9)  |      |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                   | 14        | 13         | 12    | 11     | 10          | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address                                                                                                                                                                                     | -         | 22         | -     | -      | 21          | 20     | 19            | 18            | 17    | 16            | 15    | 14    | 13    | 12   | 11 |

| AHB address to column address                                                                                                                                                                                  | -         | 22         | -     | -      | AP          | -      | 10            | 9             | 8     | 7             | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections                                                                                                                                                                                       | -         | BA         | -     | -      | 10/AP       | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| 16 MB using 32-bit wide device 128 Mbit SDR SDRAM (4M x 32) BRC (banks = 4, rows = 12, columns = 8)<br>16 MB using two 16-bit wide devices 64 Mbit SDR SDRAM (4M x 16) BRC (banks = 4, rows = 12, columns = 8) |           |            |       |        |             |        |               |               |       |               |       |       |       |      |    |

| 16 MB using two 16-bit wide devi                                                                                                                                                                               | ces 64 N  | Ibit SDR   | SDRA  | M (4N  | I x 16) BR  | C (bar | ıks =         | 4, r          | ows   | = 12          | 2, co | lumr  | ıs =  | 8)   |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                   | 14        | 13         | 12    | 11     | 10          | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address                                                                                                                                                                                     | 23        | 22         | -     | 21     | 20          | 19     | 18            | 17            | 16    | 15            | 14    | 13    | 12    | 11   | 10 |

| AHB address to column address                                                                                                                                                                                  | 23        | 22         | -     | -      | AP          | -      | -             | 9             | 8     | 7             | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections                                                                                                                                                                                       | BA1       | BA0        | -     | -      | 10/AP       | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| 32 MB using 32-bit wide device 256 Mbit SDR SDRAM (8M x 32) BRC (banks = 4, rows = 12, columns = 9)                                                                                                            |           |            |       |        |             |        |               |               |       |               |       |       |       |      |    |

| 32 MB using two 16-bit wide devi                                                                                                                                                                               | ces 128   | Mbit SDF   | R SDR | AM (8  | M x 16) BI  | RC (ba | anks          | = 4,          | row   | s = 1         | 2, c  | olum  | nns = | : 9) |    |

| 32 MB using four 8-bit wide device                                                                                                                                                                             | ces 64 M  | bit SDR \$ | SDRA  | M (8M  | x 8) BRC    | (bank  | s = 4         | , <b>ro</b> v | vs =  | 12, 0         | colu  | mns   | = 9)  |      |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                   | 14        | 13         | 12    | 11     | 10          | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address                                                                                                                                                                                     | 23        | 24         | -     | 22     | 21          | 20     | 19            | 18            | 17    | 16            | 15    | 14    | 13    | 12   | 11 |

| AHB address to column address                                                                                                                                                                                  | 23        | 24         | -     | -      | AP          | -      | 10            | 9             | 8     | 7             | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections                                                                                                                                                                                       | BA1       | BA0        | -     | -      | 10/AP       | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| 32 MB using 32-bit wide device 2                                                                                                                                                                               | 56 Mbit S |            | 8) MA | 8M x 3 | 2) BRC (b   | anks = | = 4, r        | ows           | = 13  | , <b>co</b> l | lumr  | ns =  | 8)    |      |    |

| LPC address pin, EMC_A[14:0]                                                                                                                                                                                   | 14        | 13         | 12    | 11     | 10          | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| AHB address to row address                                                                                                                                                                                     | 23        | 24         | 22    | 21     | 20          | 19     | 18            | 17            | 16    | 15            | 14    | 13    | 12    | 11   | 10 |

| AHB address to column address                                                                                                                                                                                  | 23        | 24         | -     | -      | AP          | -      | -             | 9             | 8     | 7             | 6     | 5     | 4     | 3    | 2  |

| SDRAM device connections                                                                                                                                                                                       | BA1       | BA0        | -     | -      | 10/AP       | 9      | 8             | 7             | 6     | 5             | 4     | 3     | 2     | 1    | 0  |

| Table 8. 32-bit wide system data bus low-power AHB address mapping to SDRAM pins (BRC)continued             |           |          |        |        |            |        |        |       |                |        |       |       |       |       |    |

|-------------------------------------------------------------------------------------------------------------|-----------|----------|--------|--------|------------|--------|--------|-------|----------------|--------|-------|-------|-------|-------|----|

| 64 MB using 32-bit wide device 5                                                                            | 12 Mbit S | SDR SDR  | RAM (1 | 6M x   | 32) BRC (I | banks  | = 4,   | row   | s = 1          | I3, c  | olum  | nns = | = 9)  |       |    |

| 64 MB using two 16-bit wide devi                                                                            | ces 256   | Mbit SDF | R SDR  | AM (1  | 6M x 16) E | BRC (I | bank   | s = 4 | ا, <b>ro</b> ۱ | vs =   | 13, ( | colu  | mns   | = 9)  |    |

| LPC address pin, EMC_A[14:0]                                                                                | 14        | 13       | 12     | 11     | 10         | 9      | 8      | 7     | 6              | 5      | 4     | 3     | 2     | 1     | 0  |

| AHB address to row address                                                                                  | 25        | 24       | 23     | 22     | 21         | 20     | 19     | 18    | 17             | 16     | 15    | 14    | 13    | 12    | 11 |

| AHB address to column address                                                                               | 25        | 24       | -      | -      | AP         | -      | 10     | 9     | 8              | 7      | 6     | 5     | 4     | 3     | 2  |

| SDRAM device connections                                                                                    | BA1       | BA0      | -      | -      | 10/AP      | 9      | 8      | 7     | 6              | 5      | 4     | 3     | 2     | 1     | 0  |

| 64 MB using four 8-bit wide devices 128 Mbit SDR SDRAM (16M x 8) BRC (banks = 4, rows = 12, columns = 10)   |           |          |        |        |            |        |        |       |                |        |       |       |       |       |    |