# DS36BC956 Low Power BiCMOS HEX Differential Bus Transceiver

### **General Description**

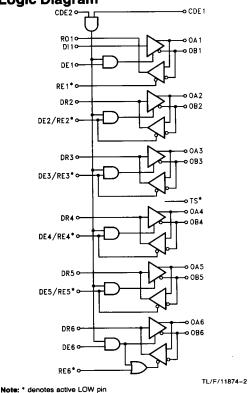

**Connection Diagram**

The DS36BC956 is a low power BiCMOS, six bit RS-485 Differential Bus Transceiver optimally designed for high speed parallel multipoint I/O buses including SCSI-1, -2, -3 and IPI interfaces. The device is offered in a thermally enhanced 48L SSOP package, offering a balance between integration and power dissipation (Junction Temperature) in an extremely small foot print. Three devices can implement a complete SCSI initiator or target interface.

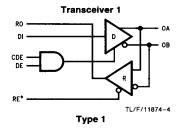

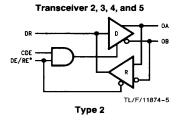

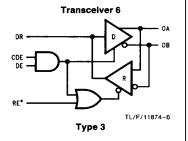

For maximum flexibility the device provides three different types of transceivers. Channel one is a type 1 configuration, with separate receiver output, driver input, and enable pins. Channels 2, 3, 4, 5 are type 2 transceivers, and provide a direction control pin and a bi-directional data pin. These channels are ideal for use on data lines and bi-directional control lines. Channel six is a type 3 transceiver, with a bidirectional data pin, and separate enable pins. This allows it to be configured as a driver, receiver, or transceiver and is ideal for use on single direction control lines.

#### **Features**

- Meets EIA RS-485 multipoint standard

- Meets SCSI-2 differential specifications

- Low power BiCMOS design

- High speed design/low skew specifications

- Available in thermally enhanced 48L SSOP package

- Glitch free driver outputs on power up and down

- Thermal shutdown protection and reporting pin (TS\*)

- Wide common mode range: -7V to +12V 35 mV minimum hysteresis

- Flow-through pin-out

#### **48L SSOP** DS36BC956 - HS-GND HS-GND HS-GND - HS-GND HS-GND -- HS-GND CDF 1 QVCC . - GND CDE2 -RO1 -- OA 1 • OB1 DF 1 OA2 - OB2 RF1\* -40 DR2 -39 · V<sub>CC</sub> DE2/RE2\* - OA3 DR3 - OB3 36 - OA4 DE3/RE3\* - OB4 DR4 35 DE4/RE4° 34 · v<sub>cc</sub> - 0A5 DR5 DE5/RE5\* 17 32 - OB5 - OA6 31 DR6 -18 - OB6 DE6 -19 30 RE6\* 🗕 20 29 - GND QGND - 21 – TS\* - HS-GND HS-GND - 22 27 - HS-GND HS-GND -23 26 HS-GND HS-GND

Order Number DS36BC956MEA See NS Package Number MS48A **Logic Diagram**

3-68

TL/F/11874-1

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>, QV<sub>CC</sub>) 7V

Input Voltage (DR, DI, CDE, DE/RE\*, DE, RE\*) 5.5V

Driver Output Voltage/Receiver

Input Voltage (OA, OB) -10V to +15V

Receiver Output Voltage (DR, RO) 5.5V

Thermal Shutdown Report Pin (TS\*) 5.5V

Maximum Package Power Dissipation @+25°C

(derate SSOP Package 16.2 mW/°C above +25°C)

$\begin{array}{lll} \mbox{Storage Temperatrure Range} & -65^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \mbox{Lead Temperature (Soldering 4 Sec)} & +260^{\circ}\mbox{C} \\ \mbox{Maximum Junction Temperature (T_J)} & +150^{\circ}\mbox{C} \\ \end{array}$

# Recommended Operating Conditions

|                                 | Min              | Max  | Units |

|---------------------------------|------------------|------|-------|

| Supply Voltage, V <sub>CC</sub> | 4.75             | 5.25 | V     |

| Bus Voltage                     | -7.0             | + 12 | V     |

| Operating Temperature (         | T <sub>A</sub> ) |      |       |

| DS36BC956                       | 0                | 70   | °C    |

### **Electrical Characteristics**

48L SSOP Package

Over recommended supply voltage and operating temperature ranges, unless otherwise specified. (Notes 2, 12)

2016 mW

| Symbol                                  | Parameter                                                                                       | Conditions                                                              | Pin       | Min                               | Тур | Max   | Units |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------|-----------------------------------|-----|-------|-------|

| DRIVER C                                | HARACTERISTICS                                                                                  |                                                                         |           |                                   |     |       | *     |

| V <sub>O</sub>                          | Output Voltage                                                                                  | $I_O = 0 \text{ mA } (V_{OA}, V_{OB})$                                  |           | 0                                 |     | Vcc   | V     |

| V <sub>OD0</sub>                        | Differential Driver Output Voltage<br>(No Load)                                                 | $I_L = 0 \text{ mA}, R_L = \infty \text{ (Figure 1)}$                   |           | 1.5                               |     | Vcc   | ٧     |

| V <sub>OD1</sub>                        | Differential Driver Output Voltage<br>(Full Load)                                               | I <sub>O</sub> = 60 mA, V <sub>CM</sub> = 0V                            |           | 1.5                               | 1.7 |       | v     |

| V <sub>OD2</sub>                        | Differential Driver Output Voltage<br>(Termination Load)                                        | R <sub>L</sub> = 100Ω, (422)<br>( <i>Figure 1,</i> Note 3)              |           | 0.5 V <sub>OD1</sub><br>or<br>2.0 | 2.5 |       | ٧     |

|                                         |                                                                                                 | $R_L = 54\Omega  (Figure  1)  (485)$                                    |           | 1.5                               | 2.2 |       | V     |

| V <sub>OD3</sub>                        | Differential Driver Output Voltage                                                              | V <sub>TEST</sub> = -7V to +12V<br>(Figure 2) (485)                     | OA,<br>OB | 1.5                               |     | 5.0   | V     |

| $\Delta  V_{OD2} , \\ \Delta  V_{OD3} $ | Change in Magnitude of Driver<br>Differential Output Voltage for<br>Complementary Output States | (Figure 1, Note 4) (422 and 485)                                        |           |                                   |     | 0.2   | ٧     |

| V <sub>OD4</sub>                        | Differential Driver Output Voltage (SCSI-3)                                                     |                                                                         |           | 1.0                               | 2.2 |       | V     |

| V <sub>OC</sub>                         | Driver Common Mode Output Voltage (Note 5)                                                      | $R_L = 54\Omega \text{ or } 100\Omega \text{ (Figure 1)}$ (422 and 485) |           | -1.0                              | 2.1 | 3.0   | ٧     |

| ΔIVOC                                   | Change in Magnitude of Common Mode Output Voltage                                               | (Figure 1, Note 4)<br>(422 and 485)                                     |           |                                   |     | 0.2   | ٧     |

| V <sub>OH</sub>                         | Output Voltage HIGH                                                                             | I <sub>OH</sub> = -55 mA                                                |           | 2.7                               | 3.0 |       | V     |

| V <sub>OL</sub>                         | Output Voltage LOW                                                                              | I <sub>OL</sub> = 55 mA                                                 |           |                                   | 1.5 | 1.7   | ٧     |

| V <sub>IH</sub>                         | Input Voltage HIGH                                                                              |                                                                         |           | 2.0                               |     |       | ٧     |

| V <sub>IL</sub>                         | Input Voltage LOW                                                                               |                                                                         |           |                                   |     | 0.8   | V     |

| V <sub>CL</sub>                         | Input Clamp Voltage                                                                             | I <sub>CL</sub> = -18 mA                                                | DR,       |                                   |     | -1.5  | ٧     |

| I <sub>IH</sub>                         | Input HIGH Current                                                                              | V <sub>IN</sub> = 2.4V (Note 6)                                         | DI        |                                   |     | 20    | μА    |

| I <sub>IL</sub>                         | Input LOW Current                                                                               | V <sub>IN</sub> = 0.4V (Note 6)                                         |           |                                   |     | - 100 | μА    |

# **Electrical Characteristics** (Continued)

Over recommended supply voltage and operating temperature ranges, unless otherwise specified. (Notes 2, 12)

| Symbol           | Parameter                                             | Conditions                                             |                            | Pin         | Min  | Тур  | Max   | Units    |

|------------------|-------------------------------------------------------|--------------------------------------------------------|----------------------------|-------------|------|------|-------|----------|

| DRIVER C         | HARACTERISTICS (Continued)                            |                                                        |                            |             |      |      |       |          |

| IOSD             | Driver Short-Circuit Output                           | $V_O = -7V$                                            | (485)                      |             |      |      | - 250 | mA       |

|                  | Current (Note 7)                                      | V <sub>O</sub> = 0V                                    | (422)                      | OA,<br>OB   |      |      | - 150 | mA       |

|                  |                                                       | V <sub>O</sub> = +12V                                  | (485)                      |             |      |      | 250   | mΑ       |

| RECEIVER         | R CHARACTERISTICS                                     |                                                        |                            |             |      |      |       |          |

| VoH              | Output Voltage HIGH (Figure 3)                        | V <sub>ID</sub> = 0.20V                                | $I_{OH} = -0.4 \text{ mA}$ |             | 2.4  | 3.3  |       | <b>v</b> |

|                  |                                                       |                                                        | $I_{OH} = -0.1 \text{ mA}$ | DR,         | 3.0  | 3.5  |       | ٧        |

|                  |                                                       | V <sub>ID</sub> = Open                                 | $I_{OH} = -0.4 \text{ mA}$ | RO          | 2.4  |      |       | ٧        |

| V <sub>OL</sub>  | Output Voltage LOW                                    | $V_{ID} = -0.20V$ , $I_{OL} = 8 \text{ mA}$ (Figure 3) |                            |             |      | 0.3  | 0.5   | >        |

| V <sub>TH</sub>  | Differential Input HIGH<br>Threshold Voltage (Note 8) | $V_O = V_{OH}, I_O = -0.4 \text{ mA}$ (422 and 485)    |                            |             |      |      | 200   | mV       |

| V <sub>TL</sub>  | Differential Input LOW<br>Threshold Voltage (Note 8)  | $V_O = V_{OL}$ , $I_O = 8.0$ mA (422 and 485)          |                            | OA,<br>OB   | -200 |      |       | mV       |

| V <sub>HST</sub> | Hysteresis (Note 9)                                   | V <sub>CM</sub> = 0V                                   |                            |             | 35   |      |       | mV       |

| Iosa             | Short Circuit Output Current                          | V <sub>O</sub> = 0V (Note 7)                           |                            | DR, RO      | -15  | -30  | -100  | mA       |

| loza             | TRI-STATE® Output Current                             | $V_{O} = GND, 0.4V, 2.4V, V_{CC}$                      |                            | RO          |      |      | 20    | μΑ       |

| DEVICE C         | HARACTERISTICS                                        |                                                        |                            |             |      |      |       |          |

| VIH              | Enable Input Voltage HIGH                             |                                                        |                            |             | 2.0  |      |       | V        |

| V <sub>IL</sub>  | Enable Input Voltage LOW                              |                                                        |                            | DE/RE*,     |      |      | 0.8   | V        |

| V <sub>CL</sub>  | Enable Input Clamp Voltage                            | $i_{CL} = -18 \text{ mA}$                              |                            | CDE,<br>DE, |      |      | -1.5  | V        |

| l <sub>H</sub>   | Enable Input Current HIGH                             | V <sub>CC</sub> = 5.25V and                            |                            | RE*         |      |      | 20    | μΑ       |

| hL               | Enable Input Current LOW                              | V <sub>CC</sub> = 3.0V                                 |                            |             |      |      | -20   | μΑ       |

| I <sub>IN</sub>  | Line Input Current (Note 10)                          | Other Input = 0V                                       | V <sub>1</sub> = +12V      |             |      | 0.5  | 1.0   | mA       |

|                  |                                                       | DE/RE*, CDE, and<br>DE = 0.8V                          | $V_{I} = -7V$              |             |      | -0.4 | -0.8  | mA       |

| ING              | Line Input Current<br>(Power Up/Down)                 | Other Input = 0V<br>DE/RE*, CDE, and                   | V <sub>I</sub> = +12V      | OA,<br>OB   |      | 0.5  | 1.0   | mA       |

|                  |                                                       | DE = 2.0V<br>V <sub>CC</sub> = 3.0V                    | V <sub>I</sub> = -7V       |             |      | -0.4 | -0.8  | mA       |

| VOL              | Output Voltage LOW                                    | I <sub>OL</sub> = 8 mA                                 |                            | TS*         |      | 0.3  |       | V        |

| 1ccd             | No Load Supply Current                                | DR On, REC Off                                         | -                          |             |      | 16   | TBD   | m/       |

| ICCR             | (Note 11)                                             | DR Off, REC On                                         |                            | Vcc         |      | 23   | TBD   | m/       |

| Iccx             | 7                                                     | DR Off, REC Off                                        | DR Off, REC Off            |             |      | 8    | TBD   | m/       |

**Switching Characteristics**Over recommended supply voltage and operating temperature ranges, unless otherwise specified. (Note 12)

| Symbol                                           | Parameter                                                                    | Conditions                                                                   | Min | Тур | Max   | Unit |

|--------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-------|------|

| DRIVER SIN                                       | IGLE-ENDED CHARACTERISTICS                                                   |                                                                              | -   |     |       |      |

| tpzH                                             | Output Enable Time To High Level                                             | R <sub>L</sub> = 110Ω <i>(Figure 8)</i>                                      |     | 30  | 60    | ns   |

| t <sub>PZL</sub>                                 | Output Enable Time To Low Level                                              | $R_L = 110\Omega$ (Figure 7)                                                 |     | 30  | 60    | ns   |

| t <sub>PHZ</sub>                                 | Output Disable Time From High Level                                          | $R_L = 110\Omega$ (Figure 8)                                                 |     | 30  | 60    | ns   |

| t <sub>PLZ</sub>                                 | Output Disable Time From Low Level                                           | R <sub>L</sub> = 110Ω <i>(Figure 7)</i>                                      |     | 30  | 60    | ns   |

| DRIVER DIF                                       | FERENTIAL CHARACTERISTICS ( $\Delta V_{CC} = T$                              | BD mV, $\Delta T_A = TBD^{\circ}C$ )                                         |     |     |       |      |

| <sup>t</sup> PLHD                                | Differential Propagation Delay (Note 13)                                     | $R_L = 54\Omega$ , $C_L = 50$ pF,<br>CD = 50 pF (Figure 4)                   | tm1 | 9   | tm1+4 | ns   |

|                                                  |                                                                              | R1 = R3 = $165\Omega$ , R2 = $75\Omega$ ,<br>CD = $60 \text{ pF}$ (Figure 5) | tm2 | 9   | tm2+4 | ns   |

| tPHLD                                            | Differential Propagation Delay (Note 13)                                     | $R_L = 54\Omega$ , $C_L = 50$ pF,<br>CD = 50 pF (Figure 4)                   | tm3 | 9   | tm3+4 | ns   |

|                                                  |                                                                              | R1 = R3 = $165\Omega$ , R2 = $75\Omega$ ,<br>CD = $60 \text{ pF}$ (Figure 5) | tm4 | 9   | tm4+4 | ns   |

| t <sub>r</sub> , t <sub>f</sub> Transition Times | $R_L = 54\Omega$ , $C_L = 50$ pF,<br>CD = 50 pF (Figure 4)                   | 2                                                                            | 4   | 16  | ns    |      |

|                                                  |                                                                              | R1 = R3 = $165\Omega$ , R2 = $75\Omega$ ,<br>CD = $60 \text{ pF}$ (Figure 5) | 2   | 4   | 16    | ns   |

| <sup>t</sup> SKD                                 | t <sub>PLHD</sub> -t <sub>PHLD</sub>   Differential Driver Skew              | $R_L = 54\Omega$ , $C_L = 50$ pF,<br>CD = 50 pF (Figure 4)                   |     | TBD | TBD   | ns   |

|                                                  |                                                                              | R1 = R3 = $165\Omega$ , R2 = $75\Omega$ ,<br>CD = $60 \text{ pF}$ (Figure 5) |     | TBD | TBD   | ns   |

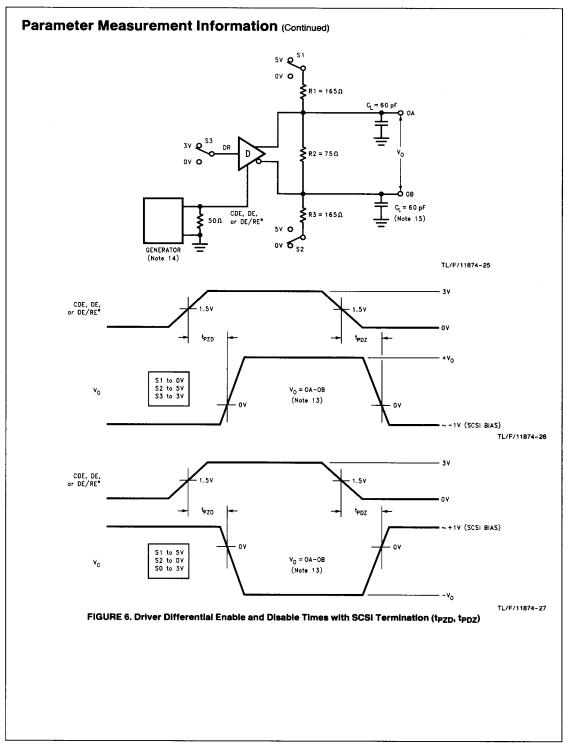

| t <sub>PZD</sub>                                 | Differential Output Enable Time                                              | $R1 = R3 = 165\Omega, R2 = 75\Omega$                                         |     | 30  | 60    | ns   |

| t <sub>PDZ</sub>                                 | Differential Output Disable Time                                             | CD = 60 pF <i>(Figure 6)</i>                                                 |     | 30  | 60    | ns   |

| RECEIVER                                         | CHARACTERISTICS ( $\Delta$ V <sub>CC</sub> = TBD mV, $\Delta$ T <sub>A</sub> | = TBD°C)                                                                     |     |     | -     |      |

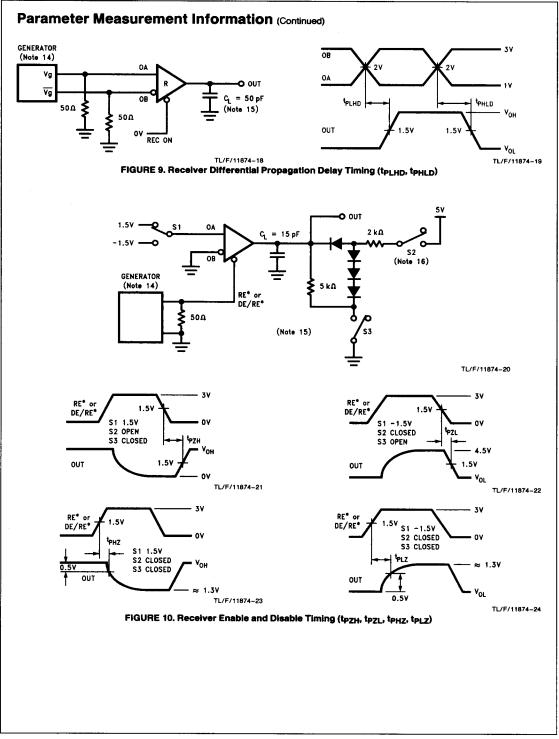

| t <sub>PLHD</sub>                                | Differential Propagation Delay                                               | C <sub>L</sub> = 50 pF, <i>(Figure 9)</i>                                    | tm5 | TBD | tm5+5 | ns   |

| tpHLD                                            | Differential Propagation Delay                                               |                                                                              | tm6 | TBD | tm6+5 | ns   |

| <sup>t</sup> SKD                                 | $ { m t_{PLHD}-t_{PHLD}} $ Differential Receiver Skew                        |                                                                              |     | TBD | TBD   | ns   |

| <sup>t</sup> PZH                                 | Output Enable Time To High Level                                             | C <sub>L</sub> = 15 pF (Figure 10)                                           |     | 30  | 80    | ns   |

| tpZL                                             | Output Enable Time To Low Level                                              |                                                                              |     | 30  | 80    | ns   |

| t <sub>PHZ</sub>                                 | Output Disable Time From High Level                                          |                                                                              |     | 30  | 80    | ns   |

| t <sub>PLZ</sub>                                 | Output Disable Time From Low Level                                           |                                                                              |     | 30  | 80    | ns   |

Note: TBD denotes "To Be Determined" and will be specified once characterization of the device is complete.

3-72

25 HS-GND

TL/F/11874-3

HS-GND 24

Note: \* denotes active low pin.

# Logic Diagram (Continued)

#### **Truth Tables**

#### **TRANSCEIVERS: 2, 3, 4, 5**

|      | Enables | 3      | Driver | Receiver |  |  |

|------|---------|--------|--------|----------|--|--|

| CDE1 | CDE2    | DE/RE* | Driver | neceiver |  |  |

| L    | х       | Н      | OFF    | OFF      |  |  |

| ×    | L       | Н      | OFF    | OFF      |  |  |

| L    | х       | L      | OFF    | ON       |  |  |

| ×    | L       | L      | OFF    | ON       |  |  |

| Н    | Н       | Н      | ON     | OFF      |  |  |

| H    | н       | L      | OFF    | ON       |  |  |

#### **TRANSCEIVERS: 1, 6**

#### DRIVER

| Enables |      |    | Driver |

|---------|------|----|--------|

| CDE1    | CDE2 | DE | Dilver |

| L       | ×    | Н  | OFF    |

| X       | L    | н  | OFF    |

| L       | ×    | L  | OFF    |

| x       | L .  | L  | OFF    |

| Н       | н    | Н  | ON     |

| н       | н    | L  | OFF    |

#### RECEIVER

| Enable | Receiver |

|--------|----------|

| RE*    | neceiver |

| Н      | OFF      |

| L      | ON       |

Note: For REC6 to be active (ON), DE6 must be L (LOW).

#### DRIVER

| Driver | Input    | Out | puts |

|--------|----------|-----|------|

| Drivei | DR or DI | 0A  | ОВ   |

| OFF    | ×        | Z   | z    |

| ON     | L        | L   | н    |

| ON     | I        | H   | L    |

#### RECEIVER

| Receiver | Inputs    | Output   |

|----------|-----------|----------|

|          | OA-OB     | DR or RO |

| OFF      | X         | Z        |

| ON       | OPEN      | н        |

| ON       | ≥ +200 mV | н        |

| ON       | ≤ −200 mV | L        |

### **Parameter Measurement Information** 375Ω V<sub>OD3</sub> 60Ω 375Ω TL/F/11874-7 FIGURE 1. Driver Output (V<sub>OD</sub>,V<sub>OC</sub>) TL/F/11874-8 FIGURE 2. Driver Output (VOD3) REC ON TL/F/11874-9 FIGURE 3. Receiver Output (V<sub>OH</sub>, V<sub>OL</sub>) G = 50 pF PLHD PHLD ОВ = CROSSING POINT QΑ GENERATOR = 50 pF 80% 20% (Note 14) (Note 15) V<sub>O</sub> = 0A-0B TL/F/11874-10 (Note 13) TL/F/11874-11 FIGURE 4. Driver Differential Propagation Delay and Transition Timing ( $t_{PLHD}$ , $t_{PHLD}$ , $t_{r}$ , $t_{f}$ ) 5V Q 1.50 **₽LHD ¹**PHLD $R1 = 165\Omega$ = 60 pF CP = CROSSING POINT OA 80% 50Ω Vn = OA-OB (Note 13) GENERATOR DR ON = 60 pF $R3 = 165\Omega$ (Note 14) (Note 15) 5V O TL/F/11874-13 S1 to 5V S2 to 0V or S1 to 0V S2 to 5V TL/F/11874-12 FIGURE 5. Driver Differential Propagation Delay and Transition Timing with SCSI Termination (tpLHD, tpHLD, tp, tr)

## Parameter Measurement Information (Continued) - 37 CDE, DE R<sub>L</sub> = 110Ω or DE/RE\* 0V or 3V ъzL **t**PLZ C\_ = 50 pF (Note 15) OUT V<sub>OL</sub> + 0.5V CDE, DE, 0.57 or DE/RE\* $V_{OL}$ 50Ω TL/F/11874~15 GENERATOR (Note 14) TL/F/11874-14 S1 to OA for DI = 0V S1 to OB for DI = 3V FIGURE 7. Driver Enable and Disable Timing (tpzL, tpLZ) OA **S**1 DR CDE, DE 0V or 3V O OUT 1.50 or DE/RE\* = 50 pF $= 110\Omega$ **t**PHZ CDE, DE, 0.57 or DE/RE\* OUT 2.3٧ (Note 15) 50Ω GND TL/F/11874-17 GENERATOR (Note 14) TL/F/11874-16 S1 to OA for DI = 3V S1 to OB for DI = 0V FIGURE 8. Driver Enable and Disable Timing (tpzH, tpHZ) 3-76

#### Parameter Measurement Information (Continued)

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground unless otherwise specified.

Note 3: The minimum limit is either 2.0V or 50% of the magnitude of V<sub>OD1</sub>, whichever is greater.

Note 4:  $\Delta$   $|V_{OD}|$  and  $\Delta$   $|V_{OC}|$  are changes in magnitude of  $V_{OD}$  and  $V_{OC}$ , respectively, that occur when the input changes state.

Note 5: In TIA/EIA-422-A and TIA/EIA-485 standards, V<sub>OC</sub>, which is the average of the two output voltages with respect to ground, is called output offset voltage, V<sub>OS</sub>.

Note 6: I<sub>IH</sub> and I<sub>IL</sub> include driver input current and receiver TRI-STATE leakage current on DR(2-6).

Note 7: Short one output at a time to avoid causing a thermal shutdown of the device due to excessive power dissipation.

Note 8: Threshold parameter limits specified as an algebraic value rather than by magnitude.

Note 9: Hysteresis defined as  $V_{HST} = V_{TH} - V_{TL}$ .

Note 10: I<sub>IN</sub> includes the receiver input current and TRI-STATE leakage current.

Note 11: Total package supply current.

Note 12: All typicals are given for  $V_{CC} = 5.0V$  and  $T_A = +25^{\circ}C$ .

Note 13: Differential propagation delays are calculated from single-ended propagation delays at the cross point.

Note 14: The input pulse is supplied by a generator having the following characteristics: f = 1.0 MHz, 50% duty cycle,  $t_f$  and  $t_f < 6.0 \text{ ns}$ ,  $Z_0 = 50\Omega$ .

Note 15: C<sub>L</sub> includes probe and stray capacitance.

Note 16: Diodes are 1N916 or equivalent.

### **Pin Descriptions**

V<sub>CC</sub> (Pins 34, 39)—Power Supply Pin: Positive power supply pins for TIA/EIA-485 driver output structures. Both pins must be connected to power supply rail for proper operation of the drivers. V<sub>CC</sub> range is specified from 4.75V to 5.25V, nominally 5.0V.

**GND** (Pins 29, 44)—**Ground Pin:** Ground pins for TIA/EIA-485 driver output structures. Both pins must be connected to ground plane for proper operation of the drivers.

QV<sub>CC</sub> (Pin 4)—Qulet Power Supply Pin: Positive power supply pin for internal driver logic, thermal shutdown circuitry, and receivers. This pin must be connected to a power supply rail for the device to operate properly. QV<sub>CC</sub> range is specified from 4.75V to 5.25V, nominally 5.0V.

**QGND** (Pin 21)—**Quiet Ground Pin:** Ground pin for internal driver logic, thermal shutdown circuitry, and receivers. This pin must be connected to a ground plane for the device to operate properly.

HS-GND (Pins 1, 2, 3, 22, 23, 24, 25, 26, 27, 46, 47, 48)— Heat Sink Ground Pin: Ground pins connected internally to an enhanced lead frame to improve the thermal performance of the package. These pins should be connected to the ground plane for maximum heat transfer. Additional PCB copper foil can be added to further enhance the thermal capabilities of the package.

CDE1,2 (Pins 45, 5)—Common Driver Enable: Common Driver Enable for TRI-STATE control of driver output stage. A HIGH on the driver enable pins enables the driver outputs. A LOW on a CDE pin will TRI-STATE all driver outputs.

**DE1,6** (Pins 8, 19)—**Driver Enable:** Driver Enable for TRI-STATE control of driver output stage. A HIGH on the driver enable pins enables the driver output. A LOW on a DE pin will TRI-STATE the respective channels driver outputs.

**DI1** (Pin 7)—**Driver Input Pin:** TTL/CMOS pin that is used as driver input.

RE\*1,6 (Pins 9, 20)—Receiver Enable Bar: Receiver Enable for TRI-STATE control of receiver output stage. A LOW on this pin enables the receiver output. A HIGH on this pin will TRI-STATE the respective channel's receiver output.

**DE/RE\*2,3,4,5** (Pins 11 13, 15, 17)—**Driver Enable/Receiver Enable Bar:** Driver Enable/Receiver Enable pin provides direction control of the respective transceiver. A HIGH on this pin enables the driver output and will TRI-STATE the receiver output stage. A LOW on this pin will TRI-STATE the driver outputs and enable the receiver output stage.

DR2,3,4,5,6 (Pins 10, 12, 14, 16, 18)—Driver Input/Receiver Output Pin: Bi-directional TTL/CMOS pin that is used as driver input or receiver output depending upon the state of the enable pins. The driver input accepts TTL/CMOS levels. The receiver output stages are specified with TTL and CMOS loading conditions.

OA1,2,3,4,5,6 (Pins 43, 41, 38, 36, 33, 31)—True Driver Output/Receiver Input Pin: This pin is the true driver output (same state as input state) or the true receiver input pin depending upon enable state.

**OB1,2,3,4,5,6** (Pins 42, 40, 37, 35, 32, 30)—**Inverted Driver Output/Receiver Input Pin:** This pin is the inverted driver output (opposite state of input) or the inverted receiver input pin depending upon enable state.

TS\* (Pin 28)—Thermal Shutdown: This pin reports the occurrence of thermal shutdown which will TRI-STATE the driver outputs. Thermal shutdown typically results from severe bus faults which produce excessive on chip power dissipation. If this power dissipation elevates the function temperature above + 150°C, the internal thermal shutdown circuitry is triggered and the TS\* pin is asserted. The TS\* pin is an open collector pin. This allows the TS\* outputs of several devices to be wire ORed.

RO1 (Pin 6)—Receiver Output Pin: The receiver output pin is specified with TTL and CMOS loading conditions.