#### General Description

The OB3328 is a unique, high-efficiency and high-precision Cold Cathode Fluorescent Lamp (CCFL) backlight co ntroller IC d edicated to full bridg e configuration. The controller is designed to drive single or multiple CCF Ls in Liquid Crystal Display (LCD) applications.

The OB332 8 convert s unre gulated DC input voltage to the pure sin usoidal voltage and current waveforms i n requi red freque ncy, to ignite and operate CCFL lamps.

The OB332 8 provides a high deg ree of design flexibility by offering great program mability for key parameters which incl ude operating frequency, striking frequency, striking time, bu rst dimming frequency, soft-start time, and soft on/o ff time for burst dimming.

The OB3328 offers variable dimming modes and selectable dimming polarity<sup>1</sup>. Both internal burs than dexternal low frequency PWM (LPWM) dimming methods are available for a wide range of dimming control (10% to 100%). Furthermore, analog dimming is provided through external DC input control to achieve 40% to 100 % dimming range.

The highly integrated OB3 328 provides complete protection fe atures covering IC un der voltage lockout (UVL O), output o ver voltage prote ction, and lamp fail safe function.

The OB3328 is available in DIP-16, S OP-16 and TSSOP-16 Packages.

#### Features 5 4 1

- Support wide input voltage

- Full bridge topology

- High precision reference and frequency control

- Built-in peak detect circuit reduces BOM count

- Support single or multi-lamp applications

- High flexibility of dimming configuration:

Analog Dimming

Internal/external burst (PWM) mode dimming

Concurrent burst and analog dimming control

- Flexible user programmability:

Operating frequency

Striking frequency, striking voltage and time

Soft start and soft on/off time

Internal burst mode frequency

- Comprehensive protection coverage: IC supply under voltage lockout (UVLO) Output over voltage protection (OVP) Lamp fail safe function

## **Applications**

- Notebook computer

- LCD Monitor

- LCD TV

- LCD flat panel display for Instrument, automobile and handhold device

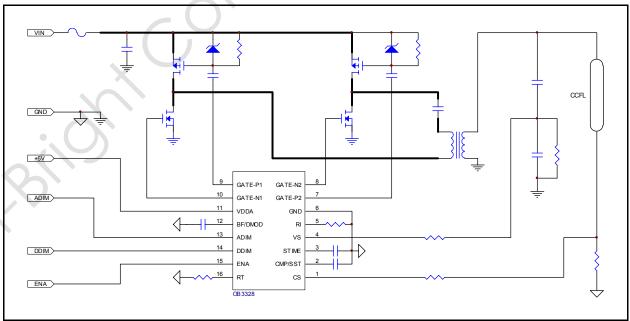

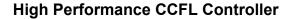

## **Typical Application Circuit**

Figure 1: OB3328 Typical Application Schematic

© On-Bright Electronics

Confidential

OB\_DO C\_DS\_2800

<sup>&</sup>lt;sup>1</sup> The OB3328 is with positive dimming polarity while its counter part OB3328N is in negative dimming polarity.

#### Absolute Maximum Ratings

| Parameter                                       | Value                  |

|-------------------------------------------------|------------------------|

| VDDA Input Voltage to GND                       | 7V                     |

| I/O to GND                                      | -0.3 to<br>VDDA + 0.3V |

| Operating Ambient<br>Temperature T <sub>A</sub> | -20 to 85°C            |

| Operating Junction Temperature T <sub>J</sub>   | 150°C                  |

| Min/Max Storage Temperature T <sub>stg</sub>    | -55 to 150°C           |

| Lead Temperature (10 Sec)                       | 260 °C                 |

**Note:** Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or an y other conditions be yond those indicated under "recommended operating conditions" is not implied. Exposur e to absolute maximum-rated con ditions for exten ded periods may affect device reliability.

## Recommended Operating Range

| Parameter           | Value        |  |  |

|---------------------|--------------|--|--|

| VDDA Voltage        | 4.5V to 5.5V |  |  |

| Operating Frequency | 30 to 150KHz |  |  |

## Package Thermal Characteristics

| Parameter                    | Value    |

|------------------------------|----------|

| Thermal resistance θJA (SOP) | 85 °C /W |

| Thermal resistance θJA (DIP) | 60 °C /W |

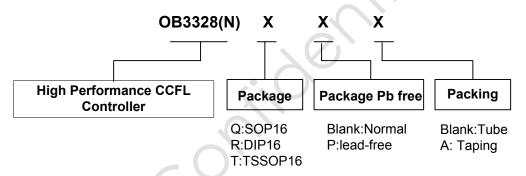

## Ordering Information<sup>2</sup>

| Part Number | Description      |

|-------------|------------------|

| OB3328RP    | DIP16, pb-free   |

| OB3328QP    | SOP16, pb-free   |

| OB3328TP    | TSSOP16, pb-free |

| OB3328NRP   | DIP16, pb-free   |

| OB3328NQP   | SOP16, pb-free   |

| OB3328NTP   | TSSOP16, pb-free |

OB3328N is negative dimming version of OB3328.

## Ordering information

© On-Bright Electronics Confidential - 2 -

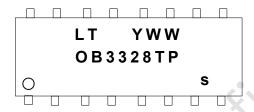

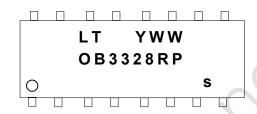

## Package Marking Information

#### SOP16

Y: Year Code (0-9)

WW: Week Code (1-52)

Q:SOP16

P:lead-free

s: internal code

#### TSSOP16

Y: Year Code (0-9)

WW: Week Code (1-52)

T:TSSOP16

P:lead-free

s: internal code

#### DIP16

Y: Year Code (0-9)

WW: Week Code (1-52)

R:DIP16

P:lead-free

s: internal code

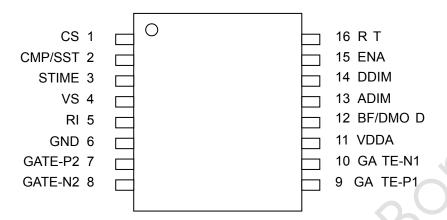

## Pin Configuration

## **Terminal Assignment**

| Pin Number | Pin Name | I/O    | Pin Function                                                                                       |

|------------|----------|--------|----------------------------------------------------------------------------------------------------|

| 1          | CS       | Input  | Lamp current sense input                                                                           |

| 2 CMP/SST  |          | I/O    | Connected to Loop com pensation ca pacitor, this cap acitor also sets the soft start time          |

| 3          | STIME    | I/O    | Connect to a capacitor to set striking time                                                        |

| 4          | VS       | Input  | Output voltage sense input                                                                         |

| 5          | RI       | I/O    | Connected to resistor setting strike frequency                                                     |

| 6 GND      |          | Ground | Ground                                                                                             |

| 7          | GATE-P2  | Output | P-MOSFET gate drive output2                                                                        |

| 8          | GATE-N2  | Output | N-MOSFET gate drive output2                                                                        |

| 9          | GATE-P1  | Output | P-MOSFET gate drive output1                                                                        |

| 10         | GATE-N1  | Output | N-MOSFET gate drive output1                                                                        |

| 11         | VDDA     | Power  | +5V power supply                                                                                   |

| 12 BF/DMOD |          | I/O    | Connected to capacitor sets Burst frequency or connected to GND selects external LPWM mode dimming |

| 13         | ADIM     | Input  | DC signal input for analog mode dimming                                                            |

| 14         | DDIM     | Input  | Digital mode dimming control signal input                                                          |

| 15         | ENA      | Input  | Chip enable control input, active high                                                             |

| 16         | RT       | I/O    | Connected to an external resistor sets operating frequency                                         |

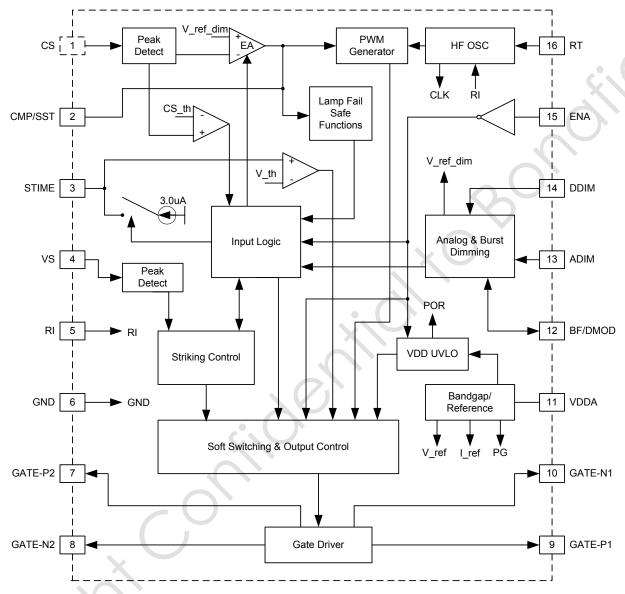

#### Functional Block Diagram

Figure2: OB3328 Functional Block Diagram

# High Performance CCFL Controller Full Bridge

#### **Electrical Characteristics**

VDDA=5V, ENA=5V, RT=36Kohm, RI=107Kohm, ADIM=DDIM=5V,  $C_{BF}$ =10nF,  $C_{STIME}$  = 1uF,  $T_{A}$ =25°C if not otherwise noted.

| Parameter Sy                      | mbol                      | Condition            | Min   | Тур       | Max | Units  |  |

|-----------------------------------|---------------------------|----------------------|-------|-----------|-----|--------|--|

| Current Consumption               |                           |                      |       |           |     |        |  |

| IC Standby                        | I <sub>standby</sub> ENA= | 0V                   | -     | 5         | 20  | uA     |  |

| Normal operating                  | I <sub>VDD</sub>          |                      | -     | 4         |     | mA     |  |

| VDDA UVLO                         |                           |                      |       |           |     |        |  |

| UVLO on                           |                           |                      | 3.6   | 0         |     | V      |  |

| UVLO off                          |                           |                      | 4.4   |           |     | V      |  |

| High Frequency Oscillator         |                           |                      |       |           |     |        |  |

| Operating frequency               | F <sub>OP</sub>           |                      | 48 50 | 52        |     | KHz    |  |

| Striking frequency                | F <sub>STK</sub>          |                      | 62 65 | 68        |     | KHz    |  |

| Temp. stability                   |                           | TA = -20 °C to 85 °C | - 200 |           | -   | PPM/°C |  |

| Min. (overlap) duty cycle         |                           |                      |       | 1%        |     |        |  |

| Max. (overlap) duty cycle         |                           | 71                   |       | 45%       |     |        |  |

| Low Frequency Oscillator for Burs | t Mode Dim                | ming                 |       |           |     |        |  |

| Burst frequency                   | 8/                        |                      | 180   | 200       | 220 | Hz     |  |

| Temp. stability                   |                           |                      | -     | 400       | -   | PPM/°C |  |

| Min. burst duty                   | OB3328 DE<br>OB3328N      | IM =0V<br>DDIM=0V    | -     | 10<br>100 | -   | %      |  |

| May burst duty                    | OB3328 DE                 |                      | -     | 100       | -   | %      |  |

| Max. burst duty                   | OB3328N                   | DDIM>3.25            |       | 10        |     | 70     |  |

| Analog Dimming Control            |                           |                      |       |           |     |        |  |

| Min. CS reference Voltage         | V_ref_dim AD              | IM= 0V               | -     | 0.5       | -   | V      |  |

| Max. CS reference Voltage         | V_ref_dim AD              | IM> 3V               | -     | 1.25      | -   | V      |  |

| External LPWM Dimming Control     |                           |                      |       |           |     |        |  |

| External LPWM duty                |                           |                      | 10    | -         | 100 | %      |  |

| External LPWM Logic input level   | high                      |                      | 2.0   |           |     | V      |  |

|                                   | low                       |                      | 8.0   |           |     | ٧      |  |

| Error Amplifier                   |                           |                      |       |           |     |        |  |

| Reference voltage                 | V <sub>REF_PK</sub>       |                      | 1.2   | 1.25      | 1.3 | V      |  |

## OB3328/OB3328N

# High Performance CCFL Controller Full Bridge

| Parameter Sy                   | mbol                   | Condition              | Min | Тур | Max | Units |

|--------------------------------|------------------------|------------------------|-----|-----|-----|-------|

| Open loop voltage gain         |                        |                        |     | 70  | -   | dB    |

| Unity gain bandwidth           |                        | CMP=39nF               |     | 250 |     | Hz    |

| Supply Current                 | •                      |                        |     |     |     | . (   |

| Soft start current             | I <sub>SST</sub>       |                        |     | 3.0 |     | uA    |

| Soft on/off current            | I <sub>SOFT</sub>      |                        |     | 120 |     | uA    |

| Striking timer current         | I <sub>STIME</sub>     |                        | -   | 3.0 | -   | uA    |

| Control and Protection Thresho | old                    |                        |     |     |     |       |

| Enable threshold               | ON 0.8<br>OFF          |                        | 2.0 |     |     | V     |

| VS regulate voltage            | VS <sub>PK</sub> Whe   | n striking             |     | 3.0 |     | V     |

| Over voltage protection        | VS <sub>PK</sub> Norma | l Operating            |     | 3.0 |     | V     |

| Lamp fail safe protection      | V <sub>CS_PK</sub>     |                        |     | 200 |     | mV    |

| Lamp fail safe deglitch time   |                        |                        |     | 20  |     | mS    |

| Striking timer threshold       | V <sub>STIME</sub>     |                        |     | 3.0 |     | V     |

| Striking completion threshold  | V <sub>CS_PK</sub>     |                        |     | 300 |     | mV    |

| Gate Driver Output             | 7                      | 0                      |     |     |     |       |

| GATE-N1/ GATE-N2               | R <sub>ON</sub>        | I <sub>OUT</sub> =70mA |     | 8   |     | ohm   |

| GATE-P1/ GATE-P2               | R <sub>oN</sub>        | I <sub>OUT</sub> =70mA |     | 8   |     | ohm   |

| Gate Driver Dead Time          |                        |                        |     |     |     |       |

| GATE-N1/GATE-P1                |                        | CMP=2V                 |     | 400 |     | nS    |

| GATE-N2/GATE-P2                |                        | CMP=2V                 |     | 400 |     | nS    |

© On-Bright Electronics Confidential OB\_DO C\_DS\_2800 - 7 -

#### **Function Description**

#### **High Efficiency Operation**

The OB3328 CCFL controller is designed to drive the inverter system in full bridge top ology, the resonant mo de full b ridge switche s converts unregulated DC voltage to pure sinusoidal waveforms for CCFL operating with high efficiency and low EMI emission. The resonant frequency of the tank is set by the transformer leakage inductance, primary series capacitor and secondary parallel capacitor.

The OB3328 provides a high performance solution with a low system cost. One reference designs for single lamp application is shown in figure 3 on page 9.

#### **Enable the Controller**

OB3328 is activated by a pplying logic high to the ENA input. Control i s TTL logic compatible. The controller is enabled when the voltage at ENA pin is higher than 1.1V. Toggling the ENA sign al resets the state machine hence restart s the inverter system.

#### Lamp Ignition and Striking Voltage Regulation

higher voltag e than that in normal operation is required to ignite CCFL, especially for aged lamp or in low ambiance temperature. The programmable stri king freque ncy, vol tage an d ignition time set by RT, RI, VS, and STIME pins ensure sufficient voltage and time for any CCFL ignition. RI in paralleled with RT pin is u sed to set the oscillator frequency which is close to resonant frequency of the tank at ignition stage thus provide sufficient stri king voltage. The output voltage is divided by the cap acitive voltage divider (forme d by C12 and C13 shown in figure 3 on page 9). The divided signal is fed into VS pin and its pea compared with internal 3.0V threshol d voltage. Consequently, the output voltage is regulated and limited. The striking voltage can be ap proximated

$$V_{striking} \approx \frac{3.0V \cdot C13}{\sqrt{2} \cdot C12}$$

Once the out put voltage reaches the target level, and if CS pin voltage is less than 350 mV, the IC will initiate the striking timer. An internal constant 3.0uA current source starts to charge the capacitor connected to STIME pin. Voltage higher than 3.0V at STIME pin indicates an ignition timeout. Under such cir cumstance, P WM Gat e out puts are disabled and thus power s witches are turned off.

No energy is further delivered to the CCFL load.

Voltage at CS pin greater than 300mV indicates the lamp being ignited and capacitor at STIME pin will be discharged. Capacitor in appropriate value is required to provide sufficient time (typically, 1 second) to ignite the lamp. Ignition time is approximated as:

$$T(sec) = C[uF]$$

#### **Over Voltage Protection**

During n ormal ope rating, if VS peak voltag e reaches the internal threshold of 3.0V, the controller im mediately sh uts do wn th e inverte r. OVP is a latch shutd own and could only be re set by toggling ENA pin.

#### Soft Start and Soft On/off

External ca pacitor connected to CM P/SST pin provides soft start and soft on/off control. At start up, an internal current source starts to charge the capacitor. Consequently, voltage at CM P/SST pin increases gradually and so as to the overlap tim e of the PWM Gate si gnals. This soft start control helps to redu ce the MOS FET inrush current and voltage stresses, thus expand the lam p life. The slope of the soft start  $\Delta V/\Delta T$  can be approximated as:

$$\frac{\Delta V}{\Delta T} = \frac{3 \times 10^{-6} \times 36}{C \times RT[kohm]}$$

Once lamps are ignited, the capacitor connected to CMP/SST pin performs the loop compensation function. In internal burst mode dimming or external burst (PWM) mode dimming conditions, the voltage ramping up and down at this pin performs a soft on/off control function in each burst cycle.

#### **Normal Operation and Striking Frequency**

The ope ration freque ncy is determined by the external resistor connected to RT pin. The operation frequency is calculated by the following equation:

$$F_{op}(KHz) = \frac{1800}{RT(Kohm)}$$

At ignition stage, RI pin is internally connected to RT pin, there fore external resistor at RI pin is in parallel with the external resistor at RT pin. The striking frequency can be calculated by the

Full Bridge

following equation:

$$F_{\text{striking}} (\text{KHz}) = \frac{1751}{RI /\!/ RT (Kohm)}$$

#### **Lamp Current Regulation**

The lamp cu rrent is regul ated by a la mp current feedback loo p with an internal transconductance error amplifier, the AC lamp current is sensed by a sense resistor (R1 3 in figure 3 on page 9) connected in series with the low voltage terminal of CCFL lamp. The AC voltage a cross the sense resistor is fed into the CS pin. The peak voltage of sensed AC voltage is detected and compared with a 1.25V internal reference voltage. The error is amplified that controls the on time of the full bridge switches, as a result, the lamp current is regulated. the lamp current can be calculated by the following equation:

$$I_{lamp} = \frac{1.25V}{\sqrt{2} \bullet R_{correc}}$$

#### **Lamp Fail Safe Functions**

During normal operation, if the lamp is removed or damaged, the voltage at CS pin will drops to 0V. If the peak voltage at CS pin cannot be regulated to the predetermined value for more than 20ms, the inverter i s I atched shut down. Toggl ing ENA restarts the operation.

#### **Dimming Control**

Three com monly used dimming mod es: analo g mode dimming, internal b urst mode dimming and external b urst (PWM) d imming functions a re supported without any additional components. The concurrent a nalog and b urst a chieves very wide dimming range.

DC volta ge ranging from 0V to 3V at ADIM pin performs a nalog mod e dimming control. The voltage at ADIM pin modulates i nternal error amplifier reference voltage from 0.5V to 1.25V, witch corresponds to a lamp current o f approximately 40% to 100%.

The BF/DM OD pin is u sed for internal/external burst mode selection and internal burst frequency setting. External bu rst (P WM) dimming mod e is selected by shorting BF/DMOD pin to ground. The OB3328 accepts an external low f requency PWM (LPWM) signal to DDIM pin with a voltage swinging from less than 0.8V to that of greater than 2.0V. The lamp brightness is controlled by the duty cycle of the LPWM sign al. The burst

frequency is equal to LPWM frequency.

Internal bu rst mode dimming is obt ained by connecting a c apacitor to BF/DMOD pin. A low frequency triangular waveform generator is formed by the ca pacitor alon g wit h internal co mparator, internal current sou rce and current sink. The triangular voltage waveform with peak of 3V and valley of 1V at this pin is used for the internal low frequency burst PWM generation. its duty cycle so as to lamp current is controlled by the DC voltage at DDIM pin. The burst frequency F burst is set by the following equation:

$$F_{burst}(Hz) = \frac{2000}{C_{BF}(nF)}$$

A DC voltage rangin g from 0V to 3V at DIM pin corresponds to a lamp c urrent of approximately 10% to 100%.

| PIN\MODE  | Analog | Internal<br>Burst | External<br>LPWM |

|-----------|--------|-------------------|------------------|

| BF/DMOD - |        | Capacitor         | <0.5V            |

| DDIM -    |        | 0-3V              | External<br>LPWM |

| ADIM 0-3V |        | -                 | 1                |

The concurrent burst and analog dimming control can achieves approximately 4% to 100% dimming ratio.

## Reference Application Circuit for Single Lamp

VIN: 8~22V ADIM: 3V, Max. Brightness; 0V, Min. Brightness (for analog mode dimming) DDIM: 3V, Max. Brightness; 0V, Min. Brightness (for burst mode dimming) ENA: Disable, 0-0.8V; Enable, 2-5V LOAD: 82.5Kohm Dummy Load

Figure3: OB3328 Reference Application Schematic

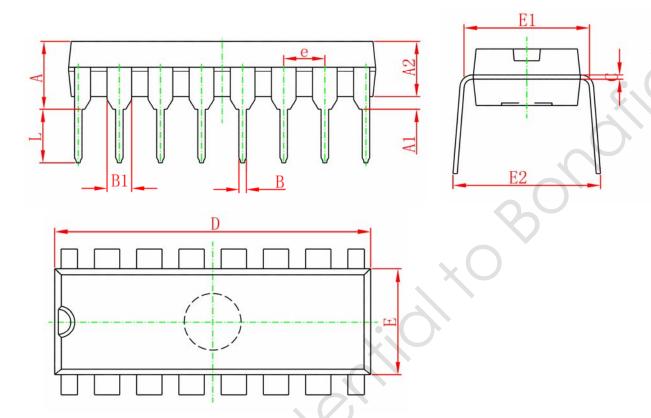

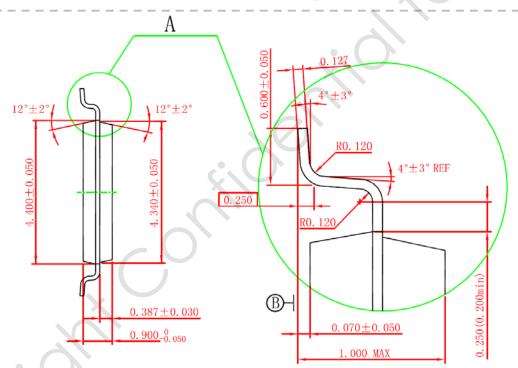

## Package Mechanical Data: DIP16

| Symbol | Dimensions In Millimeters |      | Dimensions In Inches |       |  |

|--------|---------------------------|------|----------------------|-------|--|

| Symbol | Min                       | Max  | Min                  | Max   |  |

| Α      | 3.710 4.310               |      | 0.146                | 0.170 |  |

| A1     | 0.510                     |      | 0.020                |       |  |

| A2     | 3.200 3.600               |      | 0.126                | 0.142 |  |

| В      | 0.380 0.570               |      | 0.015                | 0.022 |  |

| B1     | 1.524 (BSC)               |      | 0.060 (BSC)          |       |  |

| С      | 0.204 0.360               |      | 0.008                | 0.014 |  |

| D      | 18.800 19.20              | )    | 0.740                | 0.756 |  |

| E      | 6.200 6.600               |      | 0.244                | 0.260 |  |

| E1     | 7.320 7.920               |      | 0.288                | 0.312 |  |

| е      | 2.540 (                   | BSC) | 0.100 (BSC)          |       |  |

| 1      | 3.000 3.600               |      | 0.118                | 0.142 |  |

| E2     | 8.400 9.000               |      | 0.331                | 0.354 |  |

Confidential © On-Bright Electronics - 11 -

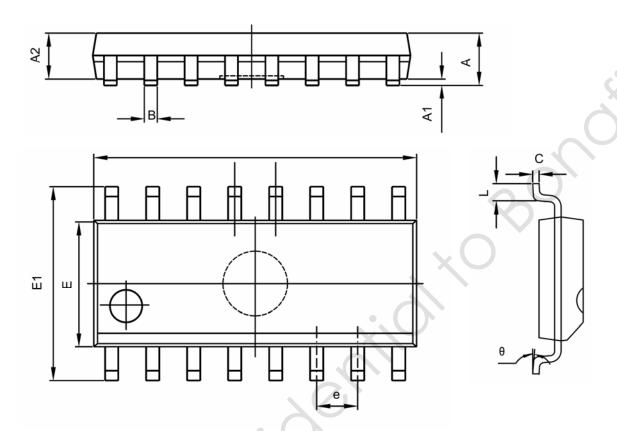

## Package Mechanical Data: SOP16

| Symbol   | Dimensions In | n Millimeters | Dimensions In Inches |         |  |

|----------|---------------|---------------|----------------------|---------|--|

| Syllibol | Min           | Max           | Min                  | Max     |  |

| Α        | 1.350 1.750   |               | 0.053                | 0.069   |  |

| A1       | 0.100 0.250   |               | 0.004                | 0.010   |  |

| A2       | 1.350 1.550   |               | 0.053                | 0.061   |  |

| В        | 0.330 0.510   |               | 0.013                | 0.020   |  |

| С        | 0.190 0.250   |               | 0.007                | 0.010   |  |

| D        | 9.800 10.000  |               | 0.386                | 0.394   |  |

| E        | 3.800 4.000   |               | 0.150                | 0.157   |  |

| E1       | 5.800 6.300   |               | 0.228                | 0.248   |  |

| е        | 1.270 (       | 1.270 (TYP)   |                      | ) (TYP) |  |

| L        | 0.400 1.270   |               | 0.016                | 0.050   |  |

| θ        | 0°            | 8°            | 0°                   | 8°      |  |

Confidential © On-Bright Electronics - 12 -

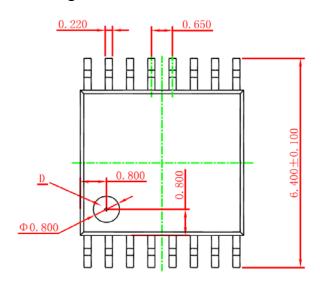

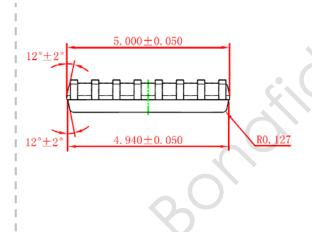

## Package Mechanical Data: TSSOP16

## The request of technology:

- Formed lead TIP planarity to datum plane B is ±0.025 Max;

- Package surfaces shall be round surface as Ra 0.800~1.200. Det ail "D" ro und surface should be polished finish, roughness as Ra 0.025~0.050 with depth 0.035 Max;

- General tolerance shall be ±0.050;

- All units are in millimeter;

© On-Bright Electronics Confidential

#### Important Notice

#### Right to make changes

On-Bright El ectronics Corp. re serves the right to make correction s, mod ifications, en hancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

#### **Warranty information**

On-Bright Electronics Corp. warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with its standard warranty. Testing and other quality control techniques are u sed to the extent it deems necessary to support this warranty. Except whe remandate d by government requirements, testing of all parameters of each product is not necessarily performed.

On-Bright Electronics Corp. assumes no liability for applications assist ance or customer product design. Customers are responsible for their products and applications using On-Bright's components, data sheet and ap plication note s. To minimize the risks associated with cuestomer products and applications, customers should provide adequate design and operating safeguards.

#### Life support

On-Bright Electronics Corp.'s products are not designed to be used as components in devices intended to support or sustain human life. On-bright Electronics Corp. will not be held liable for any damages or claims resulting from the use of its products in medical applications.

#### **Military**

On-Bright El ectronics Corp.'s products a re n ot d esigned fo r use i n milit ary appli cations. O n-Bright Electronics Corp. will not be held liable for any damages or claims resulting from the use of its products in military applications.

Confidential © On-Bright Electronics - 14 -