# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER S1C63666 Technical Manual S1C63666 Technical Hardware

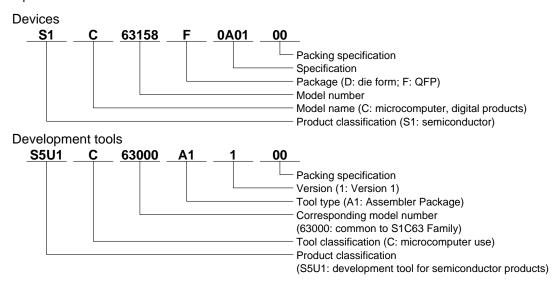

# New configuration of product number

Starting April 1, 2001, the product number has been changed as listed below. Please use the new product number when you place an order. For further information, please contact Epson sales representative.

# **CONTENTS**

| CHAPTER 1 | OU       | TLINE                                                |    | 1   |

|-----------|----------|------------------------------------------------------|----|-----|

|           | 1.1      | Features                                             |    | . 1 |

|           | 1.2      | Block Diagram                                        |    | . 2 |

|           | 1.3      | Pin Layout Diagram                                   |    |     |

|           | 1.4      | Pin Description                                      |    |     |

|           |          | ·                                                    |    |     |

|           | 1.5      | Mask Option                                          |    | . 3 |

| CHAPTER 2 | Pov      | WER SUPPLY AND INITIAL RESET                         |    | 9   |

|           | 2.1      | Power Supply                                         |    | . 9 |

|           |          | 2.1.1 Voltage regulator for OSC1 oscillation circuit | 10 |     |

|           |          | 2.1.2 Low-speed operation voltage regulator          |    |     |

|           |          | 2.1.3 High-speed operation voltage regulator         |    |     |

|           |          | 2.1.4 Internal operating voltage VD1                 |    |     |

|           |          | 2.1.5 LCD system voltage circuit                     |    |     |

|           |          | 2.1.7 Analog system power supply                     |    |     |

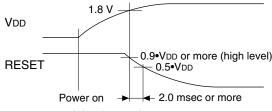

|           | 2.2      | Initial Reset                                        |    | 12  |

|           | 2.2      | 2.2.1 Reset terminal (RESET)                         |    | 12  |

|           |          | 2.2.2 Simultaneous high input to terminals K00–K03   |    |     |

|           |          | 2.2.3 Internal register at initial resetting         |    |     |

|           |          | 2.2.4 Terminal settings at initial resetting         |    |     |

|           | 2.3      | Test Terminal (TEST)                                 |    | 14  |

|           | ~-       | , ,                                                  |    |     |

| CHAPTER 3 | CP       | U, ROM, RAM                                          |    | 15  |

|           | 3.1      | CPU                                                  |    | 15  |

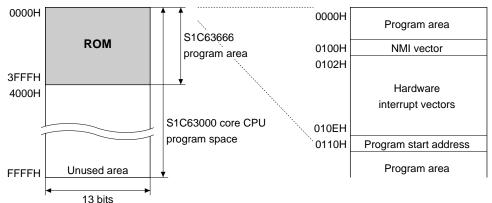

|           | 3.2      | Code ROM                                             |    | 15  |

|           | 3.3      | RAM                                                  |    | 15  |

|           | 3.4      | Data ROM                                             |    | 16  |

| CHAPTER 4 | $p_{EE}$ | RIPHERAL CIRCUITS AND OPERATION                      |    | 17  |

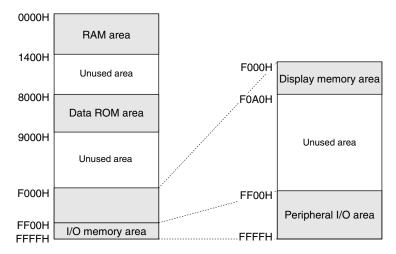

|           | 4.1      | Memory Map                                           |    |     |

|           | 4.2      | Power Control                                        |    |     |

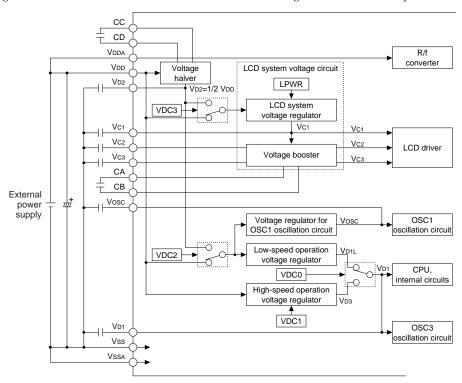

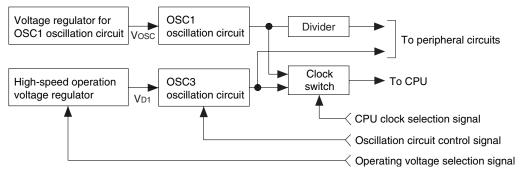

|           | 4.2      | 4.2.1 Configuration of power supply circuit          |    | 23  |

|           |          | 4.2.2 Power control procedure                        |    |     |

|           |          | 4.2.3 I/O memory for power control                   |    |     |

|           |          | 4.2.4 Programming notes                              |    |     |

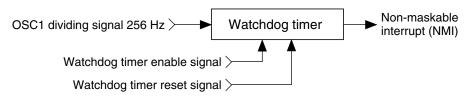

|           | 4.3      | Watchdog Timer                                       |    | 30  |

|           | 7.5      | 4.3.1 Configuration of watchdog timer                |    | 50  |

|           |          | 4.3.2 Interrupt function                             |    |     |

|           |          | 4.3.3 I/O memory of watchdog timer                   |    |     |

|           |          | 4.3.4 Programming notes                              | 31 |     |

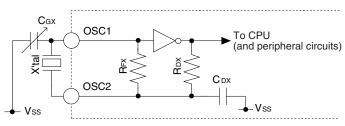

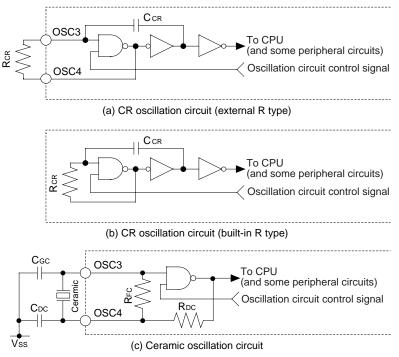

|           | 4.4      | Oscillation Circuit                                  |    | 32  |

|           | • •      | 4.4.1 Configuration of oscillation circuit           |    |     |

|           |          | 4.4.2 OSC1 oscillation circuit                       | 32 |     |

|           |          | 4.4.3 OSC3 oscillation circuit                       |    |     |

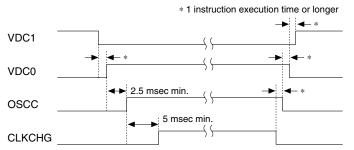

|           |          | 4.4.4 Switching of operating voltage                 |    |     |

|           |          | 4.4.5 Clock frequency and instruction execution time |    |     |

|           |          | 4.4.6 I/O memory of oscillation circuit              |    |     |

|           |          | 4.4.7 Programming notes                              | 36 |     |

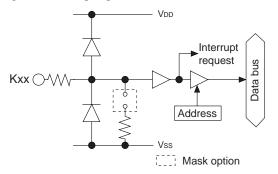

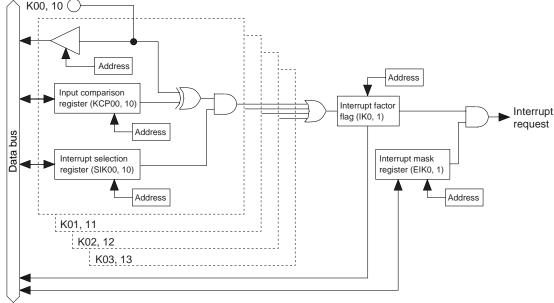

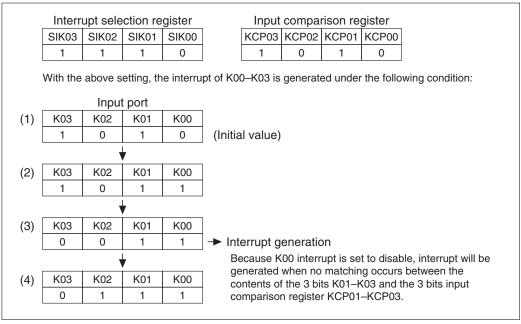

| 4.5  | <i>Input Ports (K00–K03 and K10–K13)</i>          | 37        |

|------|---------------------------------------------------|-----------|

|      | 4.5.1 Configuration of input ports                |           |

|      | 4.5.2 Interrupt function                          |           |

|      | 4.5.3 Mask option                                 |           |

|      | 4.5.4 I/O memory of input ports                   |           |

|      | 4.5.5 Programming notes                           |           |

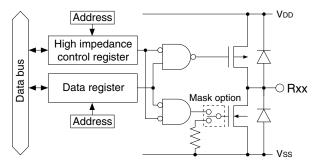

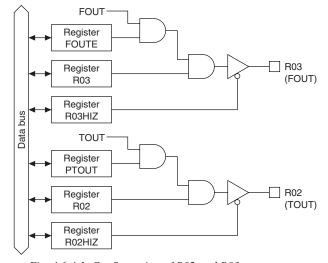

| 4.6  | Output Ports (R00–R03 and R10–R13)                | 42        |

| 7.0  | 4.6.1 Configuration of output ports               | 72        |

|      | 4.6.2 Mask option                                 |           |

|      | 4.6.3 High impedance control                      |           |

|      | 4.6.4 Special output                              |           |

|      | 4.6.5 I/O memory of output ports                  |           |

|      | 4.6.6 Programming notes                           |           |

| 4.7  |                                                   | 40        |

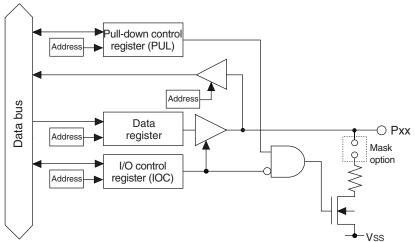

| 4.7  | I/O Ports (P00–P03 and P10–P13)                   | 48        |

|      | 4.7.1 Configuration of I/O ports                  |           |

|      | 4.7.2 Mask option                                 |           |

|      | 4.7.3 I/O control registers and input/output mode |           |

|      | 4.7.4 Pull-down during input mode                 |           |

|      | 4.7.5 I/O memory of I/O ports                     |           |

|      | 4.7.6 Programming note                            |           |

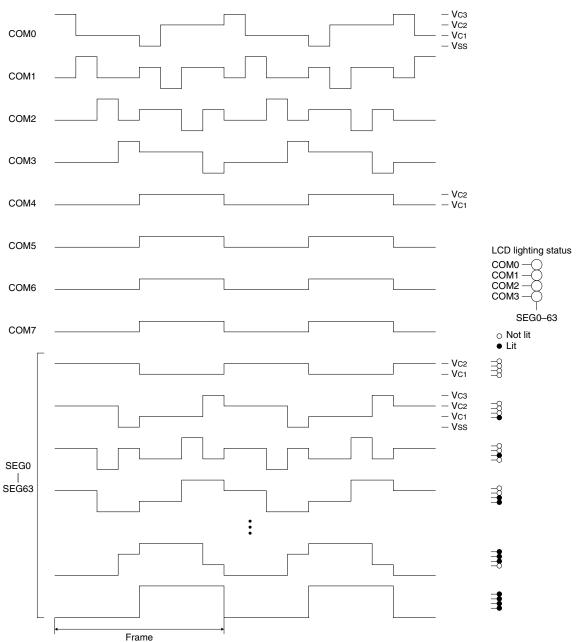

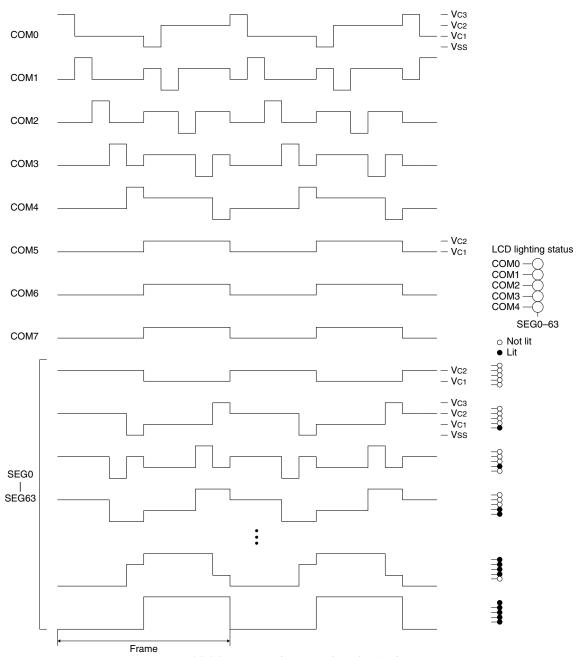

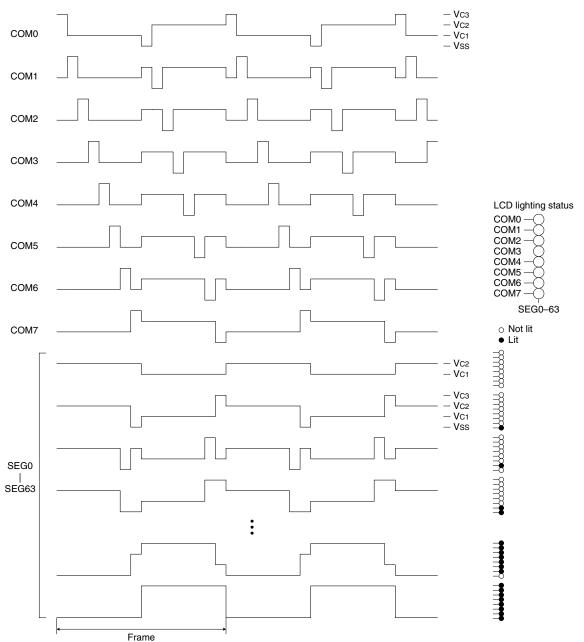

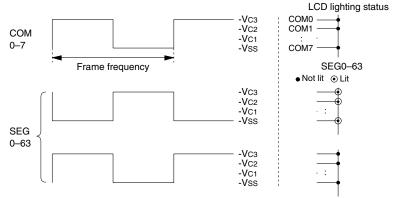

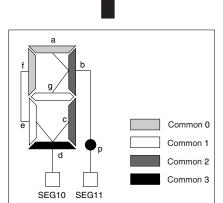

| 4.8  | LCD Driver (COM0-COM7, SEG0-SEG63)                | 53        |

|      | 4.8.1 Configuration of LCD driver                 |           |

|      | 4.8.2 Power supply for LCD driving                |           |

|      | 4.8.3 Control of LCD display and drive waveform   |           |

|      | 4.8.4 Display memory                              |           |

|      | 4.8.5 Segment option                              |           |

|      | 4.8.6 LCD contrast adjustment                     |           |

|      | 4.8.7 I/O memory of LCD driver                    |           |

|      | 4.8.8 Programming note                            |           |

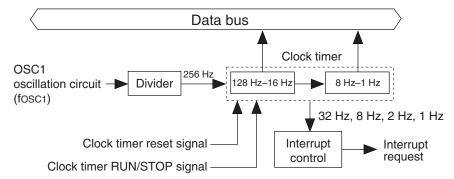

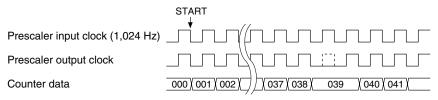

| 4.9  | Clock Timer                                       | 63        |

| ,    | 4.9.1 Configuration of clock timer                | 0.0       |

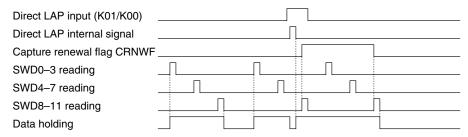

|      | 4.9.2 Data reading and hold function              |           |

|      | 4.9.3 Interrupt function                          |           |

|      | 4.9.4 I/O memory of clock timer                   |           |

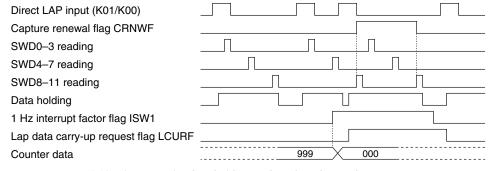

|      | 4.9.5 Programming notes                           |           |

| 1.10 |                                                   | (7        |

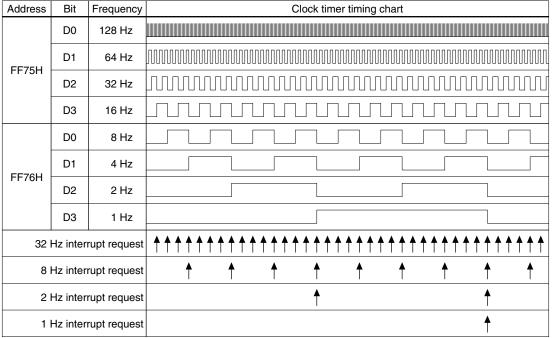

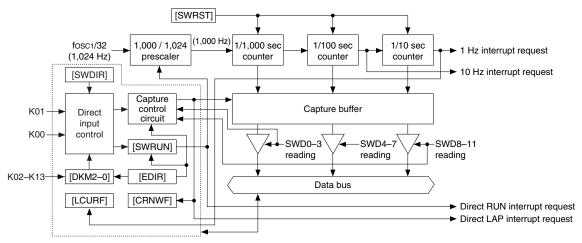

| 4.10 | Stopwatch Timer                                   | 0/        |

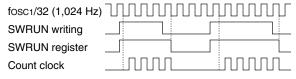

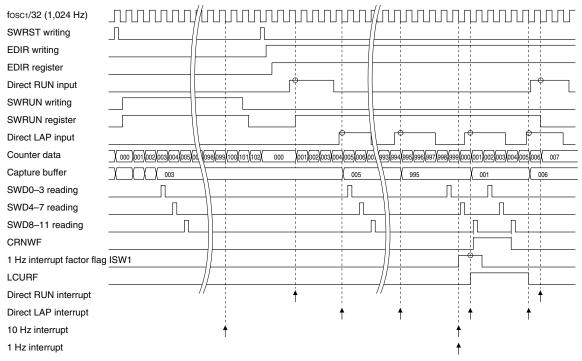

|      | 4.10.1 Configuration of stopwatch timer           |           |

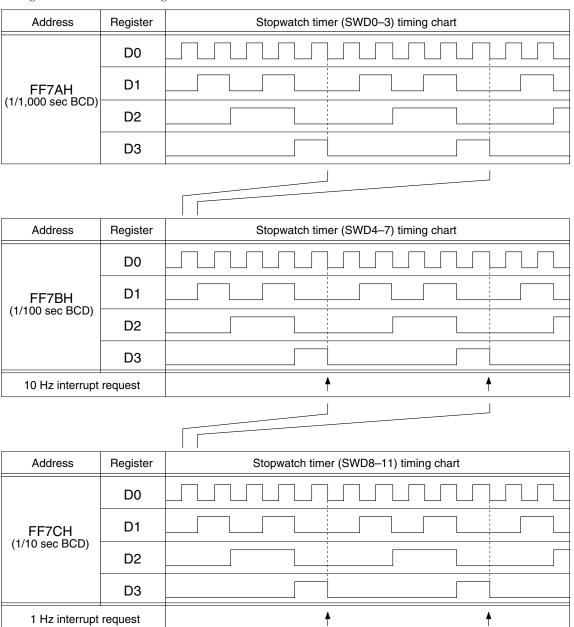

|      | 4.10.2 Counter and prescaler                      |           |

|      | 4.10.3 Capture buffer and hold function           |           |

|      | 4.10.4 Stopwatch timer RUN/STOP and reset         |           |

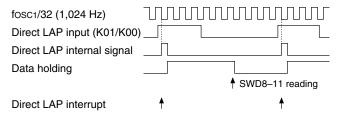

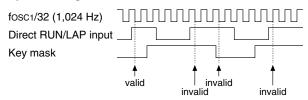

|      | 4.10.5 Direct input function and key mask         |           |

|      | 4.10.6 Interrupt function                         |           |

|      | 4.10.7 I/O memory of stopwatch timer              |           |

|      | <i>4.10.8 Programming notes</i>                   |           |

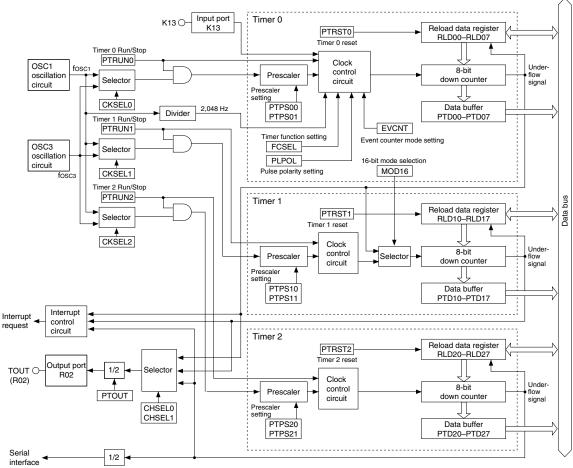

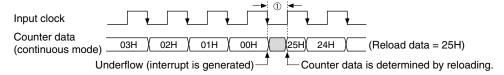

| 4.11 | Programmable Timer                                | <i>78</i> |

|      | 4.11.1 Configuration of programmable timer        |           |

|      | 4.11.2 Basic count operation                      |           |

|      | 4.11.3 Setting the input clock                    |           |

|      | 4.11.4 Event counter mode (timer 0)               |           |

|      | 4.11.5 16-bit timer (timer 0 + timer 1)           |           |

|      | <i>4.11.6 Interrupt function</i>                  |           |

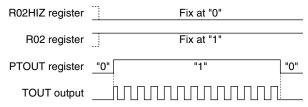

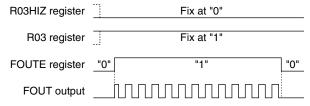

|      | <i>4.11.7 Control of TOUT output</i>              |           |

|      | 4.11.8 Transfer rate setting for serial interface |           |

|      | 4.11.9 I/O memory of programmable timer           |           |

|      | 4 11 10 Programming notes 89                      |           |

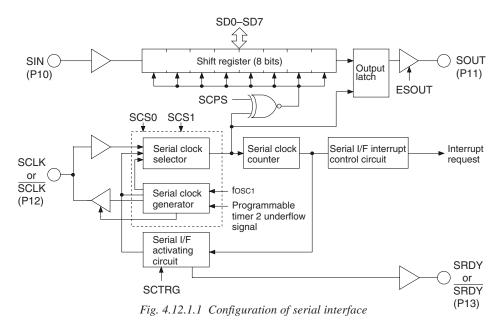

|           | 4.12 | Serial Interface (SIN, SOUT, SCLK, SRDY)              | 90  |

|-----------|------|-------------------------------------------------------|-----|

|           |      | 4.12.1 Configuration of serial interface              | 90  |

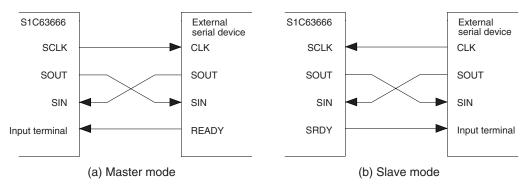

|           |      | 4.12.2 Mask option                                    |     |

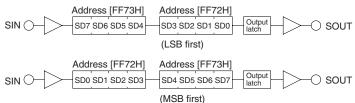

|           |      | 4.12.3 Master mode and slave mode of serial interface |     |

|           |      | 4.12.4 Data input/output and interrupt function       |     |

|           |      | 4.12.5 I/O memory of serial interface                 |     |

|           |      | 4.12.6 Programming notes                              |     |

|           | 4.13 | Sound Generator                                       |     |

|           |      | 4.13.1 Configuration of sound generator               |     |

|           |      | 4.13.2 Control of buzzer output                       |     |

|           |      | 4.13.3 Setting of buzzer frequency and sound level    |     |

|           |      | 4.13.4 Digital envelope                               |     |

|           |      | 4.13.5 One-shot output                                |     |

|           |      | 4.13.7 Programming notes                              |     |

|           | 111  |                                                       |     |

|           | 4.14 | Integer Multiplier                                    |     |

|           |      | 4.14.1 Configuration of integer multiplier            |     |

|           |      | 4.14.2 Multiplication mode                            |     |

|           |      | 4.14.4 Execution cycle                                |     |

|           |      | 4.14.5 I/O memory of integer multiplier               |     |

|           |      | 4.14.6 Programming note                               |     |

|           | 1 15 |                                                       |     |

|           | 4.13 | R/f Converter                                         |     |

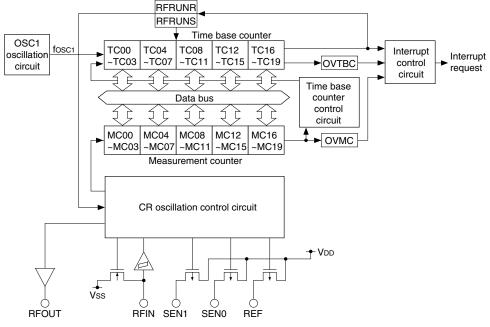

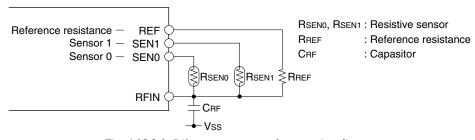

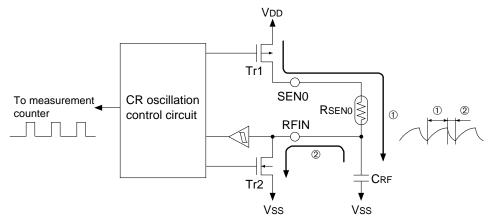

|           |      | 4.15.1 Configuration of R/f converter                 |     |

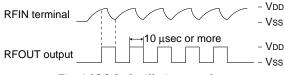

|           |      | 4.15.3 Operation of R/f conversion                    |     |

|           |      | 4.15.4 Interrupt function                             |     |

|           |      | 4.15.5 I/O memory of R/f converter                    |     |

|           |      | 4.15.6 Programming notes                              |     |

|           | 4 16 | Analog Comparator                                     |     |

|           | 7.10 | 4.16.1 Configuration of analog comparator             |     |

|           |      | 4.16.2 Analog comparator operation                    |     |

|           |      | 4.16.3 I/O memory of analog comparator                |     |

|           |      | 4.16.4 Programming notes                              |     |

|           | 4 17 | SVD (Supply Voltage Detection) Circuit                |     |

|           | 7.17 | 4.17.1 Configuration of SVD circuit                   |     |

|           |      | 4.17.2 Mask option                                    |     |

|           |      | 4.17.3 SVD operation                                  |     |

|           |      | 4.17.4 I/O memory of SVD circuit                      |     |

|           |      | 4.17.5 Programming notes                              | 126 |

|           | 4.18 | Interrupt and HALT                                    | 127 |

|           |      | 4.18.1 Interrupt factor                               |     |

|           |      | 4.18.2 Interrupt mask                                 |     |

|           |      | 4.18.3 Interrupt vector                               |     |

|           |      | 4.18.4 I/O memory of interrupt                        | 131 |

|           |      | 4.18.5 Programming notes                              | 133 |

| CHAPTER 5 | Sin  | IMARY OF NOTES                                        | 134 |

| CHAITER J | 5.1  | MARY OF NOTES  Notes for Low Current Consumption      |     |

|           | 5.2  | Summary of Notes by Function                          |     |

|           |      | * *                                                   |     |

|           | 5.3  | Precautions on Mounting                               | 139 |

| CHAPTER 6 | BAS  | IC EXTERNAL WIRING DIAGRAM                            | 141 |

|           |      |                                                       |     |

| CHAPTER 7 | $E_{LE}$ | ECTRICAL CHARACTERISTICS                                     | 142 |

|-----------|----------|--------------------------------------------------------------|-----|

|           | 7.1      | Absolute Maximum Rating                                      | 142 |

|           | 7.2      | Recommended Operating Conditions                             | 142 |

|           | 7.3      | DC Characteristics                                           | 142 |

|           | 7.4      | Analog Circuit Characteristics and Power Current Consumption | 143 |

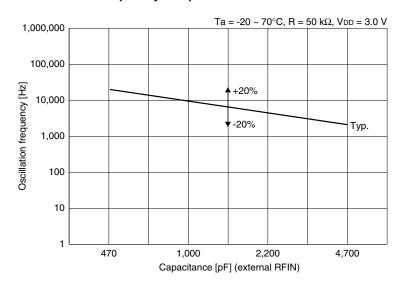

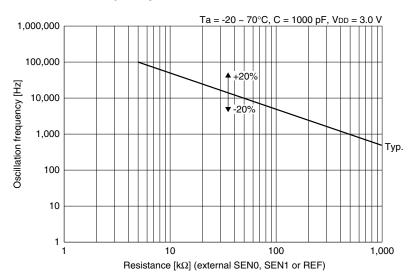

|           | 7.5      | Oscillation Characteristics                                  | 144 |

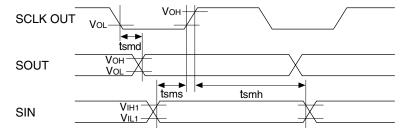

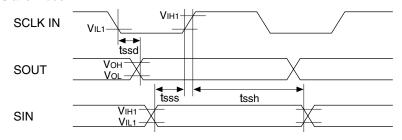

|           | 7.6      | Serial Interface AC Characteristics                          | 146 |

|           | 7.7      | Timing Chart                                                 | 147 |

|           | 7.8      | R/f Converter Characteristics                                | 147 |

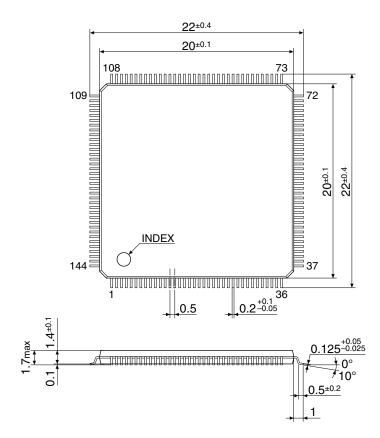

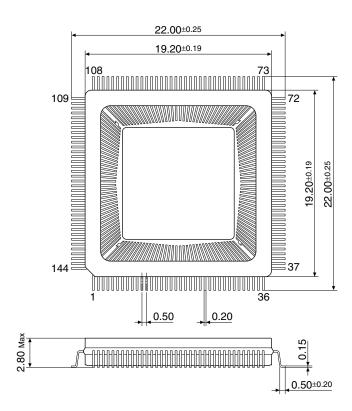

| CHAPTER 8 | PAC      | CKAGE                                                        | 148 |

|           | 8.1      | Plastic Package                                              |     |

|           | 8.2      | Ceramic Package for Test Samples                             | 149 |

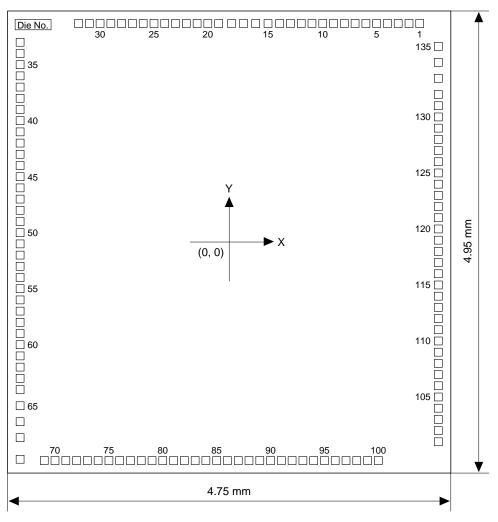

| CHAPTER 9 | PAL      | LAYOUT                                                       | 150 |

|           | 9.1      | Diagram of Pad Layout                                        |     |

|           | 9.2      | Pad Coordinates                                              | 151 |

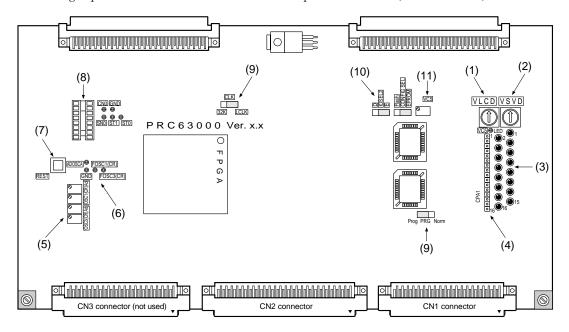

| APPENDIX  | S51      | U1C63000P1 Manual                                            |     |

|           |          | RIPHERAL CIRCUIT BOARD FOR S1C63666)                         | 152 |

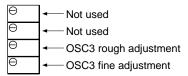

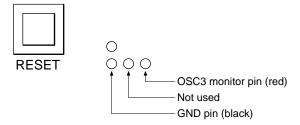

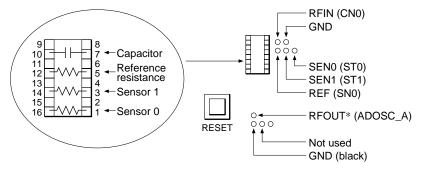

|           | A.1      | Names and Functions of Each Part                             | 152 |

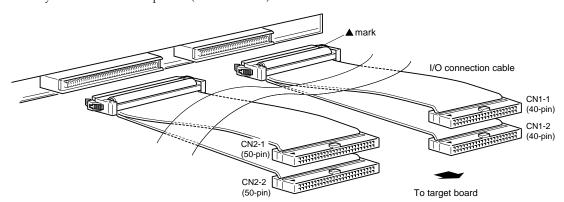

|           | A.2      | Connecting to the Target System                              | 155 |

|           | A.3      | Usage Precautions                                            |     |

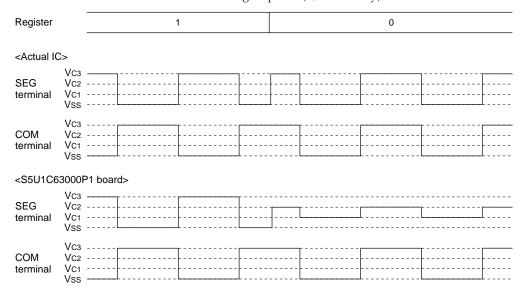

|           |          | A.3.2 Differences with the actual IC                         |     |

# CHAPTER 1 OUTLINE

The S1C63666 is a microcomputer which has a high-performance 4-bit CPU S1C63000 as the core CPU, ROM (16,384 words  $\times$  13 bits), RAM (5,120 words  $\times$  4 bits), multiply-divide circuit, serial interface, watchdog timer, programmable timer, time base counters (2 systems), an LCD driver that can drive a maximum 64 segments  $\times$  8 commons, sound generator and R/f converter built-in. The S1C63666 features low current consumption, this makes it suitable for battery driven portable equipment with R/f converter.

# 1.1 Features

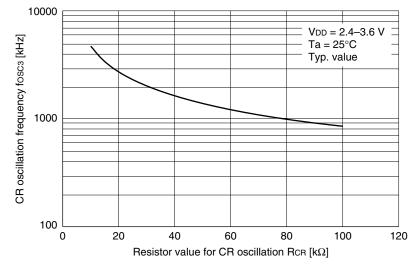

|                                        | . 32.768 kHz (Typ.) crystal oscillation circuit<br>. 4 MHz (Max.) ceramic or 1.4 MHz (Typ.) CR oscillation circuit (*1) |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Instruction set                        | . Basic instruction: 46 types (411 instructions with all) Addressing mode: 8 types                                      |

| Instruction execution time             | During operation at 32.768 kHz: 61 μsec 122 μsec 183 μsec During operation at 4 MHz: 0.5 μsec 1 μsec 1.5 μsec           |

| ROM capacity                           |                                                                                                                         |

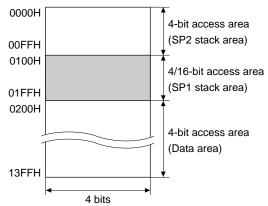

| RAM capacity                           | . Data memory: $5,120 \text{ words} \times 4 \text{ bits}$<br>Display memory: $128 \text{ words} \times 4 \text{ bits}$ |

|                                        | . 8 bits (Pull-down resistors may be supplemented *1)                                                                   |

| Output port                            | . 8 bits (It is possible to switch the 2 bits to special output *2)                                                     |

|                                        | . 8 bits (It is possible to switch the 4 bits to serial I/F input/output *2)                                            |

|                                        | . 1 port (8-bit clock synchronous system)                                                                               |

|                                        | . 64 segments × 4, 5 or 8 commons (*2)                                                                                  |

| Time base counter                      |                                                                                                                         |

|                                        | Stopwatch timer $(1/1000 \text{ sec}, \text{ with direct key input function})$                                          |

| Programmable timer                     | . 8 bits $\times$ 3 ch. or 16 bits $\times$ 1 ch. + 8 bits $\times$ 1 ch. (*2)                                          |

| Watchdog timer                         | . Built-in                                                                                                              |

| Sound generator                        | . With envelope and 1-shot output functions                                                                             |

| R/f converter                          | . 2 ch., CR oscillation type, 20-bit counter                                                                            |

| Multiply-divide circuit                | . 8-bit accumulator $\times$ 1 ch.                                                                                      |

|                                        | Multiplication: 8 bits $\times$ 8 bits $\rightarrow$ 16-bit product                                                     |

|                                        | Division: 16 bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder                                        |

| Analog comparator                      | . 1 ch.                                                                                                                 |

| Supply voltage detection (SVD) circuit | . 4 criteria voltages are selectable from 8 types (1.85 to 2.90 V *1)                                                   |

|                                        | (External voltage detection is possible *1)                                                                             |

|                                        | . Input port interrupt: 2 systems                                                                                       |

| Internal interrupt                     | . Clock timer interrupt: 4 systems                                                                                      |

|                                        | Stopwatch timer interrupt: 2 systems                                                                                    |

|                                        | Programmable timer interrupt: 2 systems                                                                                 |

|                                        | Serial interface interrupt: 1 system                                                                                    |

|                                        | R/f converter interrupt: 1 system                                                                                       |

| Power supply voltage                   | . 2.4 to 3.6 V: Max. 4 MHz operation in normal mode                                                                     |

|                                        | 2.4 to 3.6 V: 32 kHz operation in halver mode                                                                           |

| Operating temperature range            |                                                                                                                         |

| Current consumption (Typ.)             | . Low-speed operation (OSC1 = 32 kHz crystal oscillation):                                                              |

|                                        | During HALT 3.0 V (LCD ON, halver mode) 0.65 μA                                                                         |

|                                        | During operation 3.0 V (LCD ON, halver mode) 2.5 μA                                                                     |

|                                        | High-speed operation (OSC3):                                                                                            |

|                                        | During operation 3.0 V (LCD ON) 1 mA                                                                                    |

| Package                                |                                                                                                                         |

|                                        | *1: Can be selected with mask option *2: Can be selected with software                                                  |

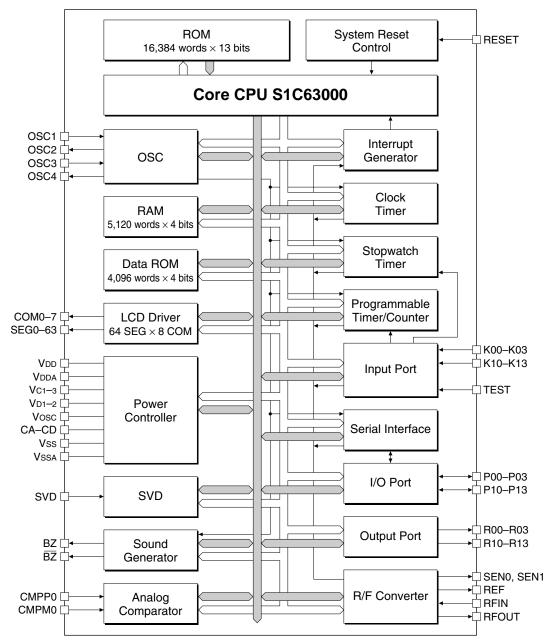

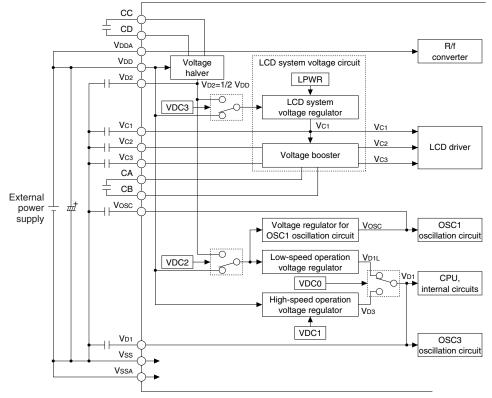

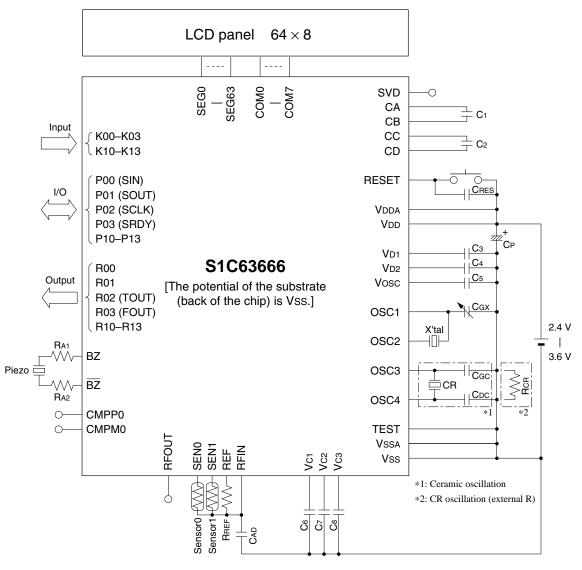

# 1.2 Block Diagram

Fig. 1.2.1 Block diagram

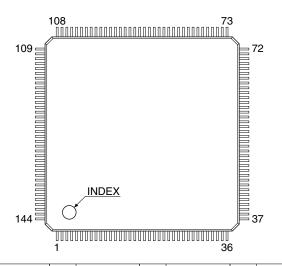

# 1.3 Pin Layout Diagram

# QFP20-144pin

| No. | Pin name        | No. | Pin name | No.     | Pin name                 | No. | Pin name |

|-----|-----------------|-----|----------|---------|--------------------------|-----|----------|

| 1   | N.C.            | 37  | N.C.     | 73      | N.C.                     | 109 | N.C.     |

| 2   | COM0            | 38  | SEG32    | 74 N.C. |                          | 110 | SEG0     |

| 3   | COM1            | 39  | SEG33    | 75      | N.C.                     | 111 | SEG1     |

| 4   | COM2            | 40  | SEG34    | 76      | COM4                     | 112 | SEG2     |

| 5   | COM3            | 41  | SEG35    | 77      | COM5                     | 113 | SEG3     |

| 6   | CA              | 42  | SEG36    | 78      | COM6                     | 114 | SEG4     |

| 7   | CB              | 43  | SEG37    | 79      | COM7                     | 115 | SEG5     |

| 8   | Vc1             | 44  | SEG38    | 80      | $V_{\mathrm{DD}}$        | 116 | SEG6     |

| 9   | Vc2             | 45  | SEG39    | 81      | K00                      | 117 | SEG7     |

| 10  | Vc3             | 46  | SEG40    | 82      | K01                      | 118 | SEG8     |

| 11  | CMPP0           | 47  | SEG41    | 83      | K02                      | 119 | SEG9     |

| 12  | CMPM0           | 48  | SEG42    | 84      | K03                      | 120 | SEG10    |

| 13  | SVD             | 49  | SEG43    | 85      | K10                      | 121 | SEG11    |

| 14  | Vssa            | 50  | SEG44    | 86      | K11                      | 122 | SEG12    |

| 15  | RFOUT           | 51  | SEG45    | 87      | K12                      | 123 | SEG13    |

| 16  | RFIN            | 52  | SEG46    | 88      | K13                      | 124 | SEG14    |

| 17  | REF             | 53  | SEG47    | 89      | P00                      | 125 | SEG15    |

| 18  | SEN0            | 54  | SEG48    | 90      | P01                      | 126 | SEG16    |

| 19  | SEN1            | 55  | SEG49    | 91      | P02                      | 127 | SEG17    |

| 20  | Vdda            | 56  | SEG50    | 92      | P03                      | 128 | SEG18    |

| 21  | CC              | 57  | SEG51    | 93      | P10                      | 129 | SEG19    |

| 22  | CD              | 58  | SEG52    | 94      | P11                      | 130 | SEG20    |

| 23  | V <sub>D2</sub> | 59  | SEG53    | 95      | P12                      | 131 | SEG21    |

| 24  | Vdd             | 60  | SEG54    | 96      | P13                      | 132 | SEG22    |

| 25  | Vosc            | 61  | SEG55    | 97      | R00                      | 133 | SEG23    |

| 26  | OSC1            | 62  | SEG56    | 98      | R01                      | 134 | SEG24    |

| 27  | OSC2            | 63  | SEG57    | 99      | R02                      | 135 | SEG25    |

| 28  | $V_{D1}$        | 64  | SEG58    | 100     | R03                      | 136 | SEG26    |

| 29  | OSC3            | 65  | SEG59    | 101     | R10                      | 137 | SEG27    |

| 30  | OSC4            | 66  | SEG60    | 102     | R11                      | 138 | SEG28    |

| 31  | Vss             | 67  | SEG61    | 103     | R12                      | 139 | SEG29    |

| 32  | TEST            | 68  | SEG62    | 104     | R13                      | 140 | SEG30    |

| 33  | RESET           | 69  | SEG63    | 105     | BZ                       | 141 | SEG31    |

| 34  | N.C.            | 70  | N.C.     | 106     | $\overline{\mathrm{BZ}}$ | 142 | N.C.     |

| 35  | N.C.            | 71  | N.C.     | 107     | Vss                      | 143 | N.C.     |

| 36  | N.C.            | 72  | N.C.     | 108     | N.C.                     | 144 | N.C.     |

N.C.: No Connection

Fig. 1.3.1 Pin layout diagram (QFP20-144pin)

# 1.4 Pin Description

Table 1.4.1 Pin description

| Pin name        | Pin No.        | I/O | Function                                                               |

|-----------------|----------------|-----|------------------------------------------------------------------------|

| Vdd             | 24             | _   | Power (+) supply pin                                                   |

| Vss             | 31             | _   | Power (–) supply pin                                                   |

| Vdda            | 20             | _   | Analog system power (+) supply pin (=VDD)                              |

| Vssa            | 14             | _   | Analog system power (–) supply (=Vss)                                  |

| V <sub>D1</sub> | 28             | _   | Internal logic system regulated voltage output pin                     |

| V <sub>D2</sub> | 23             | -   | 1/2VDD voltage halver output pin                                       |

| Vosc            | 25             | ı   | Oscillation system regulated voltage output pin                        |

| VC1-VC3         | 8–10           | ı   | LCD system power supply pin                                            |

| CA, CB          | 6, 7           | ı   | LCD system voltage booster capacitor connecting pin                    |

| CC, CD          | 21, 22         | -   | Voltage halver capacitor connecting pin                                |

| OSC1            | 26             | I   | Crystal oscillation input pin                                          |

| OSC2            | 27             | О   | Crystal oscillation output pin                                         |

| OSC3            | 29             | I   | Ceramic or CR oscillation input pin (selected by mask option)          |

| OSC4            | 30             | О   | Ceramic or CR oscillation output pin (selected by mask option)         |

| K00-K03         | 81–84          | I   | Input port pins                                                        |

| K10-K13         | 85–88          | I   | Input port pins                                                        |

| P00             | 89             | I/O | I/O port or serial I/F data input pin (selected by software)           |

| P01             | 90             | I/O | I/O port or serial I/F data output pin (selected by software)          |

| P02             | 91             | I/O | I/O port or serial I/F clock I/O pin (selected by software)            |

| P03             | 92             | I/O | I/O port or serial I/F ready signal output pin (selected by software)  |

| P10-P13         | 93–96          | I/O | I/O port pins                                                          |

| R00             | 97             | О   | Output port pin                                                        |

| R01             | 98             | О   | Output port pin                                                        |

| R02             | 99             | О   | Output port of TOUT output pin (selected by software)                  |

| R03             | 100            | О   | Output port or FOUT output pin (selected by software)                  |

| R10-R13         | 101–104        | О   | Output port pins                                                       |

| COM0-COM7       | 2–5, 76–79     | О   | LCD common output pin (1/4, 1/5 or 1/8 duty is selectable by software) |

| SEG0-SEG63      | 110–141, 38–69 | О   | LCD segment output pin                                                 |

| SEN0            | 18             | О   | R/f converter sensor 0 CR oscillation output pin                       |

| SEN1            | 19             | О   | R/f converter sensor 1 CR oscillation output pin                       |

| REF             | 17             | О   | R/f converter reference resistor CR oscillation output pin             |

| RFIN            | 16             | I   | R/f converter CR oscillation input pin                                 |

| RFOUT           | 15             | О   | R/f converter oscillation frequency output pin                         |

| CMPP0           | 11             | I   | Analog comparator non-inverted input pin                               |

| CMPM0           | 12             | I   | Analog comparator inverted input pin                                   |

| BZ              | 105            | 0   | Sound output pin                                                       |

| BZ              | 106            | 0   | Sound inverted output pin                                              |

| SVD             | 13             | I   | SVD external voltage input pin                                         |

| RESET           | 33             | I   | Initial reset input pin                                                |

| TEST            | 32             | I   | Testing input pin                                                      |

# 1.5 Mask Option

Mask options shown below are provided for the S1C63666. Several hardware specifications are prepared in each mask option, and one of them can be selected according to the application. The function option generator winfog and segment option generator winsog, that have been prepared as the development software tool of S1C63666, are used for this selection. Mask pattern of the IC is finally generated based on the data created by winfog and winsog. Refer to the "S5U1C63000A Manual" for winfog and winsog.

#### <Outline of the mask option>

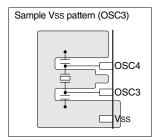

#### (1) OSC3 oscillation circuit

The OSC3 oscillator type can be selected from ceramic oscillation, CR oscillation (external R) and CR oscillation (built-in R). Refer to Section 4.4.3, "OSC3 oscillation circuit", for details.

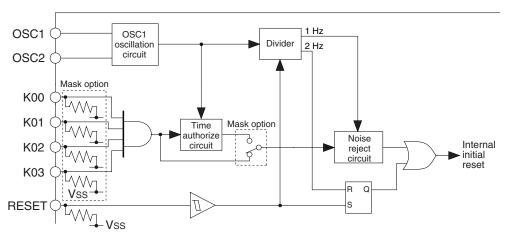

#### (2) External reset by simultaneous high input to the input port (K00-K03)

This function resets the IC when several keys are pressed simultaneously. The mask option is used to select whether this function is used or not. Further when the function is used, a combination of the input ports (K00–K03), which are connected to the keys to be pressed simultaneously, can be selected. Refer to Section 2.2.2, "Simultaneous high input to terminals K00–K03", for details.

#### (3) Time authorize circuit for the simultaneous high input reset function

When using the external reset function (shown in 2 above), using the time authorize circuit or not can be selected by mask option. The reset function works only when the input time of simultaneous low is more than the rule time if the time authorize circuit is being used.

Refer to Section 2.2.2, "Simultaneous high input to terminals K00–K03", for details.

#### (4) Input port pull-down resistor

The mask option is used to select whether the pull-down resistor is supplemented to the input ports or not. It is possible to select for each bit of the input ports.

Refer to Section 4.5.3, "Mask option", for details.

#### (5) Output specification of the output port

Either complementary output or P-channel open drain output can be selected as the output specification for the output ports R00–R03 and R10–R13. The selection is done in 1-bit units. Refer to Section 4.6.2, "Mask option", for details.

#### (6) Output specification of the I/O port

For the output specification when the I/O ports P00–P03 and P10–P13 are in the output mode, either complementary output or P-channel open drain output can be selected in 1-bit units. Refer to Section 4.7.2, "Mask option", for details.

#### (7) I/O port pull-down resistor

The mask option is used to select whether the pull-down resistor working in the input mode is supplemented to the I/O ports or not. It is possible to select for each bit of the input ports. Refer to Section 4.7.2, "Mask option", for details.

#### (8) Synchronous clock polarity in the serial interface

The polarity of the synchronous clock SCLK and the SRDY signal in slave mode of the serial interface is selected by mask option. Either positive polarity or negative polarity can be selected. Refer to Section 4.12.2, "Mask option", for details.

#### (9) External voltage detection of the SVD circuit

External voltage (SVD terminal voltage) detection can be selected in addition to supply voltage (VDD terminal-Vss terminal) detection. Refer to Section 4.17.2, "Mask option", for details.

#### (10) SVD voltage

Four criteria voltages for supply voltage detection can be selected from eight voltages. Refer to Section 4.17.2, "Mask option", for details.

#### (11) LCD drive power

Either the internal power supply or an external power supply can be selected for driving LCD. Refer to Section 4.8.2, "LCD drive power", for details.

#### (12) LCD segment specification

The display memory can be allocated to the optional SEG terminal. It is also possible to set the optional SEG terminal for DC output.

Refer to Section 4.8.5, "Segment option", for details.

# <Option list>

The following is the option list for the S1C63666.

Multiple selections are available in each option item as indicated in the option list. Select the spcifications that meet the target system and check the appropriate box. Be sure to record the spcifications for unused functions too.

| 1. OSC3 S                                                                                                          | SYSTEM CLOCK  1. Ceramic 2. CR (external R) 3. CR (built-in R)                                                                                                                                                                                                                                     |                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. MULTIP                                                                                                          | PLE KEY ENTRY RESET  ☐ 1. Not Use ☐ 2. Use (K00, K01, K02, ☐ 3. Use (K00, K01, K02)                                                                                                                                                                                                                | , K03)                                                                                                                                                                                        |

| 3. MULTIP                                                                                                          | ☐ 4. Use (K00, K01)  PLE KEY ENTRY RESET ☐ 1. Not Use                                                                                                                                                                                                                                              |                                                                                                                                                                                               |

| 4. INPUT I  • K00  • K01                                                                                           | ☐ 2. Use  PORT PULL DOWN RES  ☐ 1. With Resistor  ☐ 1. With Resistor                                                                                                                                                                                                                               | SISTOR  ☐ 2. Gate Direct ☐ 2. Gate Direct                                                                                                                                                     |

| • K01<br>• K02<br>• K03<br>• K10<br>• K11                                                                          | <ul><li>□ 1. With Resistor</li><li>□ 1. With Resistor</li><li>□ 1. With Resistor</li></ul>                                                                                                                                                                                                         | ☐ 2. Gate Direct                                                                                         |

| • K12<br>• K13                                                                                                     |                                                                                                                                                                                                                                                                                                    | ☐ 2. Gate Direct☐ 2. Gate Direct                                                                                                                                                              |

| <ul> <li>R00</li> <li>R01</li> <li>R02</li> <li>R03</li> <li>R10</li> <li>R11</li> <li>R12</li> <li>R13</li> </ul> | <ul> <li>□ 1. Complementary</li> </ul> | ☐ 2. Pch-OpenDrain |

**CHAPTER 1: OUTLINE**

| 6. I/O POR                                                                                                         | T OUTPUT SPECIFIC                                                                                                                                                                                                            | CATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>P00</li> <li>P01</li> <li>P02</li> <li>P03</li> <li>P10</li> <li>P11</li> <li>P12</li> <li>P13</li> </ul> | ☐ 1. Complementary☐ 1. Complementary     | ☐ 2. Pch-OpenDrain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7. I/O POR                                                                                                         | T PULL DOWN RESI                                                                                                                                                                                                             | STOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>P00</li> <li>P01</li> <li>P02</li> <li>P03</li> <li>P10</li> <li>P11</li> <li>P12</li> <li>P13</li> </ul> | ☐ 1. With Resistor☐ 1. | □ 2. Gate Direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8. SERIAL                                                                                                          | INTERFACE POLAR                                                                                                                                                                                                              | ITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| o. o                                                                                                               | ☐ 1. Positive<br>☐ 2. Negative                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9. SVD EX                                                                                                          | TERNAL VOLTAGE D  ☐ 1. Not Use ☐ 2. Use                                                                                                                                                                                      | DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10. SVD D                                                                                                          | ETECTION VOLTAGE                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| • 1<br>• 2<br>• 3<br>• 4                                                                                           | $\square$ 1. 1.85/0.98 V $\square$ 2. 2 $\square$ 1. 1.85/0.98 V $\square$ 2. 2                                                                                                                                              | $.00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.15 \ V \ \square \ 4. \ 2.30 \ V \ \square \ 5. \ 2.45 \ V \ \square \ 6. \ 2.60 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \\ .00 \ V \ \square \ 3. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \ \square \ 7. \ 2.75 \ V \ \square \ 8. \ 2.90 \ V \ \square \ 9. \ 9. \ 2.90 \ V \ \square \ 9. \ 9. \ 2.90 \ V \ \square \ 9. \ 9. \ 9. \ 9. \ $ |

| 11. LCD D                                                                                                          | RIVING POWER                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                    | <ul><li>□ 1. Internal Power</li><li>□ 2. External Power</li><li>□ 3. External Power</li></ul>                                                                                                                                | (3.0 V panel) 3 V, VDD=VC2 (4.5 V panel) 3 V, VDD=VC3 (3.0 V panel) 2 V, VDD=VC3, VC1=VC2 (3.0 V panel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## 12. SEGMENT OPTION

| Pin                                                                                                                                                                                                                                                                           | (   | ОМ | 0  | (        | COM   | 11                                               | (      | ОМ    | 2        | (        | OM |   | s (Fo | OM    | 4     | (    | ЮМ | 5    | (        | COM6 COM7 Output specificati |      |   |   |   |                         | ıtion             |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|----|----------|-------|--------------------------------------------------|--------|-------|----------|----------|----|---|-------|-------|-------|------|----|------|----------|------------------------------|------|---|---|---|-------------------------|-------------------|-------|

| name                                                                                                                                                                                                                                                                          | Н   | _  | D  | Н        | L     | D                                                | Н      | L     | D        | Н        | L  | D | Н     | L     | D     | Н    | L  | D    | Н        | L                            | Б    | Н | L | D | Output spe              | Juliua            | LIOII |

| SEG0                                                                                                                                                                                                                                                                          |     | _  | Ť  |          | Ť     | Ť                                                |        | _     | _        | <u> </u> | _  | Ť |       | _     | _     |      | _  | _    |          | <u> </u>                     | Ť    |   | _ | _ | SEG output              | $\Box$ S          | _     |

| SEG1                                                                                                                                                                                                                                                                          |     |    |    |          |       |                                                  |        |       |          |          |    |   |       |       |       |      |    |      |          |                              |      |   |   |   | DC output               | □C                |       |

| SEG2                                                                                                                                                                                                                                                                          |     |    |    |          |       |                                                  |        |       |          |          |    |   |       |       |       |      |    |      |          |                              |      |   |   |   | SEG output              |                   | _     |

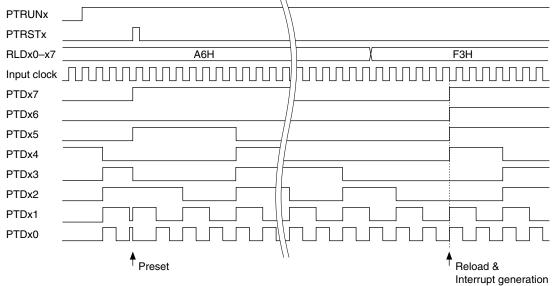

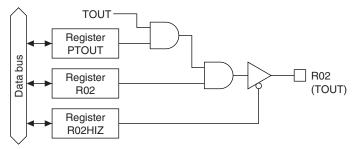

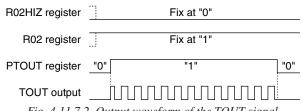

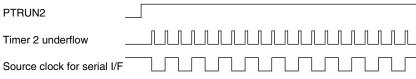

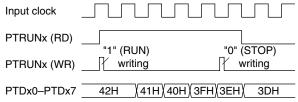

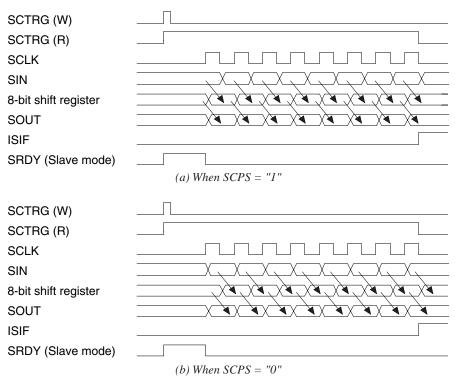

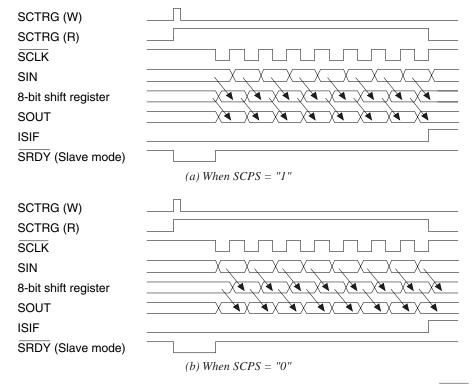

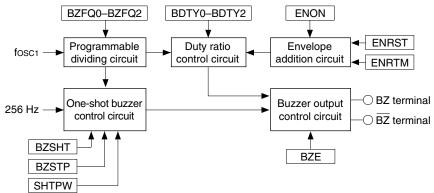

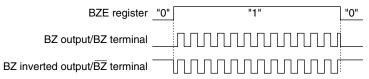

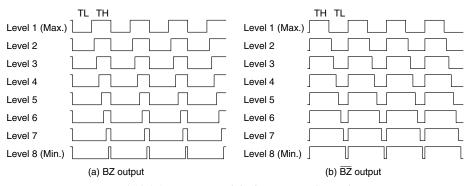

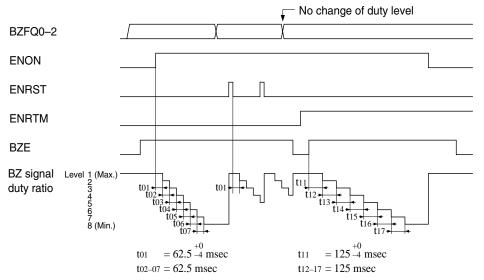

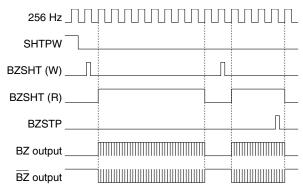

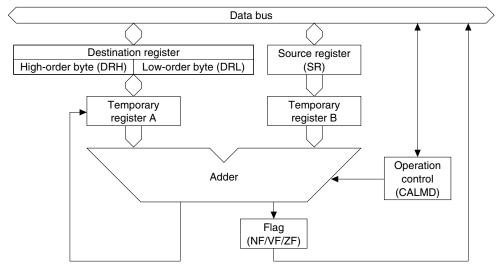

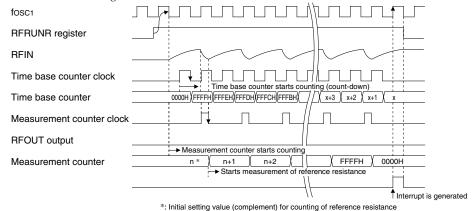

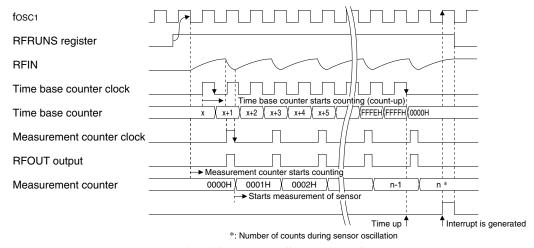

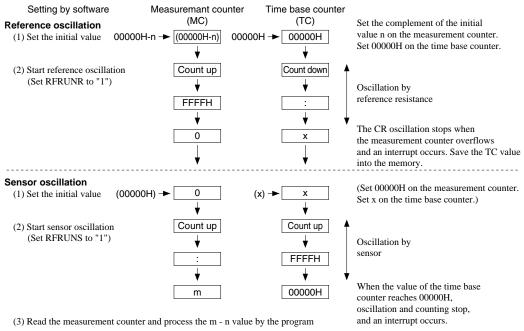

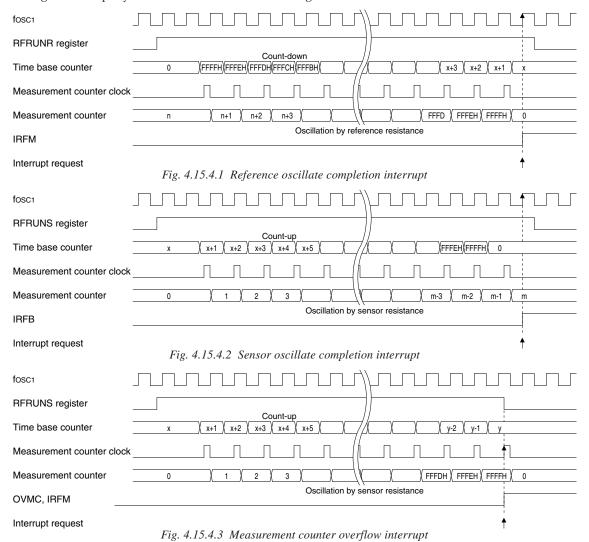

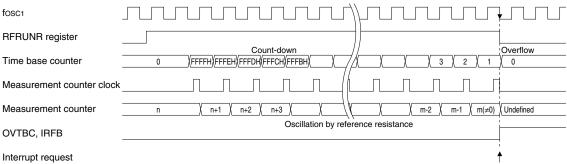

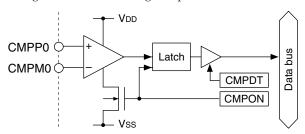

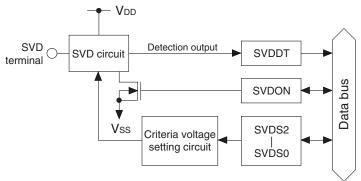

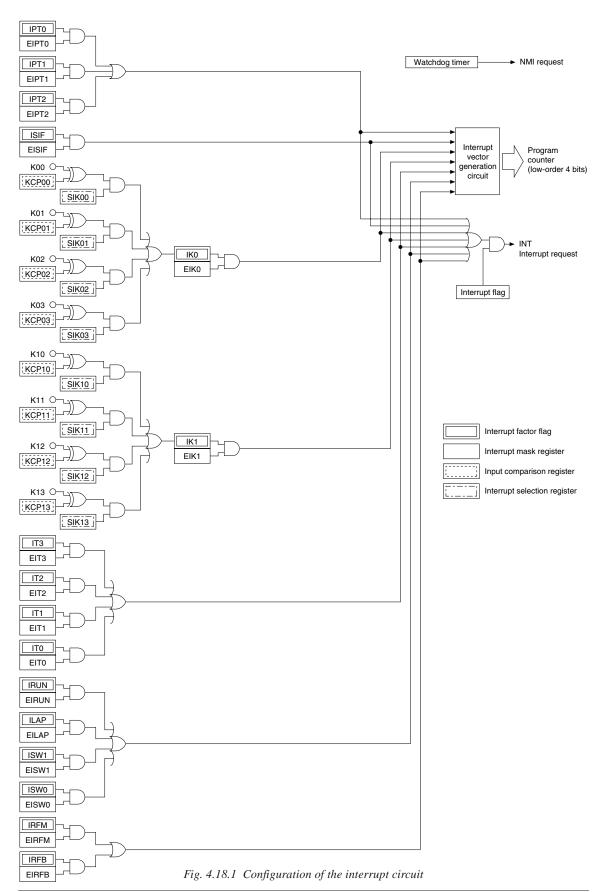

| SEG3                                                                                                                                                                                                                                                                          |     |    |    |          |       |                                                  |        |       |          |          |    |   |       |       |       |      |    |      |          |                              |      |   |   |   | DC output               | $\Box$ C          |       |