# 1. DESCRIPTION

The S1D16702 is a 68 output low-power resistance common (row) driver which is suitable for driving a very high capacity dotmatrix LCD panels up to a duty ratio of 1/300. It is intended to be used in conjunction with the S1D16006 as a pair.

Since the S1D16006 is so designed to drive LCD's over a wide range of voltages, and also the maximum potential V0 of its LCD drive bias voltages is isolated from VDD to allow the LCD driving bias voltages to be externally generated optionally with a high accuracy, it can cope with a wide range of LCD panels.

The S1D16702 is featured in its simple pad layout which is easy in mounting PC boards in addition to its selectable bidirectional driver output sequence. It also has 68 LCD output segments of high pressure resistance and low output impedance.

It can display the  $65 \times 132$  panel when used as the expansion driver of S1D15301 being built in RAM (S1D16702\*01\*\*).

# 2. FEATURES

- Number of LCD drive output segments: 68

- Common output ON resistance:  $700 \Omega$  (Typ.)

- Display duty ratio: 1/64 to 1/300 (Reference)

- Display capacity: Possible to display  $640 \times 480$  dots when used in combination with S1D16006.

- Selectable pin output shift direction

- Instantaneous display blanking enabled by inhibit function (S1D16702\*00\*\*)

- Non-bias display off function (S1D16702\*01\*\*)

- Adjustable offset bias of LCD power to VDD level

- Wide range of LCD drive voltages: -7 V to -28 V (Absolute maximum rated voltage: -30 V)

- Logic system power supply: -2.7 V to -5.5 V

- Shipping pattern S1D16702D00A\* (Al pad chip) S1D16702D01A\* (Al pad chip) S1D16702F00A\* (80-pin QFP5)

- No radial rays countermeasure taken in designing

- Non-bias display off function

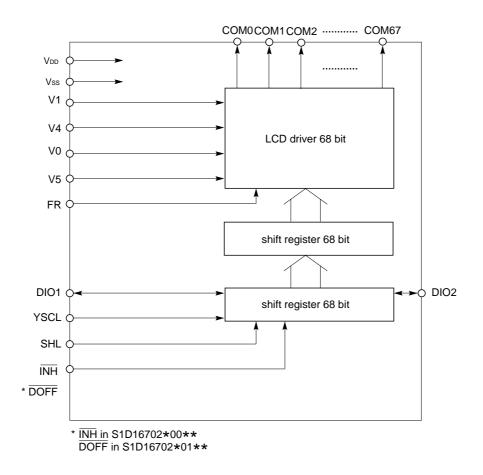

# **3. BLOCK DIAGRAM**

# 4. PIN DESCRIPTION

| Pin name          | I/O          |                             | Function                                                                                                                                                                                                                                                          |               |            |                     |         |     | Number<br>of pins |

|-------------------|--------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|---------------------|---------|-----|-------------------|

| COM0 to<br>COM67  | 0            |                             | LCD drive common (row) output<br>The output changes at the YSCL falling edge.                                                                                                                                                                                     |               |            |                     |         |     | 68                |

| DIO1,<br>DIO2     | I/O          | To be se                    | 100-bit shift register serial data input/output<br>Fo be set to input or output according to the SHL input<br>Fhe output changes at the YSCL falling edge.                                                                                                        |               |            |                     |         |     | 2                 |

| YSCL              | I            |                             | Serial data shift clock input<br>The scanning data is shifted at the falling edge.                                                                                                                                                                                |               |            |                     |         |     | 1                 |

|                   |              |                             | ata latch puls                                                                                                                                                                                                                                                    | •             |            | 0 00 /              |         |     |                   |

| 0.11              |              | SHL                         | COM outpu                                                                                                                                                                                                                                                         | t shift d     | irection   | DIO1                | 1       |     |                   |

| SHL               | I            | LOW                         | 0                                                                                                                                                                                                                                                                 | $\rightarrow$ | 67         | Input               | Output  |     |                   |

|                   |              | HIGH                        | 67                                                                                                                                                                                                                                                                | $\rightarrow$ | 0          | Ourput              | Input   |     |                   |

| DOFF              | I            | content o                   | lay blanking o<br>f shift registe<br>he non-selec                                                                                                                                                                                                                 | r is clea     | ared and a | all common          | outputs | )   | 1                 |

| ĪNĦ               | I            | When LC<br>common<br>Commor | CD display blanking control input<br>/hen LOW is input, the content of shift register is cleared and all<br>pmmon outputs become the non-select level instantaneously.<br>ommon output = V4 (when FR = LOW)<br>ommon output = V1 (when FR = HIGH) (S1D16702*00**) |               |            |                     |         | ıll | (1)               |

| FR                | I            | LCD driv                    | LCD drive output AC converted signal input                                                                                                                                                                                                                        |               |            |                     |         |     | 1                 |

| Vdd, Vss          | Power supply | Logic po                    | wer supply                                                                                                                                                                                                                                                        | Vdd           | : 0 V (GI  | ND) Vss: -{         | 5.0 V   |     | 2                 |

| V0, V1,<br>V4, V5 | Power supply | LCD driv                    | e power supp                                                                                                                                                                                                                                                      | -             |            | -28 V<br>1 >V4 ≥ V5 |         |     | 4                 |

INH in S1D16702\*00\*\* DOFF in S1D16702\*01\*\*

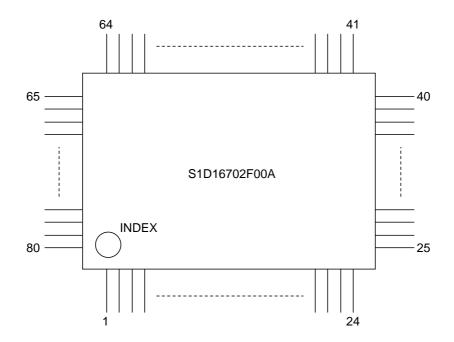

### **5. PIN LAYOUT**

### Package type: QFP-5 80pin

| PIN No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | COM 3    | 21      | COM 23   | 41      | COM 43   | 61      | COM 63   |

| 2       | COM 4    | 22      | COM 24   | 42      | COM 44   | 62      | COM 64   |

| 3       | COM 5    | 23      | COM 25   | 43      | COM 45   | 63      | COM 65   |

| 4       | COM 6    | 24      | COM 26   | 44      | COM 46   | 64      | COM 66   |

| 5       | COM 7    | 25      | COM 27   | 45      | COM 47   | 65      | COM 67   |

| 6       | COM 8    | 26      | COM 28   | 46      | COM 48   | 66      | DIO2     |

| 7       | COM 9    | 27      | COM 29   | 47      | COM 49   | 67      | ĪNH      |

| 8       | COM 10   | 28      | COM 30   | 48      | COM 50   | 68      | FR       |

| 9       | COM 11   | 29      | COM 31   | 49      | COM 51   | 69      | YSCL     |

| 10      | COM 12   | 30      | COM 32   | 50      | COM 52   | 70      | SHL      |

| 11      | COM 13   | 31      | COM 33   | 51      | COM 53   | 71      | Vdd      |

| 12      | COM 14   | 32      | COM 34   | 52      | COM 54   | 72      | Vss      |

| 13      | COM 15   | 33      | COM 35   | 53      | COM 55   | 73      | Vo       |

| 14      | COM 16   | 34      | COM 36   | 54      | COM 56   | 74      | V1       |

| 15      | COM 17   | 35      | COM 37   | 55      | COM 57   | 75      | V4       |

| 16      | COM 18   | 36      | COM 38   | 56      | COM 58   | 76      | V5       |

| 17      | COM 19   | 37      | COM 39   | 57      | COM 59   | 77      | DIO1     |

| 18      | COM 20   | 38      | COM 40   | 58      | COM 60   | 78      | COM 0    |

| 19      | COM 21   | 39      | COM 41   | 59      | COM 61   | 79      | COM 1    |

| 20      | COM 22   | 40      | COM 42   | 60      | COM 62   | 80      | COM 2    |

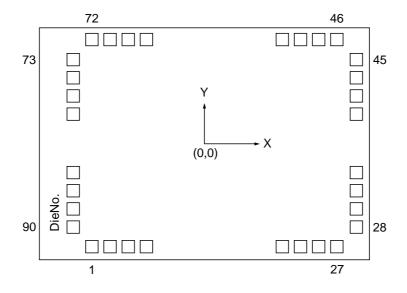

# 6. PAD

### Pad layout

#### • Pad center coordinates

| PAD | PIN                                 | Х     | Y     | PAD | PIN    | X    | Y    | PAD | PIN    | Х     | Y     |

|-----|-------------------------------------|-------|-------|-----|--------|------|------|-----|--------|-------|-------|

| NO. | NAME                                | ^     | I     | NO. | NAME   | ^    | I    | NO. | NAME   | ^     | T     |

| 1   | DM                                  | -1579 | -1357 | 31  | COM 29 | 1976 | -711 | 61  | COM 56 | -195  | 1357  |

| 2   | COM 3                               | -1449 |       | 32  | COM 30 |      | -581 | 62  | COM 57 | -324  |       |

| 3   | COM 4                               | -1320 |       | 33  | COM 31 |      | -452 | 63  | COM 58 | -453  |       |

| 4   | COM 5                               | -1191 |       | 34  | COM 32 |      | -323 | 64  | COM 59 | -583  |       |

| 5   | COM 6                               | -1062 |       | 35  | COM 33 |      | -194 | 65  | COM 60 | -712  |       |

| 6   | COM 7                               | -933  |       | 36  | COM 34 |      | -65  | 66  | COM 61 | -841  |       |

| 7   | COM 8                               | -803  |       | 37  | COM 35 |      | 65   | 67  | COM 62 | -970  |       |

| 8   | COM 9                               | -674  |       | 38  | COM 36 |      | 194  | 68  | COM 63 | -1099 |       |

| 9   | COM 10                              | -545  |       | 39  | COM 37 |      | 323  | 69  | COM 64 | -1229 |       |

| 10  | COM 11                              | -416  |       | 40  | COM 38 |      | 452  | 70  | COM 65 | -1358 |       |

| 11  | COM 12                              | -287  |       | 41  | COM 39 |      | 581  | 71  | COM 66 | -1487 | ♥     |

| 12  | COM 13                              | -154  |       | 42  | COM 40 |      | 711  | 72  | DM     | -1616 | 1357  |

| 13  | COM 14                              | -28   |       | 43  | COM 41 |      | 840  | 73  | DM     | -1865 | 1201  |

| 14  | COM 15                              | 101   |       | 44  | COM 42 | ♥    | 969  | 74  | COM 67 |       | 1071  |

| 15  | COM 16                              | 230   |       | 45  | DM     | 1976 | 1098 | 75  | DIO2   |       | 941   |

| 16  | COM 17                              | 359   |       | 46  | DM     | 1743 | 1357 | 76  | *1 INH |       | 715   |

| 17  | COM 18                              | 489   |       | 47  | DM     | 1614 |      | 77  | FR     |       | 585   |

| 18  | COM 19                              | 618   |       | 48  | COM 43 | 1485 |      | 78  | YSCL   |       | 455   |

| 19  | COM 20                              | 747   |       | 49  | COM 44 | 1355 |      | 79  | SHL    |       | 325   |

| 20  | COM 21                              | 876   |       | 50  | COM 45 | 1226 |      | 80  | Vdd    |       | 195   |

| 21  | COM 22                              | 1005  |       | 51  | COM 46 | 1097 |      | 81  | Vss    |       | 55    |

| 22  | COM 23                              | 1135  |       | 52  | COM 47 | 968  |      | 82  | Vo     |       | -112  |

| 23  | COM 24                              | 1264  |       | 53  | COM 48 | 839  |      | 83  | V1     |       | -252  |

| 24  | COM 25                              | 1393  |       | 54  | COM 49 | 709  |      | 84  | V4     |       | -391  |

| 25  | COM 26                              | 1522  |       | 55  | COM 50 | 580  |      | 85  | V5     |       | -531  |

| 26  | DM                                  | 1651  | ♥     | 56  | COM 51 | 451  |      | 86  | DIO1   |       | -671  |

| 27  | DM                                  | 1781  | -1357 | 57  | COM 52 | 322  |      | 87  | COM 0  |       | -810  |

| 28  | DM                                  | 1976  | -1098 | 58  | COM 53 | 193  |      | 88  | COM 1  |       | -941  |

| 29  | COM 27                              | 1976  | -969  | 59  | COM 54 | 63   | 🕇    | 89  | COM 2  | ♥     | -1071 |

| 30  | COM 28                              | 1976  | -840  | 60  | COM 55 | -66  | 1357 | 90  | DM     | -1865 | -1201 |

|     | *1 PAD No 76: INH for S1D16702*00** |       |       |     |        |      |      |     |        |       |       |

\*1 PAD No. 76: INH for S1D16702\*00\*\*

DOFF for S1D16702\*01\*\*

# 7. FUNCTIONAL DESCRIPTION

#### Shift register

This is a bidirectional shift register to transfer common data.

#### Level shifter

This is a level interface circuit used to convert the signal voltage level from the logic system level to LCD drive level.

#### LCD driver circuit

This driver outputs the LCD drive voltage.

The relationship among the display blanking signal INH, contents of shift register, AC converted signal FR and common output voltage is as shown in the table below:

|      | (S1D16702*00**)            |      |       |                  |  |  |  |  |  |  |

|------|----------------------------|------|-------|------------------|--|--|--|--|--|--|

| INH  | Contents of shift register | FR   | COM o | M output voltage |  |  |  |  |  |  |

|      | HIGH                       | HIGH | V5    | (Select level)   |  |  |  |  |  |  |

| HIGH | TIIGH                      | LOW  | Vo    |                  |  |  |  |  |  |  |

| пібп |                            | HIGH | V1    | (Non-select      |  |  |  |  |  |  |

|      | LOW                        | LOW  | V4    | level)           |  |  |  |  |  |  |

| LOW  | Fixed to LOW               | HIGH | V1    | (Non-select      |  |  |  |  |  |  |

| LOW  |                            | LOW  | V4    | level)           |  |  |  |  |  |  |

The relationship among the display blanking signal INH, contents of shift register, AC converted signal FR and common output voltage is as shown in the table below.

| (31010702*01 |                            |      |       |                       |  |  |  |  |

|--------------|----------------------------|------|-------|-----------------------|--|--|--|--|

| DOFF         | Contents of shift register | FR   | COM o | COM output voltage    |  |  |  |  |

|              | HIGH                       | HIGH | V5    | (Select level)        |  |  |  |  |

| HIGH         | TIIGH                      | LOW  | Vo    |                       |  |  |  |  |

| пюп          | LOW                        | HIGH | V1    | (Non-select           |  |  |  |  |

|              | LOW                        | LOW  | V4    | level)                |  |  |  |  |

| LOW          | Fixed to LOW               | _    | Vo    | (Non-select<br>level) |  |  |  |  |

#### (S1D16702\*01\*\*)

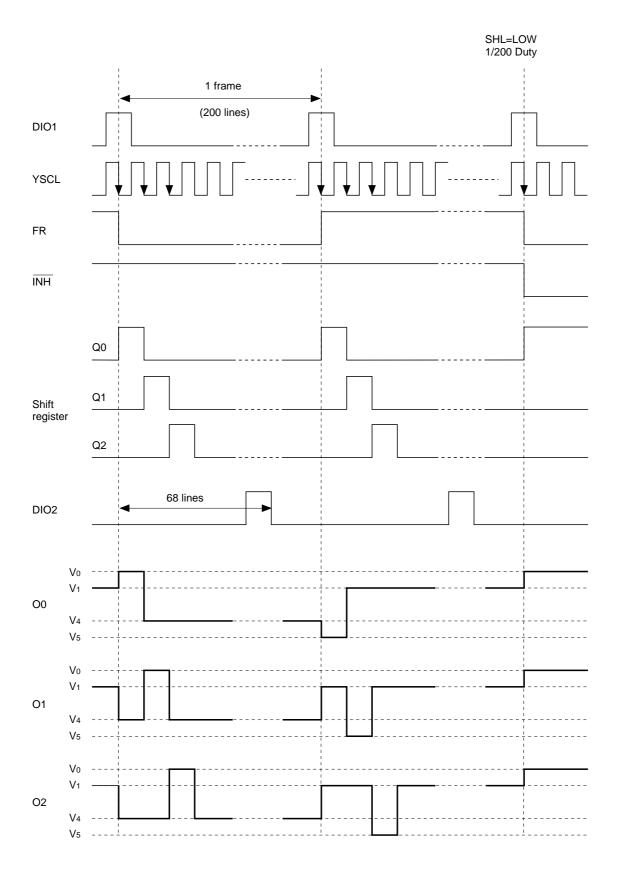

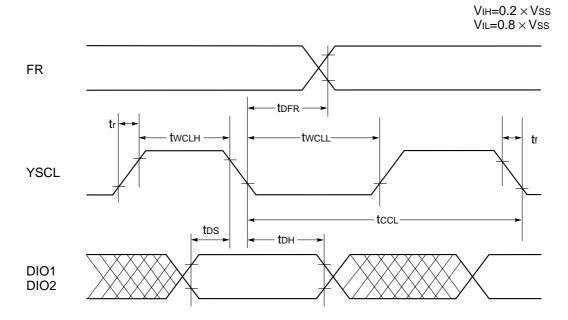

# **8. TIMING CHART**

# 9. ABSOLUTE MAXIMUM RATINGS

|                                |            |                 | Vdd=0V |

|--------------------------------|------------|-----------------|--------|

| Parameter                      | Symbol     | Rating          | Unit   |

| Supply voltage (1)             | Vss        | -7.0 to +0.3    | V      |

| Supply voltage (2)             | V5         | -30.0 to +0.3   | V      |

| Supply voltage (3)             | V0, V1, V4 | V5-0.3 to +0.3  | V      |

| Input voltage                  | Vi         | Vss-0.3 to +0.3 | V      |

| Output voltage                 | Vo         | Vss-0.3 to +0.3 | V      |

| Output current (1)             | lo         | 20              | mA     |

| Output current (2)             | Іосом      | 20              | mA     |

| Operating temperature          | Topr       | -40 to + 85     | °C     |

| Storing temperature            | Tstg       | -65 to +150     | °C     |

| Soldering temperature and time | Tsol       | 260°C · 10sec   | -      |

Notes:

1. The voltage of V0, V1 and V4 must always satisfy the condition of  $VDD \ge V0 \ge V1 \ge V4 \ge V5$ .

2. Floating of the logic system power during while the LCD drive system power is applied, or exceeding VSS = -2.6 V or more can cause permanent damage to the LSI. Functional operation under these conditions is not implied.

Care should be taken to the power supply sequence especially in the system power ON or OFF.

3. All the above voltage is based on VDD = 0 V.

# **10. ELECTRICAL CHARACTERISTICS**

### **DC** characteristics

| Parameter                                       | Symbol | Condition                                                                                                                                                        | Min.   | Тур. | Max.    | Unit | Applicable pin        |

|-------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---------|------|-----------------------|

| Supply voltage (1)                              | Vss    | _                                                                                                                                                                | -5.5   | -5.0 | -2.7    | V    | Vss                   |

| Recommended<br>operating voltage                | V5     | _                                                                                                                                                                | -28.0  | _    | -7.0    | V    | V5                    |

| Operation enable voltage                        | V5     | Functional operation                                                                                                                                             | _      | _    | -7.0    | V    | V5                    |

| Supply voltage (2)                              | Vo     | Recommended value                                                                                                                                                | -2.5   | -    | 0       | V    | Vo                    |

| Supply voltage (3)                              | V1     | Recommended value                                                                                                                                                | 2/9·V5 | _    | Vdd     | V    | V1                    |

| Supply voltage (4)                              | V4     | Recommended value                                                                                                                                                | V5     | _    | 7/9·V5  | V    | V4                    |

| HIGH input voltage (1)                          | Viн    |                                                                                                                                                                  | 0.2Vss | _    | 0       | V    | DIO1, DIO2,           |

| LOW input voltage (1)                           | VIL    | Vss=-2.7V to -5.5V                                                                                                                                               | Vss    | -    | 0.8Vss  | V    | YSCL, SHL, FR         |

| HIGH input voltage (2)                          | Viht   | Vss=-2.7V to -5.5V                                                                                                                                               | 0.2Vss | _    | 0       | V    | ĪNH                   |

| LOW input voltage (2)                           | Vilt   | . • 33=-2.7 • 10 -5.5 •                                                                                                                                          | Vss    | _    | 0.85Vss | V    |                       |

| HIGH output voltage                             | Vон    | loн=-0.3mA<br>loн=-0.2mA<br>(Vss=-2.7 to -4.5V)                                                                                                                  | -0.4   | _    | 0       | V    |                       |

| LOW output voltage                              | Vol    | IoL=+0.3mA<br>IoL=+0.2mA<br>(Vss=-2.7 to -4.5V)                                                                                                                  | Vss    | _    | Vss+0.4 | V    | - DIO1, DIO2          |

| Input leakage<br>current                        | lu     | $Vss \le Vin \le 0V$                                                                                                                                             | _      | _    | 2.0     | μΑ   | YSCL, SHL,<br>INH, FR |

| Input/output<br>leakage current                 | Ili/o  | $V_{SS} \le V_{IN} \le 0V$                                                                                                                                       | -      | -    | 5.0     | μΑ   | DIO1, DIO2            |

| Static current                                  | IDDS   | V5=-7.0 to -28.0V<br>VIH=VDD, VIL=VSS                                                                                                                            | -      | _    | 25      | μΑ   | Vdd                   |

| Output resistance                               | Rсом   | $ \begin{array}{c c} \Delta VON \\ = 0.5V \end{array} \begin{array}{c} V_{5=} & When the \\ V_1, V_4, V_0 \\ -20.0V & or V_5 \\ level is \\ output \end{array} $ | _      | 0.70 | 1.40    | kΩ   | COM0 to COM99         |

| Average operating<br>current<br>consumption (1) | ISS1   | Vss=-5.0V, VIH=VDD,<br>VIL=Vss, fyscL=12KHz,<br>Frame frequency=60Hz<br>Input data; HIGH at no load<br>every 1/200 duy<br>Other conditions are the               | -      | 7    | 15      | μΑ   | Vss                   |

|                                                 |        | same as $Vss = -3.0 V$                                                                                                                                           | -      | 5    | 10      |      |                       |

| Average operating<br>current<br>consumption (2) | Iss2   | Vss=-5.0V, $V1=-2.0V$ ,<br>V4=-18.0V, $V5=-20.0VOther conditions are thesame as in the item of Iss1.$                                                            | _      | 7    | 15      | μΑ   | V5                    |

| Input pin<br>capacitance                        | Сі     | Ta=25°C                                                                                                                                                          | _      | _    | 8       | pF   | YSCL, SHL,<br>ĪNĦ, FR |

| Input/output pin<br>capacitance                 | Ci/o   |                                                                                                                                                                  | _      | -    | 15      | pF   | DIO1, DIO2            |

| capacitance                                     | Ci/o   |                                                                                                                                                                  |        |      |         | ۲'   |                       |

Unless otherwise specified, VDD = V0 = 0V, Vss =  $-5.0V\pm10\%$ , Ta = -40 to  $85^{\circ}C$ .

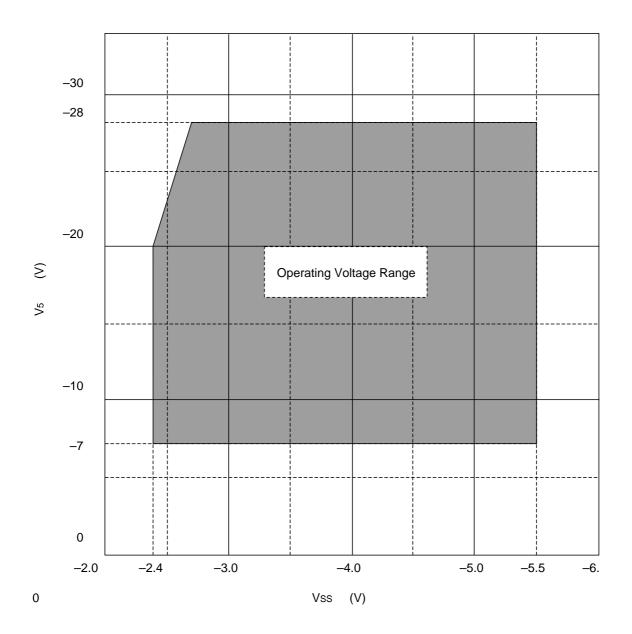

### **Operating Voltage Range VSS – V5**

V5 voltage must be set within the following operating voltage range of Vss - V5.

#### **AC Characteristics**

#### Input timing characteristics

#### Unless otherwise specified Vss=–5.0V $\pm$ 10%, Ta=–40 to 85°C

| Parameter               | Symbol | Condition | Min. | Max. | Unit |

|-------------------------|--------|-----------|------|------|------|

| Input signal rise time  | tr     | _         | -    | 50   | ns   |

| Input signal fall time  | tr     | -         | -    | 50   | ns   |

| YSCL period             | tccL   | _         | 500  | _    | ns   |

| YSCL HIGH pulsewidth    | twclh  | _         | 70   | _    | ns   |

| YSCL LOW pulsewidth     | twcll  | _         | 330  | _    | ns   |

| Data setup time         | tDS    | _         | 100  | _    | ns   |

| Data hold time          | tDH    | _         | 10   | _    | ns   |

| Allowable FR delay time | tDFR   | _         | -500 | 500  | ns   |

| Unless otherwise specified Vss=-2.7V to -4.5V, Ta=-40 to 85°C | ; |

|---------------------------------------------------------------|---|

|---------------------------------------------------------------|---|

| Parameter               | Symbol | Condition | Min. | Max. | Unit |

|-------------------------|--------|-----------|------|------|------|

| Input signal rise time  | tr     | _         | —    | 50   | ns   |

| Input signal fall time  | tr     | _         | _    | 50   | ns   |

| YSCL period             | tcc∟   | _         | 1000 | _    | ns   |

| YSCL HIGH pulsewidth    | twclh  | _         | 160  | _    | ns   |

| YSCL LOW pulsewidth     | twcll  | _         | 330  | _    | ns   |

| Data setup time         | tDS    | _         | 200  | _    | ns   |

| Data hold time          | tDH    | _         | 10   | _    | ns   |

| Allowable FR delay time | tdfr   | _         | -500 | 500  | ns   |

The standard applicable to tCCL, tWCLH, tWCLL, tDS and tDH when VSS = -2.4 V must be 1.3 times of that applies when VSS = -2.7 V to -4.5 V.

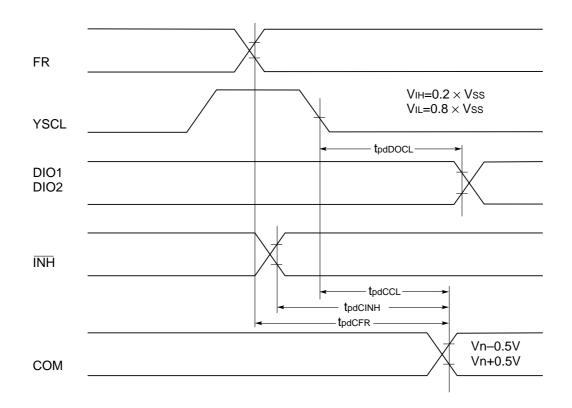

### **Output timing characteristics**

Unless otherwise specified Vss=–5.0V $\pm$ 10%, Ta=–40 to 85°C

| Parament                               | Symbol  | Condition  | Min. | Max. | Unit |

|----------------------------------------|---------|------------|------|------|------|

| (YSCL - fall to DIO) delay time        | tpdDOCL | CL=15pF    | 30   | 300  | ns   |

| (YSCL - fall to COM output) delay time | tpdcc∟  | V5=-7.0 to |      | 3.0  |      |

| (INH to COM output) delay time         | tpdcinh | –28.0V     | _    | 3.0  | μs   |

| (FR to COM output) delay time          | tpdcfr  | CL=100pF   | —    | 3.0  | μs   |

Unless otherwise specified Vss=-2.7V to -4.5V, Ta=-40 to 85°C

| Parament                               | Symbol  | Condition  | Min. | Max. | Unit |

|----------------------------------------|---------|------------|------|------|------|

| (YSCL - fall to DIO) delay time        | tpdDOCL | CL=15pF    | 60   | 600  | ns   |

| (YSCL - fall to COM output) delay time | tpdcc∟  | V5=-7.0 to |      | 3.0  |      |

| (INH to COM output) delay time         | tpdcinh | –28.0V     | _    | 3.0  | μs   |

| (FR to COM output) delay time          | tpdCFR  | CL=100pF   | _    | 3.0  | μs   |

The standard applicable when Vss = -2.4 V must be 1.3 times of that applies when Vss = -2.7 V to -4.5 V.

# **11. LCD DRIVE POWER**

#### Each voltage level forming method

To obtain each voltage level for LCD driving, it is the most simple to divide the resistance of potential as shown in the connection example.

On the other hand, to obtain a high quality display, it is necessary to raise the accuracy and constancy of each voltage level and to set the divided resistance value as low as possible in the range of system power capacity. Especially when a low-power LCD driving is required, set the divided resistance to a higher value and drive the LCD with a voltage follower by means of operational amplifier instead. In taking into consideration of a case where the operational amplifier is employed, the maximum potential level V0 for LCD driving has been isolated from the VDD pin. When the potential of  $V_0$  lowers than that of VDD and the potential difference between the two becomes larger, however, the capacity of LCD drive output driver lowers. To avoid it, use the system with the potential difference of 0 V to 2.5 V between V0 and VDD.

When no operational amplifier is used, connect V0 and VDD pins.

#### Note in power ON/OFF

Since this LSI is high in the voltage of LCD driving system, when a high voltage is applied to the LCD driving system with the logic system power supply kept floating, an overcurrent flows and LSI breaks down in some cases.

#### Be sure to follow the power ON/OFF sequence as shown below:

At power ON ... Logic system ON $\rightarrow$  LCD driving system ON or simultaneous ON of the bothAt power OFF ... LCD driving system OFF $\rightarrow$  Logic system OFF or simultaneous OFF of the both

#### **Precautions:**

Users of this development specification are reminded of the following precautions.

- 1. This development specification is subject to change without previous notice.

- 2. This specificatino does not warrant the user to exercise the industrial property right or other rights, nor does this specification vest such rights to the user.

Application examples provided in this specification are solely intended to ensure better understanding of the product. The manufacturer shall not be liable for any circuit related problem arising from using such examples.

Numeric representation of measure or size provided in the characteristics table is one obtained from the numeric line.

- 3. No part of this specification may be reproduced or duplicated in any form or by any means without the written permission of the manufacturer.

- 4. As for use of semiconductor elements, users are required to pay attention to the following points. [Precautions on the Product Handling in Light]

Characteristics of semiconductor elements are changed if they are exposed to light. Thus, exposing this IC to light can result in its in malfunction. In order to prevent IC malfunctioning due to light, make sure that the following measures are taken for the boards or products equipped with our IC.

- (1) Design and mounting procedure employed do not allow light to IC.

- (2) The inspection process is implemented in the environment that does not allow light to IC.

- (3) Light shielding measures are established not only for surface of IC but also for rear face and side faces, too.

# **12. DIFFERENT POINTS FROM REPLACEMENT PRODUCT**

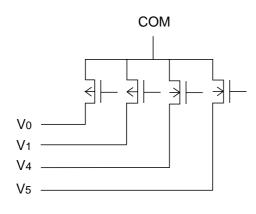

|                         | S1D16702*00**                         | S1D16300*****                |

|-------------------------|---------------------------------------|------------------------------|

| Function                | Bidirectional shift register          | Bidirectional shift register |

|                         | INH                                   | INH                          |

|                         | 68 output segments                    | 68 output segments           |

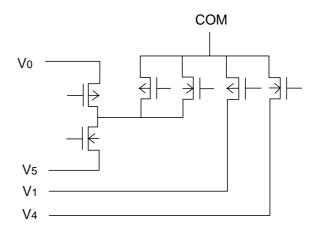

| Output Tr configuration | Fig. 1                                | Fig. 2                       |

| PAD layout              | Identical to the equivalent product   | _                            |

| PAD coordinates         | Different from the equivalent product | _                            |

Flg. 2