# Integrated Power Module for Small Appliance Motor Drive Applications

### **Description**

IRSM836-035MA is a 3A, 500V Integrated Power Module (IPM) designed for advanced appliance motor drive applications such as energy efficient fans and pumps. IR's technology offers an extremely compact, high performance AC motor-driver in an isolated package. This advanced IPM offers a combination of IR's low R<sub>DS(on)</sub> Trench MOSFET technology and the industry benchmark 3-phase high voltage, rugged driver in a small PQFN package. At only 12x12mm and featuring integrated bootstrap functionality, the compact footprint of this surface-mount package makes it suitable for applications that are space-constrained. Integrated over-current protection, fault reporting and under-voltage lockout functions deliver a high level of protection and fail-safe operation. IRSM836-035MA functions without a heat sink.

#### **Features**

- Integrated gate drivers and bootstrap functionality

- Open-source for leg-shunt current sensing

- Protection shutdown pin

- Low R<sub>DS(on)</sub> Trench FREDFET

- Under-voltage lockout for all channels

- Matched propagation delay for all channels

- Optimized dV/dt for loss and EMI trade offs

- 3.3V Schmitt-triggered active high input logic

- Cross-conduction prevention logic

- Motor power range up to ~110W, without heat sink

- Isolation 1500VRMS min

|                  |                 | Standard Pack |          | Orderable Part Number |

|------------------|-----------------|---------------|----------|-----------------------|

| Base Part Number | Package Type    | Form          | Quantity | Orderable Part Number |

| 36L              |                 | Tape and Reel | 2000     | IRSM836-035MATR       |

| IRSM836-035MA    | PQFN 12 x 12 mm | Tray          | 800      | IRSM836-035MA         |

All part numbers are PbF

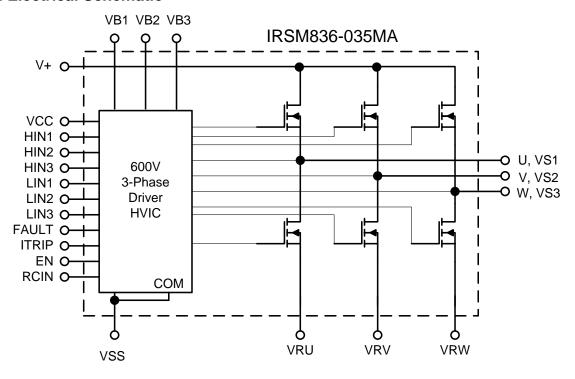

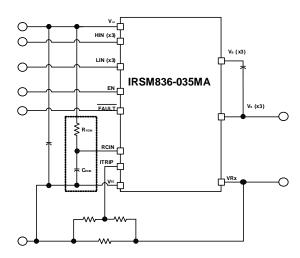

#### **Internal Electrical Schematic**

# **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the module may occur. These are not tested at manufacturing. All voltage parameters are absolute voltages referenced to VSS unless otherwise stated in the table.

| Symbol                                | Description                                     | Min                      | Max                      | Unit             |

|---------------------------------------|-------------------------------------------------|--------------------------|--------------------------|------------------|

| BV <sub>DSS</sub>                     | MOSFET Blocking Voltage                         |                          | 500                      | V                |

| I <sub>O</sub> @ T=25°C               | DC Output Current per MOSFET                    |                          | 3                        | A                |

| I <sub>OP</sub>                       | Pulsed Output Current (Note 1)                  |                          | 20                       | ] ^              |

| P <sub>d</sub> @ T <sub>C</sub> =25°C | Maximum Power Dissipation per MOSFET            |                          | 36                       | W                |

| V <sub>ISO</sub>                      | Isolation Voltage (1min) (Note 2)               |                          | 1500                     | V <sub>RMS</sub> |

| $T_J$                                 | Operating Junction Temperature                  | -40                      | 150                      | °C               |

| T <sub>L</sub>                        | Lead Temperature (Soldering, 30 seconds)        |                          | 260                      | °C               |

| Ts                                    | Storage Temperature                             | -40                      | 150                      | °C               |

| V <sub>S1,2,3</sub>                   | High Side Floating Supply Offset Voltage        | V <sub>B1,2,3</sub> - 20 | V <sub>B1,2,3</sub> +0.3 | V                |

| V <sub>B1,2,3</sub>                   | High Side Floating Supply Voltage               | -0.3                     | 500                      | V                |

| Vcc                                   | Low Side and Logic Supply voltage               | -0.3                     | 20                       | V                |

| V <sub>IN</sub>                       | Input Voltage of LIN, HIN, ITRIP, EN, RCIN, FLT | V <sub>SS</sub> -0.3     | V <sub>CC</sub> +0.3     | V                |

Note 1: Pulse Width = 100µs, TC =25°C, Duty=1%.

Note 2: Characterized, not tested at manufacturing

#### **Recommended Operating Conditions**

| Symbol              | Description                               | Min                | Max                | Unit |

|---------------------|-------------------------------------------|--------------------|--------------------|------|

| V+                  | Positive DC Bus Input Voltage             |                    | 400                | V    |

| V <sub>S1,2,3</sub> | High Side Floating Supply Offset Voltage  | (Note 3)           | 400                | V    |

| V <sub>B1,2,3</sub> | High Side Floating Supply Voltage         | V <sub>S</sub> +12 | V <sub>S</sub> +20 | V    |

| V <sub>CC</sub>     | Low Side and Logic Supply Voltage         | 13.5               | 16.5               | V    |

| V <sub>IN</sub>     | Input Voltage of LIN, HIN, ITRIP, EN, FLT | 0                  | 5                  | V    |

| Fp                  | PWM Carrier Frequency                     |                    | 20                 | kHz  |

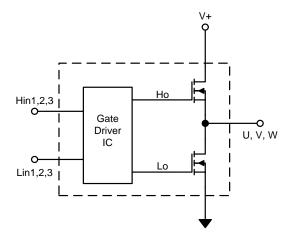

The Input/Output logic diagram is shown in Figure 1. For proper operation the module should be used within the recommended conditions. All voltages are absolute referenced to COM. The V<sub>S</sub> offset is tested with all supplies biased at 15V differential.

Note 3: Logic operational for V<sub>s</sub> from COM-5V to COM+250V. Logic state held for V<sub>s</sub> from COM-5V to COM-V<sub>BS</sub>.

#### **Static Electrical Characteristics**

$(V_{CC}\text{-COM}) = (V_B\text{-}V_S) = 15 \text{ V}$ .  $T_A = 25^{\circ}\text{C}$  unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to all six channels. The  $V_{CCUV}$  parameters are referenced to  $V_{SS}$ . The  $V_{BSUV}$  parameters are referenced to  $V_{S}$ .

| Symbol                                     | Description                                                                           | Min  | Тур  | Max  | Units | Conditions                                          |

|--------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------|

| BV <sub>DSS</sub>                          | Drain-to-Source Breakdown Voltage                                                     | 500  |      |      | V     | T <sub>J</sub> =25°C, I <sub>LK</sub> =250μA        |

| I <sub>LKH</sub>                           | Leakage Current of High Side FET's in Parallel                                        |      | 10   |      | μΑ    | T <sub>J</sub> =25°C, V <sub>DS</sub> =500V         |

| I <sub>LKL</sub>                           | Leakage Current of Low Side FET's in Parallel Plus Gate Drive IC                      |      | 15   |      | μΑ    | T <sub>J</sub> =25°C, V <sub>DS</sub> =500V         |

| R <sub>DS(ON)</sub>                        | Drain to Source ON Resistance                                                         |      | 1.85 | 2.2  | Ω     | T <sub>J</sub> =25°C, V <sub>CC</sub> =15V, Id = 1A |

| V <sub>IN,th+</sub>                        | Positive Going Input Threshold                                                        | 2.5  |      |      | V     |                                                     |

| V <sub>IN,th</sub> -                       | Negative Going Input Threshold                                                        |      |      | 0.8  | V     |                                                     |

| V <sub>CCUV+</sub> ,<br>V <sub>BSUV+</sub> | V <sub>CC</sub> and V <sub>BS</sub> Supply Under-Voltage,<br>Positive Going Threshold | 8    | 8.9  | 9.8  | V     |                                                     |

| V <sub>CCUV-</sub> ,<br>V <sub>BSUV-</sub> | V <sub>CC</sub> and V <sub>BS</sub> supply Under-Voltage,<br>Negative Going Threshold | 7.4  | 8.2  | 9    | V     |                                                     |

| V <sub>CCUVH,</sub><br>V <sub>BSUVH</sub>  | V <sub>CC</sub> and V <sub>BS</sub> Supply Under-Voltage<br>Lock-Out Hysteresis       |      | 0.7  |      | V     |                                                     |

| I <sub>QBS</sub>                           | Quiescent V <sub>BS</sub> Supply Current V <sub>IN</sub> =0V                          |      |      | 125  | μA    |                                                     |

| I <sub>QCC</sub>                           | Quiescent V <sub>CC</sub> Supply Current V <sub>IN</sub> =0V                          |      |      | 3.35 | mA    |                                                     |

| I <sub>QCC, ON</sub>                       | Quiescent V <sub>CC</sub> Supply Current V <sub>IN</sub> =4V                          |      |      | 10   | mA    |                                                     |

| I <sub>IN+</sub>                           | Input Bias Current V <sub>IN</sub> =4V                                                |      | 100  | 160  | μA    |                                                     |

| I <sub>IN-</sub>                           | Input Bias Current V <sub>IN</sub> =0V                                                |      |      | 1    | μA    |                                                     |

| I <sub>TRIP+</sub>                         | I <sub>TRIP</sub> Bias Current V <sub>ITRIP</sub> =4V                                 |      | 5    | 40   | μA    |                                                     |

| I <sub>TRIP</sub> -                        | I <sub>TRIP</sub> Bias Current V <sub>ITRIP</sub> =0V                                 |      |      | 1    | μA    |                                                     |

| V <sub>IT, TH+</sub>                       | I <sub>TRIP</sub> Threshold Voltage                                                   | 0.37 | 0.46 | 0.55 | V     |                                                     |

| V <sub>IT, TH</sub> -                      | I <sub>TRIP</sub> Threshold Voltage                                                   |      | 0.4  |      | V     |                                                     |

| V <sub>IT, HYS</sub>  | I <sub>TRIP</sub> Input Hysteresis           | <br>0.06 |     | V |                      |

|-----------------------|----------------------------------------------|----------|-----|---|----------------------|

| R <sub>BR</sub>       | Internal Bootstrap Equivalent Resistor Value | <br>200  |     | Ω | T <sub>J</sub> =25°C |

| V <sub>RCIN,TH</sub>  | RCIN Positive Going Threshold                | <br>8    |     | V |                      |

| R <sub>ON,FAULT</sub> | FAULT Open-Drain Resistance                  | <br>50   | 100 | Ω |                      |

Note 4: Characterized, not tested at manufacturing

# **Dynamic Electrical Characteristics**

$(V_{CC}\text{-COM}) = (V_B\text{-}V_S) = 15 \text{ V}. T_A = 25^{\circ}\text{C}$  unless otherwise specified.

| Symbol                 | Description                                            | Min | Тур | Max  | Units | Conditions                                                        |  |

|------------------------|--------------------------------------------------------|-----|-----|------|-------|-------------------------------------------------------------------|--|

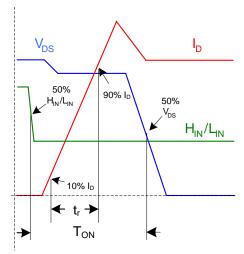

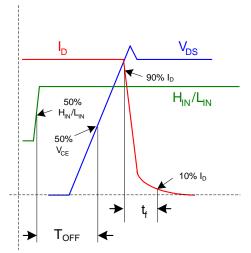

| T <sub>ON</sub>        | Input to Output Propagation Turn-On Delay Time         |     | 0.7 | 1.5  | μs    | I <sub>D</sub> =1mA, V <sup>+</sup> =50V                          |  |

| T <sub>OFF</sub>       | Input to Output Propagation Turn-Off Delay Time        |     | 0.7 | 1.5  | μs    | See Fig.2                                                         |  |

| T <sub>FIL,IN</sub>    | Input Filter Time (HIN, LIN)                           | 200 | 330 |      | ns    | V <sub>IN</sub> =0 & V <sub>IN</sub> =4V                          |  |

| T <sub>FIL,EN</sub>    | Input Filter Time (EN)                                 | 100 | 200 |      | ns    | V <sub>IN</sub> =0 & V <sub>IN</sub> =4V                          |  |

| T <sub>BLT-ITRIP</sub> | I <sub>TRIP</sub> Blanking Time                        | 100 | 330 |      | ns    | V <sub>IN</sub> =0 & V <sub>IN</sub> =4V, V <sub>I/Trip</sub> =5V |  |

| T <sub>FAULT</sub>     | Itrip to Fault                                         |     | 600 | 1000 | ns    | V <sub>IN</sub> =0 & V <sub>IN</sub> =4V                          |  |

| T <sub>EN</sub>        | EN Falling to Switch Turn-Off                          |     | 700 | 1000 | ns    | V <sub>IN</sub> =0 & V <sub>IN</sub> =4V                          |  |

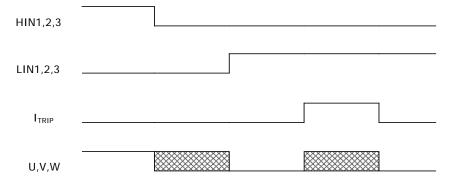

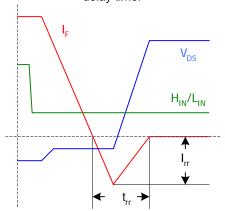

| T <sub>ITRIP</sub>     | I <sub>TRIP</sub> to Switch Turn-Off Propagation Delay |     | 950 | 1300 | ns    | I <sub>D</sub> =1A, V <sup>+</sup> =50V, See Figure 3             |  |

### **MOSFET Avalanche Characteristics**

| Symbol | Description                   | Min | Тур | Max | Units | Conditions                                                                      |

|--------|-------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------|

| EAS    | Single Pulse Avalanche Energy |     | 150 |     | mJ    | T <sub>J</sub> =25°C, L=93mH, VDD=150V, I <sub>TEST</sub> =1.8A, TO-220 package |

#### **Thermal and Mechanical Characteristics**

| Symbol                | Description                                                            | Min | Тур  | Max | Units | Conditions |

|-----------------------|------------------------------------------------------------------------|-----|------|-----|-------|------------|

| R <sub>th(J-CT)</sub> | Total Thermal Resistance Junction to Case Top                          |     | 27.4 |     | °C/W  | One device |

| R <sub>th(J-CB)</sub> | R <sub>th(J-CB)</sub> Total Thermal Resistance Junction to Case Bottom |     | 2.2  |     | °C/W  | One device |

### **Qualification Information**†

| Qualification Level        |               | Industrial <sup>††</sup> (per JEDEC JESD 47E)  |  |

|----------------------------|---------------|------------------------------------------------|--|

| Moisture Sensitivity Level |               | MSL3 <sup>†††</sup> (per IPC/JEDEC J-STD-020C) |  |

| ECD                        | Machine Model | Class B (per JEDEC standard JESD22-A115)       |  |

| Human Body Model           |               | Class 2 (per standard ESDA/JEDEC JS-001-2012)  |  |

| RoHS Compliant             |               | Yes                                            |  |

- Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- Higher MSL ratings may be available for the specific package types listed here. Please contact your ††† International Rectifier sales representative for further information.

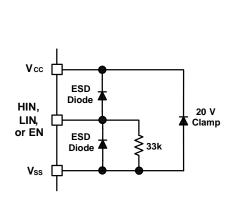

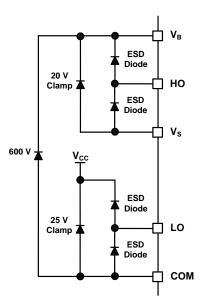

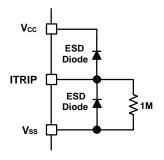

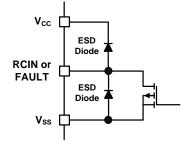

# **Input/Output Pin Equivalent Circuit Diagrams**

# **Input-Output Logic Level Table**

| EN | Itrip | Hin1,2,3 | Lin1,2,3 | U,V,W |

|----|-------|----------|----------|-------|

| 1  | 0     | 1        | 0        | V+    |

| 1  | 0     | 0        | 1        | 0     |

| 1  | 0     | 0        | 0        | off   |

| 1  | 1     | Χ        | Х        | off   |

| 0  | Х     | Х        | Х        | off   |

Figure 1: Input/Output Logic Diagram

Figure 2a: Input to Output propagation turn-on delay time.

Figure 2b: Input to Output propagation turn-off delay time.

Figure 2c: Diode Reverse Recovery.

Figure 2: Switching Parameter Definitions

Figure 3: I<sub>TRIP</sub> Timing Waveform

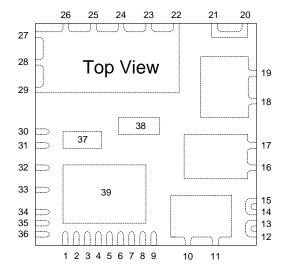

# **Module Pin-Out Description**

| Pin               | Name     | Description                                             |

|-------------------|----------|---------------------------------------------------------|

| 1                 | HIN3     | Logic Input for High Side Gate Driver - Phase 3         |

| 2                 | LIN1     | Logic Input for Low Side Gate Driver - Phase 1          |

| 3                 | LIN2     | Logic Input for Low Side Gate Driver - Phase 2          |

| 4                 | LIN3     | Logic Input for Low Side Gate Driver - Phase 3          |

| 5                 | /FLT     | Fault Output Pin                                        |

| 6                 | Itrip    | Over-Current Protection Pin                             |

| 7                 | EN       | Enable Pin                                              |

| 8                 | RCin     | Reset Programming Pin                                   |

| 9, 39             | VSS, COM | Ground for Gate Drive IC and Low Side Gate Drive Return |

| 10, 11, 30,<br>37 | U, VS1   | Output 1, High Side Floating Supply Offset Voltage      |

| 12, 13            | VR1      | Phase 1 Low Side FET Source                             |

| 14, 15            | VR2      | Phase 2 Low Side FET Source                             |

| 16, 17, 38        | V, VS2   | Output 2, High Side Floating Supply Offset Voltage      |

| 18, 19            | W, VS3   | Output 3, High Side Floating Supply Offset Voltage      |

| 20, 21            | VR3      | Phase 3 Low Side FET Source                             |

| 22-29             | V+       | DC Bus Voltage Positive                                 |

| 31                | VB1      | High Side Floating Supply Voltage 1                     |

| 32                | VB2      | High Side Floating Supply Voltage 2                     |

| 33                | VB3      | High Side Floating Supply Voltage 3                     |

| 34                | VCC      | 15V Supply                                              |

| 35                | HIN1     | Logic Input for High Side Gate Driver - Phase 1         |

| 36                | HIN2     | Logic Input for High Side Gate Driver - Phase 2b        |

#### Note

Pins 37 and 38 are not required to be connected electrically on the PCB

All pins with the same name are internally connected. For example, pins 10, 11, 30 and 37 are internally connected.

www.irf.com

### Fault Reporting and Programmable Fault Clear Timer

The IRSM836-035MA provides an integrated fault reporting output and an adjustable fault clear timer. There are two situations that would cause the IRSM836-035MA to report a fault via the FAULT pin. The first is an under-voltage condition of V<sub>CC</sub> and the second is when the ITRIP pin recognizes a fault. Once the fault condition occurs, the FAULT pin is internally pulled to V<sub>SS</sub> and the fault clear timer is activated. The fault output stays in the low state until the fault condition has been removed and the fault clear timer expires; once the fault clear timer expires, the voltage on the FAULT pin will return to V<sub>CC</sub>.

The length of the fault clear time period (t<sub>FLTCLR</sub>) is determined by exponential charging characteristics of the capacitor where the time constant is set by R<sub>RCIN</sub> and C<sub>RCIN</sub>. In Figure 4 where we see that a fault condition has occurred (UVLO or ITRIP), RCIN and FAULT are pulled to V<sub>SS</sub>, and once the fault has been removed, the fault clear timer begins. Figure 5 shows that R<sub>RCIN</sub> is connected between the V<sub>CC</sub> and the RCIN pin, while C<sub>RCIN</sub> is placed between the RCIN and V<sub>SS</sub> pins.

Figure 4: RCIN and FAULT pin waveforms

Figure 5: Programming the fault clear timer

The design guidelines for this network are shown in Table 1.

| 6                 | ≤1 nF                          |  |

|-------------------|--------------------------------|--|

| CRCIN             | Ceramic                        |  |

| В                 | 0.5 M $\Omega$ to 2 M $\Omega$ |  |

| R <sub>RCIN</sub> | >> R <sub>ON,RCIN</sub>        |  |

Table 1: Design guidelines

The length of the fault clear time period can be determined by using the formula below.

$$t_{\mathit{FLTCLR}} = - \Big( R_{\mathit{RCIN}} C_{\mathit{RCIN}} \Big) ln \Bigg( 1 - \frac{V_{\mathit{RCIN},\mathit{TH}}}{V_{\mathit{CC}}} \Bigg)$$

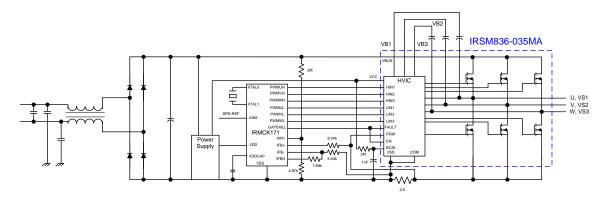

# Typical Application Connection IRSM836-035MA

- Electrolytic bus capacitors should be mounted as close to the module bus terminals as possible to reduce ringing and EMI problems. Additional high frequency ceramic capacitor mounted close to the module pins will further improve performance.

- 2. In order to provide good decoupling between VCC-VSS and VB1,2,3-VS1,2,3 terminals, the capacitors shown connected between these terminals should be located very close to the module pins. Additional high frequency capacitors, typically 0.1μF, are recommended.

- 3. Value of the boot-strap capacitors depends upon the switching frequency. Their selection should be made based on application note AN-1044.

- 4. PWM generator must be disabled within Fault duration to guarantee shutdown of the system. Overcurrent condition must be cleared before resuming operation.

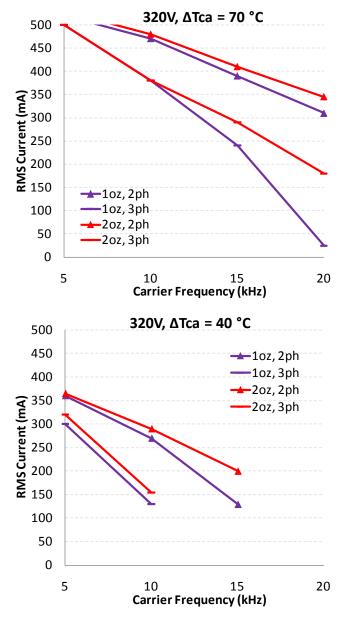

# **Current Capability in a Typical Application**

Figure 6 shows the current capability for this module at specified conditions. The current capability of the module is affected by application conditions including the PCB layout, ambient temperature, maximum PCB temperature, modulation scheme, PCB copper thickness and so on. The curves below were obtained from measurements carried out on the IRMCS1171 reference design board which includes the IRSM836-035MA and IR's IRMCK171 digital control IC.

Figure 6: Maximum Sinusoidal Phase Current vs. PWM Switching Frequency Sinusoidal Modulation, V<sup>+</sup>=320V, PF=0.95

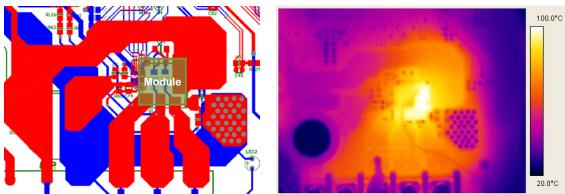

### **PCB Example**

Figure 7 below shows an example layout for the application PCB. The effective area of the V+ top-layer copper plane is ~3cm² in this example. For an FR4 PCB with 1oz copper, R<sub>th(J-A)</sub> is about 40°C/W. A lower R<sub>th(J-A)</sub> can be achieved using thicker copper and/or additional layers.

Figure 7: PCB layout example and corresponding thermal image

At the module's typical operating conditions, dV/dt of the phase node voltage is influenced by the load capacitance which includes parasitic capacitance of the PCB, MOSFET output capacitance and motor winding capacitance. To turn off the MOSFET, the load capacitance needs to be charged by the phase current. For the IRMCS1171 reference design, turn-off dV/dt ranges from 2 to 5 V/ns depending on the phase current magnitude. Turn-on dV/dt is influenced by PCB parasitic capacitance and motor winding capacitance and typically ranges from 4 to 6 V/ns. The MOSFET turn-on loss combined with the complimentary body diode reverse recovery loss comprises the majority of the total switching losses. Two-phase modulation can be used to reduce switching losses and run the module at higher phase currents.

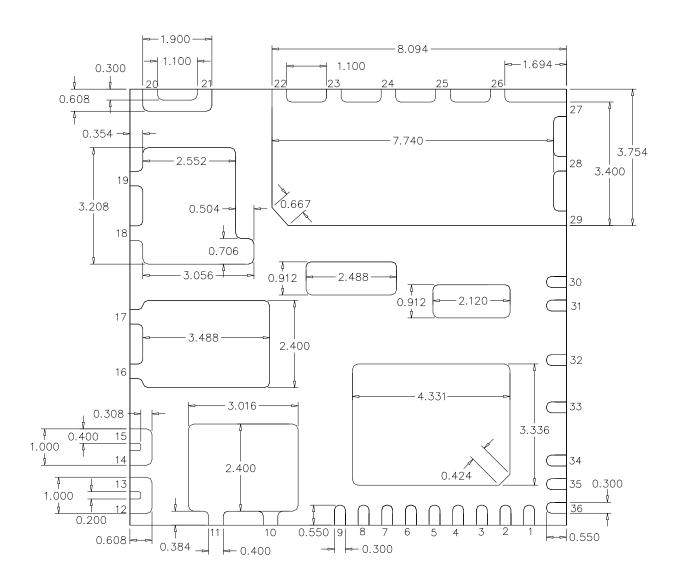

# 36L Package Outline IRSM836-035MA (Bottom View)

Dimensions in mm

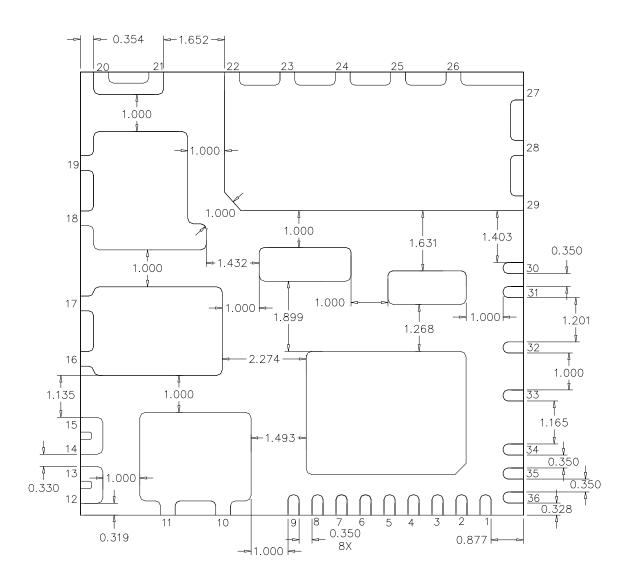

# 36L Package Outline IRSM836-035MA (Bottom View)

Dimensions in mm

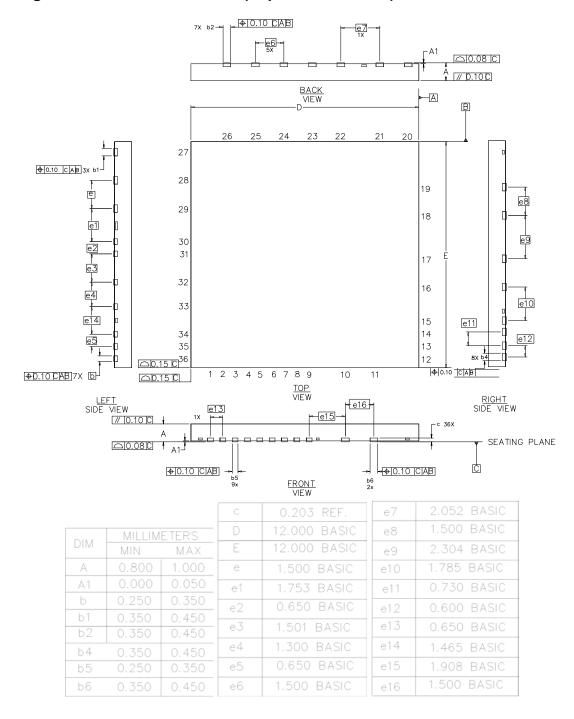

### 36L Package Outline IRSM836-035MA (Top and Side View)

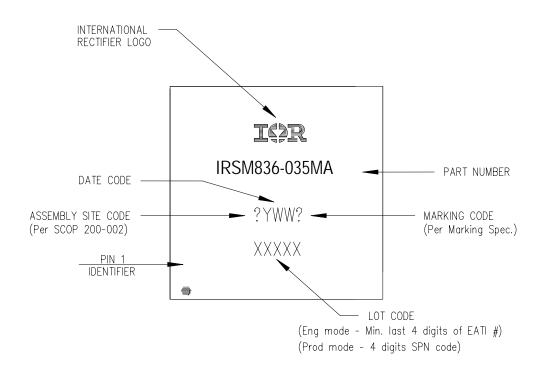

# **Top Marking**

# **Revision History**

Formatting corrections; added notes about what pins are internally connected; updated ordering January 30, 2013 table stating all parts are PbF.

Data and Specifications are subject to change without notice IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information