#### 82C201, 82C201-10/82C202/82A203/82A204/82A205 CS8220: PC/AT COMPATIBLE CHIPSet\*\*

- Fully IBM™ PC AT Compatible

- Flexible architecture allows usage in any iAPX 286 design

- Early ALE Generation

- Early RAS Generation

- Low Power CMOS Process Technology for 82C201 and 82C202, and Advance Low Power Schottky Process Technology for 82A203, 82A204 and 82A205

The CS8220 PC/AT compatible CHIPSet is a 5 chip LSI implementation of most of the MSI/SSI logic used to control the IBM Personal Computer AT. The flexible architecture of the chip set allows it to be used in any iAPX 286 based system design. The 82C201 and 82C202 perform the functions of the Intel 82284 Clock Generator and Ready Interface, 82288 Bus Controller for iAPX286 processors, 8284A Clock Generator and Driver, and replace 30 other MSI/SSI devices in the IBM PC AT design. Significant new features have been added to enhance system performance while still maintaining PC AT compatibility.

The 82C201 is the standard 8 MHz device. The 82C201-10 will operate with a system clock frequency of 10 MHz.

Two signals, ALE and RAS, can be altered with the activation of the Early Mode select line

- 10 or 8 MHz with One Wait State or

6 MHz with Zero Wait State Capability

- Complete System Board Memory Decode

- Configurable RAM Selects

- 16 Bit to 8 Bit Conversion Logic

- Variable Wait State Selection

- 24 mA sink and -3.3 mA source current for System Bus outputs

- Single 5 Volt Supply

(EMODE). When EMODE is low, both signals become valid before the normal ALE and RAS signals. This allows the use of 120nsec DRAMS in a 6Mhz zero wait state system or 150nsec DRAMS in a 8Mhz one wait state system. The 10 MHz one wait state system using 82C201-10 will require 120 nsec DRAMs. Variable wait state selection is also provided to accommodate slower memories and peripherals where necessary.

The 82A203, 82A204, and 82A205 include most of the buffers and drivers required in an IBM PC AT compatible design. Advanced Schottky Bipolar process technology is used to implement these devices, allowing high speed and high source (-3.3mA) and sink (24mA) current capability.

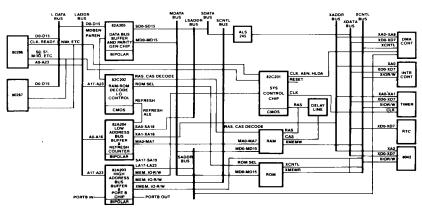

Figure 1. PC/AT Block Diagram

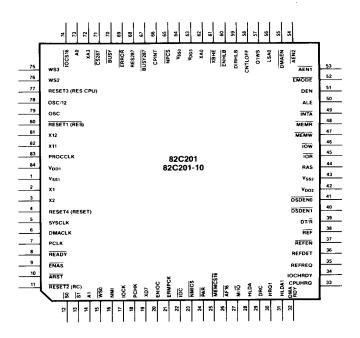

### 82C201 Pin Description

| Pin No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                                    |

|---------|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,3     | ı           | X1,X2   | CRYSTAL Inputs for parallel resonant fundamental mode frequency crystal. The crystal frequency must be twice the processor clock frequency. Alternatively, a TTL clock may be connected to X1.                                                     |

| 15      | I           | WS0     | ZERO WAIT STATE option. When active the memory accesses will have no wait state cycles inserted. For proper operation set-up and hold times to the clock must be met.                                                                              |

| 12, 13  | ı           | Sō, S1  | STATUS inputs from the CPU. The status signals are used by the bus controller to determine the state of the CPU. Pull-up resistors should be provided on these inputs.                                                                             |

| 8       | O           | READY   | READY is an active low output indicating that the current bus cycle be completed. Ready is an open collector output requiring an external pull up resistor. \$0, \$1, \$\text{WS0}\$ and \$\text{RESET1}\$ inputs control \$\text{READY}\$ output. |

| 80      | I           | RESET1  | RESET1 (RES) is connected to the Power Good signal. When low it will provide a reset signal for the system.                                                                                                                                        |

| 11      | I           | RESET2  | RESET2 (RC) is an active LOW input generated by the Universal Peripheral Interface device 8042. It forces a CPU reset by activating RESET3 signal.                                                                                                 |

| 77      | 0           | RESET3  | RESET3 (RES CPU) is the reset signal to reset the CPU. RESET3 is generated when RESET1 or RESET2 inputs become active. RESET3 is also activated when a HALT status is generated by the CPU by forcing M/IO, S0, S1 and A1 LOW.                     |

| 4       | 0           | RESET4  | RESET4 (RESET) is generated as a result of RESET1 becoming active and provides the reset for the system. RESET4 is synchronized with the Processor clock.                                                                                          |

| 83      | 0           | PROCCLK | PROCESSOR CLOCK signal provides the clock for the CPU. It is equal to the crystal frequency on pins X1 and X2.                                                                                                                                     |

| 5       | 0           | SYSCLK  | SYSTEM CLOCK is equal to half the PROCCLK and may be used for clocking peripheral devices. It is synchronized to the processor T-states.                                                                                                           |

| 6       | 0           | DMACLK  | DMA CLOCK is an output running at half the SYSCLK frequency. This clock is synchronized to the CPU T-cycles. It is clock source for the DMA Controller.                                                                                            |

| 7       | 0           | PCLK    | PCLK (Peripheral Clock) is half the rate of the PROCCLK. It is used for clocking the peripheral controllers.                                                                                                                                       |

# **82C201 Pin Description** (Continued)

| Pin No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                                                                          |

|---------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | 0           | ENAS    | ENABLE ADDRESS STROBE is an active LOW output which enables the Address Strobe input of the Real Time Clock device MC146818. It goes low at the first read status input ( $\overline{S1}$ = 0) from the CPU.                                                                             |

| 14      | I           | A1      | ADDRESS 1 is the demultiplexed address signal from<br>the CPU. It is used to detect the 'SHUT DOWN'<br>condition of the CPU.                                                                                                                                                             |

| 73      | ı           | A0      | ADDRESS 0 is the address signal from the CPU. It is used to generate the enable signal for the data bus transceivers.                                                                                                                                                                    |

| 82,81   | I           | X11,X12 | CRYSTAL inputs for the internal oscillator which generates the clock for the I/O devices and other peripherals in the system. A parallel resonant fundamental frequency mode crystal should be connected across the X11, X12 inputs. Alternatively, a TTL clock may be connected to X11. |

| 79      | 0           | osc     | OSCILLATOR output is the clock frequency of the crystal connected across X11, X12.                                                                                                                                                                                                       |

| 78      | 0           | OSC/12  | OSCILLATOR divide by 12 is an output with a clock frequency equal to 1/12 of the crystal frequency across the X11, X12 inputs.                                                                                                                                                           |

| 27      | I           | M/ĪŌ    | MEMORY-INPUT OUTPUT is the M/IO signal from the CPU. When HIGH it indicates memory access, when LOW it indicates an I/O access. It is used to generate the Memory andI/O control signals for the system.                                                                                 |

| 49      | 0           | INTA    | INTERRUPT ACKNOWLEDGE is an active LOW output. It is used by the Interrupt Controllers to output the interrupt vector onto the data bus. It is tristated when HLDA is active high and CNTLOFF output is low.                                                                             |

| 45      | 1/0         | IOR     | I/O READ signal for the I/O devices. When LOW it indicates an I/O READ command is in progress. It is tri-stated when HLDA is high and CNTLOFF output is low.                                                                                                                             |

| 46      | I/O         | ĪŌW     | I/O WRITE signal for the I/O devices. When LOW it indicates an I/O WRITE command is progress. It is tri stated when HLDA is high and CNTLOFF output is low.                                                                                                                              |

| 48      | I/O         | MEMR    | MEMORY READ COMMAND instructs a memory device to place data on the data bus. MEMR is also active low during refresh cycles. It is tri-stated when HLDA is high and CNTLOFF output is low.                                                                                                |

# **82C201 Pin Description** (Continued)

| Pin No. | Pin<br>Type | Symbol | Pin Description                                                                                                                                                                                                                                                                                        |

|---------|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47      | 1/0         | MEMW   | MEMORY WRITE COMMAND instructs a memory device to read the data on the data bus. It is tri-stated when HLDA is high and CNTLOFF output is low.                                                                                                                                                         |

| 50      | 0           | ALE    | ADDRESS LATCH ENABLE is an active HIGH signal and controls the address latches used to hold the address during a bus cycle. ALE is not issued for halt bus cycle.                                                                                                                                      |

| 44      | 0           | RAS    | RAS is an active HIGH output. It is used to generate the RAS and CAS signals for memory accesses.                                                                                                                                                                                                      |

| 39      | 0           | DT/Ř   | DATA TRANSMIT/RECEIVE determines the data direction to and from the local data bus. A HIGH indicates a write bus cycle and a LOW indicates a READ bus cycle. DEN output is always inactive when DT/R changes state. DT/R is HIGH when no bus cycle is active.                                          |

| 51      | 0           | DEN    | DATA ENABLE is an active HIGH output. When active it enables the data transceivers connected to the local bus.                                                                                                                                                                                         |

| 41      | 0           | DSDEN0 | DATA STROBE DATA ENABLE 0 is an active LOW output. When active it enables the data transceivers connected to the low byte (D0-D7) data bus. This signal is active when DEN is high. Also an active Numerical Processor Chip Select will disable this output.                                           |

| 40      | 0           | DSDEN1 | DATA STROBE DATA ENABLE 1 is an active LOW output. When active it enables the data transceivers connected to the high byte (D8-D15) data bus. This signal is active when DEN is high. Also an active Numerical Processor Chip Select will disable this output.                                         |

| 61      | I/O         | XBHE   | BUS HIGH ENABLE is an active LOW signal which enables the high byte data bus signals to pass through the data bus transceivers.                                                                                                                                                                        |

| 62      | I/O         | XA0    | ADDRESS 0 when active decodes the cascaded Interrupt Controller's command words issued by the CPU. The XA0 works in conjunction with the read, write and chip select inputs of the interrupt controller and determines whether the CPU wishes to issue a command or read the status of the controller. |

| 72      | ı           | хаз    | ADDRESS 3 is used for generating the chip select and reset signals for the 80287.                                                                                                                                                                                                                      |

| 71      | 1           | CS287  | CHIP SELECT 287 is an active LOW input used to generate the Numerical Processor Select NPCS for the 80287.                                                                                                                                                                                             |

### 82C201 Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                  |

|---------|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 65      | 0           | NPCS    | NUMERICAL PROCESSOR CHIP SELECT is active LOW output and is used as the Numerical Processor Select NPS1 for the 80287.                                                                                                           |

| 70      | I           | BUSY    | BUSY is an active LOW input from the 80287 to indicate that it is currently executing a command. It is used to generate the Busy signal for the processor.                                                                       |

| 67      | 0           | BUSY287 | BUSY 287 is an active LOW output for the processor. It indicates to the processor the operating condition of the Coprocessor.                                                                                                    |

| 69      | 1           | ERROR   | ERROR is an active LOW input from the Numeric<br>Processor indicating that an unmasked error<br>condition exists.                                                                                                                |

| 66      | 0           | CPINT   | COPROCESSOR INTERRUPT is an active HIGH output. It is the Interrupt Request from the Numeric Coprocessor and is connected to the Interrupt Request 13 of the Interrupt Controller.                                               |

| 68      | 0           | RES287  | RES287 is an active HIGH output and is used to reset the Numeric Processor.                                                                                                                                                      |

| 26      | ı           | AF16    | AF16 is an active LOW input signal which should be asserted when 16 bit memory acceses are made. It is used to inhibit the command delays for memory accesses by the I/O devices.                                                |

| 25      | ı           | MEMCS16 | MEMORY CHIP SELECT is an active low signal. It is active for a 16-bit, 1 wait-state memory cycle. It must be obtained by decoding LA17-LA23 address lines.                                                                       |

| 30      | l           | HRQ1    | HOLD REQUEST 1 is an active HIGH signal from the DMA controller. It is used to generate the CPU Hold Request signal.                                                                                                             |

| 33      | 0           | CPUHRQ  | CPU HOLD REQUEST is an active HIGH output for the CPU for DMA transfers by the DMA controller. It is also active during refresh cycles.                                                                                          |

| 28      | ı           | HLDA    | HOLD ACKNOWLEDGE is an active HIGH input generated by the CPU, granting a DMA cycle to the DMA controller. HLDA active forces all commands, IOR, IOW, MEMR, MEMW, and INTA, to be tri-stated provided the CNTLOFF output is low. |

| 31      | 0           | HLDA1   | HOLD ACKNOWLEDGE 1 is an active HIGH ouput providing the Hold Acknowledge signal for the DMA controller.                                                                                                                         |

| 74      | ı           | TOCS16  | I/O CHIP SELECT is an active low signal. It is active for a 16-bit, 1 wait-state I/O cycle.                                                                                                                                      |

## 82C201 Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                                                                   |

|---------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53      | I           | AEN1    | ADDRESS ENABLE 1 is an active LOW signal from one of the two DMA controllers to enable the address latches holding the address. It is active for 8-bit data transfers.                                                                                                            |

| 54      | I           | AEN2    | ADDRESS ENABLE 2 is an active LOW signal from one of the two DMA controllers to enable the address latches holding the address. It is active for 16 bit data transfers.                                                                                                           |

| 52      | 1           | EMODE   | EARLY MODE is an input which selects between the Early generation of ALE and RAS signals or normal generation of the ALE and RAS signals. A LOW input will select the EARLY mode and a HIGH input will select the Normal mode.                                                    |

| 76      | ı           | WS2     | TWO WAIT STATES option. When active the I/O acceses will have two wait states inserted. WS2 may be generated by I/O address decoders.                                                                                                                                             |

| 75      | ı           | WS3     | THREE WAIT STATES option. When active the I/O acceses will have three wait states inserted. WS3 may be generated by I/O address decoders.                                                                                                                                         |

| 59      | 0           | DIRHLB  | DIRECTION FOR HIGH TO LOW BYTE and low to high byte conversion during data transfers to and from the 8 bit peripherals. This signal is also referred to as DIR245.                                                                                                                |

| 58      | 0           | CNTLOFF | CONTROL OFF is an active HIGH output which is used to enable the low byte data bus latch during byte accesses. When CNTLOFF is low, HLDA active tristates all command outputs.                                                                                                    |

| 60      | 0           | ENHLB   | ENABLE HIGH TO LOW byte performs the high to low byte conversion with the DIR HLB signal. Conversion does not take place if A0 = 0 which indicates word transfers. This signal is also referred to as as Gate 245.                                                                |

| 55      | 0           | DMAEN   | DMA ADDRESS ENABLE is an active LOW signal and is active when any I/O device is making a DMA access to the system memory.                                                                                                                                                         |

| 34      | I           | IOCHRDY | I/O CHANNEL READY signal is generated by an I/O device. When LOW it indicates a 'not ready' condition and forces the insertion of wait states in I/O or Memory accesses by the I/O device. When HIGH it will allow the completion of a memory or an I/O access by the I/O device. |

82C201

8

# **82C201 Pin Description** (Continued)

| Pin No. | Pin<br>Type | Symbol | Pin Description                                                                                                                                                                                                            |

|---------|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32      | 0           | DMARDY | DMA READY signal for the DMA Controller used to extend memory read and write cycles from the DMA controller for slower memories or I/O devices. When low it inserts wait states.                                           |

| 35      | ı           | REFREQ | REFRESH REQUEST INPUT is an input indicating that a refresh cycle be initiated for the dynamic RAMs. This signal is obtained from the Timer controller, 8254, and provides a refresh request every 15 microseconds.        |

| 36      | 0           | REFDET | REFRESH DETECT is an output which changes state when a refresh cycle is being initiated. It may be used externally to monitor the state of the refresh cycle execution.                                                    |

| 38      | I/O         | REF    | REFRESH is an open drain active LOW signal. It is used to initiate a refresh cycle for the dynamic RAMs. As an input it can used to force a REFRESH cycle from an I/O device. An external pull up is required on this pin. |

| 37      | 0           | REFEN  | REFRESH ENABLE is an active LOW output which is used to start a refresh counter which provides addresses for the dynamic RAM refresh cycle.                                                                                |

| 56      | 0           | LSA0   | ADDRESS 0 for system bus which is forced LOW for word accesses.                                                                                                                                                            |

| 57      | 0           | Q1WS   | ONE WAIT STATE is an active high output which goes active during phase 2 (O2) of the CPU bus cycle following the Ts state. It can be used externally to extend the READ or WRITE cycles for slower I/O devices.            |

| 29      | ſ           | DRC    | DMA READY CLOCK is an active HIGH input and is used to generate the DMA READY signal for the DMA controllers.                                                                                                              |

| 10      | ŀ           | ARST   | ASYNCHRONOUS RESET is an active, LOW input. Under normal configurations, it should be tied to a 10K pull-up resistor. It resets the chip to a known state, and is used for testing purposes only.                          |

| 23      | ı           | NMICS  | NON-MASKABLE INTERRUPT CHIP SELECT input is active LOW. When active it enables the NMI to the CPU.                                                                                                                         |

| 19      | ı           | XD7    | DATA BUS BIT 7 of the peripheral data bus, is used to generate the Non-Maskable Interrupt for the CPU.                                                                                                                     |

| 16      | 0           | NMI    | NON-MASKABLE INTERRUPT is an active HIGH output and is connected to the NMI of the CPU.                                                                                                                                    |

# **82C201 Pin Description** (Continued)

| Pin No.  | Pin<br>Type | Symbol          | Pin Description                                                                                                                                                                                                                                                  |

|----------|-------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22       | I           | ĪŌĊ             | I/O CHECK is an active LOW input. It is used to signal an Error condition from an I/O device. When active it generates the IOCK output if Enable I/O Check input was active.                                                                                     |

| 17       | 0           | IOCK            | I/O CHECK output is activated when an I/O Check (IOC) input is activated. Enable I/O Check must be active for IOCK to be generated. The IOCK is used to generate the Non-Maskable Interrupt for the CPU, and is also stored in PORT B as one of the status bits. |

| 20       | I           | ENIOC           | ENABLE I/O CHECK is the enable input for the I/O Check logic. It enables the generation of the IOCK output when IOC is active.                                                                                                                                   |

| 24       | ı           | PAR             | PARITY error is Active LOW input and generates the<br>Parity Check PCHK output.                                                                                                                                                                                  |

| 21       | ı           | ERMPCK          | ENABLE RAM PARITY CHECK is an active HIGH input used to enable the parity check logic.                                                                                                                                                                           |

| 18       | 0           | РСНК            | PARITY CHECK is an active HIGH output active when<br>a parity check is detected. It is used to generate the<br>Non-Maskable Interrupt for the CPU.                                                                                                               |

| 42,63,84 |             | V <sub>DD</sub> | Power Supply.                                                                                                                                                                                                                                                    |

| 1,43,64  |             | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                          |

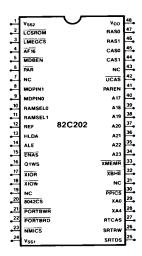

### 82C2O2 Pin Description

| Pin No. | Pin<br>Type | Symbol             | Pin Description                                                                                                                                                                                                                                                                                                                                         |

|---------|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40-34   | l           | A17-A23            | ADDRESS BUS inputs from the processor address bus.                                                                                                                                                                                                                                                                                                      |

| 12      | I           | REF                | REFRESH is an active HIGH input and initiates a refresh cycle for the dynamic RAMs.                                                                                                                                                                                                                                                                     |

| 10,11   | I           | RAMSEL0<br>RAMSEL1 | RAM SELECT 0 and 1 select the 256K, 512K or 1024K RAM option. The select logic works as follows: RAMSEL0 RAMSEL1 RAM MEMORY 0 0 256K 0 1 640K 1 0 512K 1 1 1024K                                                                                                                                                                                        |

| 13      | 1           | HLDA               | HOLD ACKNOWLEDGE is an active HIGH input from the processor. When active it indicates that the processor has relinquished the system bus in favour of another bus master in the system. It is used to latch the internally generated RAS/CAS signals into appropriate outputs.                                                                          |

| 14      | ı           | ALE                | ADDRESS LATCH ENABLE is an active HIGH input and latches the low order address signals from a multiplexed bus into the address registers. It is used to latch the internally generated RAS/CAS signals into appropriate outputs.                                                                                                                        |

| 33      | I           | XMEMR              | MEMORY READ is an active LOW input from a peripheral device instructing the memory to place its data on the data bus. It is used to generate the direction signal for the data bus buffers holding the data bus signals.                                                                                                                                |

| 42      | I           | UCAS               | USER CAS is an active LOW input and is used to enable parity generation logic when addressing memory which is selected by logic external to the 82C202. It is usually connected to the CAS generated externally for memory beyond what is addressable by the 82C202. When active it enables parity generation/check for the externally selected memory. |

| 41      | 0           | PAREN              | PARITY ENABLE is an active HIGH output. It is active during the parity check cycle.                                                                                                                                                                                                                                                                     |

| 29      | l           | XA0                | ADDRESS 0 is the address 0 signal on the address bus. It is used to detect the parity error on low or high memory data byte.                                                                                                                                                                                                                            |

| 32      | I           | XBHE               | BUS HIGH ENABLE signal is used in the same way as XAO to generate the parity error for the low or high memory data byte.                                                                                                                                                                                                                                |

| 47, 46  | 0 .         | RASO,<br>RAS1      | ROW ADDRESS SELECT 0 and 1 are used for selecting RAM banks. The RAS0 selects the lower memory bank, and RAS1 selects the high memory bank.                                                                                                                                                                                                             |

# **82C202 Pin Description** (Continued)

| Pin No. | Pin<br>Type | Symbol              | Pin Description                                                                                                                                                                                                                                                |

|---------|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45, 44  | 0           | CAS0,<br>CAS1       | COLUMN ADDRESS SELECT 0 and 1 are used to select the low and high byte access signals for the RAM access cycles.                                                                                                                                               |

| 4       | 0           | AF16                | AF16 is an active LOW output indicating a word memory access. It is used to generate Command Delay control signal for delaying READ or WRITE commands for slower peripherals or I/O devices.                                                                   |

| 3       | 0           | <u>LMEĞCS</u>       | LOW MEG CHIP SELECT is an active LOW output which is active when low memory address space, 0-1.024 Megabyte, is accessed. It can be used to disable certain read or write signals on the I/O connector if accesses are made beyond one megabyte address space. |

| 2       | 0           | LCSROM              | ROM CHIP SELECT is an active LOW output which is active when the ROM/PROM/EPROM space is accessed. It can be used to generate the chip select inputs for the non-volatile devices in the system.                                                               |

| 5       | 0           | MDBEN               | MEMORY DATA BUS ENABLE is an active LOW output. It is used to set the direction on the data bus buffers which drive the data bus between the system and the memory devices.                                                                                    |

| 30      | 1           | PPICS               | PROGRAMMABLE PERIPHERAL INTERFACE CHIP SELECT is an active LOW input. It is active when the Peripheral Interface Device 8042 is selected. It is used to generate the Chip Select signal for the 8042.                                                          |

| 20      | 0           | 8042CS              | 8042 CHIP SELECT is an active LOW signal for the 8042 device. It is selected when PPICS is active.                                                                                                                                                             |

| 28      | l           | XA4                 | ADDRESS 4 is the address 4 of the CPU address bus. It is used to generate the chip selects and data strobes for other peripherals in the system.                                                                                                               |

| 17,18   | I           | XIOR,<br>XIOW       | I/O READ AND WRITE are active LOW inputs and are active whenever a read or write cycle is performed with an I/O device. They are used to generate the read and write signals for the peripherals or other I/O ports on the system.                             |

| 22,21   | 0           | PORTBRD,<br>PORTBWR | READ and WRITE signals for the I/O port are active LOW outputs. They are generated when an Port B is either 'read' or 'written' to.                                                                                                                            |

| 15      | I           | ENAS                | ENABLE ADDRESS STROBE is an active LOW input and is used to generate the address strobe signal for the real time clock device MC146818.                                                                                                                        |

| 27,25   | 0           | RTCAS,<br>SRTDS     | REAL TIME CLOCK ADDRESS STROBE and DATA STROBE outputs for the real time clock MC146818.                                                                                                                                                                       |

### 82C202 Pin Description

(Continued)

| Pin No.    | Pin<br>Type | Symbol            | Pin Description                                                                                                                                                 |

|------------|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26         | 0           | SRTRW             | REAL TIME CLOCK READ/WRITE output for the real time clock device MC146818. A HIGH state indicates a 'read' operation and a LOW state means a 'write' operation. |

| 16         | l           | Q1WS              | Q1 WAIT STATE is an active HIGH input and is used to extend the Real Time Clock Address strobe by one wait state.                                               |

| 23         | 0           | NMICS             | NMI CHIP SELECT is an active LOW output. It may be used to enable the Non-Maskable Interrupt to the processor.                                                  |

| 9,8        | ı           | MDPINO,<br>MDPIN1 | MEMORY DATA PARITY INPUT 0,1 for parity on LOW and HIGH bytes of memory.                                                                                        |

| 6          | 0           | PAR               | PARITY is an active LOW output. This latched output is active when an even parity error is detected on either the LOW or HIGH byte memory access.               |

| 48         | _           | V <sub>DD</sub>   | Power Supply.                                                                                                                                                   |

| 1,24       | _           | V <sub>SS</sub>   | Ground.                                                                                                                                                         |

| 7,19,31,43 |             | N.C.              | Not Connected.                                                                                                                                                  |

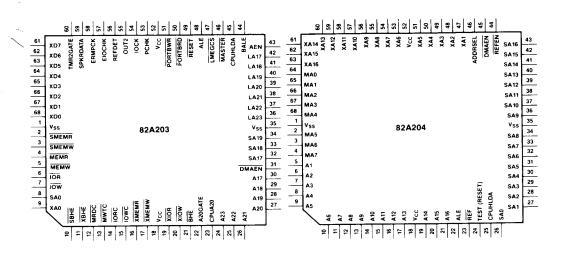

# 82A203 Pin Description

| Pin No. | Pin<br>Type | Symbol          | Pin Description                                                                                                                                                                                                       |

|---------|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | _           | V <sub>SS</sub> | Ground.                                                                                                                                                                                                               |

| 2       | 0           | SMEMR           | Memory Read command for the expansion bus. It is active when low 1 Megabyte memory space is addressed.                                                                                                                |

| 3       | 0           | SMEMW           | Memory Write command for the expansion bus. It is active when low 1 Megabyte memory space is addressed.                                                                                                               |

| 4       | 1/0         | MEMR            | Memory Read command for the extended expansion bus. It is active on all memory read cycles.                                                                                                                           |

| 5       | I/O         | MEMW            | Memory Write command for the extended expansion bus. It is active on all memory write cycles.                                                                                                                         |

| 6       | 1/0         | ĪOR             | Input/Output Read command for the expansion bus. The read cycle can be initiated by the CPU or DMA controller, or by a DMA controller resident on the I/O channel.                                                    |

| 7       | I/O         | ĪOW             | Input/Output Write command for the expansion bus. The write cycle can be initiated by the CPU or DMA controller, or by a DMA controller resident on the I/O channel.                                                  |

| 8       | I/O         | SA0             | Address 0 of the CPU bus. The I/O pin outputs the A0 from the CPU during local CPU cycles. The expansion bus can force the A0 on this pin during the period when another master on the expansion bus has the control. |

| 9       | 1/0         | XA0             | Address 0 from the local I/O bus. In DMA cycle the XA0 is forced by the DMA controller. During CPU read cycle the XA0 is forced by the CPU.                                                                           |

| 10      | I/O         | SBHE            | Bus High Enable signal from or to the Expansion Bus is active when the high byte transfer is taking place.                                                                                                            |

| 11      | 1/0         | XBHE            | Bus High Enable to or from the peripheral bus is active when high byte transfer is taking place.                                                                                                                      |

| 12      | I/O         | MRDC            | Memory Read is the read signal generated by the CPU through the 82C201 to indicate a memory read cycle by the CPU.                                                                                                    |

| 13      | I/O         | MWTC            | Memory Write is the write signal generated by the CPU through the 82C201 to indicate a memory write cycle by the CPU.                                                                                                 |

| 14      | I/O         | IORC            | Input Output Read signal generated by the CPU through the 82C201 to indicate an I/O Read cycle.                                                                                                                       |

| 15      | I/O         | IOWC            | Input Output Write signal generated by the CPU through the 82C201 to indicate an I/O Write cycle.                                                                                                                     |

# **82A203 Pin Description** (Continued)

| Pin No. | Pin<br>Type | Symbol          | Pin Description                                                                                                                                                                                                                                                                                  |

|---------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | I/O         | XMEMR           | Memory Read signal from and to the peripheral bus. The Read is forced (as an output) by the CPU during read of the peripheral devices. The DMA controller forces this pin as input to read data from a memory location or memory to memory transfer.                                             |

| 17      | I/O         | XMEMW           | Memory Write signal from and to the peripheral bus. The Write is forced (as an output) by the CPU during write to the peripheral devices. The DMA controller forces this pin as input to write data to a memory location or memory to memory transfer.                                           |

| 18      |             | V <sub>CC</sub> | 5V Power Supply.                                                                                                                                                                                                                                                                                 |

| 19      | 1/0         | XIOR            | I/O Read signal for the peripheral bus. As an output it<br>is used to Read the internal registers of the peripheral<br>controllers. As an input it is forced by the DMA<br>controllers to access data from a peripheral device.                                                                  |

| 20      | 1/0         | XIOW            | I/O Write signal for the peripheral bus. As an output it is used to write to the internal registers of the peripheral controllers. As an input it is forced by the DMA controller to write data to a peripheral device.                                                                          |

| 21      | 1           | ВНЕ             | Bus high Enable signal is connected to BHE output of the CPU. It indicates the transfer of data on the upper half of the data bus. In conjunction with the A0 polarity it determines whether the access is on a word or byte boundary. The coding of BHE and A0 follows the 80286 coding scheme. |

| 22      | ı           | A20GATE         | A20 Gate is used to force A20 LOW. When A20GATE is LOW A20 on the CPU address bus is forced LOW. When A20GATE is high, A20 is transmitted as generated by the CPU.                                                                                                                               |

| 23      | I           | CPUA20          | CPU A20 is the CPU address 20. It is transmitted as A20 after being conditioned by the A20GATE signal.                                                                                                                                                                                           |

| 24-30   | I/O         | A23-A17         | A23-A17 are the Address bits 17 through 23 of the CPU address bus. As input these pins are forced by the CPU address bus. As outputs the expansion bus address lines A17-A23 are output on these pins.                                                                                           |

| 31      | I           | DMAEN           | DMA Address Enable is used to condition the transceivers for the peripheral control signals. When LOW it allows the DMA control signals (MEMR, MEMW, I/OR, I/OW, XA0) to be output on the system control bus.                                                                                    |

| 32-34   | 0           | SA17-19         | System address bus addresses 17-19 are output to the expansion bus during a memory or an I/O cycle.                                                                                                                                                                                              |

| 35      | _           | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                                                          |

### 82A203 Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36-42   | 1/0         | LA23-17 | System address bus A17–23 is controlled by the MASTER signal. When MASTER is LOW the expansion I/O bus forces the A17–A23 addresses on the local system bus. When MASTER is HIGH the system board forces the addresses on the expansion bus. LA17–LA23 gives the system up to 16 Mbytes of addressability. LA17–LA19 are valid when bus ALE signal, BALE, is high. LA17–LA19 are not latched during CPU cycles and do not stay valid for the entire cycle. They are used to generate memory decodes for 1 wait-state memory cycles. The I/O add-on adapter boards must latch these signals on the falling edge of BALE signal. |

| 43      | 0           | AEN     | Address Enable is an output signal for the expansion bus. When LOW it indicates that another MASTER on the expansion bus has made a request by activating MASTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 44      | 0           | BALE    | Buffered Address Latch Enable is a buffered ALE signal for the devices on the expansion bus. SA0-SA19 are latched on the falling edge of BALE. During DMA cycles, BALE is forced high.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 45      | ı           | CPUHLDA | CPU Hold Acknowledge signal is used to control the direction of the address and control signal transceivers. A HIGH on the CPU HLDA is interpreted as a DMA cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 46      | ı           | MASTER  | Master is generated by the devices on the expansion bus. A LOW indicates that another device on the expansion bus is active. After MASTER is forced low by an I/O device, the I/O CPU must wait for one system clock period before forcing the address and data lines. The MASTER signal must not be held low for more than 15 microseconds, or else data in the system memory may be lost due to lack of a refresh cycle.                                                                                                                                                                                                     |

| 47      | I           | LMEGCS  | Low Megabyte Chip Select is generated by 82C202. When active, it indicates that low megabyte memory address space is being accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 48      | 1           | ALE     | Address Latch Enable is obtained from the 82C201. It is used to generate the buffered ALE signal for the expansion bus, and to latch the address bus signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 49      | ı           | RESET   | Reset is used to reset the Port B latch. Reset is active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 50      | ı           | PORTBRD | Port B Read is active when the CPU reads PORT B latch, which stores the status conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **82A203 Pin Description** (Continued)

| Pin No.        | Pin<br>Type | Symbol             | Pin Description                                                                                                                                                            |  |

|----------------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 51             | 1           | PORTBWR            | Port B Write is active when the CPU outputs the data to the PORT B latch.                                                                                                  |  |

| 52             |             | v <sub>cc</sub>    | 5 Volt Power Supply.                                                                                                                                                       |  |

| 53             | 1           | РСНК               | Parity Check is generated by the 82C201 and can be read on a PORT B Read command.                                                                                          |  |

| 54             | 1           | IOCK               | I/O Channel Check is generated by the 82C201. It can be read by a read to the PORT B.                                                                                      |  |

| 55             | 1           | OUT2               | OUT2 is the output from the Timer 8254. It can be read by a read to the PORT B.                                                                                            |  |

| 56             | I           | REFDET             | Refresh Detect is generated by the 82C201. It can be read by a read to the PORT B.                                                                                         |  |

| 57             | 0           | EIOCHK             | Enable I/O Check is an <u>output</u> which is used to enable the I/O Check (IOC) from the I/O expansion bus to be latched into the 82C201.                                 |  |

| 58             | 0           | ERMPCK             | Enable RAM Parity Check is generated for the 82C201. It allows the 82C201 to latch the parity error and output it as PCHK signal for the 82A203.                           |  |

| 59             | 0           | SPKRDATA           | Speaker data is an output which is used to allow the 8254 tone signal to be output to the speaker.                                                                         |  |

| 60             | 0           | TMR2GATE           | Timer 2 Gate signal enables the timer on 8254 Timer to generate the tone signal for the speaker.                                                                           |  |

| 68-65<br>64-61 | I/O<br>O    | XD0-XD3<br>XD4-XD7 | Data Bus 0-7 for the peripheral bus. XD0-XD3 are used as inputs to PORT B Latch and outputs from PORT B status buffer. XD4-XD7 are outputs only from PORT B status buffer. |  |

### 82A204 Pin Description

| Pin No.        | Pin<br>Type | Symbol             | Description                                                                                                                                                                                      |  |

|----------------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1              |             | V <sub>SS</sub>    | Ground.                                                                                                                                                                                          |  |

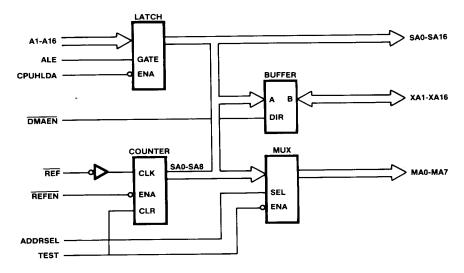

| 64-68<br>2-4   | 0           | MA0-MA4<br>MA5-MA7 | Address signals 0-7 for addressing the memory.                                                                                                                                                   |  |

| 5-17<br>19-21  | !<br>!      | A1-A13<br>A14-A16  | Address signals 1-16 from the CPU for addressing the memory.                                                                                                                                     |  |

| 18             | _           | V <sub>CC</sub>    | 5 Voit Power Supply.                                                                                                                                                                             |  |

| 22             | I           | ALE                | Address Latch Enable from the 82C201.                                                                                                                                                            |  |

| 23             | ı           | REF                | Refresh is generated by the 82C201 to initiate a refresh cycle for the DRAMs.                                                                                                                    |  |

| 24             | I           | TEST<br>(RESET)    | Test, when HIGH, resets the refresh counter and tri-states the memory addresses MA0-7. This will allow another device to access the memory. In normal operation the TEST pin must be pulled LOW. |  |

| 25             | I           | CPUHLDA            | CPU Hold Acknowledge is generated by the CPU in response to a Hold Request from a DMA controller. The 82A204 uses it to tri-state the SA bus, allowing the XA bus to drive the address bus.      |  |

| 26             | 0           | SA0                | Address 0 for the refresh memory.                                                                                                                                                                |  |

| 27-34<br>36-43 | I/O<br>I/O  | SA1-8<br>SA9-16    | System addresses 1-16 for the expansion bus.                                                                                                                                                     |  |

| 35             |             | V <sub>SS</sub>    | Ground.                                                                                                                                                                                          |  |

| 44             | I           | REFEN              | Refresh Enable is generated by the 82C201 and allows a refresh cycle to be initiated.                                                                                                            |  |

| 45             | 1           | DMAEN              | DMA Enable is generated by the 82C201 when a DMA cycle is underway. It is used by the 82A204 to condition the address transceiver in the proper direction.                                       |  |

| 46             | ı           | ADDRSEL            | Address Select is used to multiplex the memory address between the system addresses and the addresses generated by the refresh counter.                                                          |  |

| 47-51<br>53-63 | I/O<br>I/O  | XA1-5<br>XA6-16    | Peripheral addresses 1-16 for the local I/O bus.                                                                                                                                                 |  |

| 52             |             | V <sub>CC</sub>    | 5 Volt Power Supply.                                                                                                                                                                             |  |

|                |             |                    |                                                                                                                                                                                                  |  |

**82A2O4** 18

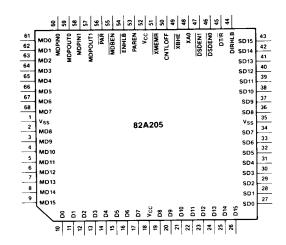

#### 82A205 Pin Description

| Pin No.        | Pin<br>Type | Symbol            | Description                                                                                                                                                                         |  |  |  |

|----------------|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1              | _           | V <sub>SS</sub>   | Ground.                                                                                                                                                                             |  |  |  |

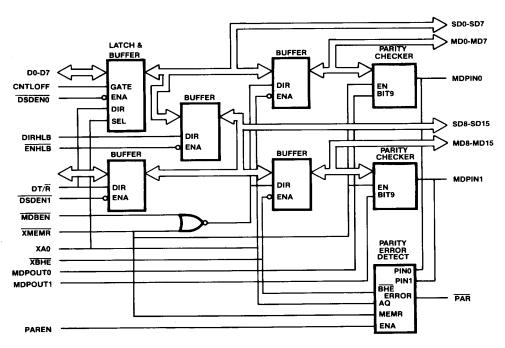

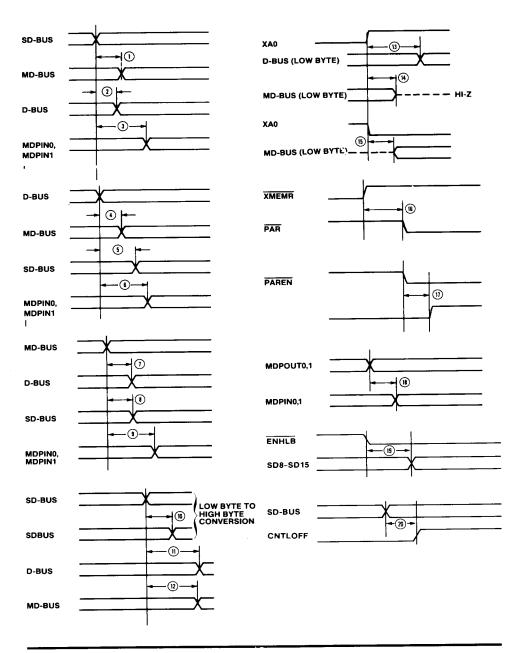

| 61-68<br>2-9   | I/O<br>I/O  | MD0-7<br>MD8-15   | Memory data bus for the on board memory.                                                                                                                                            |  |  |  |

| 10-17<br>19-26 | I/O<br>I/O  | D0-D7<br>D8-D15   | CPU data bus signals from/to the CPU.                                                                                                                                               |  |  |  |

| 18             |             | V <sub>CC</sub>   | 5 Volt Power Supply.                                                                                                                                                                |  |  |  |

| 27-34<br>36-43 | I/O<br>I/O  | SD0-SD7<br>SD8-15 | System Data bus for the expansion bus. Its direction is determined by DT/R signal from the 82C201.                                                                                  |  |  |  |

| 35             |             | V <sub>SS</sub>   | Ground.                                                                                                                                                                             |  |  |  |

| 44             | ı           | DIRHLB            | DIRHLB is generated by the 82C201 and controls the direction of low to high byte conversion during data transfers to and from 8 bit peripherals.                                    |  |  |  |

| 45             | I           | DT/R              | Data Transmit/Receive is generated by the 82C201. determines direction of data to and from the memory. A HIGH on the pin indicates a write cycle and a LOW indicates a read cycle.  |  |  |  |

| 46, 47         | l           | DSDEN0<br>DSDEN1  | Data Strobe Enable 0 and 1 are generated by the 82C201. These signals enable the data transceivers connected to the LOW and HIGH data bytes.                                        |  |  |  |

| 48             | I           | XA0               | XA0 is address signal 0 for the peripheral bus. It is generated by the 82A203. It is used to condition the bus transceiver for the memory data bus.                                 |  |  |  |

| 49             | I           | ХВНЕ              | XBHE is the Bus High Enable signal generated by the 82A203. It is used to condition the bus transceiver for the memory data bus, and is active during a high byte transfer.         |  |  |  |

| 50             | I           | CNTLOFF           | Control Off is generated by the 82C201 and is used to enable low byte data bus latch during byte access.                                                                            |  |  |  |

| 51             | 1           | XMEMR             | Memory Read is generated by the 82A203 and is used to enable the parity generation logic on the device, and to set the direction on the output transceiver for the memory data bus. |  |  |  |

| 52             |             | V <sub>cc</sub>   | 5 V Power Supply.                                                                                                                                                                   |  |  |  |

| 53             | 1           | PAREN             | Parity Enable allows the parity check to be done on parity on the parity bit read from the memory.                                                                                  |  |  |  |

| 54             | I           | ENHLB             | ENHLB enables the high to low byte conversion in conjunction with DIRHLB signal. It is generated by the 82C201.                                                                     |  |  |  |

# 82A205 Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol              | Description                                                                                                                                      |

|---------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 55      | i           | MDBEN               | Memory Data Bus Enable is generated by the 82C202. It enables the data bus transceivers connected to the memory devices.                         |

| 56      | 0           | PAR                 | Parity signal, when active, signifies a parity error on a memory read cycle.                                                                     |

| 59,57   | I           | MDPOUT0,<br>MDPOUT1 | Memory Data Parity Out 0 and 1 are the parity bits read from the memory banks 0 and 1. They are used to compute the parity during a ready cycle. |

| 60, 58  | 0           | MDPINO,<br>MDPIN1   | Memory Data Parity In 0 and 1 are the parity bits written to the memory banks 0 and 1 during a memory write cycle.                               |

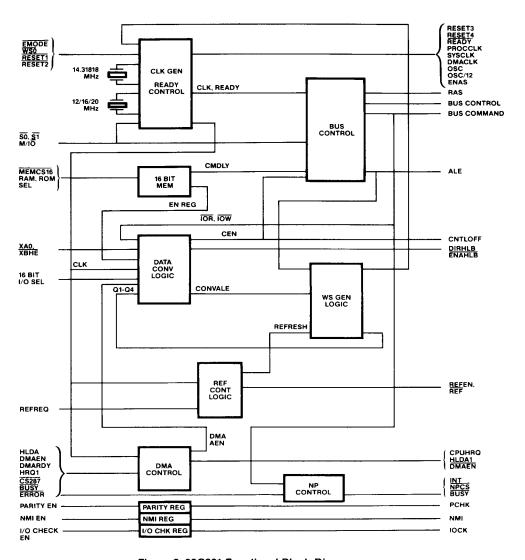

#### **Functional Description 82C201**

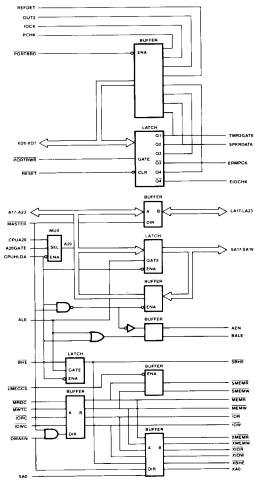

The 82C201 block diagram is illustrated in Figure 2. The device consists of the following functional blocks:

Clock Generation and Reset/Ready Synchronization Command and Control Signal Generation Conversion Logic Wait State Control DMA and Refresh Logic Numerical Processor Control NMI and Error Logic

#### Clock Generation and Reset/Ready Synchronization

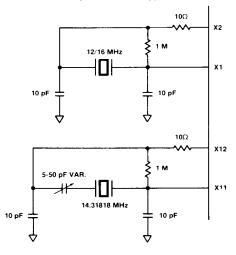

The Clock Generation circuitry contains the two oscillators used to generate the system clock signals. Both oscillators are designed to use an external, parallel resonant fundamental mode crystal to generate the basic operating frequency. Crystal connections for the CPU Clock oscillator are made to pins X1 and X2. The X11 and X12 pins are used for generating the Video Clock. The CPU Clock oscillator crystal frequency should be twice the CPU operating frequency (e.g. 12Mhz crystal for a 6 Mhz CPU). For the IBM PC AT, a 14.31818 Mhz crystal should be used with the Video Clock oscillator to maintain compatibility. The 14.31818 Mhz crystal may require a trimmer capacitor in series with the crystal. The trimmer capacitor can then be adjusted to eliminate unwanted color shifts in video signals. Recommended circuits and crystal specifications for both oscillators are shown in Figure 3.

Two clock signals are derived from the Video Clock oscillator, the 14.31818 Mhz clock (14MHz) to the expansion connectors for the system bus and the OSC/12 clock for the counter timer. The OSC/12 clock is generated internally by dividing the 14.31818 Mhz signal from the oscillator by twelve. Due to the possibility of heavy loading, the 14 Mhz clock should be externally buffered before being routed to the expansion connectors.

The remaining 82C201 clocks are derived from the CPU Clock oscillator. These clocks are used throughout the system board and determine the speed at which the computer operates.

PROCCLK is a clock output which is intended to drive both the CPU and the Numerical Processor. The PROCCLK output has a frequency equal to that of the CPU Clock oscillator crystal. The PROCCLK output buffer has sufficient drive capability to meet the 3.8 volt minimum V<sub>IH</sub> requirement of the 80286/80287 clock inputs, and may be used to drive them directly.

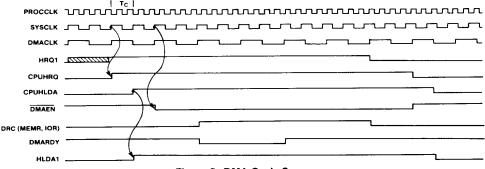

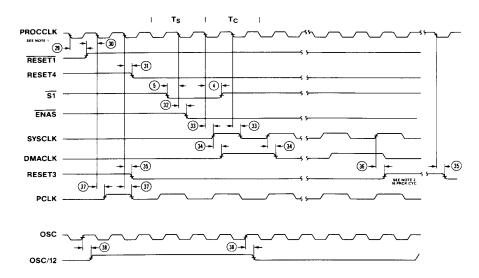

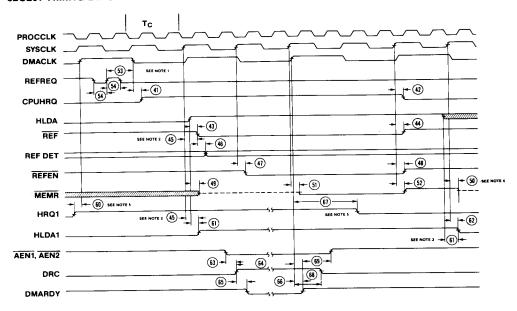

SYSCLK and DMACLK are system clock signals whose output frequencies are  $\frac{1}{2}$  and  $\frac{1}{4}$  the PROCCLK oscillator, respectively. Immediately after Reset, the SYSCLK and DMACLK signals are held in a LOW state and will not begin operating until after the CPU asserts Status (S1=0) at the beginning of the first bus cycle. SYSCLK will then make its first low to high transition on the falling edge of PROCCLK in Phase 1 of the next CPU bus cycle following T<sub>S</sub>. SYSCLK and DMACLK are now synchronized to the CPU's internal clock, and SYSCLK will provide a low to high transition at the beginning of each Phase 1 while DMACLK makes this same transition on alternate Phase 1 cycles. An illustration of the DMACLK/SYSCLK start-up from Reset is shown in 82C201 reset timing diagrams.

The remaining clock signal, PCLK, also has a frequency equal to 1/2 of the frequency of PROCCLK. The difference between this signal and SYSCLK is that PCLK has no phase relationship to the CPU's internal clock. PCLK becomes active immediately after ARST is deasserted. ARST is a seperate reset line which clears both the PCLK and OSC/12 dividers and should, for normal operation, be tied to the same signal as the RESET1 input. Alternately, ARST can be used to synchronize PCLK to any desired event using additional external circuitry. Since PCLK is not used internally in the 82C201 for timing purposes, this will have no effect on the proper operation of the CPU. It does, however, effect the operation of OSC/12, which is normally used as the Counter/Timer clock.

Two reset output signals are provided on the 82C201 for resetting the system. RESET4 is a synchronized reset signal for general system reset. RESET3, which is similar to RESET4, is the CPU reset signal and, additionally provides

Figure 2. 82C201 Functional Block Diagram

a reset when a Shutdown condition in the CPU is detected. Both signals, RESET4 and RESET3, are active high signals derived from the RESET1 input. Both RESET4 and RESET3 meet the setup and hold time requirements of the 80286. After a Shutdown condition is detected, RESET3 is asserted for 16 PROCCLK times and then deasserted. A RESET3 resulting from shutdown detection is also synchronous with PROCCLK, ensuring proper CPU operation.

A ready signal (READY) is provided on the 82C201 to allow the CPU to run with slower memories and peripherals. This signal is an open drain output requiring an external pull-up resistor to  $V_{CC}$ . The value of this resistor should not be less than 900 ohms nor greater than 1K ohms to ensure adequate rise and fall times. READY is synchronized in this section of the 82C201 to the PROCCLK output. Most of the control for READY, however, is provided for in other sections of the device. A detailed description of READY control can be found in the section entitled "Wait State and Conversion Logic." READY can also be asserted by applying a LOW to the WS0 input. In this case, WS0 must be externally synchronized for proper operation.

In order to prevent inadvertent writes to the Clock/Calendar device from occuring during power-up and power-down situations, ENAS (address strobe enable) is generated in the 82C201. ENAS is deasserted whenever RESET1 is active, and is only asserted after the CPU has started its first status cycle.

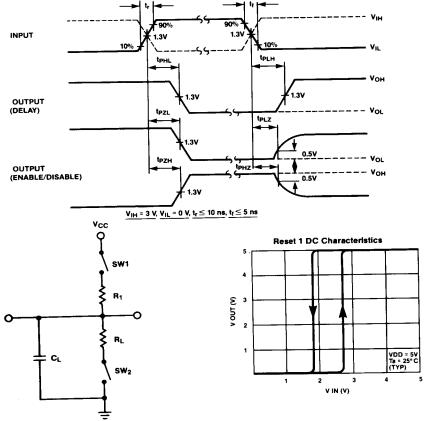

The RESET1 input is buffered internally in the 82C201 with a Schmitt trigger, and is intended to be used as the Power Normal input for the system. This signal should be LOW when power is applied to the system and remain LOW for at least 5 msec after all voltages have reached their proper operating range and the PROCCLK has reached the specified AC and DC parameters. The RESET1 input has a typical input hysteresis of 1 volt and may be directly connected to an RC network to generate the necessary power-on reset. (See Figure 9 for typical DC characteristics.)

Reset of the CPU can also be accomplished by asserting the RESET2 input. This input is controlled by the keyboard processor and can be used to reset the CPU by means of specific key combinations. When RESET2 is activated, the CPU reset signal (RESET3) is then asserted and will not be deasserted for 16 PROCCLK cycles after RESET2 is deasserted.

#### **Command and Control Signal Generation**

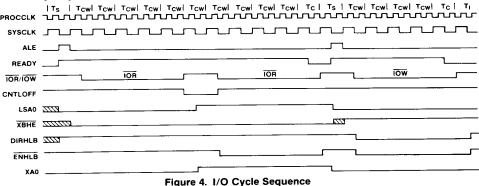

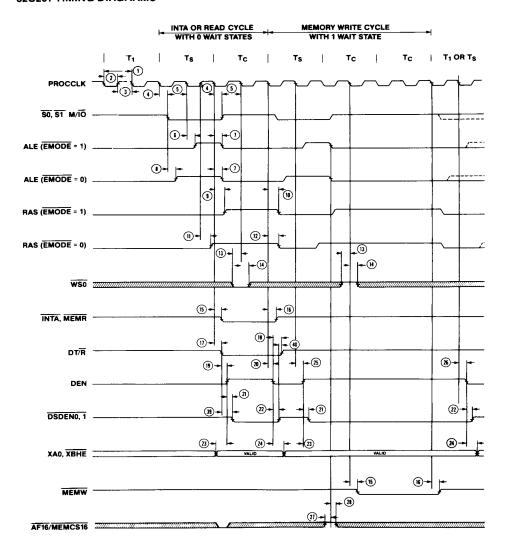

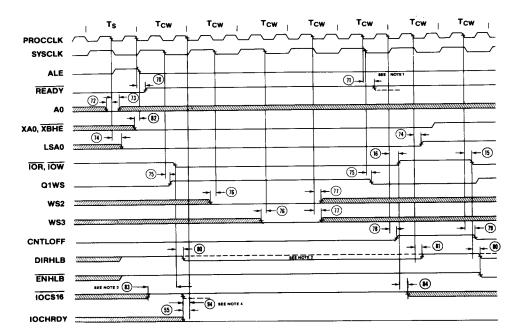

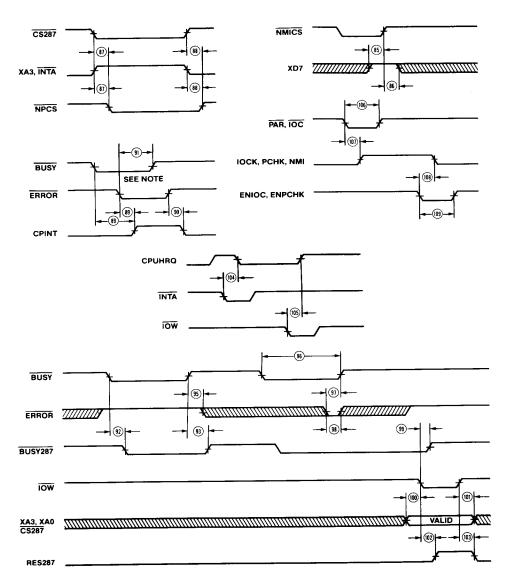

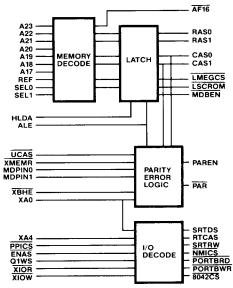

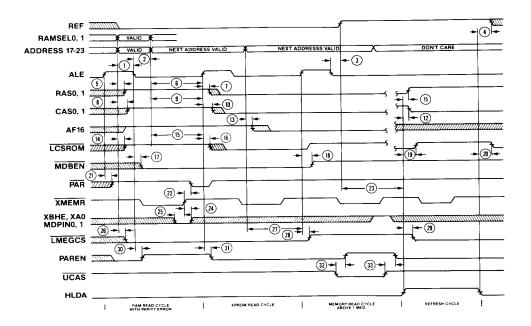

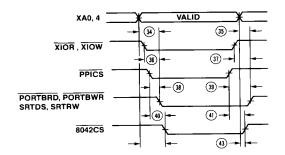

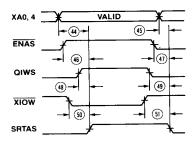

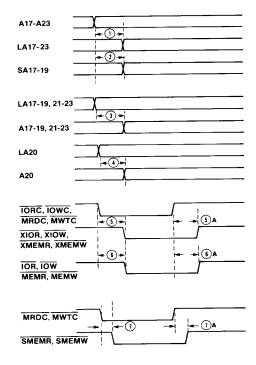

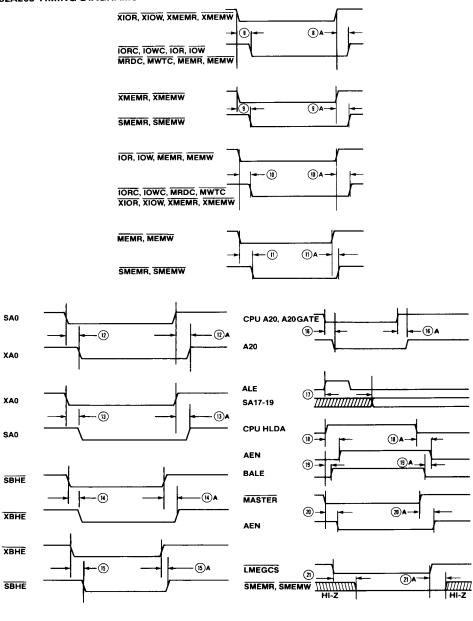

This section of the 82C201 generates various I/O and Memory control signals for an 80286 based system. The Command and Control Signal Generation Logic has two types of output signals. The first type, the Command signals, are decoded from the CPU status information available during the T<sub>S</sub> cycle. These signals (MEMR, MEMW, IOR, IOW, INTA) indicate which type of cycle is to be performed. The second type (ALE, DT/R, DEN, DSDEN0, DSDEN1, RAS) are the Control signals. These signals latch the address, determine the direction and enabling of the data bus buffers and start a memory cycle. Both sets of signals are derived from the CPU status information (M/IO, S0 S1) and are controlled by an internal state machine. Table 1 contains a list of the command and control outputs for each type of bus cycle.

Figure 3. Recommended Oscillator Circuit

**Table 1 Bus Cycle Status Definition**

| M/IO | <b>S</b> 1 | SO | Type of Bus Cycle     |

|------|------------|----|-----------------------|

| 0    | 0          | 0  | Interrupt acknowledge |

| 0    | 0          | 1  | I/O Read              |

| 0    | 1          | 0  | I/O Write             |

| 0    | 1          | 1  | None; idle            |