# ES2842 PCI Integrated LAN V.90/V.92 Modem Solution Product Brief

## DESCRIPTION

The ES2842, ESS Technology's first LAN plus host-based *Tele*Drive® modem chip for the PCI bus, provides desktop and notebook computers with greater connectivity to both packet networks and telephone networks. The ES2842 maximizes integration and reduces the external component BOM cost to a minimum.

The ES2842 device combines into a single-chip a host-based V.90/V.92 modem, modem control buffers, a modem codec, and an IEEE 802.3-compatible Ethernet media access controller (MAC) with an analog phoneline interface and a PCI bus interface. This advanced high-level device integration allows the ES2842 to be used as a host-based modem and LAN solution for desktop and notebook systems requiring either a modem connection or a 10/100 Ethernet connection. The ES2842 is also capable of providing a home network connection that complies with the Home Phoneline Networking Alliance (HomePNA) 1-Mb/ s (HPNA1.0) specification.

The ES2842 LAN feature supports 100BASE-TX (100-Mb/s mode) and 10BASE-T (10-Mb/s mode) full-duplex operations. The ES2842 includes a media-independent interface (MII) and reduced MII (RMII), enabling it to interface with an external PHY transceiver used for either a LAN or HPNA-based chipset.

The ES2842 modem sends and receives data and fax information and supports the telephone answering machine (TAM) feature. With its built-in ACPI  $D3_{cold}$  wake-on-LAN and wake-on-ring support, the ES2842 is an ideal modem solution for notebooks and battery-operated devices. The ES2842 modem provides the interface and control logic needed to transfer data between its serial I/O terminals and the PCI interface.

The ES2842 delivers a high modem connectivity rate, as well as high throughput without the need of a dedicated DSP. The ES2842 supports worldwide homologation and is capable of data/fax/voice call discrimination. With the addition of an external transformer DAA, the ES2842 provides a very cost-effective modem/LAN solution for add-on card, motherboard, and mini-PCI card implementations.

The ES2842 is available in a 128-pin low-profile quad flat pack (LQFP) package.

## FEATURES

- V.90/V.92 analog data/fax/TAM modem

- Data mode capabilities:

- V.90/V.92: 56 kbps

- ITU-T V.34: 33.6 kbps and fallbacks

- Fax mode capabilities:

- ITU-T V.17, V.29, V.27ter, and V.21ch2

- Group 3 (TIA/EIA-578 Class 1 and Class 2)

- Requires minimum 166-MHz Pentium with MMX technology

- Integrated modem codec and analog front end

- 16-bit ADC and DAC with built-in anti-aliasing and reconstruction filters

- Supports external transformer DAA

- 10/100-Mb/s LAN or 1-Mb/s HPNA networking capability

- Integrated on-chip 1/10/100-Mbps MAC controller capable of interfacing with 10Base-T PHY transceiver and with 100Base-TX PHY transceiver

- MII for connecting to external 10/100-Mbps PHY transceiver

- RMII for connecting to external 10/100-Mbps PHY transceiver

- Full-duplex operation supported in MII and RMII ports with independent transmit (TX) and receive (RX) channels

- Support for IEEE 802.3x flow control and IEEE 802.3u autonegotiation for 10Base-T and 100Base-TX

- EEPROM interface for subsystem ID and subsystem vendor ID

- ACPI and PCI power management standard-compliant

- Wake-on-ring and wake-on-LAN capability

- On-chip FIFOs for PCI bus and both RX and TX state machines

- Supports both RJ-11 tip and ring connection and RJ-45 LAN/ Ethernet connection

- PC99/PC2001-compliant with support for V.250, V.251, and V.253 commands

- Worldwide homologation

## MODEM DRIVER SUPPORT

- Microsoft Windows™ 98/SE/ME/2000

- Microsoft Windows NT 4.0

#### LAN DRIVER SUPPORT

- NIC drivers for Netware 3.x and 4.x networks (16-bit and 32-bit ODI)

- Microsoft Windows networks (NDIS 2.0, 4.0, and 5.0)

- Packet driver

- Linux

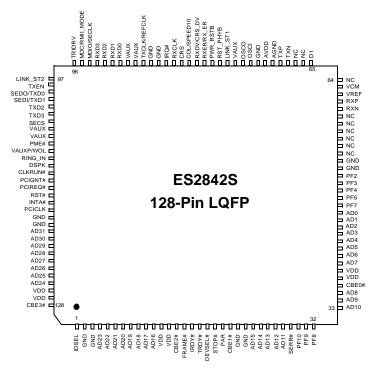

# PINOUT

Figure 1 shows the ES2842 pinout diagram.

Figure 1 ES2842 Pinout Diagram

# **PIN DESCRIPTIONS**

Table 1 lists the ES2842 pin descriptions.

| Table 1 | ES2842 Pin Descrip | tions |

|---------|--------------------|-------|

|         |                    | แบบเธ |

| Names                   | Pin Numbers                                   | I/O | Definitions                                                                                                                                                                                                                                                                   |

|-------------------------|-----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL                   | 1                                             | I   | ID select.                                                                                                                                                                                                                                                                    |

| GND                     | 2, 3, 22, 23, 52, 53, 72,<br>85, 86, 116, 117 | G   | Digital ground.                                                                                                                                                                                                                                                               |

| VDD                     | 12, 13, 37, 38, 126, 127                      | Р   | 3.3V digital power supply.                                                                                                                                                                                                                                                    |

| AD[31:0]                | 4:11, 24:28, 33:35,<br>39:46, 118:125         | I/O | Address and data lines from the PCI bus.                                                                                                                                                                                                                                      |

| C/BE[3:0]#              | 14, 21, 36, 128                               | I/O | PCI command/byte enable. During address phase of a transaction, these pins define the bus command. During data phase, these pins define the bus enable.                                                                                                                       |

| FRAME#                  | 15                                            | I/O | Cycle frame.                                                                                                                                                                                                                                                                  |

| IRDY#                   | 16                                            | I/O | Initiator ready.                                                                                                                                                                                                                                                              |

| TRDY#                   | 17                                            | I/O | Target ready.                                                                                                                                                                                                                                                                 |

| DEVSEL#                 | 18                                            | I/O | Device select.                                                                                                                                                                                                                                                                |

| STOP#                   | 19                                            | I/O | Stop transaction.                                                                                                                                                                                                                                                             |

| PAR                     | 20                                            | I/O | Parity.                                                                                                                                                                                                                                                                       |

| SERR#                   | 29                                            | OD  | System bus error.                                                                                                                                                                                                                                                             |

| PF[10:7] and<br>PF[5:2] | 30:32, 47:51                                  | I/O | General-purpose programmable bidirectional flag. These pins can be used for interfacing with a tele-<br>phone or other device, performing such functions as caller ID, etc. Refer to pin<br>descriptions of pins 54, 108, and 109 for preprogrammed telephone interface pins. |

PIN DESCRIPTIONS

| Table 1 | ES2842 Pin Descriptions | (Continued)  |

|---------|-------------------------|--------------|

| 100101  |                         | (Containada) |

| Names    | Pin Numbers          |     | Definitions                                                                                                                                                                                                                                                                                   |

|----------|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       | 54:59, 64:67         | -   | No connect.                                                                                                                                                                                                                                                                                   |

| RXN      | 60                   |     | Codec analog differential receive negative input. The DC level is VCM, and the full-scale input is either $2.2Vp$ -p±5% or $1.1Vp$ -p±5%, depending on the gain setting.                                                                                                                      |

| RXP      | 61                   | I   | Codec analog differential receive positive input. The DC level is VCM, and the full-scale input is either $2.2Vp-p\pm5\%$ or $1.1Vp-p\pm5\%$ , depending on the gain setting.                                                                                                                 |

| VREF     | 62                   | 0   | Voltage reference bypass. Has a range of 1.235V±5%. Bypass to AGND with 0.1-μF ceramic chip capacitor parallel with 10-μF tantalum capacitor.                                                                                                                                                 |

| VCM      | 63                   | 0   | Common mode voltage bypass. Has a range of 2.16V±5%. Bypass to AGND with 0.1-μF ceramic chip capacitor parallel with 10-μF tantalum capacitor.                                                                                                                                                |

| TXN      | 68                   | 0   | Codec analog differential transmit negative output. The DC level is VCM, and the full-scale input is either 2.8Vp-p $\pm$ 5% or 1.4Vp-p $\pm$ 5%, depending on the gain setting.The maximum loading is 1.2k $\Omega$ , in parallel with 20 pF for modem applications.                         |

| ТХР      | 69                   | 0   | Codec analog differential transmit positive output. The DC level is VCM, and the full-scale input is either 2.8Vp-p $\pm$ 5% or 1.4Vp-p $\pm$ 5%, depending on the gain setting.The maximum loading is 1.2k $\Omega$ , in parallel with 20 pF for modem applications.                         |

| AGND     | 70                   | G   | Analog ground.                                                                                                                                                                                                                                                                                |

| AVDD     | 71                   | Р   | 5V analog power supply.                                                                                                                                                                                                                                                                       |

| OSCI     | 73                   | I   | Crystal clock input.                                                                                                                                                                                                                                                                          |

| OSCO     | 74                   | 0   | Crystal clock output.                                                                                                                                                                                                                                                                         |

| VAUX     | 75, 88, 89, 104, 105 | Р   | 3.3V V <sub>AUX</sub> power supply for wake-on-ring and wake-on-LAN.                                                                                                                                                                                                                          |

| LINK_ST1 | 76                   | I   | Link status interface input from PHY.                                                                                                                                                                                                                                                         |

| PHY_RSTB | 77                   | 0   | Reset output to PHY; will follow PWR_RSTB and remain active for 1.3 msec after PWR_RSTB. Can be toggled by bit 7 of LAN_IO register [4Ah].                                                                                                                                                    |

| PWR_RSTB | 78                   | I   | Power-on reset. This is an active-low input signal when a power-on reset event occurs.                                                                                                                                                                                                        |

| RXER     | 79                   | I   | Receive error input for MII mode. Indicates that the external PHY transceiver has detected coding errors in the receive data frame now being transmitted to RXD[3:0]. RXER is ignored while RX_DV is deasserted.                                                                              |

| RX_ER    |                      | I   | Receive error input for RMII mode. Indicates that the external PHY transceiver has detected coding errors in the receive data frame now being transmitted to RXD[1:0]. RX_ER is ignored while RX_DV is deasserted.                                                                            |

| RXDV     |                      | I   | Receive data valid.                                                                                                                                                                                                                                                                           |

| CRS_DV   | 80                   | I   | Carrier sense/receive data valid. Asserted asynchronously by the PHY when the receive medium is nonidle. In 10Base-T mode, carrier is detected when squelch is passed in RMII mode.                                                                                                           |

| COL      |                      | I   | Collision. When selected as COL, asserted output whenever a collision is detected.                                                                                                                                                                                                            |

| SPEED10  | 81                   | I   | Speed select. Acts as toggle for 10-Mb/s and 100-Mb/s operation for external PHY transceiver in RMII mode.                                                                                                                                                                                    |

| CRS      | 82                   | I   | Carrier sense input.                                                                                                                                                                                                                                                                          |

| RXCLK    | 83                   | I   | Receive clock input. Provides the nibble rate clock timing reference for the output transfer of RXDV, RXD[3:0], and RXER/RX_ER signals and operates at 25/2.5 MHz.                                                                                                                            |

| IRQ#     | 84                   | I   | Interrupt request.                                                                                                                                                                                                                                                                            |

| TXCLK    |                      | I   | Transmit clock input. When selected as TXCLK, provides timing reference for transfer of the trans-<br>mitted data and operates at 25/2.5 MHz.                                                                                                                                                 |

| REFCLK   | 87                   | I   | Reference clock input. When selected as REFCLK, provides continuous clock timing reference for CRS_DV, RXD[1:0], TXEN, TXD[1:0], and RX_ER. Operates at 50 MHz ±50 ppm with a duty cycle between 35% and 65% in RMII mode.                                                                    |

| RXD[3:0] | 90:93                | Ι   | Receive data. When in RMII mode, only RXD[1:0] are defined.                                                                                                                                                                                                                                   |

| MDIO     | 94                   | I/O | When the MDIO function is selected, this pin functions as the MII management data I/O pin. It acts as an output during the header portion of management frame transfers and during the data portion of write operations. It also acts as an input during the data portion of read operations. |

| SECLK    | 1                    | 0   | Serial EEPROM data clock input.                                                                                                                                                                                                                                                               |

ORDERING INFORMATION

| Names     | Pin Numbers | I/O | Definitions                                                                                                                                                                                                                    |

|-----------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDC       |             | 0   | When the MDC function is selected, this pin functions as the MII management data clock pin. It runs up to 2.5 MHz.                                                                                                             |

| RMII_MODE | 95          |     | RMII_MODE enable. The ES2842 supports both MII and RMII modes. When the RMII_MODE signal is high, RMII mode is supported. When the RMII_MODE signal is low, MII mode is supported. Strap option pin latched at power-on reset. |

| TRIDRV    | 96          | 0   | Tri-state output pin connected to the input pin of HPNA PHY to tri-state output of HPNA PHY. When asserted high, this pin tri-states all outputs except open-drain outputs.                                                    |

| LINK_ST2  | 97          | I   | Link status Interface input from (second) HPNA PHY.                                                                                                                                                                            |

| TXEN      | 98          | 0   | Transmit enable. This pin indicates that the MAC is presenting valid data on TXD[3:0]. TXEN transi-<br>tions are latched on the falling edge of REFCLK.                                                                        |

| SEDO      |             | 0   | Serial EEPROM data input.                                                                                                                                                                                                      |

| TXD[0]    | 99          | 0   | Transmit data output pin 0.                                                                                                                                                                                                    |

| SEDI      |             | I   | Serial EEPROM data output pin with an internal pullup.                                                                                                                                                                         |

| TXD[1]    | 100         | 0   | Transmit data output pin 1.                                                                                                                                                                                                    |

| TXD[3:2]  | 101, 102    | 0   | Transmit data pins 2 and 3 in MII mode. Not defined in RMII mode.                                                                                                                                                              |

| SECS      | 103         | 0   | Serial EEPROM port chip select output using 10k $\Omega$ pulldown resistor.                                                                                                                                                    |

| PME#      | 106         | OD  | Power management enable interrupt output to wake up the system.                                                                                                                                                                |

| VAUXP     | 107         | I   | $V_{AUX}$ support detection pin. $V_{AUXP}$ is driven high at reset to indicate that ACPI is supported with $D3_{cold}$ state. No support when driven low. Strap option pin latched at power-on reset.                         |

| WOL       | 107         | 0   | Wake-on-LAN signal output. The ES2842 asserts this signal if a change is detected in link status, Magic Packet™, or sample frame events.                                                                                       |

| RING_IN   | 108         | I   | Ring-in-detection input.                                                                                                                                                                                                       |

| DSPK      | 109         | 0   | Modem speaker digital output.                                                                                                                                                                                                  |

| CLKRUN#   | 110         | I/O | CLKRUN# is an input/output pin for PCI clock status and an output to start or accelerate clock func-<br>tion.                                                                                                                  |

| PCIGNT#   | 111         | I   | PCI grant input.                                                                                                                                                                                                               |

| PCIREQ#   | 112         | 0   | PCI request output.                                                                                                                                                                                                            |

| RST#      | 113         | I   | PCI bus reset.                                                                                                                                                                                                                 |

| INTA#     | 114         | OD  | Interrupt A request output, active-low. INTA# is the level triggered interrupt pin dedicated to servic-<br>ing internal device interrupt requests.                                                                             |

| PCICLK    | 115         | I   | PCI bus clock input.                                                                                                                                                                                                           |

Table 1 ES2842 Pin Descriptions (Continued)

## **ORDERING INFORMATION**

| Part Number | Description                 | Package      |  |

|-------------|-----------------------------|--------------|--|

| ES2842S     | PCI V.90/V.92 HSP Modem LAN | 128-pin LQFP |  |

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: (510) 492-1088 Fax: (510) 492-1898 No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

ESS Technology, Inc. makes no representations or warranties regarding the content of this document.

All specifications are subject to change without prior notice.

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

TeleDrive is a registered trademark of ESS Technology, Inc.

(P) U.S. patents pending.

All other trademarks are owned by their respective holders and are used for identification purposes only.