# Self-Contained Audio Preamplifier

# SSM2017

**FEATURES**

Excellent Noise Performance: 950 pV/VHz or 1.5 dB

**Noise Figure**

Ultralow THD: < 0.01% @ G = 100 Over the Full Audio

Band

Wide Bandwidth: 1 MHz @ G = 100

High Slew Rate: 17 V/μs typ

Unity Gain Stable

True Differential Inputs

Subaudio 1/f Noise Corner

8-Pin Mini-DIP with Only One External Component

Required

Very Low Cost ( )

Extended Temperature Range: -40°C to +85°C

APPLICATIONS

Audio Mix Consoles

Intercom/Paging Systems

Two-Way Radio

Sonar

**Digital Audio Systems**

## **GENERAL DESCRIPTION**

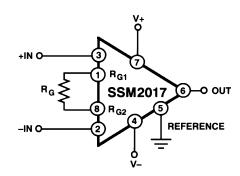

The SSM2017 is a latest generation audio preamplifier combining SSM preamplifier design expertise with advanced processing. The result is excellent audio performance from a self-contained 8-pin mini-DIP device, requiring only one external gain set resistor or potentiometer. The SSM2017 is further enhanced by its unity gain stability.

Key specifications include ultralow noise (1.5 dB noise figure) and THD (<0.01% at G=100), complemented by wide bandwidth and high slew rate.

Applications for this low cost device include microphone preamplifiers and bus summing amplifiers in professional and consumer audio equipment, sonar, and other applications requiring a low noise instrumentation amplifier with high gain capability.

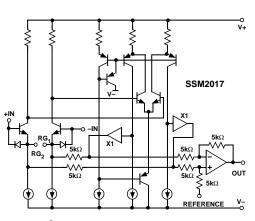

### **FUNCTIONAL BLOCK DIAGRAM**

# $\textbf{SSM2017-SPECIFICATIONS} \quad \text{(V}_S = \pm 15 \text{ V and } -40^{\circ}\text{C} \leq T_A \leq +85^{\circ}\text{C, unless otherwise noted. Typical specifications apply at } T_A = +25^{\circ}\text{C.)}$

| Parameter                                                                                     | Symbol                                    | Conditions                                                                                                                                                                                        | Min                        | Тур                                                          | Max                | Units                                                                                                                                   |

|-----------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| DISTORTION PERFORMANCE  Total Harmonic Distortion Plus Noise                                  | THD+N                                     | $\begin{array}{l} T_A = +25^{\circ}C \\ V_O = 7 \ V \ rms \\ R_L = 5 \ k\Omega \\ G = 1000, \ f = 1 \ kHz \\ G = 100, \ f = 1 \ kHz \\ G = 10, \ f = 1 \ kHz \\ G = 1, \ f = 1 \ kHz \end{array}$ |                            | 0.012<br>0.005<br>0.004<br>0.008                             |                    | %<br>%<br>%                                                                                                                             |

| NOISE PERFORMANCE<br>Input Referred Voltage Noise Density                                     | e <sub>n</sub>                            | f = 1 kHz, G = 1000<br>f = 1 kHz; G = 100<br>f = 1 kHz; G = 10<br>f = 1 kHz; G = 1                                                                                                                |                            | 0.95<br>1.95<br>11.83<br>107.14                              |                    | $\begin{array}{c} nV/\sqrt{\overline{Hz}} \\ nV/\sqrt{\overline{Hz}} \\ nV/\sqrt{\overline{Hz}} \\ nV/\sqrt{\overline{Hz}} \end{array}$ |

| Input Current Noise Density                                                                   | i <sub>n</sub>                            | f = 1 kHz, G = 1000                                                                                                                                                                               |                            | 2                                                            |                    | pA/√Hz                                                                                                                                  |

| DYNAMIC RESPONSE Slow Rate                                                                    | SR                                        | $G = 10$ $R_L = 4.7 \text{ k}\Omega$ $C_L = 50 \text{ pF}$                                                                                                                                        | 10                         | 17                                                           |                    | V/µs                                                                                                                                    |

| Small Signal Bandwidth                                                                        | BW-3 dB                                   | $T_A = +25^{\circ}C$<br>G = 1000<br>G = 10                                                                                                                                                        |                            | 200<br>1000<br>2000<br>4000                                  |                    | kHz<br>kHz<br>kHz<br>kHz                                                                                                                |

| INPUT Input Offset Voltage Input Bias Current Input Offset Current Common-Mode Rejection      | I <sub>B</sub> Ios CMR                    | $ \begin{pmatrix} V_{\rm CM} = 0 & V \\ V_{\rm CM} = 0 & V \\ V_{\rm CM} = \pm 8 & V \\ G = 1000 \\ G = 100 \\ \end{pmatrix} $                                                                    | 80<br>60                   | $ \begin{array}{c c} 0.1 \\ 0.002 \\ 112 \\ 92 \end{array} $ | 1.2<br>25<br>±2.5  | mV<br>μΑ<br>μΑ<br>dB                                                                                                                    |

| Power Supply Rejection                                                                        | PSR                                       | $G = 10 \\ G = 1, T_A = +25^{\circ}C \\ G = 1, T_A = -40^{\circ}C \text{ to } +85^{\circ}C \\ V_S = \pm 6 \text{ V to } \pm 18 \text{ V} \\ G = 1000 \\ G = 100 \\ G = 10$                        | 26<br>20<br>80<br>60<br>40 | 74<br>54<br>54<br>124<br>118<br>101                          |                    | dB<br>dB<br>dB<br>dB                                                                                                                    |

| Input Voltage Range<br>Input Resistance                                                       | IVR<br>R <sub>IN</sub>                    | G = 1 Differential, $G = 1000$ $G = 1$ Common Mode, $G = 1000$ $G = 1$                                                                                                                            | 26<br>±8                   | 82<br>1<br>30<br>5.3<br>7.1                                  |                    | $\begin{array}{c} dB \\ V \\ M\Omega \\ M\Omega \\ M\Omega \\ M\Omega \\ M\Omega \end{array}$                                           |

| OUTPUT<br>Output Voltage Swing<br>Output Offset Voltage<br>Minimum Resistive Load Drive       | V <sub>O</sub> V <sub>OOS</sub>           | $R_{L} = 2 \text{ k}\Omega; T_{A} = +25^{\circ}\text{C}$ $T_{A} = +25^{\circ}\text{C}$ $T_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                      | ±11.0                      | ±12.3<br>-40<br>2<br>4.7                                     | 500                | V<br>mV<br>kΩ<br>kΩ                                                                                                                     |

| Maximum Capacitive Load Drive<br>Short Circuit Current Limit<br>Output Short Circuit Duration | $I_{SC}$                                  | Output-to-Ground Short                                                                                                                                                                            |                            | 50<br>±50                                                    | 10                 | pF<br>mA<br>sec                                                                                                                         |

| GAIN<br>Gain Accuracy                                                                         | $R_{G} = \frac{10 \ k\Omega}{G - 1}$      | $\begin{array}{c} T_A = +25^{\circ}C \\ R_G = 10~\Omega,~G = 1000 \\ R_G = 101~\Omega,~G = 100 \\ R_G = 1.1~k\Omega,~G = 10 \\ R_G = \infty,~G = 1 \end{array}$                                   |                            | 0.25<br>0.20<br>0.20<br>0.05                                 | 1<br>1<br>1<br>0.5 | dB<br>dB<br>dB<br>dB                                                                                                                    |

| Maximum Gain                                                                                  | G                                         | 1vG, O - 1                                                                                                                                                                                        |                            | 70                                                           | 0.0                | dB                                                                                                                                      |

| REFERENCE INPUT<br>Input Resistance<br>Voltage Range<br>Gain to Output                        |                                           |                                                                                                                                                                                                   |                            | 10<br>±8<br>1                                                |                    | kΩ<br>V<br>V/V                                                                                                                          |

| POWER SUPPLY<br>Supply Voltage Range<br>Supply Current                                        | $egin{array}{c} V_S \ I_{SY} \end{array}$ | $V_{CM} = 0 \text{ V}, \text{ R}_{L} = \infty$                                                                                                                                                    | ±6                         | ±10.6                                                        | ±22<br>±14.0       | V<br>mA                                                                                                                                 |

-2-

Specifications subject to change without notice.

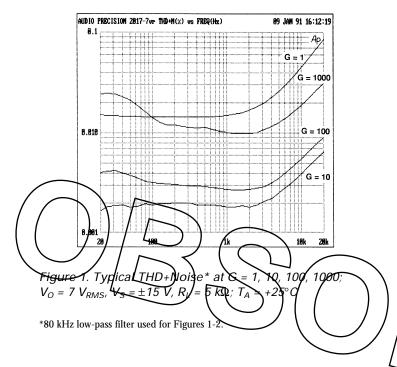

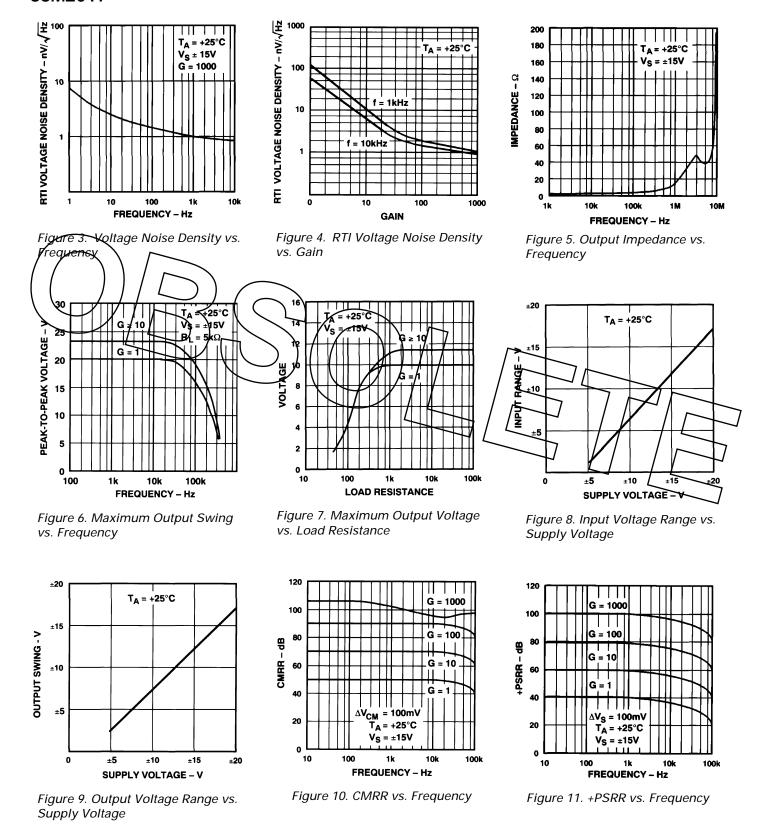

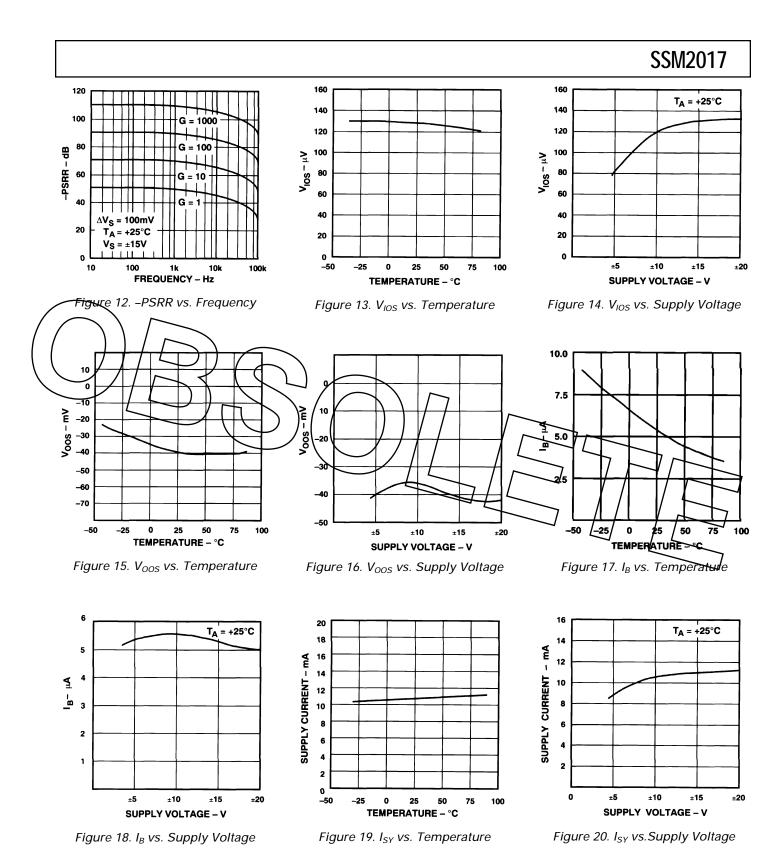

# **Typical Performance Characteristics**

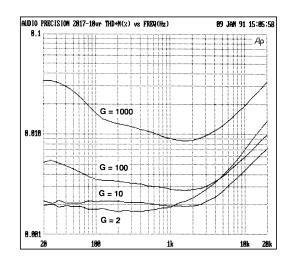

Figure 2. Typical THD+ Noise \* at G = 2, 10, 100, 1000;  $V_D = 10 \ V_{RMS}$ ,  $V_{S,r} = \pm 18 \ V$ ,  $R_L = 5 \ k\Omega$ ;  $T_A = +25^{\circ}C$

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                                                                |  |

|-------------------------------------------------------------------------------|--|

| Input Voltage Supply Voltage                                                  |  |

| Output Short Circuit Duration 10 sec                                          |  |

| Storage Temperature Range (P, Z Packages) -65°C to +150°C                     |  |

| Junction Temperature ( $T_J$ )65°C to +150°C                                  |  |

| Lead Temperature Range (Soldering, 60 sec) 300°C                              |  |

| Operating Temperature Range40°C to +85°C                                      |  |

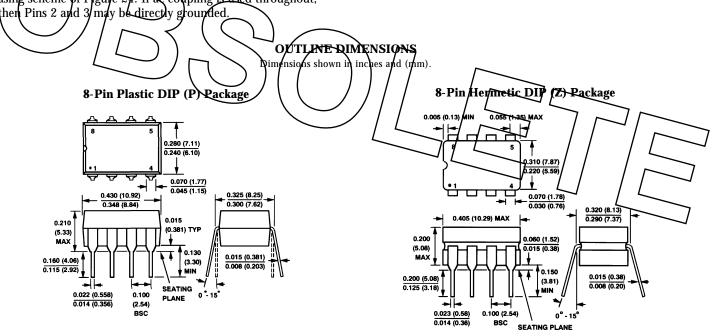

| Thermal Resistance*                                                           |  |

| 8-Pin Hermetic DIP (Z): $\theta_{\rm tr} = 134$ : $\theta_{\rm to} = 12$ °C/W |  |

| 8-Pin Hermetic DIP (Z): $\theta_{JA} = 134$ ; $\theta_{JC} = 12$     | °C/W |

|----------------------------------------------------------------------|------|

| 8-Pin Plastic DIP (P): $\theta_{JA} = 96$ ; $\theta_{JC} = 37 \dots$ | °C/W |

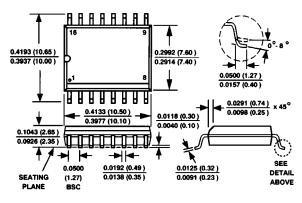

| 16-Pin SOIC (S): $\theta_{JA} = 92$ ; $\theta_{JC} = 27$             | °C/W |

<sup>\*</sup> $\theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip and plastic DIP;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SOL package.

| Model         | Temperature    | Package           | Package |  |

|---------------|----------------|-------------------|---------|--|

|               | Range*         | Description       | Option  |  |

| SSM2017P      | -40°C to +85°C | 8-Pin Plastic DIP | N-8     |  |

| SSM2017S      | -40°C to +85°C | 16-Lead SOL       | R-16    |  |

| SSM2017S-REEL | -40°C to +85°C | 16-Lead SOL       | R-16    |  |

**ORDERING GUIDE**

# **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the SSM2017 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. B \_3\_

<sup>\*</sup>XIND = -40°C to +85°C.

-4-

REV. B

REV. B \_5\_

and

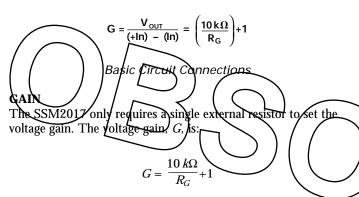

$$R_G = \frac{10 \ k\Omega}{G - 1}$$

For convenience, Table I lists various values of  $R_{\!\scriptscriptstyle G}$  for common gain levels.

Table I. Values of R<sub>G</sub> for Various Gain Levels

| $\overline{\mathbf{A_{V}}}$ | dB | $\mathbf{R}_{\mathbf{G}}$ |

|-----------------------------|----|---------------------------|

| 1                           | 0  | NC                        |

| 3.2                         | 10 | 4.7k                      |

| 10                          | 20 | 1.1k                      |

| 31.3                        | 30 | 330                       |

| 100                         | 40 | 100                       |

| 314                         | 50 | 32                        |

| 1000                        | 60 | 10                        |

The voltage gain can range from 1 to 3500. A gain set resistor is not required for unity gain applications. Metal-film or wirewound resistors are recommended for best results.

The total gain accuracy of the SSM2017 is determined by the tolerance of the external gain set resistor,  $R_{\rm G}$ , combined with the gain equation accuracy of the SSM2017. Total gain drift combines the mismatch of the external gain set resistor drift with that of the internal resistors (20 ppm/ $^{\circ}$ C typ).

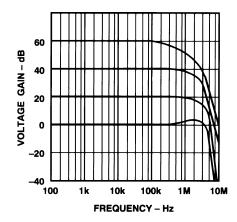

Bandwidth of the SSM2017 is relatively independent of gain as shown in Figure 21. For a voltage gain of 1000, the SSM2017 has a small-signal bandwidth of 200 kHz. At unity gain, the bandwidth of the SSM2017 exceeds 4 MHz.

Figure 21. Bandwidth of the SSM2017 for Various Values of Gain

#### **NOISE PERFORMANCE**

The SSM2017 is a very low noise audio preamplifier exhibiting a typical voltage noise density of only 1 nV/\(\bar{Hz}\) at 1 kHz. The exceptionally low noise characteristics of the SSM2017 are in part achieved by operating the input transistors at high collector currents since the voltage noise is inversely proportional to the square root of the collector current. Current noise, however, is directly/proportional to the square root of the collector current. As a result, the outstanding voltage noise performance of the SSM2017 is obtained at the expense of current noise performance. At low preamplifier gains, the effect of the SSM2017's voltage and current noise is insignificant.

The total noise of an audio preamplifier channel can be calculate by:

$$E_n = \sqrt{e_n^2 + (i_n R_S)^2 + e_t^2}$$

where:

$E_n$  = total input referred noise

$e_n$  = amplifier voltage noise

$i_n$  = amplifier current noise

$R_S$  = source resistance

$e_t$  = source resistance thermal noise.

For a microphone preamplifier, using a typical microphone impedance of 150  $\Omega$  the total input referred noise is:

$$e_n = 1 \text{ nV/}\sqrt{\text{Hz}}$$

@ 1 kHz, SSM2017  $e_n$

$$i_n = 2 \text{ pA}/\sqrt{\text{Hz}} @ 1 \text{ kHz}, \text{SSM2017 } i_n$$

$R_S = 150 \Omega$ , microphone source impedance

$e_t = 1.6 \text{ nV/}\sqrt{\text{Hz}}$  @ 1 kHz, microphone thermal noise

$$E_n = \sqrt{(1 \ nV\sqrt{Hz})^2 + 2 \ (pA/\sqrt{Hz} \times 150 \ \Omega)^2 + (1.6 \ nV/\sqrt{Hz})^2}$$

= 1.93  $nV/\sqrt{Hz}$  @ 1  $kHz$ .

This total noise is extremely low and makes the SSM2017 virtually transparent to the user.

-6- REV. B

#### **INPUTS**

The SSM2017 has protection diodes across the base emitter junctions of the input transistors. These prevent accidental avalanche breakdown which could seriously degrade noise performance. Additional clamp diodes are also provided to prevent the inputs from being forced too far beyond the supplies.

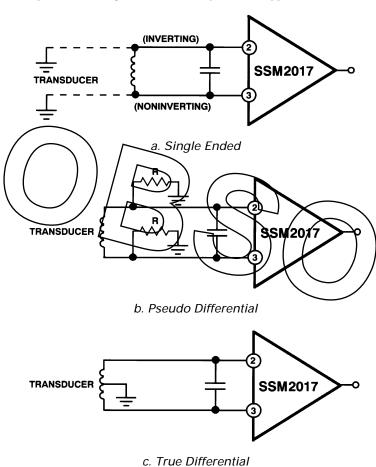

Figure 22. Three Ways of Interfacing Transducers for High Noise Immunity

Although the SSM2017's inputs are fully floating, care must be exercised to ensure that both inputs have a dc bias connection capable of maintaining them within the input common-mode range. The usual method of achieving this is to ground one side of the transducer as in Figure 22a, but an alternative way is to float the transducer and use two resistors to set the bias point as in Figure 22b. The value of these resistors can be up to 10 k $\Omega$ , but they should be kept as small as possible to limit common-mode pickup. Noise contribution by resistors themselves is negligible since it is attenuated by the transducer's impedance. Balanced transducers give the best noise immunity and interface directly as in Figure 22c.

### REFERENCE TERMINAL

The output signal is specified with respect to the reference terminal, which is normally connected to analog ground. The reference may also be used for offset correction or level shifting. A reference source resistance will reduce the common-mode rejection by the ratio of 5 k $\Omega/R_{REF}.$  If the reference source resistance is 1  $\Omega,$  then the CMR will be reduced to 74 dB (5 k $\Omega/1$   $\Omega$  = 74 dB).

COMMON-MODE REJECTION

Ideally, a microphone preamplifier responds only to the difference between the two input signals and rejects common-mode voltages and noise. In practice, there is a small change in output voltage when both inputs experience the same common-mode voltage change; the ratio of these voltages is called the common-mode gain. Common-mode rejection (CMR) is the logarithm of the ratio of differential mode gain to common mode gain. expressed in dB.

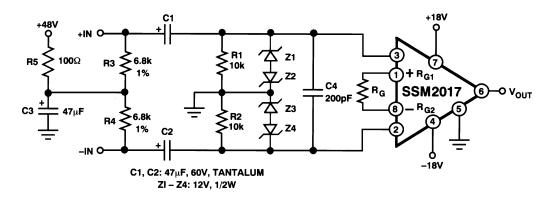

#### PHANTOM POWERING

A typical phantom microphone powering circuit is shown in Figure 23.  $Z_1$  through  $Z_4$  provide transient overvoltage protection for the SSM2017 whenever microphones are plugged in or unplugged.

Figure 23. SSM2017 in Phantom Powered Microphone Circuit

REV. B -7-

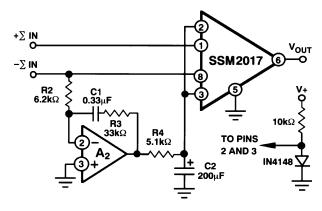

### **BUS SUMMING AMPLIFIER**

In addition to is use as a microphone preamplifier, the SSM2017 can be used as a very low noise summing amplifier. Such a circuit is particularly useful when many medium impedance outputs are summed together to produce a high effective noise gain.

The principle of the summing amplifier is to ground the SSM2017 inputs. Under these conditions, Pins 1 and 8 are ac virtual grounds sitting about 0.55 V below ground.

To remove the 0.55 V offset, the circuit of Figure 24 is recommended.

$A_2$  forms a "servo" amplifier feeding the SSM2017's inputs. This places Pins I and 8 at a true dc virtual ground. R4 in conjunction with C2 remove the voltage noise of  $A_2$ , and in fact just about any operational amplifier will work well here since it is removed from the signal path. If the dc offset at Pins I and 8 is not too critical, then the servo loop can be replaced by the diode biasing scheme of Figure 24. If ac coupling is used throughout,

Figure 24. Bus Summing Amplifier

# 16-Pin SOIC (S) Package

-8-

REV. B