## MN158414

#### ■ Features

- ROM capacity: 4,096 × 8 bits

- ◆ RAM capacity:256×4bits +1,024×4bits (direct access)(access via port)

- Machine cycle: 2.0  $\mu$ s (4.5 to 5.5 V)

(2.23  $\mu$ s at 3.58 MHz when DTMF is used)

8.0 μs(2.5 to 5.5 V)

• Interrupt:External interrupt 4

Timer interrupt

Serial interrupt

1

2 Hz-cycle interrupt 1

- Timer/counter: Timer and event counter functions provided by 8-bit programmable timer with 7-bit prescaler

- Serial interface: 8-bit synchronous type

- DTMF circuit incorporated: DTMF output, 1 channel

- TONE circuit incorporated: Programmable setting of frequency enabled

- LCD driver circuit incorporated: 4 commons, 32 segments

- Time base interrupt generator circuit incorporated: 2 Hz cycle

- Clock selector circuit incorporated:

Programmable selection of system clock sources enabled. Clock sources are OSC1, OSC2 or XI, XO.

- Backup mode: STOP/HALT mode

- Supply voltage: 2.5 V to 5.5 V

| ●I/O pins: | 8  | for general purpose I/C      |

|------------|----|------------------------------|

|            | 15 | for general purpose input    |

|            | 8  | for general purpose output   |

|            | 5  | for high breakdown voltage   |

|            |    | N-channel open drain output  |

|            | 1  | for serial data input        |

|            | 1  | for serial data output       |

|            | 1  | for serial clock I/O         |

|            | 4  | for LCD drive common output  |

|            | 32 | for LCD drive segment output |

|            | 1  | for DTMF output              |

|            | 1  | for TONE output              |

|            |    |                              |

- Process: Silicon gate CMOS

- Package: 84-QFP

- Piggyback: EP158414

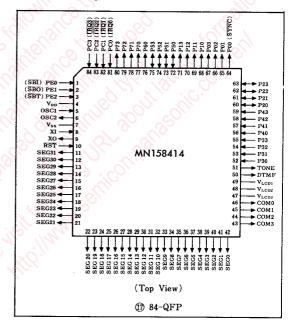

#### ■ Pin Configuration

#### ■ Pin Descriptions

| Pin                  | Symbol                                                         | Pin name                           | I/O       | Description                                                                                                                                                                                                                                           |

|----------------------|----------------------------------------------------------------|------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 7                  | V <sub>DD</sub><br>V <sub>SS</sub>                             | Power supply                       | I         | Connect+2.5-5.5 V to $V_{\text{DD}}$ , and 0 V to $V_{\text{SS}}$                                                                                                                                                                                     |

| 5<br>6               | OSC1<br>OSC2                                                   | Clock input<br>Clock output        | I<br>O    | Oscillator terminals to connect f <sub>osc</sub> ceramic oscillator or crystal oscillator.  A feedback resistor is incorporated between OSC1 and OSC2.                                                                                                |

| 8<br>9               | XI<br>XO                                                       | Clock input<br>Clock output        | I<br>O    | Event counter clock source terminals to connect a crystal oscillator.  A feedback resistor is incorporated between XI and XO. They serve as an operating clock source when XI/XO is specified by clock selection.                                     |

| 10                   | RST                                                            | Reset input                        | I         | Reset is applied if the "L" level is inputted over 1 machine cycle.  A pull-up resistor is incorporated.                                                                                                                                              |

| 64                   | SYNC<br>(P00)                                                  | Sync. signal output /output        | 0         | An internal timing signal is outputted every machine cycle at reset time.  Available as a normal output port after reset is cancelled.                                                                                                                |

| 81<br>82<br>83<br>84 | LRQ0<br>IRQ1<br>IRQ2<br>IRQ3<br>(PC0<br>~PC3)                  | External inter-<br>rupt/input      | I         | External interrupt terminals which receives an interrupt at a negative edge. Also available as as a normal input port.                                                                                                                                |

| 1                    | SBI<br>(PEO)                                                   | Serial interface data input/input  |           | Serial interface receive data input terminal which inputs 8-bit serial data. Also available as a normal input port.                                                                                                                                   |

| 2                    | SBO<br>(PE1)                                                   | Serial interface data output/input | O<br>/I   | Serial interface send data output terminal which outputs 8-bit serial data. Can be set to high impedance when no data is outputted.  Also available as a normal input port.                                                                           |

| 3                    | SBT<br>(PE1)                                                   |                                    | I/O<br>/I | Clock I/O terminal for sending or receiving of Serial Interface. In internal clock mode, it is output terminal and in external clock mode, it is input terminal.                                                                                      |

| 50                   | DTMF                                                           | DTMF signal output                 | 0         | A DTMF signal is outputted. When DTMF is used, source oscillation of 3.58 MHz is used.                                                                                                                                                                |

| 49<br>48<br>47       | V <sub>LCD</sub> 1<br>V <sub>LCD</sub> 2<br>V <sub>LCD</sub> 3 | LCD power suppy                    | I         | LCD drive power supply terminals $ \begin{array}{l} V_{\text{LCD1}} = V_{\text{DD}} - (1/3) V_{\text{LCD}}, \\ V_{\text{LCD2}} = V_{\text{DD}} - (2/3) V_{\text{LCD}}, \\ V_{\text{LCD3}} = V_{\text{DD}} - V_{\text{LCD}} & \text{CCD} \end{array} $ |

| 43~46                | COM0~<br>COM3                                                  | LCD common output                  | 0         | LCD Common signal output terminals                                                                                                                                                                                                                    |

| 11~42                | SEG0~<br>SEG31                                                 | LCD segment output                 | 0         | LCD segment signal output terminals                                                                                                                                                                                                                   |

| 51                   | TONE                                                           | TONE output                        | 0         | Enables programmable setting of pulse output of 694.8 to 1,639.0 Hz(source oscillation: 3.58 MHz), same as DTMF output. Output can be turned on/off by controlling the port P30.                                                                      |

| 64~67<br>68~71       | P00~P03<br>P10~P13                                             | Parallel data output               | 0         | 4-bit parallel data output ports. Push-pull output. High impedance at reset time.                                                                                                                                                                     |

| 60~63<br>72~75       | P20~P23<br>P50~P53                                             | Parall data I/O                    | I/O       | 4-bit parallel data input or output ports. P20-P23 and P50-P53 can be I/O-selected at P32 and P33, respectively. High impedance at reset time.                                                                                                        |

### ■ Pin Descriptions(Continued)

| Pin            | Symbol             | Pin name               | I/O | Description                                                                                                                                      |

|----------------|--------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 52~55<br>56~59 | P30~P33<br>P40~P43 | Parallel data input    | I   | 4-bit parallel data input ports.  No pull-up resistor is incor-porated.                                                                          |

| 76<br>77~80    | P60<br>P70~P73     | Parallel data output   | 0   | 4-bit parallel data output ports. 12 V breckdown N-channel open drain output. High impedance at reset time.                                      |

| 81~84          |                    | Parallel data output   | I   | 4-bit parallel data input ports.  These ports are jointly used as IRQ0, IRQ1, IRQ2 and IRQ3, respectively.  No pull-up resistor is incorporated. |

| 1~3            | PE0~PE2            | Parallel data<br>input | I   | 3-bit Parallel data input ports. These ports are jointly used as SBI, SBO and SBT, respectively. No pull-up resistor is incorporated.            |

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805