## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## MOS INTEGRATED CIRCUIT

## $\mu$ PD17P228

# 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROLLER

#### **DESCRIPTION**

The  $\mu$ PD17P228 is a model of the  $\mu$ PD17228 with a one-time PROM instead of an internal mask ROM.

Since the user can write programs to the  $\mu$ PD17P228, it is ideal for experimental production or small-scale production of the  $\mu$ PD17225, 17226, 17227 or 17228 systems.

When reading this document, also read the documents related to the μPD17225, 17226, 17227 and 17228.

Detailed functions are described in the following user's manual. Read this manual when designing your system.  $\mu$ PD172 $\times\times$  Series User's Manual: U12795E

#### **FEATURES**

- Pin compatible with μPD17225, 17226, 17227 and 17228 (except PROM programming function)

- · Carrier generator circuit for infrared remote controller (REM output)

- 17K architecture: General-purpose register method

- Program memory (one-time PROM): 16 Kbytes (8192 × 16)

- Data memory (RAM): 223 × 4 bits

- Pull-up resistor can be connected to RESET pin

- Low-voltage detection circuit (WDOUT output)

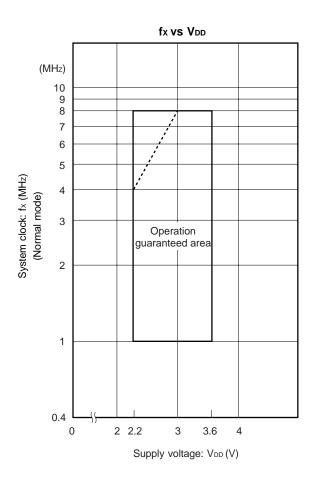

- Supply voltage:  $V_{DD} = 2.2$  to 3.6 V (fx = 4 MHz: high-speed mode, 4  $\mu$ s)  $V_{DD} = 3.0$  to 3.6 V (fx = 8 MHz: high-speed mode, 2  $\mu$ s)

## **APPLICATIONS**

Preset remote controllers, toys, and portable systems

#### ORDERING INFORMATION

| Part Number     | Package                             |

|-----------------|-------------------------------------|

| μPD17P228MC-5A4 | 30-pin plastic SSOP (7.62 mm (300)) |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

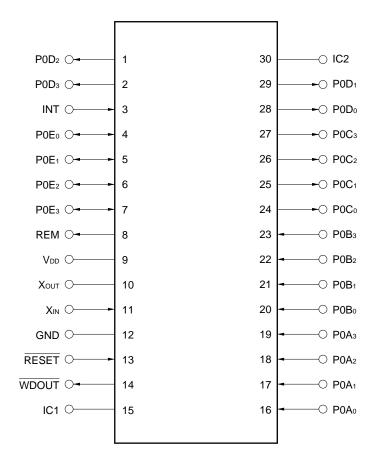

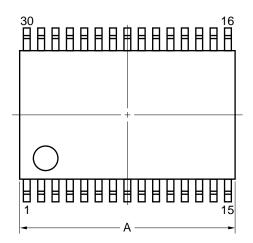

## PIN CONFIGURATION (TOP VIEW)

30-pin plastic SSOP (7.62 mm (300))

μPD17P228MC-5A4

## (1) Normal oprating mode

GND : Ground

IC1, IC2 : Internally connected Note

INT : External interrupt request signal input

$\begin{array}{lll} P0A_0\text{-}P0A_3 & : & Input \ port \ (CMOS \ input) \\ P0B_0\text{-}P0B_3 & : & Input \ port \ (CMOS \ input) \end{array}$

P0C<sub>0</sub>-P0C<sub>3</sub> : Output port (N-ch open-drain output) P0D<sub>0</sub>-P0D<sub>3</sub> : Output port (N-ch open-drain output) P0E<sub>0</sub>-P0E<sub>3</sub> : I/O port (CMOS push-pull output)

REM : Remote controller output (CMOS push-pull output)

RESET : Reset input

VDD : Power supply

WDOUT : Hang-up/low voltage detection output (N-ch open-drain output)

XIN, XOUT : Resonator connection

Note This pin cannot be used. Leave unconnected.

## (2) PROM programming mode

Caution Contents in parantheses indicate how to handle unused pins in PROM programming mode. L :Connect to GND via a resistor (470  $\Omega$ ) separately. OPEN:Leave unconnected.

CLK : Clock input for PROM

Do - D7 : Data input/output for PROM

GND : Ground

MD<sub>0</sub> - MD<sub>3</sub> : Mode select input for PROM

V<sub>DD</sub> : Power supply

VPP : Power supply for PROM writing

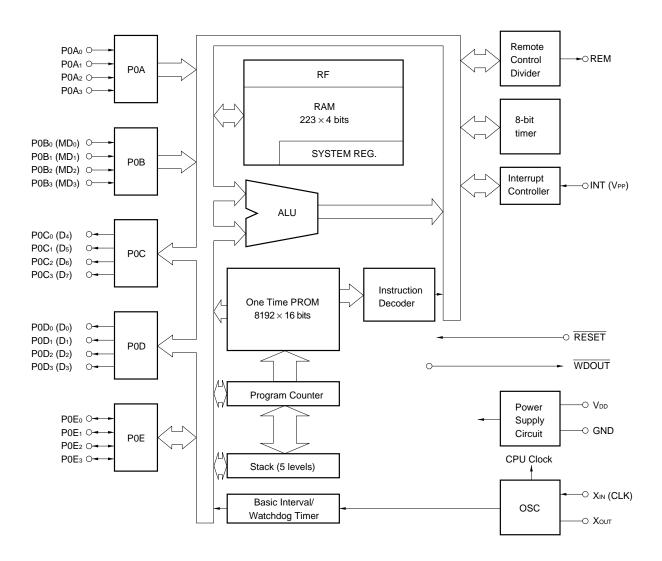

## **BLOCK DIAGRAM**

Remark ( ): during PROM programming mode

## **CONTENTS**

| 1. | DIFFRENCES AMONG $\mu$ PD17225, 17226, 17227, 17228 AND $\mu$ PD17P228 | 6  |

|----|------------------------------------------------------------------------|----|

| 2. | PIN FUNCTIONS                                                          | 7  |

|    | 2.1 Normal Operation Mode                                              | 7  |

|    | 2.2 PROM Programming Mode                                              | 8  |

|    | 2.3 Input/Output Circuits                                              | 9  |

|    | 2.4 Processing of Unused Pins                                          | 10 |

|    | 2.5 Notes on Using the RESET and INT Pins                              | 10 |

| 3. | WRITING AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)                   | 11 |

|    | 3.1 Operating Mode When Writing/Verifying Program Memory               | 11 |

|    | 3.2 Program Memory Writing Procedure                                   | 12 |

|    | 3.3 Program Memory Reading Procedure                                   | 13 |

| 4. | ELECTRICAL SPECIFICATIONS                                              | 14 |

| 5. | PACKAGE DRAWING                                                        | 21 |

| 6. | RECOMMENDED SOLDERING CONDITIONS                                       | 22 |

| ΑP | PENDIX. DEVELOPMENT TOOLS                                              | 23 |

## 1. DIFFERENCES AMONG $\mu$ PD17225, 17226, 17227, 17228 AND $\mu$ PD17P228

$\mu$ PD17P228 is equipped with PROM to which data can be written by the user instead of the internal mask ROM (program memory) of the  $\mu$ PD17228.

Table 1-1 shows the differences between the  $\mu$ PD17225, 17226, 17227, 17228 and  $\mu$ PD17P228.

The differences among these five models are the program memory and mask option, and their CPU functions and internal hardware are identical. Therefore, the  $\mu$ PD17P228 can be used to evaluate the program developed for the  $\mu$ PD17225, 17226, 17227, and 17228 system. **Note, however, that some of the electrical specifications such as supply current and low-voltage detection voltage of the \muPD17P228 are different from those of the \muPD17225, 17226, 17227, and 17228.**

Table 1-1. Differences among  $\mu$ PD17225, 17226, 17227, 17228 and  $\mu$ PD17P228

| Product Name                                 | μPD17P228                                  | μPD17225                                  | μPD17226                                  | μPD17227                                   | μPD17228                                   |

|----------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|

| Program memory                               | One-time PROM                              |                                           | Mask ROM                                  |                                            |                                            |

|                                              | 16 K bytes<br>(8192 × 16)<br>(0000H-1FFFH) | 4 K bytes<br>(2048 × 16)<br>(0000H-07FFH) | 8 K bytes<br>(4096 × 16)<br>(0000H-0FFFH) | 12 K bytes<br>(6144 × 16)<br>(0000H-17FFH) | 16 K bytes<br>(8192 × 16)<br>(0000H-1FFFH) |

| Data memory                                  | 223 × 4 bits                               | 111 ×                                     | 4 bits                                    | 223 ×                                      | 4 bits                                     |

| Pull-up resistor of RESET Pin                | Provided                                   |                                           | Any (mas                                  | sk option)                                 |                                            |

| Low-voltage detector circuit <sup>Note</sup> | Provided                                   |                                           | Any (mas                                  | sk option)                                 |                                            |

| VPP pin, operation mode select pin           | Provided                                   |                                           | Not pr                                    | ovided                                     |                                            |

| Instruction execution time (tcy)             | 2 μs                                       |                                           | 2 μs (VDD =                               | 2.2 to 3.6 V)                              |                                            |

|                                              | $(V_{DD} = 3.0 \text{ to } 3.6 \text{ V})$ |                                           | 4 $\mu$ s (VDD =                          | 2.0 to 3.6 V)                              |                                            |

|                                              | 4 μs                                       |                                           |                                           |                                            |                                            |

|                                              | $(V_{DD} = 2.2 \text{ to } 3.6 \text{ V})$ |                                           |                                           |                                            |                                            |

|                                              | 16 <i>μ</i> s                              |                                           |                                           |                                            |                                            |

|                                              | $(V_{DD} = 2.2 \text{ to } 3.6 \text{ V})$ |                                           |                                           |                                            |                                            |

| Operation when P0C, P0D are standby          |                                            | Retain output lev                         | el immediately befo                       | re standby mode                            |                                            |

| Supply voltage                               | V <sub>DD</sub> = 2.0 to 3.6 V             |                                           | V <sub>DD</sub> = 2.0                     | ) to 3.6 V                                 |                                            |

| Package                                      | 30-pin plastic<br>SSOP<br>(7.62 mm (300))  | • 28-pin plastic SDIP (10.16 mm (400))    |                                           |                                            |                                            |

Note Although the circuit configuration is identical, its electrical characteristics differ depending on the product.

## 2. PIN FUNCTIONS

## 2.1 Normal Operation Mode

| Pin No.              | Symbol                                                                       | Function                                                                                                                                                                                                                                                                              | Output Format      | At Reset                                                   |

|----------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------|

| 16<br>17<br>18<br>19 | P0A <sub>0</sub><br>P0A <sub>1</sub><br>P0A <sub>2</sub><br>P0A <sub>3</sub> | 4-bit CMOS input port with pull-up resistor.  Can be used for key return input of key matrix. When at least one of these pins goes low, standby function is released.                                                                                                                 | _                  | Input                                                      |

| 20<br>21<br>22<br>23 | P0B <sub>0</sub><br>P0B <sub>1</sub><br>P0B <sub>2</sub><br>P0B <sub>3</sub> | 4-bit CMOS input port with pull-up resistor.  Can be used for key return input of key matrix. When at least one of these pins goes low, standby function is released.                                                                                                                 | -                  | Input                                                      |

| 24<br>25<br>26<br>27 | P0C <sub>0</sub><br>P0C <sub>1</sub><br>P0C <sub>2</sub><br>P0C <sub>3</sub> | 4-bit N-ch open-drain output port.  Can be used for key source output of key matrix.                                                                                                                                                                                                  | N-ch<br>open-drain | Low-level<br>output                                        |

| 28<br>29<br>1<br>2   | P0D <sub>0</sub><br>P0D <sub>1</sub><br>P0D <sub>2</sub><br>P0D <sub>3</sub> | 4-bit N-ch open-drain output port.  Can be used for key source output of key matrix.                                                                                                                                                                                                  | N-ch<br>open-drain | Low-level<br>output                                        |

| 4<br>5<br>6<br>7     | P0E <sub>0</sub><br>P0E <sub>1</sub><br>P0E <sub>2</sub><br>P0E <sub>3</sub> | 4-bit input/output port.  Can be set in input or output mode in 1-bit units.  In output mode, this port functions as a high current CMOS output port. In input mode, function as CMOS input and can be specified to connect pull-up resistor by program.                              | CMOS<br>push-pull  | Input                                                      |

| 8                    | REM                                                                          | Outputs transfer signal for infrared remote controller. Active-high output.                                                                                                                                                                                                           | CMOS<br>push-pull  | Low-level output                                           |

| 13                   | RESET                                                                        | System reset input. CPU can be reset when low-level signal is input to this pin. While low-level signal is input, oscillator is stopped. This pin connected to pull-up resistor by mask option.                                                                                       | -                  | Input                                                      |

| 9                    | V <sub>DD</sub>                                                              | Power supply                                                                                                                                                                                                                                                                          | _                  | _                                                          |

| 12                   | GND                                                                          | Ground                                                                                                                                                                                                                                                                                | _                  | -                                                          |

| 3                    | INT                                                                          | External interrupt request signal input                                                                                                                                                                                                                                               | -                  | Input                                                      |

| 14                   | WDOUT                                                                        | Output detecting hang-up and drop in supply voltage. This pin outputs at low level either when an overflow occurs in the watchdog timer, when an overflow/underflow occurs in the stack, or when the supply voltage drops below a specified level. Connect this pin to the RESET pin. | N-ch<br>open-drain | High- impedance  Low-level output at low voltage detection |

| 11<br>10             | XIN<br>Xout                                                                  | Connects ceramic resonator for system clock oscillation                                                                                                                                                                                                                               | -                  | (Oscillation stops)                                        |

| 15<br>30             | IC1<br>IC2                                                                   | These pins cannot be used. Leave open.                                                                                                                                                                                                                                                | _                  | -                                                          |

## 2.2 PROM Programming Mode

| Pin No.                        | Symbol                                | Function                                                                                                                     | Output Format     | At Reset |

|--------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|

| 3                              | Vpp                                   | Power supply for PROM programming.  Apply +12.5 V to this pin as the program voltage when writing/ verifying program memory. | -                 | -        |

| 9                              | VDD                                   | Power supply. Apply +6 V to this pin when writing/verifying program memory.                                                  | -                 | _        |

| 11                             | CLK                                   | Inputs clock for PROM programming.                                                                                           | -                 | -        |

| 12                             | GND                                   | Ground.                                                                                                                      | -                 | -        |

| 20<br> <br>23                  | MD₀<br> <br>MD₃                       | Input pins used to select operation mode when PROM is programmed.                                                            | -                 | Input    |

| 24<br> <br>27<br>28<br>29<br>1 | D4<br> <br>D7<br>D0<br>D1<br>D2<br>D3 | Input/output 8-bit data for PROM programming                                                                                 | CMOS<br>push-pull | Input    |

**Remark** The other pins are not used in the PROM programming mode. How to handle the other opins are described in the section **PIN CONFIGURATION (2) PROM programming mode**.

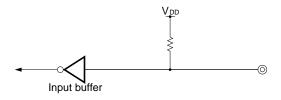

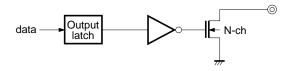

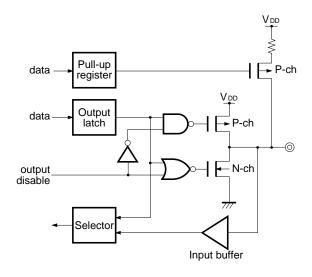

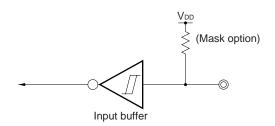

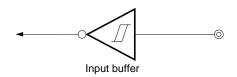

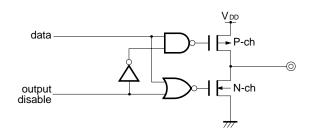

## 2.3 Input/Output Circuits

The equivalent input/output circuit for each  $\mu$ PD17P228 pin is shown below.

## (1) P0A, P0B

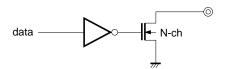

## (2) POC, POD

## (3) P0E

## (4) RESET

Schmitt trigger input with hysteresis characteristics

## (5) INT

Schmitt trigger input with hysteresis characteristics

## (6) REM

## (7) WDOUT

## 2.4 Processing of Unused Pins

Process the unused pins as follows:

Table 2-1. Processing of Unused Pins

| Pin                                | Recommended Connection                                                        |

|------------------------------------|-------------------------------------------------------------------------------|

| P0A <sub>0</sub> -P0A <sub>3</sub> | Connect to V <sub>DD</sub> .                                                  |

| P0B <sub>0</sub> -P0B <sub>3</sub> | Connect to V <sub>DD</sub> .                                                  |

| P0C <sub>0</sub> -P0C <sub>3</sub> | Connect to GND.                                                               |

| P0D <sub>0</sub> -P0D <sub>3</sub> | Connect to GND.                                                               |

| P0E <sub>0</sub> -P0E <sub>3</sub> | Input : Individually connect to VDD or GND via resistor. Output : Leave open. |

| REM                                | Leave open.                                                                   |

| INT                                | Connect to GND.                                                               |

| WDOUT                              | Connect to V <sub>DD</sub> via resistor.                                      |

| IC1, IC2                           | These pins cannot be used.<br>Leave open.                                     |

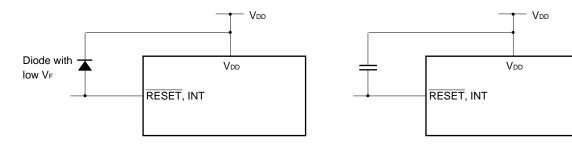

## 2.5 Notes on Using the RESET and INT Pins

In addition to the functions shown in **2. PIN FUNCTION**, the  $\overline{\text{RESET}}$  pin also has the function of setting a test mode (for IC testing) in which the internal operations of the  $\mu\text{PD17P228}$  are tested.

When a voltage higher than  $V_{DD}$  is applied to either of these pins, the test mode is set. This means that, even during normal operation, the  $\mu$ PD17P228 may be set in the test mode if noise exceeding  $V_{DD}$  is applied.

For example, if the wiring length of the RESET or INT pin is too long, noise superimposed on the wiring line of the pin may cause the above problem.

Therefore, keep the wiring length of these pins as short as possible to suppress the noise; otherwise, take noise preventive measures as shown below by using external components.

## Connect diode with low V<sub>F</sub> between V<sub>DD</sub> and RESET/INT pin

• Connect capacitor between VDD and RESET/INT pin

Connect the WDOUT and RESET pins since a low level is output after the test mode is set using the INT pin.

## 3. WRITING AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)

The program memory of the  $\mu PD17P228$  is a one-time PROM of 8192  $\times$  16 bits.

To write or verify this one-time PROM, the pins shown in Table 3-1 are used. Note that no address input pin is used. Instead, the address is updated by using the clock input from the CLK pin.

Table 3-1. Pins Used to Write/Verify Program Memory

| Pin Name                         | Function                                                                        |

|----------------------------------|---------------------------------------------------------------------------------|

| VPP                              | Supplies voltage when writing/verifying program memory.                         |

|                                  | Apply +12.5 V to this pin.                                                      |

| V <sub>DD</sub>                  | Power supply.                                                                   |

|                                  | Supply +6 V to this pin when writing/verifying program memory.                  |

| CLK                              | Inputs clock to update address when writing/verifying program memory.           |

|                                  | By inputting pulse four times to CLK pin, address of program memory is updated. |

| MD <sub>0</sub> -MD <sub>3</sub> | Input to select operation mode when writing/verifying program memory.           |

| D <sub>0</sub> -D <sub>7</sub>   | Inputs/outputs 8-bit data when writing/verifying program memory.                |

## 3.1 Operating Mode When Writing/Verifying Program Memory

The  $\mu$ PD17P228 is set in the program memory write/verify mode when +6 V is applied to the V<sub>DD</sub> pin and +12.5 V is applied to the V<sub>PP</sub> pin after the  $\mu$ PD17P228 has been in the reset status (V<sub>DD</sub> = 5 V,  $\overline{RESET}$  = 0 V) for a specific time. In this mode, the operating modes shown in Table 3-2 can be set by setting the MD<sub>0</sub> through MD<sub>3</sub> pins. Leave all the pins other than those shown in Table 3-1 unconnected or connect them to GND via pull-down resistor (470  $\Omega$ ). (Refer to **PIN CONNECTION (2) PROM programming mode.)**

**Table 3-2. Setting Operation Mode**

|          |                 | Setting of Op | erating Mode    | Setting of Operating Mode |                 |                                     |  |  |  |  |

|----------|-----------------|---------------|-----------------|---------------------------|-----------------|-------------------------------------|--|--|--|--|

| $V_{PP}$ | V <sub>DD</sub> | MD₀           | MD <sub>1</sub> | MD <sub>2</sub>           | MD <sub>3</sub> |                                     |  |  |  |  |

| +12.5 V  | +6 V            | Н             | L               | Н                         | L               | Program memory address 0 clear mode |  |  |  |  |

|          |                 | L             | Н               | Н                         | Н               | Write mode                          |  |  |  |  |

|          |                 | L             | L               | Н                         | Н               | Verify mode                         |  |  |  |  |

|          |                 | Н             | ×               | Н                         | Н               | Program inhibit mode                |  |  |  |  |

x: don't care (L or H)

Data Sheet U14542EJ1V0DS00 11

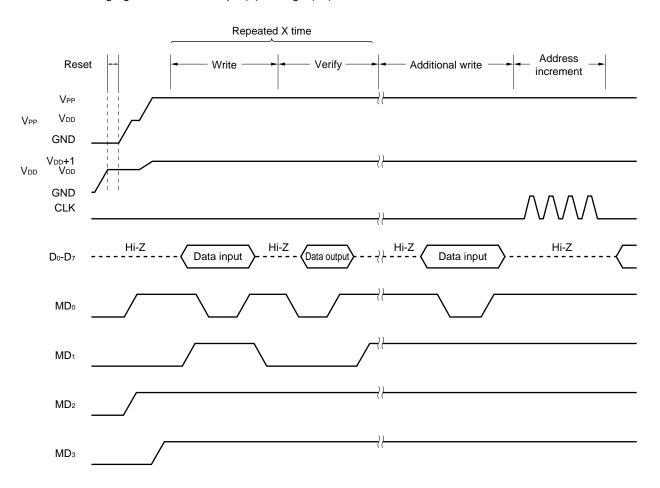

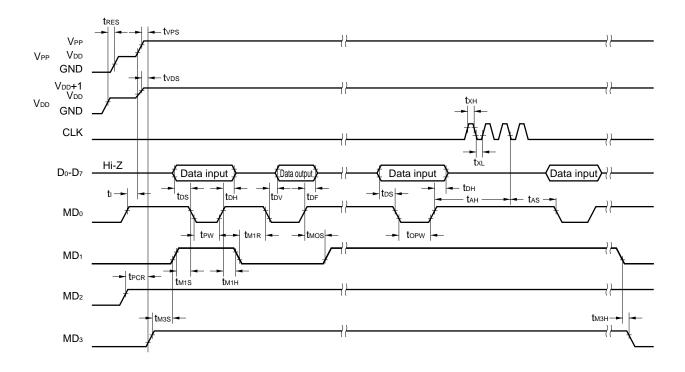

## 3.2 Program Memory Writing Procedure

The program memory is written at high speed in the following procedure.

- (1) Pull down the pins not used to GND via resistor. Keep the CLK pin low.

- (2) Supply 5 V to the VDD pin. Keep the VPP pin low.

- (3) Supply 5 V to the VPP pin after waiting for 10  $\mu$ s.

- (4) Set the program memory address 0 clear mode by using the mode setting pins.

- (5) Supply +6 V to VDD and +12.5 V to VPP.

- (6) Set the program inhibit mode.

- (7) Write data to the program memory in the 1-ms write mode.

- (8) Set the program inhibit mode.

- (9) Set the verify mode. If the data have been written to the program memory, proceed to (10). If not, repeat steps (7) through (9).

- (10) Additional writing of (number of times of writing in (7) through (9):  $X \times 1$  ms.

- (11) Set the program inhibit mode.

- (12) Input a pulse to the CLK pin four times to update the program memory address (+1).

- (13) Repeat steps (7) through (12) up to the last address.

- (14) Set the 0 clear mode of the program memory address.

- (15) Change the voltages on the VDD and VPP pins to 5 V.

- (16) Turn off power.

The following figure illustrates steps (2) through (12) above.

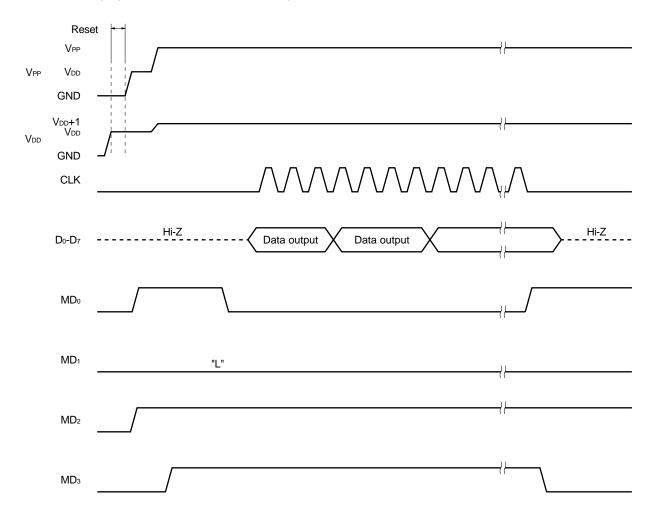

## 3.3 Program Memory Reading Procedure

- (1) Pull down the pins not used to GND via resistor. Keep the CLK pin low.

- (2) Supply 5 V to the VDD pin. Keep the VPP pin low.

- (3) Supply 5 V to the VPP pin after waiting for 10  $\mu$ s.

- (4) Set the program memory address 0 clear mode by using the mode setting pins.

- (5) Supply +6 V to VDD and +12.5 V to VPP.

- (6) Set the program inhibit mode.

- (7) Set the verify mode. Data of each address is output sequentially each time the clock pulse is input to the CLK pin four times.

- (8) Set the program inhibit mode.

- (9) Set the program memory address 0 clear mode.

- (10) Change the voltage on the VDD and VPP pins to 5 V.

- (11) Turn off power.

The following figure illustrates steps (2) through (9) above.

## 4. ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings ( $T_A = 25^{\circ}C$ )

| Item                                      | Symbol          |                       |            | Ratings                                                                                                             | Unit |

|-------------------------------------------|-----------------|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------|------|

| Supply voltage                            | V <sub>DD</sub> |                       |            | -0.3 to +7.0                                                                                                        | V    |

| PROM power supply                         | VPP             |                       |            | -0.3 to +13.5                                                                                                       | V    |

| Input voltage                             | Vı              |                       |            | -0.3 to V <sub>DD</sub> + 0.3                                                                                       | V    |

| Output voltage                            | Vo              |                       |            | -0.3 to V <sub>DD</sub> + 0.3                                                                                       | V    |

| High-level output current <sup>Note</sup> | Іон             | REM pin               | Peak value | -36.0                                                                                                               | mA   |

|                                           |                 |                       | rms value  | -24.0                                                                                                               | mA   |

|                                           |                 | 1 pin (P0E pin)       | Peak value | -7.5                                                                                                                | mA   |

|                                           |                 |                       | rms value  | -5.0                                                                                                                | mA   |

|                                           |                 | Total of P0E pins     | Peak value | -22.5                                                                                                               | mA   |

|                                           |                 |                       | rms value  | -15.0                                                                                                               | mA   |

| Low-level output current Note             | lol             | 1 pin (P0C, P0D, P0E, | Peak value | 7.5                                                                                                                 | mA   |

|                                           |                 | REM or WDOUT pin)     | rms value  | -0.3 to +13.5  -0.3 to V <sub>DD</sub> + 0.3  -0.3 to V <sub>DD</sub> + 0.3  -36.0  -24.0  -7.5  -5.0  -22.5  -15.0 | mA   |

|                                           |                 | Total of P0C, P0D,    | Peak value | 22.5                                                                                                                | mA   |

|                                           |                 | WDOUT pins            | rms value  | 15.0                                                                                                                | mA   |

|                                           |                 | Total of P0E pins     | Peak value | 30.0                                                                                                                | mA   |

|                                           |                 |                       | rms value  | 20.0                                                                                                                | mA   |

| Operating temperature                     | TA              |                       | •          | -40 to +85                                                                                                          | °C   |

| Storage temperature                       | Tstg            |                       |            | -65 to +150                                                                                                         | °C   |

| Power dissipation                         | Pd              | T <sub>A</sub> = 85°C |            | 180                                                                                                                 | mW   |

**Note** Calculate rms value by this expression: [rms value] = [Peak value]  $\times \sqrt{\text{Duty}}$

Caution Even if one of the parameters exceeds its absolute maximum rating even momentarily, the quality of the product may be degraded. The absolute maximum rating therefore specifies the upper or lower limit of the value at which the product can be used without physical damages. Be sure not to exceed or fall below this value when using the product.

## Recommended Operating Ranges (TA = -40 to +85°C, VDD = 2.2 to 3.6 V)

| Item                                         | Symbol           |            | Conditions                                               | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------|------------------|------------|----------------------------------------------------------|------|------|------|------|

| Supply voltage                               | V <sub>DD1</sub> | fx = 1 MHz | High-speed mode (Instruction execution time: 16 $\mu$ s) | 2.2  |      | 3.6  | V    |

|                                              | V <sub>DD2</sub> | fx = 4 MHz | Ordinary mode (Instruction execution time: 4 $\mu$ s)    |      |      |      |      |

|                                              | VDD3             | fx = 8 MHz | High-speed mode (Instruction execution time: 4 $\mu$ s)  |      |      |      |      |

|                                              | V <sub>DD4</sub> |            | High-speed mode (Instruction execution time: 2 $\mu$ s)  | 3.0  |      | 3.6  | V    |

| Oscillation frequency                        | fx               |            |                                                          | 1.0  | 4.0  | 8.0  | MHz  |

| Operating temperature                        | TA               |            |                                                          | -40  | +25  | +85  | °C   |

| Low-voltage detector circuit <sup>Note</sup> | Тсч              |            |                                                          | 4    |      | 32   | μs   |

**Note** Reset if the status of  $V_{DD} = 2.05 \text{ V}$  (TYP.) lasts for 1 ms or longer. Program hang-up does not occur even if the voltage drops, until the reset function is effected (when the  $\overline{RESET}$  pin and  $\overline{WDOUT}$  pin are connected). Some oscillators stop oscillating before the reset function is effected.

**Remark** The region indicated by the broken line in the above figure is the guaranteed operating range in the high-speed mode.

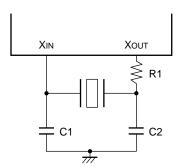

## System Clock Oscillator Characteristics (TA = -40 to +85°C, VDD = 2.2 to 3.6 V)

| Resonator         | Recommended<br>Constants         | Item                                                | Conditions                                                      | MIN. | TYP. | MAX. | Unit |

|-------------------|----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| Ceramic resonator | X <sub>IN</sub> X <sub>OUT</sub> | Oscillation frequency (fx) <sup>Note 1</sup>        |                                                                 | 1.0  | 4.0  | 8.0  | MHz  |

|                   |                                  | Oscillation<br>stabilization time <sup>Note 2</sup> | After V <sub>DD</sub> reached MIN. in oscillation voltage range |      |      | 4    | ms   |

- **Notes 1.** The oscillation frequency only indicates the oscillator characteristics.

- 2. The oscillation stabilization time is necessary for oscillation to be stabilized, after VDD application or STOP mode release.

Caution To use a system clock oscillator circuit, perform the wiring in the area enclosed by the dotted line in the above figure as follows, to avoid adverse wiring capacitance influences:

- · Keep wiring length as short as possible.

- Do not cross a signal line with some other signal lines. Do not route the wiring in the vicinity of lines through which a large current flows.

- Always keep the oscillator capacitor ground at the same potential as GND. Do not ground the capacitor to a ground pattern, through which a large current flows.

- Do not extract signals from the oscillator.

## External circuit example

**Remark** To select a resonator and determine oscillator constants, please evaluate the oscillation yourself or request the resonator manufacturer to evaluate it.

## DC Characteristics (T<sub>A</sub> = -40 to +85°C, V<sub>DD</sub> = 2.2 to 3.6 V)

| Item                              | Symbol            |                           | Conditions                        |                        | MIN.               | TYP. | MAX.               | Unit |

|-----------------------------------|-------------------|---------------------------|-----------------------------------|------------------------|--------------------|------|--------------------|------|

| High-level input voltage          | V <sub>IH1</sub>  | RESET, INT                |                                   |                        | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | V    |

|                                   | V <sub>IH2</sub>  | P0A, P0B                  |                                   |                        | 0.7VDD             |      | V <sub>DD</sub>    | V    |

|                                   | VIH3              | P0E                       |                                   |                        | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | V    |

| Low-level input voltage           | VIL1              | RESET, INT                |                                   |                        | 0                  |      | 0.2V <sub>DD</sub> | V    |

|                                   | VIL2              | P0A, P0B                  |                                   |                        | 0                  |      | 0.3VDD             | V    |

|                                   | VIL3              | P0E                       |                                   |                        | 0                  |      | 0.35Vpd            | V    |

| High-level input leakage current  | Ішн               | P0A, P0B, P0E, RESET, INT | VIH = VDD                         |                        |                    |      | 3                  | μΑ   |

| Low-level input leakage           | ILIL1             | INT                       | VIL = 0 V                         |                        |                    |      | -3                 | μΑ   |

| current                           | ILIL2             | P0E                       | VIL = 0 V w/o pull-               | up resistor            |                    |      | -3                 | μΑ   |

| High-level output leakage current | Ісон              | POC, POD, POE, WDOUT      | Voh = Vdd                         |                        |                    |      | 3                  | μΑ   |

| Low-level output leakage current  | ILOL              | P0E, WDOUT                | Vol = 0 V w/o pul                 | I-up resistor          |                    |      | -3                 | μΑ   |

| Internal pull-up resistor         | R <sub>1</sub>    | P0E, RESET                |                                   |                        | 25                 | 50   | 100                | kΩ   |

|                                   | R <sub>2</sub>    | P0A, P0B                  |                                   |                        | 100                | 200  | 400                | kΩ   |

| High-level output current         | Іон1              | REM                       | Vон = 1.0 V, VDD =                | 3 V                    | -6                 | -13  | -24                | mA   |

| High-level output voltage         | Vон               | P0E, REM                  | Iон = −0.5 mA                     |                        | VDD-0.3            |      | V <sub>DD</sub>    | V    |

| Low-level output voltage          | V <sub>OL1</sub>  | POC, POD, REM, WDOUT      | IoL = 0.5 mA                      |                        | 0                  |      | 0.3                | V    |

|                                   | V <sub>OL2</sub>  | P0E                       | IoL = 1.5 mA                      |                        | 0                  |      | 0.3                | V    |

| Low-voltage detector circuit      | VDT               | WDOUT = low level         | V <sub>DT</sub> = V <sub>DD</sub> |                        |                    | 2.05 | 2.2                | V    |

| Data retention voltage            | V <sub>DDDR</sub> | RESET = low leve          | el or STOP mode                   |                        | 1.3                |      | 3.6                | V    |

| Supply current                    | I <sub>DD1</sub>  | Operating mode            | V <sub>DD</sub> = 3 V ± 10%       | fx = 1 MHz             |                    | 0.55 | 1.1                | mA   |

|                                   |                   | (high-speed)              |                                   | fx = 4 MHz             |                    | 1.0  | 2.0                | mA   |

|                                   |                   |                           |                                   | fx = 8 MHz             |                    | 1.3  | 2.6                | mA   |

|                                   | I <sub>DD2</sub>  | Operating mode            | V <sub>DD</sub> = 3 V ± 10%       | fx = 1 MHz             |                    | 0.5  | 1.0                | mA   |

|                                   |                   | (low-speed)               |                                   | fx = 4 MHz             |                    | 0.75 | 1.5                | mA   |

|                                   |                   |                           |                                   | fx = 8 MHz             |                    | 0.9  | 1.8                | mA   |

|                                   | IDD3              | HALT mode                 | V <sub>DD</sub> = 3 V ± 10%       | fx = 1 MHz             |                    | 0.4  | 0.8                | mA   |

|                                   |                   |                           |                                   | fx = 4 MHz             |                    | 0.5  | 1.0                | mA   |

|                                   |                   |                           |                                   | fx = 8 MHz             |                    | 0.6  | 1.2                | mA   |

|                                   | I <sub>DD4</sub>  | STOP mode                 | V <sub>DD</sub> = 3 V ± 10%       |                        |                    | 2.0  | 20.0               | μΑ   |

|                                   |                   |                           | built-in POC                      | T <sub>A</sub> = 25 °C |                    | 2.0  | 5.0                | μΑ   |

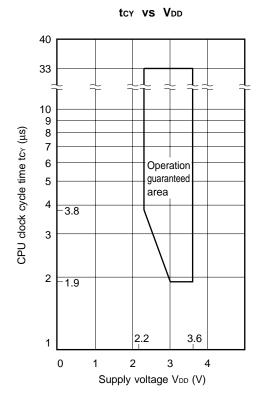

## AC Characteristics (T<sub>A</sub> = -40 to +85°C, V<sub>DD</sub> = 2.2 to 3.6 V)

| Item                                                              | Symbol           | Conditions                     | MIN. | TYP. | MAX. | Unit |

|-------------------------------------------------------------------|------------------|--------------------------------|------|------|------|------|

| CPU clock cycle time <sup>Note</sup> (instruction execution time) | t <sub>CY1</sub> |                                | 3.8  |      | 33   | μs   |

|                                                                   | tcy2             | V <sub>DD</sub> = 3.0 to 3.6 V | 1.9  |      | 33   | μs   |

| INT high/low level width                                          | tinth, tintl     |                                | 20   |      |      | μs   |

| RESET low level lwidth                                            | trsl             |                                | 10   |      |      | μs   |

**Note** The CPU clock cycle time (instruction execution time) is determined by the oscillation frequency of the resonator connected and SYSCK (RF: address 02H) of the register file.

The figure on the right shows the CPU clock cycle time  $t_{\text{CY}}$  vs. supply voltage  $V_{\text{DD}}$  characteristics.

## DC Programming Characteristics (T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 6.0 $\pm$ 0.25 V, V<sub>PP</sub> = 12.5 $\pm$ 0.3 V)

| Parameter                      | Symbol           | Test Conditions      | MIN.                 | TYP. | MAX.            | Unit |

|--------------------------------|------------------|----------------------|----------------------|------|-----------------|------|

| High-level input voltage       | V <sub>IH1</sub> | Other than CLK       | 0.7 Vdd              |      | V <sub>DD</sub> | V    |

|                                | V <sub>IH2</sub> | CLK                  | V <sub>DD</sub> -0.5 |      | V <sub>DD</sub> | V    |

| Low-level input voltage        | V <sub>IL1</sub> | Other than CLK       | 0                    |      | 0.3 VDD         | V    |

|                                | V <sub>IL2</sub> | CLK                  | 0                    |      | 0.4             | V    |

| Input leakage current          | lu               | VIN = VIL OF VIH     |                      |      | 10              | μΑ   |

| High-level output voltage      | Vон              | Iон = −1 mA          | V <sub>DD</sub> -1.0 |      |                 | V    |

| Low-level output voltage       | Vol              | IoL = 1.6 mA         |                      |      | 0.4             | V    |

| V <sub>DD</sub> supply current | IDD              |                      |                      |      | 30              | mA   |

| VPP supply current             | IPP              | MD0 = VIL, MD1 = VIH |                      |      | 30              | mA   |

Cautions 1. Keep VPP to within +13.5 V including overshoot.

2. Apply VDD before VPP and turns it off after VPP.

## AC Programming Characteristics (TA = 25°C, VDD = 6.0 $\pm$ 0.25 V, VPP = 12.5 $\pm$ 0.3 V)

| Parameter                                                 | Symbol            | Test Conditions             | MIN.  | TYP. | MAX. | Unit |

|-----------------------------------------------------------|-------------------|-----------------------------|-------|------|------|------|

| Address setup time <sup>Note</sup> (vs. MD₀↓)             | tas               |                             | 2     |      |      | μs   |

| MD₁ setup time (vs. MD₀↓)                                 | t <sub>M1S</sub>  |                             | 2     |      |      | μs   |

| Data setup time (vs. MD₀↓)                                | tos               |                             | 2     |      |      | μs   |

| Address hold time <sup>Note</sup> (vs. MD <sub>0</sub> ↑) | <b>t</b> AH       |                             | 2     |      |      | μs   |

| Data hold time (vs. MD <sub>0</sub> ↑)                    | tон               |                             | 2     |      |      | μs   |

| MD <sub>0</sub> ↑→ data output float delay time           | tor               |                             | 0     |      | 130  | ns   |

| V <sub>PP</sub> setup time (vs. MD₃↑)                     | tvps              |                             | 2     |      |      | μs   |

| V <sub>DD</sub> setup time (vs. MD₃↑)                     | tvds              |                             | 2     |      |      | μs   |

| Initial program pulse width                               | tpw               |                             | 0.95  | 1.0  | 1.05 | ms   |

| Additional program pulse width                            | topw              |                             | 0.95  |      | 21.0 | ms   |

| MD₀ setup time (vs. MD₁↑)                                 | tмos              |                             | 2     |      |      | μs   |

| MD₀↓→ data output delay time                              | <b>t</b> DV       | MD0 = MD1 = VIL             |       |      | 1    | μs   |

| MD₁ hold time (vs. MD₀↑)                                  | <b>t</b> м1н      | tм1H+tм1R ≥ 50 μs           | 2     |      |      | μs   |

| MD₁ recovery time (vs. MD₀↓)                              | <b>t</b> M1R      |                             | 2     |      |      | μs   |

| Program counter reset time                                | <b>t</b> PCR      |                             | 10    |      |      | μs   |

| CLK input high-, low-level width                          | txH, txL          |                             | 0.125 |      |      | μs   |

| CLK input frequency                                       | fx                |                             |       |      | 4.19 | MHz  |

| Initial mode set time                                     | tı                |                             | 2     |      |      | μs   |

| MD₃ setup time (vs. MD₁↑)                                 | tмзs              |                             | 2     |      |      | μs   |

| MD₃ hold time (vs. MD₁↓)                                  | tмзн              |                             | 2     |      |      | μs   |

| MD₃ setup time (vs. MD₀↓)                                 | t <sub>M3SR</sub> | When program memory is read | 2     |      |      | μs   |

| Address <sup>Note</sup> → data output delay time          | <b>t</b> DAD      | When program memory is read |       |      | 2    | μs   |

| Address <sup>Note</sup> → data output hold time           | <b>t</b> HAD      | When program memory is read | 0     |      | 130  | ns   |

| MD₃ hold time (vs. MD₀↑)                                  | tмзнк             | When program memory is read | 2     |      |      | μs   |

| MD₃↓→ data output float delay time                        | tdfr              | When program memory is read |       |      | 2    | μs   |

| Reset setup time                                          | tres              |                             | 10    |      |      | μs   |

**Notes** The internal address increment (+1) is performed on the fall of the 3rd clock, where 4 clocks compreise one cycle. The internal clock is not connected to a pin.

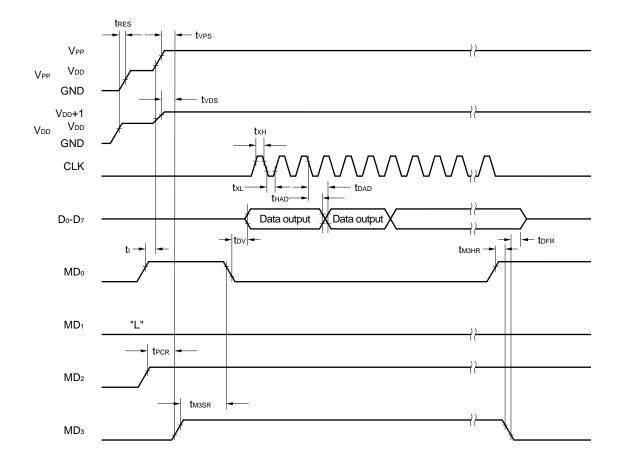

## **Program Memory Write Timing**

## **Program Memory Read Timing**

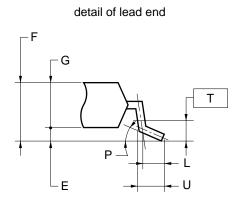

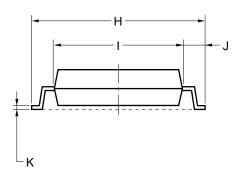

## 5. PACKAGE DRAWING

## 30-PIN PLASTIC SSOP (7.62 mm (300))

## NOTE

Each lead centerline is located within 0.13 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            |

|------|------------------------|

| Α    | 9.85±0.15              |

| В    | 0.45 MAX.              |

| С    | 0.65 (T.P.)            |

| D    | $0.24^{+0.08}_{-0.07}$ |

| Е    | 0.1±0.05               |

| F    | 1.3±0.1                |

| G    | 1.2                    |

| Н    | 8.1±0.2                |

| I    | 6.1±0.2                |

| J    | 1.0±0.2                |

| K    | 0.17±0.03              |

| L    | 0.5                    |

| М    | 0.13                   |

| N    | 0.10                   |

| Р    | 3°+5°                  |

| Т    | 0.25                   |

| U    | 0.6±0.15               |

|      |                        |

S30MC-65-5A4-2

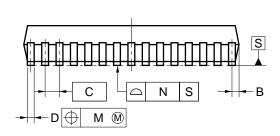

## 6. RECOMMENDED SOLDERING CONDITIONS

For the  $\mu$ PD17P228 soldering must be performed under the following conditions.

For details of recommended conditions for surface mounting, refer to information document "Semiconductor Device Mounting Technology Manual" (C10535E).

For other soldering methods, please consult with NEC personnel.

Table 6-1. Soldering Conditions of Surface Mount Type

## • μPD17P228MC-5A4: 30-pin plastic SSOP (7.62 mm(300))

| Soldering Method | Soldering Conditions                                                                                                                                                                                                             | Symbol      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Infrated Reflow  | Package peak temperature: 235°C, Time: 30 seconds max. (210°C min.), Number of times: 2 max. Number of days: 3 (after that, prebaking is necessary at 125°C for 10 hours)                                                        | IR35-103-2  |

| VPS              | Package peak temperature: 215°C, Time: 40 seconds max. (200°C min.),<br>Number of times: 2 max. Number of days: 3 (after that, prebaking is necessary<br>at 125°C for 10 hours)                                                  | VP15-103-2  |

| Wave soldering   | Solder bath temperature: 260°C max, Time: 10 seconds max., Number of times: once, preheating temperature: 120°C max. (package surface temperature)  Number of days: 3 (after that, prebaking is necessary at 125°C for 10 hours) | WS-60-103-1 |

| Partial heating  | Pin temperature: 300°C max., Time: 3 seconds max. (per side of device)                                                                                                                                                           | _           |

**Note** Number of days in storage after the dry pack has been opened. The storage conditions are at 25°C, 65% RH MAX.

Caution Do not use two or more soldering methods in combination (except the partial heating method).

## APPENDIX. DEVELOPMENT TOOLS

To develop the programs for the  $\mu$ PD17P228 subseries, the following development tools are available:

## Hardware

| Name                                                                                                       | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-circuit emulator (IE-17K, IE-17K-ETNote 1)                                                              | IE-17K and IE-17K-ET are the in-circuit emulators used in common with the 17K series microcontroller.  IE-17K and IE-17K-ET are connected to a PC-9800 series or IBM PC/AT <sup>TM</sup> compatible machines as the host machine with RS-232C.  By using these in-circuit emulators with a system evaluation board corresponding to the microcomputer, the emulators can emulate the microcomputer. A higher level debugging environment can be provided by using man-machine interface SIMPLEHOST <sup>TM</sup> . |

| SE board<br>(SE-17225)                                                                                     | This is an SE board for $\mu$ PD17225 subseries. It can be used alone to evaluate a system or in combination with an in-circuit emulator for debugging.                                                                                                                                                                                                                                                                                                                                                            |

| Emulation probe<br>(EP-17K30GS)                                                                            | EP-17K30GS is an emulation probe for 17K series 30-pin SSOP (MC-5A4). When used with EV-9500GT-30 <sup>Note 2</sup> , it connects an SE board to the target system.                                                                                                                                                                                                                                                                                                                                                |

| Conversion adapter (EV-9500GT-30 <sup>Note 2</sup> )                                                       | The EV-9500GT-30 is a conversion adapter for the 30-pin SSOP (MC-5A4). It is used to connect the EP-17K30GS and target system.                                                                                                                                                                                                                                                                                                                                                                                     |

| PROM programmer<br>(AF-9706 <sup>Note 3</sup> , AF-9708 <sup>Note 3</sup> ,<br>AF-9709 <sup>Note 3</sup> ) | AF-9706, AF-9708, and AF-9709 are PROM programmers corresponding to $\mu$ PD17P228. By connecting program adapter PA-17P236 to this PROM programmer, $\mu$ PD17P228 can be programmed.                                                                                                                                                                                                                                                                                                                             |

| Program adapter (PA-17P236)                                                                                | PA-17P236 are adapters that is used to program $\mu$ PD17P228, and is used in combination with AF-9706, AF-9708, or AF-9709.                                                                                                                                                                                                                                                                                                                                                                                       |

Notes 1. Low-cost model: External power supply type

- 2. Two EV-9500GT-30 are supplied with the EP-17K30GS. Five EV-9500GT-30s are optionally available as a set.

- **3.** These are products from Ando Electric Co., Ltd. For details, consult Ando Electric Co., Ltd. (Tel: 03-3733-1166).

## Software

| Name                     | Outline                                                                                                                                                                | Host Machine         | os                             | Supply   | Order Code    |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------|----------|---------------|

| 17K assembler<br>(RA17K) | The RA17K is an assembler common to the 17K series products. When developing the program of devices, RA17K is used in combination with a device file (AS17225).        | PC-9800<br>series    | Japanese Windows <sup>TM</sup> | 3.5" 2HD | μSAA13RA17K   |

|                          |                                                                                                                                                                        | IBM PC/AT compatible | Japanese Windows               | 3.5" 2HC | μSAB13RA17K   |

|                          |                                                                                                                                                                        | machine              | English Windows                |          | μSBB13RA17K   |

| Device file<br>(AS17225) | The AS17225 is a device file for $\mu$ PD17225, 17226, 17227, and 17228 and is used in combination with an assembler for the 17K series (RA17K).                       | PC-9800<br>series    | Japanese Windows               | 3.5" 2HD | μSAA13AS17225 |

|                          |                                                                                                                                                                        | IDIVI PC/AT          | Japanese Windows               | 3.5" 2HC | μSAB13AS17225 |

|                          |                                                                                                                                                                        |                      | English Windows                |          | μSBB13AS17225 |

| Support<br>software      | SIMPLEHOST is a software package that enables man-machine interface on the Windows when a program is developed by using an incircuit emulator and a personal computer. | PC-9800<br>series    | Japanese Windows               | 3.5" 2HD | μSAA13ID17K   |

| (SIMPLEHOST)             |                                                                                                                                                                        | IBM PC/AT compatible | Japanese Windows               | 3.5" 2HC | μSAB13ID17K   |

|                          |                                                                                                                                                                        | machine              | English Windows                |          | μSBB13ID17K   |

#### NOTES FOR CMOS DEVICES -

## 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

## **③ STATUS BEFORE INITIALIZATION OF MOS DEVICES**

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

## **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

## **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

## **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

## NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

## **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

## **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

## **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

## **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

## **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

## **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

## **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130 Tel: 65-253-8311 Fax: 65-250-3583

## **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

## NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil

Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J99.1

[MEMO]

SIMPLEHOST is a trademark of NEC Corporation.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of IBM Corporation.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from use of a device described herein or any other liability arising

from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights

or other intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

- "Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots