# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# HD49338F/HF

# CDS/PGA & 12-bit A/D Converter

REJ03F0107-0200 Rev.2.00 May 20, 2005

# **Description**

The HD49338F/HF is a CMOS IC that provides CDS-PGA analog processing (CDS/PGA) suitable for CCD camera digital signal processing systems together with a 12-bit A/D converter in a single chip.

### **Functions**

Correlated double sampling

**PGA**

Offset compensation

Serial interface control

12-bit ADC

Operates using only the 3 V voltage

Corresponds to switching mode of power dissipation and operating frequency

Power dissipation: 150 mW (Typ), maximum frequency: 36 MHz Power dissipation: 100 mW (Typ), maximum frequency: 25 MHz

ADC direct input mode Y-IN direct input mode QFP 48-pin package

#### **Features**

Suppresses low-frequency noise output from CCD by the S/H type correlated double sampling.

The S/H response frequency characteristics for the reference level can be adjusted using values of external parts and registers.

High sensitivity is achieved due to the high S/N ratio and a wide coverage provided by a PG amplifier.

Feedback is used to compensate and reduce the DC offsets including the output DC offset due to PGA gain change and the CCD offset in the CDS (correlated double sampling) amplifier input.

PGA, standby mode, etc., is achieved via a serial interface.

High precision is provided by a 12-bit-resolution A/D converter.

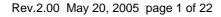

# **Pin Arrangement**

# **Pin Description**

| Pin No. | Symbol             | Description                           | I/O | Analog(A) or<br>Digital(D) |

|---------|--------------------|---------------------------------------|-----|----------------------------|

| 1       | D0                 | Digital output (LSB)                  | 0   | D                          |

| 2 to 11 | D1 to D10          | Digital output                        | 0   | D                          |

| 12      | D11                | Digital output (MSB)                  | 0   | D                          |

| 13      | DRDV <sub>DD</sub> | Output buffer power supply (3 V)      | _   | D                          |

| 14      | DVss               | Digital ground (0 V)                  | _   | D                          |

| 15      | DV <sub>SS</sub>   | Digital ground (0 V)                  | _   | D                          |

| 16      | ADCLK              | ADC conversion clock input pin        | ı   | D                          |

| 17      | $DV_DD$            | Digital power supply (3 V)            | _   | D                          |

| 18      | $DV_DD$            | Digital power supply (3 V)            | _   | D                          |

| 19      | PBLK               | Preblanking input pin                 | I   | D                          |

| 20      | OBP                | Optical black pulse input pin         | ı   | D                          |

| 21      | SPBLK              | Black level sampling clock input pin  | I   | D                          |

| 22      | SPSIG              | Signal level sampling clock input pin | ı   | D                          |

| 23      | NC                 | No connection pin                     | _   | _                          |

| 24      | $DV_DD$            | Output power supply (3 V)             | _   | D                          |

| 25      | $AV_{SS}$          | Analog ground (0 V)                   | _   | Α                          |

| 26      | AV <sub>SS</sub>   | Analog ground (0 V)                   | _   | Α                          |

| 27      | $AV_{DD}$          | Analog power supply (3 V)             | _   | A                          |

| 28      | BLKSH              | Black level S/H pin                   | _   | A                          |

| 29      | BLKFB              | Black level FB pin                    | _   | A                          |

| 30      | CDSIN              | CDS input pin                         | 1   | A                          |

| 31      | BLKC               | Black level C pin                     | _   | A                          |

# Pin Description (cont.)

| Pin No. | Symbol           | Description                                                                | I/O | Analog(A) or<br>Digital(D) |

|---------|------------------|----------------------------------------------------------------------------|-----|----------------------------|

| 32      | BIAS             | Internal bias pin                                                          | _   | Α                          |

|         |                  | Connect a 33 k $\Omega$ resistor between BIAS and AV <sub>SS</sub> .       |     |                            |

| 33      | $AV_DD$          | Analog power supply (3 V)                                                  | _   | Α                          |

| 34      | Y IN             | Y input pin                                                                | _   | Α                          |

| 35      | AVss             | Analog ground (0 V)                                                        | _   | Α                          |

| 36      | ADCIN            | ADC input pin                                                              | _   | Α                          |

| 37      | VRM              | Reference voltage pin 1                                                    | _   | Α                          |

|         |                  | Connect a 0.1 $\mu F$ ceramic capacitor between VRM and AV <sub>SS</sub> . |     |                            |

| 38      | VRT              | Reference voltage pin 3                                                    | _   | Α                          |

|         |                  | Connect a 0.1 $\mu\text{F}$ ceramic capacitor between VRT and AVss.        |     |                            |

| 39      | VRB              | Reference voltage pin 2                                                    | _   | Α                          |

|         |                  | Connect a 0.1 $\mu F$ ceramic capacitor between VRB and AVss.              |     |                            |

| 40      | $DV_DD$          | Digital power supply (3 V)                                                 | _   | D                          |

| 41      | DV <sub>SS</sub> | Digital ground (0 V)                                                       | _   | D                          |

| 42      | OEB *1           | Digital output enable pin                                                  | _   | D                          |

| 43      | $DV_DD$          | Digital power supply (3 V)                                                 | _   | D                          |

| 44      | $DV_DD$          | Digital power supply (3 V)                                                 | _   | D                          |

| 45      | DV <sub>SS</sub> | Digital ground (0 V)                                                       | _   | D                          |

| 46      | CS               | Serial interface control input pin                                         | I   | D                          |

| 47      | SDATA            | Serial data input pin                                                      | 1   | D                          |

| 48      | SCK              | Serial clock input pin                                                     | I   | D                          |

Note: 1. With pull-down resistor.

# **Input/Output Equivalent Circuit**

| Pin Name       |                                                              | Equivalent Circuit                |

|----------------|--------------------------------------------------------------|-----------------------------------|

| Digital output | D0 to D11                                                    | DIN Digital output                |

| Digital input  | ADCLK, OBP,<br>SPBLK, SPSIG,<br>CS, SCK, SDATA,<br>PBLK, OEB | Digital input                     |

| Analog         | CDSIN                                                        | CDSIN Internally connected to VRT |

|                | ADCIN                                                        | ADCIN Internally connected to VRM |

|                | YIN                                                          | YIN                               |

|                | BLKSH, BLKFB                                                 | BLKFB BLKSH                       |

|                | VRT, VRM, VRB                                                | VRT VRM VRB AVDD                  |

|                | BIAS                                                         | BIAS AV <sub>DD</sub> WHE         |

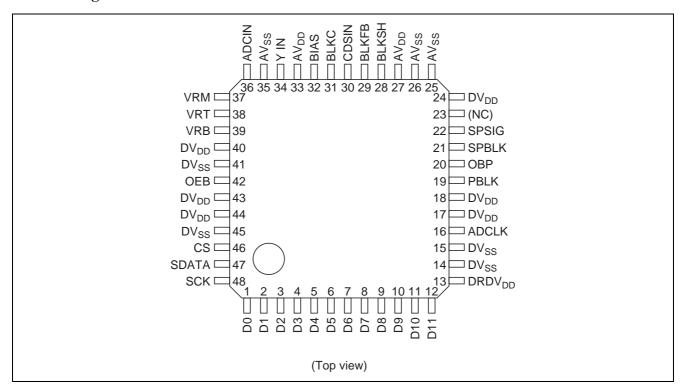

# **Block Diagram**

## **Internal Functions**

#### **Functional Description**

CDS input

CCD low-frequency noise is suppressed by CDS (correlated double sampling).

The signal level is clamped at 56 LSB to 304 LSB by resister during the OB period.

Gain can be adjusted using 10 bits of register (0.033 dB steps) within the range from -2.36 dB to 31.40 dB. \*1

ADC input

The center level of the input signal is clamped at 2048 LSB (Typ).

Gain can be adjusted using 10 bits of register (0.00446 times steps) within the range from 0.57 times (-4.86 dB) to 5.14 times (14.22 dB). \*1

Y-IN input

The input signal is clamped at 280 LSB (Typ) by SYNC Tip clamp.

Automatic offset calibration of PGA and ADC

DC offset compensation feedback for CCD and CDS

Pre-blanking

CDS input operation is protected by separating it from the large input signal.

Digital output is fixed at 32 LSB.

Digital output enable function

Note: 1. Full-scale digital output is defined as 0 dB (one time) when 1 V is input.

#### **Operating Description**

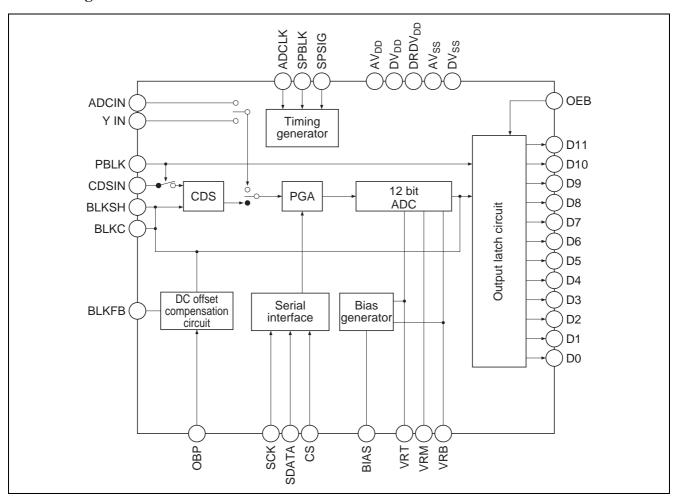

Figure 1 shows CDS/PGA + ADC function block.

Figure 1 HD49338F/HF Functional Block Diagram

## 1. CDS (Correlated Double Sampling) Circuit

The CDS circuit extracts the voltage differential between the black level and a signal including the black level. The black level is directly sampled at C1 by using the SPBLK pulse, buffered by the SHAMP, then provided to the CDSAMP.

The signal level is directly sampled at C2 by using the SPSIG pulse, and provided to CDSAMP (see figure 1). The difference between these two signal levels is extracted by the CDSAMP, which also operates as a programmable gain amplifier at the previous stage. The CDS input is biased with VRT (2 V) during the SPBLK pulse validation period. During the PBLK period, the above sampling and bias operation are paused.

#### 2. PGA Circuit

The PGAMP is the programmable gain amplifier for the latter stage. The PGAMP and the CDSAMP set the gain using 10 bits of register.

The equation below shows how the gain changes when register value N is from 0 to 1023.

In CDSIN mode:  $Gain = (-2.36 \text{ dB} + 0.033 \text{ dB}) \times \text{N (LOG linear)}.$

In ADCIN mode:  $Gain = (0.57 \text{ times} + 0.00446 \text{ times}) \times N \text{ (linear)}.$

Full-scale digital output is defined as 0 dB (one time) when 1 V is input.

3. Automatic Offset Calibration Function and Black-Level Clamp Data Setting

The DAC DC voltage added to the output of the PGAMP is adjusted by automatic offset calibration.

The data, which cancels the output offset of the PGAMP and the input offset of the ADC, and the clamp data (56 LSB to 304 LSB) set by register are added and input to the DAC.

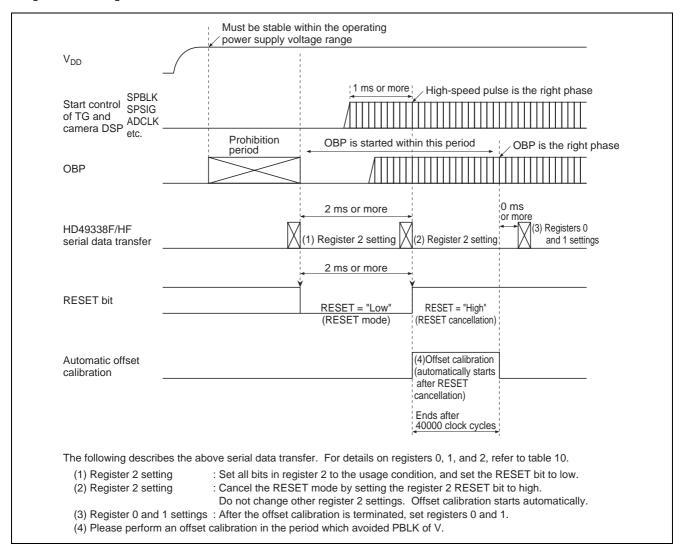

The automatic offset calibration starts automatically after the RESET mode set by register 1 is cancelled and terminates after 40000 clock cycles (when fclk = 20 MHz, 2 ms).

### 4. DC Offset Compensation Feedback Function

Feedback is done to set the black signal level input during the OB period to the DC standard, and all offsets (including the CCD offset and the CDSAMP offset) are compensated for.

The offset from the ADC output is calculated during the OB period, and SHAMP feedback capacitor C3 is charged by the current DAC (see figure 1).

The open-loop differential gain ( $\Delta Gain/\Delta H$ ) per 1 H of the feedback loop is given by the following equation. 1H is the one cycle of the OBP.

$\Delta Gain/\Delta H = 0.078/(fclk \times C3)$  (fclk: ADCLK frequency, C3: SHAMP external feedback capacitor) Example: When fclk = 20 MHz and C3 = 1.0  $\mu$ F,  $\Delta Gain/\Delta H = 0.0039$

When the PGAMP gain setting is changed, the high-speed lead-in operation state is entered, and the feedback loop gain is increased by a multiple of N. Loop gain multiplication factor N can be selected from 2 times, 4 times, 8 times, or 16 times by changing the register settings (see table 1). Note that the open-loop differential gain  $(\Delta Gain/\Delta H)$  must be one or lower. If it is two or more, oscillation occurs.

The time from the termination of high-speed lead-in operation to the return of normal loop gain operation can be selected from 1 H, 2 H, 4 H, or 8 H. If the offset error is over 64 LSB, the high-speed lead-in operation continues, and when the offset error is 64 LSB or less, the operation returns to the normal loop-gain operation after 1 H, 2 H, 4 H, or 8 H depending on the register settings. See table 2.

Table 1 Loop Gain Multiplication Factor during High-Speed Lead-In Operation

| HGair<br>(register | Multiplication<br>Factor N |    |  |  |  |  |  |  |  |  |

|--------------------|----------------------------|----|--|--|--|--|--|--|--|--|

| [0]                | [0] [1]                    |    |  |  |  |  |  |  |  |  |

| L                  | L                          | 4  |  |  |  |  |  |  |  |  |

| Н                  | L                          | 8  |  |  |  |  |  |  |  |  |

| L                  | Н                          | 16 |  |  |  |  |  |  |  |  |

| Н                  | Н                          | 32 |  |  |  |  |  |  |  |  |

Table 2 High-Speed Lead-In Operation Cancellation Time

| HGsto<br>(register | Cancellation |      |

|--------------------|--------------|------|

| [0]                | [1]          | Time |

| L                  | L            | 1 H  |

| Н                  | L            | 2 H  |

| L                  | Н            | 4 H  |

| Н                  | Н            | 8 H  |

#### 5. Pre-Blanking Function

During the PBLK input period, the CSD input operation is separated and protected from the large input signal. The ADC digital output is fixed to clamp data (56 to 304 LSB).

# 6. ADC Digital Output Control Function

The ADC digital output includes the functions output enable, code conversion, and test mode. Tables 3, 4 and 5 show the output functions and the codes.

**ADC Digital Output Functions** Table 3

| STBY | OEB | TEST0 | TEST1 | LINV | MINV | PBLK | ADC Digital Output  D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 | Operating Mode       |

|------|-----|-------|-------|------|------|------|-----------------------------------------------------------|----------------------|

| H    | X   | X     | X     | X    | X    | X    | Hi-Z                                                      | Low-power wait state |

| L    | Н   | Χ     | Χ     | Χ    | Х    | Х    | Hi-Z                                                      | Output Hi-Z          |

|      | L   | L     | L     | L    | L    | Н    | Same as in table 4.                                       | Normal operation     |

|      |     |       |       | L    | Н    | Н    | D11 is inverted in table 4.                               |                      |

|      |     |       |       | Н    | L    | Н    | D10 to D0 are inverted in table 4.                        |                      |

|      |     |       |       | Н    | Н    | Н    | D11 to D0 are inverted in table 4.                        |                      |

|      |     |       |       | Χ    | Χ    | L    | Output code is set up to Clamp Level.                     | Pre-blanking         |

|      |     |       | Н     | L    | L    | Н    | Same as in table 5.                                       | Normal operation     |

|      |     |       |       | L    | Н    | Н    | D11 is inverted in table 5.                               |                      |

|      |     |       |       | Н    | L    | Н    | D10 to D0 are inverted in table 5.                        |                      |

|      |     |       |       | Н    | Н    | Н    | D11 to D0 are inverted in table 5.                        |                      |

|      |     |       |       | Χ    | Χ    | L    | Output code is set up to Clamp Level.                     | Pre-blanking         |

|      |     | Н     | Χ     | L    | L    | Χ    | H   L   H   L   H   L   H   L   H   L   H   L             | Test mode            |

|      |     |       |       | Ĺ    | Н    | Χ    | L                                                         |                      |

|      |     |       |       | Н    | L    | Х    | H                                                         |                      |

|      |     |       |       | Н    | Н    | Χ    | L                                                         |                      |

- STBY, TEST, LINV, and MINV are set by register.

Mode setting for the OEB and the PBLK are done by external input pins.

The polarity of the PBLK pin when the register setting is SPinv is low.

Table 4 **ADC Output Code**

| Output | Pin   |      | D11 | D10 | D9 | D8  | D7  | D6    | D5 | D4    | D3 | D2  | D1  | D0  |

|--------|-------|------|-----|-----|----|-----|-----|-------|----|-------|----|-----|-----|-----|

| Output | Steps | 0    | L   | L   | L  | L   | L   | L     | L  | L     | L  | L   | L   | L   |

| codes  |       | 1    | L   | L   | L  | L   | L   | L     | L  | L     | L  | L   | L   | Н   |

|        |       | 2    | L   | L   | L  | L   | L   | L     | L  | L     | L  | L   | Н   | L   |

|        |       | 3    | L   | L   | L  | L   | L   | L     | L  | L     | L  | L   | Н   | Н   |

|        |       | 4    | L   | L   | L  | L   | L   | L     | L  | L     | L  | H   | L   | L   |

|        |       | 5    | L   | L   | L  | ¦ L | L   | ; L ; | L  | ; L ; | L  | ; H | ; L | : Н |

|        |       | 6    | L   | L   | L  | ¦ L | L   | : L : | L  | : L : | L  | : Н | : Н | L   |

|        |       | :    | ÷   | :   | :  | :   | :   | :     | :  | :     | :  | :   | 1   | :   |

|        |       | 2047 | L   | Н   | Н  | Н   | Н   | Н     | Н  | Н     | Н  | Н   | Н   | H   |

|        |       | 2048 | Н   | L   | L  | L   | L   | L     | L  | L     | L  | L   | L   | L   |

|        |       | :    | ÷   |     | :  |     | :   |       |    |       |    | :   | į į |     |

|        |       | 4092 | Н   | Н   | Н  | ; Н | Н   | ; Н ; | Н  | ; H ; | Н  | ; Н | ; L | : L |

|        |       | 4093 | Н   | H   | H  | ; Н | ; Н | ; H ; | H  | ; H   | H  | ; Н | ; L | H   |

|        |       | 4094 | Н   | H   | Н  | ; Н | ; Н | ; H ; | Н  | ; H   | Н  | ; Н | ; Н | L   |

|        |       | 4095 | Н   | Н   | Н  | H   | Н   | Н     | Н  | Н     | Н  | Н   | : н | Н   |

Table 5 **ADC Output Code** (TEST1)

| Output | Pin   |      | D11 | D10   | D9 | D8  | D7  | D6    | D5  | D4    | D3 | D2  | D1  | D0  |

|--------|-------|------|-----|-------|----|-----|-----|-------|-----|-------|----|-----|-----|-----|

| Output | Steps | 0    | L   | L     | L  | L   | L   | L     | L   | L     | L  | L   | L   | L   |

| codes  |       | 1    | L   | L     | L  | L   | L   | L     | L   | L     | L  | L   | L   | Н   |

|        |       | 2    | L   | L     | L  | L   | L   | L     | L   | L     | L  | L   | Н   | Н   |

|        |       | 3    | L   | L     | L  | L   | L   | L     | L   | L     | L  | L   | Н   | L   |

|        |       | 4    | L   | L     | L  | L   | L   | L     | L   | L     | L  | H   | ; н | L   |

|        |       | 5    | L   | ; L ; | L  | ; L | L   | ; L ; | ; L | ; L ; | L  | ; Н | ; Н | ; H |

|        |       | 6    | L   | L     | L  | L   | L   | L     | L   | L     | L  | H   | L   | : H |

|        |       | :    |     |       |    | 1   |     |       |     |       |    | i : | 1   |     |

|        |       | 2047 | L   | Н     | L  | L   | L   | L     | L   | L     | L  | L   | L   | L   |

|        |       | 2048 | Н   | Н     | L  | L   | L   | L     | L   | L     | L  | L   | L   | L   |

|        |       | :    |     |       |    | į : |     |       |     |       |    |     |     |     |

|        |       | 4092 | Н   | ; L ; | L  | ; L | L L | ; L ; | ¦ L | ; L ; | L  | ; L | ; Н | ; L |

|        |       | 4093 | Н   | ; L ; | L  | ; L | L L | ; L ; | ; L | ; L ; | L  | ; L | ; Н | ; H |

|        |       | 4094 | Н   | ; L ; | L  | ¦ L | L   | ; L ; | L   | ; L ; | L  | ¦ L | ; L | ; H |

|        |       | 4095 | H   | L     | L  | L   | L   | L     | L   | L     | L  | L   | L   | L   |

7. Adjustment of Black-Level S/H Response Frequency Characteristics The CR time constant that is used for sampling/hold (S/H) at the black level can be adjusted by changing the register settings, as shown in table 6.

Table 6 **SHSW CR Time Constant Setting**

|                                                      | SH         | SV  | /-f | sel | (R  | eg  | iste        | rs   | settii        | ng)   |     |                         |     |       |     |     |             |     |     |             |     |     |     |     |            |     |              |     |            |

|------------------------------------------------------|------------|-----|-----|-----|-----|-----|-------------|------|---------------|-------|-----|-------------------------|-----|-------|-----|-----|-------------|-----|-----|-------------|-----|-----|-----|-----|------------|-----|--------------|-----|------------|

|                                                      | [0]        | 1][ | 2]  | [3] | [0] | [1] | 2][3        | 3][[ | [0][1]        | [2][3 | 3]  | [0][1                   | ][2 | 2][3] | [0] | [1] | [2]         | [3] | [0] | [1]         | [2] | [3] | [0] | [1] | [2]        | 3][ | 0][1         | ][2 | 2][3]      |

|                                                      | L          | L   | L   | L   | Н   | L   | LL          | -1   | L H           | LI    | 니   | HE                      | ł L | . L   | L   | L   | Н           | L   | Н   | L           | Н   | L   | L   | Н   | Н          | L   | H            | 1 1 | 1 L        |

| CR Time Constant (Typ) (cutoff frequency conversion) | 2.2<br>(72 | -   |     | - 1 |     | -   | nsec<br>Hz) | - 1  | 2.51<br>(63 N |       |     | 2.6 <sup>2</sup><br>(60 |     |       | 1   |     |             |     | _   | 11 r<br>1 M |     |     | _   |     | nse<br>1Hz | - 1 | 3.77<br>(42  |     | sec<br>Hz) |

|                                                      | SH         | S۷  | /-f | sel | (R  | eg  | iste        | rs   | settii        | ng)   |     |                         |     |       |     |     |             |     |     |             |     |     |     |     |            |     |              |     |            |

|                                                      | [0]        | 1][ | 2]  | [3] | [0] | [1] | 2][3        | 3][  | [0][1]        | [2][3 | 3]  | [0][1                   | ][2 | 2][3] | [0] | [1] | [2]         | [3] | [0] | [1]         | [2] | [3] | [0] | [1] | [2]        | 3][ | 0][1         | ][2 | 2][3]      |

|                                                      | L          | L   | L   | Н   | Н   | L   | LH          |      | L H           |       |     |                         |     |       |     | L   |             | Н   |     |             |     |     |     |     |            |     |              |     | 1 H        |

| CR Time Constant (Typ) (cutoff frequency conversion) | 4.4<br>(36 | -   |     | - 1 |     | _   | nsec<br>Hz) | - 1  | 5.87<br>(27 N |       | - 1 | 6.60<br>(24             |     |       | 1 - |     | nse<br>/IHz |     |     | .6 r<br>5 M |     |     |     |     | nse<br>Iz) | - 1 | 26.4<br>(6 N |     | sec<br>z)  |

8. The SHAMP frequency characteristics can be adjusted by changing the register settings and the C4 value of the external 31st pin.

The settings are shown in table 7.

Values other than those shown in the table 7 cannot be used.

Table 7 **SHAMP Frequency Characteristics Setting**

|                    |      | SHA-fsel (Register setting) |      |                       |                                |     |  |  |  |  |  |  |  |

|--------------------|------|-----------------------------|------|-----------------------|--------------------------------|-----|--|--|--|--|--|--|--|

| LoPwr              | [0]  | [1]                         | [0]  | [1]                   | [0]                            | [1] |  |  |  |  |  |  |  |

| (Register setting) | Н    | L                           | L    | Н                     | Н                              | Н   |  |  |  |  |  |  |  |

| "Lo"               | 1000 | MHz<br>)0 pF<br>) pF)       | 1300 | MHz<br>)0 pF<br>) pF) | 56 MHz<br>18000 pF<br>(360 pF) |     |  |  |  |  |  |  |  |

| "Hi"               | 1500 | MHz<br>)0 pF<br>) pF)       | 2200 | MHz<br>)0 pF<br>) pF) | 24 MHz<br>27000 pF<br>(820 pF) |     |  |  |  |  |  |  |  |

Note: Upper line: SHAMP cutoff frequency (Typ)

Middle line: Standard value of C4 (maximum value is not defined)

Lower line: Minimum value of C4 (do not set below this value)

# **Timing Chart**

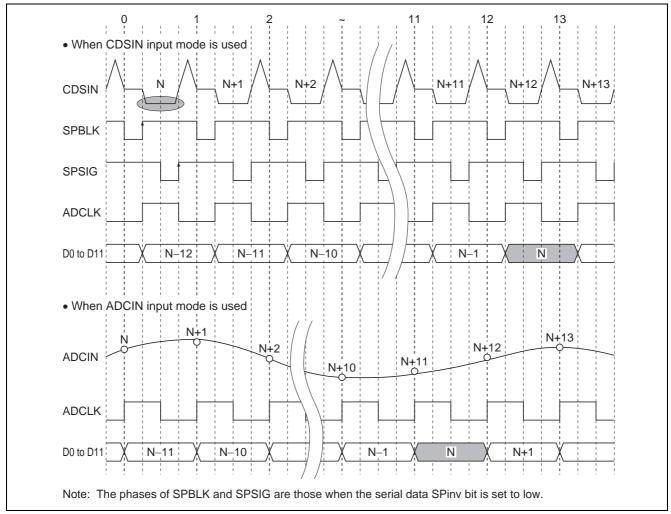

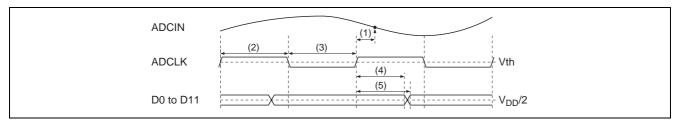

Figure 2 shows the timing chart when CDSIN and ADCIN input modes are used.

Figure 2 Output Timing Chart when CDSIN and ADCIN Input Modes are Used

The ADC output (D0 to D11) is output at the rising edge of the ADCLK in both modes. Pipe-line delay is twelve clock cycles when CDSIN is used and eleven when ADCIN is used. In ADCIN input mode, the input signal is sampled at the rising edge of the ADCLK.

# **Detailed Timing Specifications**

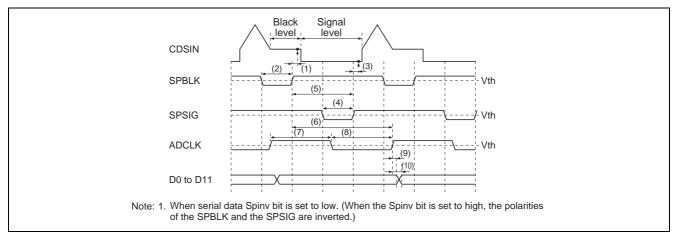

### **Detailed Timing Specifications when CDSIN Input Mode is Used**

Figure 3 shows the detailed timing specifications when the CDSIN input mode is used, and table 8 shows each timing specification.

Figure 3 Detailed Timing Chart when CDSIN Input Mode is Used

Table 8 Timing Specifications when the CDSIN Input Mode is Used

| No.      | Timing                                          | Symbol              | Min        | Тур                              | Max        | Unit |

|----------|-------------------------------------------------|---------------------|------------|----------------------------------|------------|------|

| (1)      | Black-level signal fetch time                   | t <sub>CDS1</sub>   | _          | (1.5)                            | _          | ns   |

| (2)      | SPBLK low period *1                             | t <sub>CDS2</sub>   | Typ × 0.8  | 1/4f <sub>CLK</sub>              | Typ × 1.2  | ns   |

| (3)      | Signal-level fetch time                         | t <sub>CDS3</sub>   | _          | (1.5)                            | _          | ns   |

| (4)      | SPSIG low period *1                             | t <sub>CDS4</sub>   | Typ × 0.8  | 1/4f <sub>CLK</sub>              | Typ × 1.2  | ns   |

| (5)      | SPBLK rising to SPSIG rising time *1            | t <sub>CDS5</sub>   | Typ × 0.85 | $1/2 f_{\text{CLK}} \times 0.90$ | Typ × 1.00 | ns   |

| (6)      | SPBLK rising to ADCLK rising inhibition time *1 | t <sub>CDS6</sub>   | 1          | 5                                | 9          | ns   |

| (7), (8) | ADCLK twh min./twl min.                         | t <sub>CDS7,8</sub> | 11         | _                                | _          | ns   |

| (9)      | ADCLK rising to digital output hold time        | t <sub>CHLD9</sub>  | 3          | 7                                | _          | ns   |

| (10)     | ADCLK rising to digital output delay time       | t <sub>COD10</sub>  | _          | 16                               | 24         | ns   |

Note: 1. SPBLK and SPSIG polarities when serial data Spinv bit is set to low.

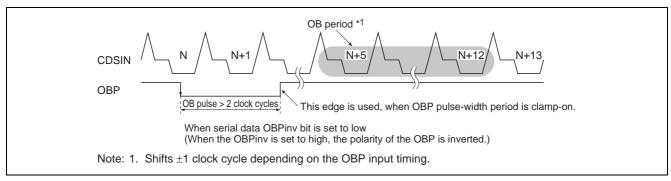

### **OBP Detailed Timing Specifications**

Figure 4 shows the OBP detailed timing specifications.

The OB period is from the fifth to the twelfth clock cycle after the OB pulse is input. The average of the black signal level is taken for eight input cycles during the OB period and becomes the clamp level (DC standard).

Figure 4 OBP Detailed Timing Specifications

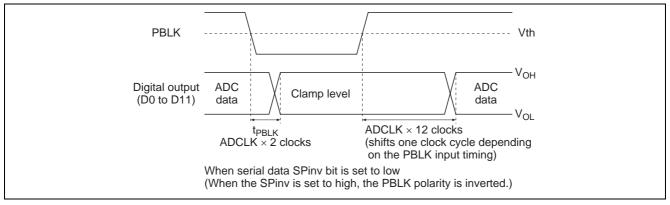

### **Detailed Timing Specifications at Pre-Blanking**

Figure 5 shows the pre-blanking detailed timing specifications.

Figure 5 Detailed Timing Specifications at Pre-Blanking

### Detailed Timing Specifications when ADCIN Input Mode is Used

Figure 6 shows the detailed timing chart when ADCIN input mode is used, and table 9 shows each timing specification.

Figure 6 Detailed Timing Chart when ADCIN Input Mode is Used

Table 9 Timing Specifications when ADCIN Input Mode is Used

| No.      | Timing                                          | Symbol               | Min        | Тур                   | Max        | Unit |

|----------|-------------------------------------------------|----------------------|------------|-----------------------|------------|------|

| (1)      | Signal fetch time                               | t <sub>ADC1</sub>    | _          | (6)                   |            | ns   |

| (2), (3) | ADCLK t <sub>WH</sub> min./t <sub>WL</sub> min. | t <sub>ADC2, 3</sub> | Typ × 0.85 | 1/2f <sub>ADCLK</sub> | Typ × 1.15 | ns   |

| (4)      | ADCLK rising to digital output hold time        | t <sub>AHLD4</sub>   | 10         | 14.5                  |            | ns   |

| (5)      | ADCLK rising to digital output delay time       | t <sub>AOD5</sub>    | _          | 23.5                  | 31.5       | ns   |

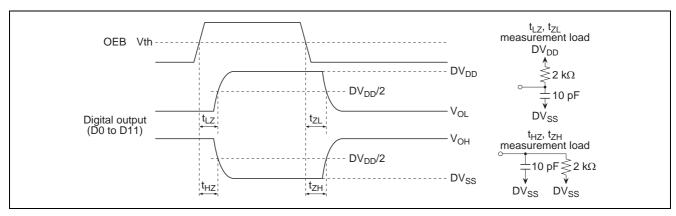

### **Detailed Timing Specifications for Digital Output-Enable Control**

Figure 7 shows the detailed timing specifications for digital output enable control. When the OEB pin is set to high, output disable mode is entered, and the output state becomes High-Z.

Figure 7 Detailed Timing Specifications for Digital Output Enable Control

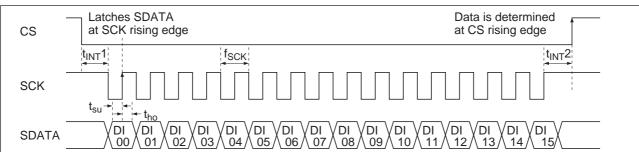

# **Serial Interface Specifications**

**Table 10 Serial Data Function List**

|             | Resister 0                                         | Resister 1                                         | Resister 2                                           | Resister 3                | Resister 4 to 7<br>Test Mode (can not be used) |

|-------------|----------------------------------------------------|----------------------------------------------------|------------------------------------------------------|---------------------------|------------------------------------------------|

| DI 00 (LSB) | Low                                                | High                                               | Low                                                  | High                      | Low to High                                    |

| DI 01       | Low                                                | Low                                                | High                                                 | High                      | Low to High                                    |

| DI 02       | Low                                                | Low                                                | Low                                                  | Low                       | High                                           |

| DI 03       | PGA gain setting (LSB) *5                          | SLP Low: Normal operation mode High: Sleep mode    | Clamp-level [0] (LSB)                                | YC-Bias off               |                                                |

| DI 04       | PGA gain setting *5                                | STBY Low: Normal operation mode High: Standby mode | Clamp-level [1]                                      | Gray code [0] (TEST1)     |                                                |

| DI 05       | PGA gain setting *5                                | Output mode setting (LINV)                         | Clamp-level [2]                                      | Gray code [1]             |                                                |

| DI 06       | PGA gain setting *5                                | Output mode setting (MINV)                         | Clamp-level [3]                                      | Average4, 4 lines average |                                                |

| DI 07       | PGA gain setting *5                                | Output mode setting (TEST0)                        | Clamp-level [4] (MSB)                                | Gray_test [0]             |                                                |

| DI 08       | PGA gain setting *5                                | SHA-fsel [0] (LSB) SHAMP frequency                 | HGstop-Hsel [0] High-speed lead-in                   | Gray_test [1]             |                                                |

| DI 09       | PGA gain setting *5                                | SHA-fsel [1] (MSB) characteristics switching       | HGstop-Hsel [1] cancellation time                    | Gray_test [2]             | Cannot be used. *7 All low                     |

| DI 10       | PGA gain setting *5                                | SHSW-fsel [0] (LSB)                                | HGain-Nsel [0] High-speed lead-in                    | Cannot be used. *8 Low    |                                                |

| DI 11       | PGA gain setting *5                                | SHSW-fsel [1] SHSW frequency                       | HGain-Nsel [1] gain multiplication                   | Cannot be used. *8 Low    |                                                |

| DI 12       | PGA gain setting (MSB) *5                          | SHSW-fsel [2] character-<br>istics<br>switching    | LoPwr Low: Normal mode<br>High: Low power mode       | Cannot be used. *8 High   |                                                |

| DI 13       | Х                                                  | SHSW-fsel [3] (MSB)                                | SPinv,<br>SPSIG/SPBLK/PBLK inversion                 | Cannot be used. *8 Low    |                                                |

| DI 14       | YSEL Low: CDSIN input mode<br>High: YIN input mode | Cannot be used. *7                                 | OBPinv, OBP inversion                                | Cannot be used. *8 Low    |                                                |

| DI 15 (MSB) | CSEL Low: CDSIN input mode<br>High: YIN input mode | All low                                            | RESET Low: Reset mode<br>High: Normal operation mode | Cannot be used. *8 High   |                                                |

Figure 8 Serial Interface Timing Specifications

- Notes: 1. 2 byte continuous communications.

2. SDATA is latched at SCK rising edge.

3. Insert 16 clocks of SCK while CS is low.

- 4. Data is invalid if data transmission is aborted during transmission.

- 5. The gain conversion table differs in the CDSIN input mode and the ADCIN input mode.

6. STBY: Reference voltage generator circuit is in the operating state.

- 6. STBY: Reference voltage generator circuit is in the operating state. SLP: All circuits are in the sleep state.

7. This bit is used for the IC testing, and cannot be used by the user. Please do not set up in addition to "ALL Low".

8. This bit is used for the IC testing, and cannot be used by the user. It is set to the state on the right of a column when RESET bit is set to low. The register 3 should transmit by setup on the right of a column.

**Timing Specifications**

|                       | Min   | Max   |  |  |  |  |  |  |  |

|-----------------------|-------|-------|--|--|--|--|--|--|--|

| f <sub>SCK</sub>      | _     | 5 MHz |  |  |  |  |  |  |  |

| t <sub>INT</sub> 1, 2 | 50 ns | _     |  |  |  |  |  |  |  |

| t <sub>su</sub>       | 50 ns | _     |  |  |  |  |  |  |  |

| tho                   | 50 ns |       |  |  |  |  |  |  |  |

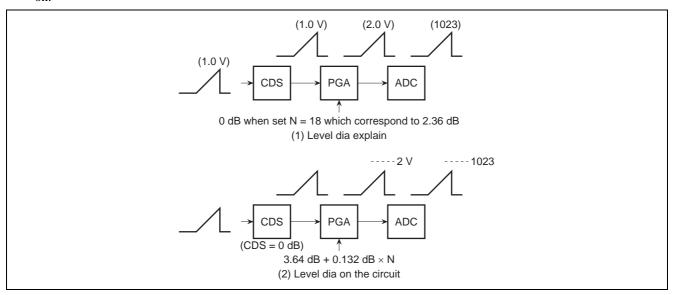

### **Explanation of Serial Data of CDS Part**

Serial data of CDS part has the following functions.

PGA gain (D5 to D12 of register 0)

Details are referred to page 6 block diagram.

At CDS\_in mode: -2.36 dB + 0.132 dB × N (Log linear)

At ADC\_in mode: 0.57 times + 0.01784 times × N (Times linear)

\*: Full-scale digital output is defined as 0 dB when 1 V is input.

Above PGA gain definition means input signal 1 Vp-p to CDS\_in, and set N = 18 (correspond 2.36 dB), and then PGA outputs the 2 V full-range, and also ADC out puts the full code (1023).

This mean offset gain of PGA has  $6 \, dB - 2.36 \, dB = 3.64 \, dB$ , therefore it should be decided that how much dB add on.

Figure 9 Level Dia of PGA

CSEL (D15 of register 0)

Data = 0: Select CDSIN Data = 1: Select ADCIN

|   |   | Α | ddres | ess STD1[7:0] (L) |   |   |   |  | STD2[15:8] (H) |          |          |          |          |          |               |               |     |      |       |     |               |               |

|---|---|---|-------|-------------------|---|---|---|--|----------------|----------|----------|----------|----------|----------|---------------|---------------|-----|------|-------|-----|---------------|---------------|

| 1 | 1 | 1 | 1     | 0                 | 0 | 0 | 1 |  |                | D4       | D3       | D2       | D1       | D0       | D15           | D14           | D13 | D12  | D11   | D10 | D9            | D8            |

|   |   |   |       |                   |   |   |   |  |                | <b>^</b> | <b>^</b> | <b>^</b> | <b>^</b> | <b>^</b> | $\overline{}$ | $\overline{}$ |     |      |       |     | $\overline{}$ | $\overline{}$ |

|   |   |   |       |                   |   |   |   |  |                | test0    | NIN/     | /NI      | STBY     | SLP      | test          | :_l2          | 5   | SHSV | V_fse | I   | SHA           | _fsel         |

SLP and STBY (D3, D4 of register 1)

SLP: Stop the all circuit. Consumption current of CDS part is less than 10  $\mu A.$

Start up from offset calibration when recover is needed.

STBY: Only the standard voltage generating circuit is operated. Consumption current of CDS part is about 3 mA. Allow 50 H time for feedback clamp is stabilized until recover.

Output mode (D5 to D7 of register 1 and D4 of register 3)

It is a test mode. Combination details are table 3 to 5. Normally set to all 0.

SHA-fsel (D8 to D9 of register 1)

It is a LPF switching of SH amplifier. Frequency characteristics are referred to page 9. To get rough idea, set the double cut off frequency point with using.

SHSW-fsel (D10 to D13 of register 1)

It is a time constant which sampling the black level of SH amplifier. Frequency characteristics are referred to page 9. To get rough idea, set the double cut off frequency point with using. S/N changes by this data, so find the appropriate point with set data to up/down.

#### HD49338F/HF

Clamp (D3 to D7 of register 2)

Determine the OB part level with digital code of ADC output.

Clamp level = setting data  $\times$  2 + 14

Default data is 9 = 32 LSB.

HGstop-Hsel, HGain-Nsel (D8 to D11 of register 2)

Determine the lead-in speed of OB clamp. Details are referred to page 7. PGA gain need to be changed for switch the high speed leading mode. Transfer the gain +1/-1 to previous field, its switch to high speed leading mode.

Low\_PWR (D12 of register 2)

Switch circuit current and frequency characteristic.

Data = 0: 36 MHz guarantee

Data = 1: 25 MHz guarantee

SPinv (D13 of register 2)

SPSIG/SPBLK/PBLK input signal inverted switching.

Data = 1: Normal

Data = 0: Inverted

Reset (D15 of register 2)

Software reset.

Data = 1: Normal

Data = 0: Reset

Offset calibration should be done when starting up with using this bit. Details are referred to page 19.

C\_Bias\_off (D3 of register 3)

Center bias is turned off in ADCIN mode.

Data = 0: Normally on

Data = 1: Off

Ave\_4H (D6 of register 3)

Clamp detection data is averaged 4H.

Data = 0: 1H

Data = 1: Averaged 4H

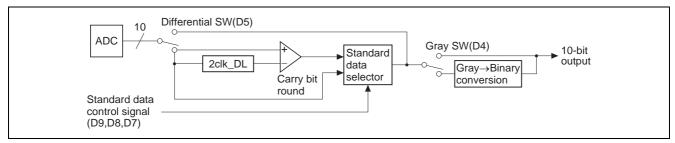

#### **Differential Code and Gray Code** (D4 to D5 and D7 to D9 of register 3)

Gray code (D4 to D5 of register 3)

DC output code can be change to following type.

| Gray Code [1] | Gray Code [0] | Output Code                 |

|---------------|---------------|-----------------------------|

| 0             | 0             | Binary code                 |

| 0             | 1             | Gray code                   |

| 1             | 0             | Differential encoded binary |

| 1             | 1             | Differential encoded gray   |

Serial data setting items (D7 to D9 of register 3)

| Setting Bit  | Setting Contents                                           |

|--------------|------------------------------------------------------------|

| Gray_test[0] | Standard data output timing control signal                 |

| Gray_test[1] | (Refer to the following table)                             |

| Gray_test[2] | ADCLK polar with OBP. (Lo→Positive edge, HI→Negative edge) |

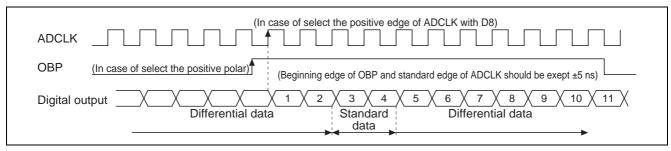

#### Standard data output timing

| Standard Data Output Timing |

|-----------------------------|

| Third and fourth            |

| Fourth and fifth            |

| Fifth and sixth             |

| Sixth and seventh           |

|                             |

Ripple (pseudo outline made by quantized error) occurres on the point which swithing the ADC output multiple bit in parallel. When switching the several of ADC output at the same time, ripple (pseudo outline caused by miss quantization) occurs to the image.

Differential code and gray code are recommended for this countermeasure.

Figure 10 indicates circuit block. When luminance signal changes are smoothly, the number of bit of switching digital output bit can be reduced and easily to reduce the ripple using this function.

This function is especially effective for longer the settings of sensor more than clk = 30 kHz, and ADC output. Figure 11 indicates the timing specifications.

Figure 10 Differential Code, Gray Code Circuit

Figure 11 Differential Code Timing Specifications

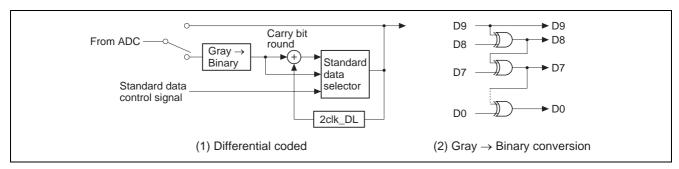

To use differential code, complex circuit is necessary at DSP side.

Figure 12 Complex Circuit Example

# **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                                   | Symbol                | Ratings                       | Unit |

|----------------------------------------|-----------------------|-------------------------------|------|

| Power supply voltage                   | V <sub>DD</sub> (max) | 4.1                           | V    |

| Analog input voltage                   | V <sub>IN</sub> (max) | -0.3 to AV <sub>DD</sub> +0.3 | V    |

| Digital input voltage                  | V <sub>I</sub> (max)  | -0.3 to DV <sub>DD</sub> +0.3 | V    |

| Operating temperature                  | Topr                  | -10 to +75                    | °C   |

| Power dissipation                      | Pt(max)               | 400                           | mW   |

| Storage temperature                    | Tstg                  | -55 to +125                   | °C   |

| Power supply voltage range (HD49338HF) | Vopr                  | 2.85 to 3.3                   | V    |

| Power supply voltage range (HD49338F)  | _                     | 2.70 to 3.3                   |      |

Notes: 1. V<sub>DD</sub> indicates AV<sub>DD</sub> and DV<sub>DD</sub>.

2.  $AV_{DD}$  and  $DV_{DD}$  must be commonly connected outside the IC. When they are separated by a noise filter, the potential difference must be 0.3 V or less at power on, and 0.1 V or less during operation.

### **Electrical Characteristics**

(Unless othewide specified,  $Ta=25^{\circ}C$ ,  $AV_{DD}=3.0~V$ ,  $DV_{DD}=3.0~V$ , and  $R_{BIAS}=33~k\Omega$ )

Items Common to CDSIN and ADCIN Input Modes

| Item                        | Symbol               | Min                                             | Тур  | Max                                            | Unit   | Test Conditions               | Remarks                           |

|-----------------------------|----------------------|-------------------------------------------------|------|------------------------------------------------|--------|-------------------------------|-----------------------------------|

| Power supply voltage range  | $V_{DD}$             | 2.85                                            | 3.00 | 3.30                                           | V      | LoPwr = low                   |                                   |

| Conversion frequency        | f <sub>CLK</sub> low | 5.5                                             | _    | 25                                             | MHz    | LoPwr = high                  |                                   |

|                             | f <sub>CLK</sub> hi  | 25                                              | _    | 36                                             | MHz    | LoPwr = low                   |                                   |

| Digital input voltage       | V <sub>IH</sub>      | $2.0 \times \frac{\text{DV}_{\text{DD}}}{3.0}$  | _    | $DV_{DD}$                                      | V      |                               | Digital input pins other than CS, |

|                             | V <sub>IL</sub>      | 0                                               | _    | $0.8 \times \frac{\text{DV}_{\text{DD}}}{3.0}$ | V      |                               | SCK and SDATA                     |

|                             | V <sub>IH2</sub>     | $2.25 \times \frac{\text{DV}_{\text{DD}}}{3.0}$ | _    | $DV_{DD}$                                      | V      |                               | CS, SCK, SDATA                    |

|                             | V <sub>IL2</sub>     | 0                                               | _    | $0.6 \times \frac{\text{DV}_{\text{DD}}}{3.0}$ | V      |                               | <del>-</del>                      |

| Digital output voltage      | V <sub>OH</sub>      | DV <sub>DD</sub> -0.5                           | _    | _                                              | V      | $I_{OH} = -1 \text{ mA}$      |                                   |

|                             | V <sub>OL</sub>      | _                                               | _    | 0.5                                            | V      | I <sub>OL</sub> = +1 mA       |                                   |

| Digital input current       | I <sub>IH</sub>      | _                                               | _    | 50                                             | μΑ     | V <sub>IH</sub> = 3.0 V       |                                   |

|                             | I <sub>IH2</sub>     | _                                               | _    | 250                                            | μА     | V <sub>IH</sub> = 3.0 V       |                                   |

|                             | I <sub>IL</sub>      | -50                                             | _    | _                                              | μА     | $V_{IL} = 0 V$                |                                   |

| Digital output current      | l <sub>ozh</sub>     | _                                               | _    | 50                                             | μΑ     | $V_{OH} = V_{DD}$             |                                   |

|                             | I <sub>OZL</sub>     | -50                                             | _    | _                                              | μΑ     | $V_{OL} = 0 V$                |                                   |

| ADC resolution              | RES                  | 12                                              | 12   | 12                                             | bit    |                               |                                   |

| ADC integral linearity      | INL                  | _                                               | (8)  | _                                              | LSBp-p | f <sub>CLK</sub> = 20 MHz     |                                   |

| ADC differential linearity+ | DNL+                 | _                                               | 0.6  | 0.95                                           | LSB    | $f_{CLK} = 20 \text{ MHz}$    | *1                                |

| ADC differential linearity- | DNL-                 | -0.95                                           | -0.6 | _                                              | LSB    | f <sub>CLK</sub> = 20 MHz     | *1                                |

| Sleep current               | I <sub>SLP</sub>     | -100                                            | 0    | 100                                            | μА     | Digital input pin is          |                                   |

|                             |                      |                                                 |      |                                                |        | set to 0 V, output            |                                   |

|                             |                      |                                                 |      |                                                |        | pin is open                   |                                   |

| Standby current             | I <sub>STBY</sub>    | _                                               | 3    | 5                                              | mA     | Digital I/O pin is set to 0 V |                                   |

| Digital output Hi-Z         | t <sub>HZ</sub>      | _                                               | _    | 100                                            | ns     | $R_L = 2 k\Omega$ ,           | See figure 7                      |

| delay time                  | t <sub>LZ</sub>      |                                                 | _    | 100                                            | ns     | C <sub>L</sub> = 10 pF        |                                   |

|                             | t <sub>ZH</sub>      |                                                 |      | 100                                            | ns     | =                             |                                   |

|                             | t <sub>ZL</sub>      |                                                 |      | 100                                            | ns     |                               |                                   |

Notes: 1. Differential linearity is the calculated difference in linearity errors between adjacent codes.

2. Values within parentheses ( ) are for reference.

# **Electrical Characteristics** (cont.)

(Unless othewide specified, Ta = 25°C, AV  $_{DD}$  = 3.0 V, DV  $_{DD}$  = 3.0 V, and  $R_{BIAS}$  = 33 k\Omega)

Items for CDSIN Input Mode

| Item                       | Symbol             | Min                     | Тур                      | Max        | Unit | <b>Test Conditions</b>      | Remarks     |

|----------------------------|--------------------|-------------------------|--------------------------|------------|------|-----------------------------|-------------|

| Consumption current (1)    | I <sub>DD1</sub>   | _                       | 57                       | 68         | mA   | LoPwr = low                 |             |

|                            |                    |                         |                          |            |      | $f_{CLK} = 36 \text{ MHz}$  |             |

| Consumption current (2)    | $I_{DD2}$          | _                       | 37                       | 46         | mA   | LoPwr = high                |             |

|                            |                    |                         |                          |            |      | $f_{CLK} = 250 \text{ MHz}$ |             |

| CCD offset tolerance range | $V_{CCD}$          | (-100)                  | _                        | (100)      | mV   |                             |             |

| Timing specifications (1)  | t <sub>CDS1</sub>  | _                       | (1.5)                    | _          | ns   |                             | See table 8 |

| Timing specifications (2)  | t <sub>CDS2</sub>  | $\text{Typ} \times 0.8$ | 1/4f <sub>CLK</sub>      | Typ × 1.2  | ns   |                             | _           |

| Timing specifications (3)  | t <sub>CDS3</sub>  | _                       | (1.5)                    | _          | ns   |                             | _           |

| Timing specifications (4)  | t <sub>CDS4</sub>  | Typ × 0.8               | 1/4f <sub>CLK</sub>      | Typ × 1.2  | ns   |                             | _           |

| Timing specifications (5)  | t <sub>CDS5</sub>  | Typ × 0.85              | $1/2f_{CLK} \times 0.90$ | Typ × 1.00 | ns   |                             | _           |

| Timing specifications (6)  | t <sub>CDS6</sub>  | 1                       | 5                        | 9          | ns   |                             | _           |

| Timing specifications (7)  | t <sub>CDS7</sub>  | 11                      | _                        | _          | ns   |                             | _           |

| Timing specifications (8)  | t <sub>CDS8</sub>  | 11                      | _                        | _          | ns   |                             | _           |

| Timing specifications (9)  | t <sub>CHLD9</sub> | 3                       | 7                        | _          | ns   | C <sub>L</sub> = 10 pF      | _           |

| Timing specifications (10) | t <sub>COD10</sub> | _                       | 16                       | 24         | ns   | _                           |             |

| Clamp level                | CLP(00)            | _                       | (56)                     | _          | LSB  |                             |             |

|                            | CLP(09)            | _                       | (128)                    | _          | LSB  |                             |             |

|                            | CLP(31)            | _                       | (304)                    | _          | LSB  |                             |             |

| PGA gain at CDS input      | AGC(0)             | -4.4                    | -2.4                     | -0.4       | dB   |                             |             |

|                            | AGC(256)           | 4.1                     | 6.1                      | 8.1        | dB   |                             |             |

|                            | AGC(512)           | 12.5                    | 14.5                     | 16.5       | dB   |                             |             |

|                            | AGC(768)           | 21.0                    | 23.0                     | 25.0       | dB   |                             |             |

|                            | AGC(1023)          | 29.4                    | 31.4                     | 33.4       | dB   |                             |             |

Note: Values within parentheses () are for reference.

### Items for ADCIN Input Mode

| Item                       | Symbol             | Min                      | Тур                   | Max        | Unit  | <b>Test Conditions</b>           | Remarks     |

|----------------------------|--------------------|--------------------------|-----------------------|------------|-------|----------------------------------|-------------|

| Consumption current (3)    | I <sub>DD3</sub>   | _                        | 39                    | 49         | mA    | LoPwr = low                      |             |

|                            |                    |                          |                       |            |       | $f_{CLK} = 36 \text{ MHz}$       |             |

| Consumption current (4)    | $I_{DD4}$          | _                        | 21                    | 26         | mA    | LoPwr = high                     |             |

|                            |                    |                          |                       |            |       | $f_{CLK} = 20 \text{ MHz}$       |             |

| Timing specifications (11) | t <sub>ADC1</sub>  | _                        | (6)                   | _          | ns    |                                  | See table 9 |

| Timing specifications (12) | t <sub>ADC2</sub>  | $\text{Typ} \times 0.85$ | 1/2f <sub>ADCLK</sub> | Typ × 1.15 | ns    |                                  |             |

| Timing specifications (13) | t <sub>ADC3</sub>  | $\text{Typ} \times 0.85$ | 1/2f <sub>ADCLK</sub> | Typ × 1.15 | ns    |                                  | _           |

| Timing specifications (14) | t <sub>AHLD4</sub> | _                        | 14.5                  | _          | ns    | C <sub>L</sub> = 10 pF           | _           |

| Timing specifications (15) | t <sub>AOD5</sub>  | _                        | 23.5                  | 31.5       | ns    |                                  |             |

| Input current at ADC input | IIN <sub>CIN</sub> | -110                     | _                     | 110        | μΑ    | V <sub>IN</sub> = 1.0 V to 2.0 V |             |

| Clamp level at ADC input   | OF2                | _                        | (2048)                | _          | LSB   |                                  |             |

| Clamp level at YIN input   | OF1                | _                        | (280)                 | _          | LSB   |                                  |             |

| PGA gain at ADC input      | GSL(0)             | 0.45                     | 0.57                  | 0.72       | Times |                                  |             |

|                            | GSL(256)           | 1.36                     | 1.71                  | 2.16       | Times |                                  |             |

|                            | GSL(512)           | 2.27                     | 2.86                  | 3.60       | Times |                                  |             |

|                            | GSL(768)           | 3.18                     | 4.00                  | 5.04       | Times |                                  |             |

|                            | GSL(1023)          | 4.08                     | 5.14                  | 6.47       | Times |                                  |             |

Note: Values within parentheses () are for reference.

# **Operation Sequence at Power On**

### **Notice for Use**

- 1. Careful handling is necessary to prevent damage due to static electricity.

- 2. This product has been developed for consumer applications, and should not be used in non-consumer applications.

- 3. As this IC is sensitive to power line noise, the ground impedance should be kept as small as possible. Also, to prevent latchup, a ceramic capacitor of  $0.1~\mu F$  or more and an electrolytic capacitor of  $10~\mu F$  or more should be inserted between the ground and power supply.

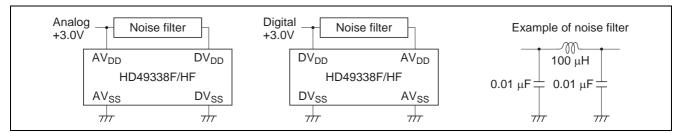

- 4. Common connection of  $AV_{DD}$  and  $DV_{DD}$  should be made off-chip. If  $AV_{DD}$  and  $DV_{DD}$  are isolated by a noise filter, the phase difference should be 0.3 V or less at power-on and 0.1 V or less during operation.

- 5. If a noise filter is necessary, make a common connection after passage through the filter, as shown in the figure below.

- 6. Connect  $AV_{SS}$  and  $DV_{SS}$  off-chip using a common ground. If there are separate analog system and digital system set grounds, connect to the analog system.

- 7. When  $V_{DD}$  is specified in the data sheet, this indicates  $AV_{DD}$  and  $DV_{DD}$ .

- 8. No Connection (NC) pins are not connected inside the IC, but it is recommended that they be connected to power supply or ground pins or left open to prevent crosstalk in adjacent analog pins.

- 9. To ensure low thermal resistance of the package, a Cu-type lead material is used. As this material is less tolerant of bending than Fe-type lead material, careful handling is necessary.

- 10. The infrared reflow soldering method should be used to mount the chip. Note that general heating methods such as solder dipping cannot be used.

- 11. Serial communication should not be performed during the effective video period, since this will result in degraded picture quality. Also, use of dedicated ports is recommended for the SCK and SDATA signals used in the HD49330AF. If ports are to be shared with another IC, picture quality should first be thoroughly checked.

- 12. At power-on, automatic adjustment of the offset voltage generated from PGA, ADC, etc., must be implemented in accordance with the power-on operating sequence (see page 16).

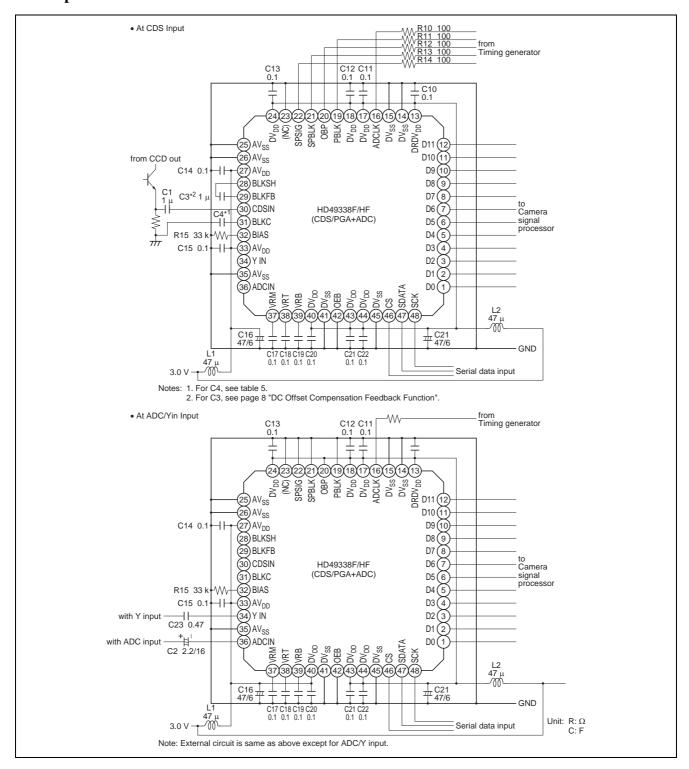

# **Example of Recommended External Circuit**

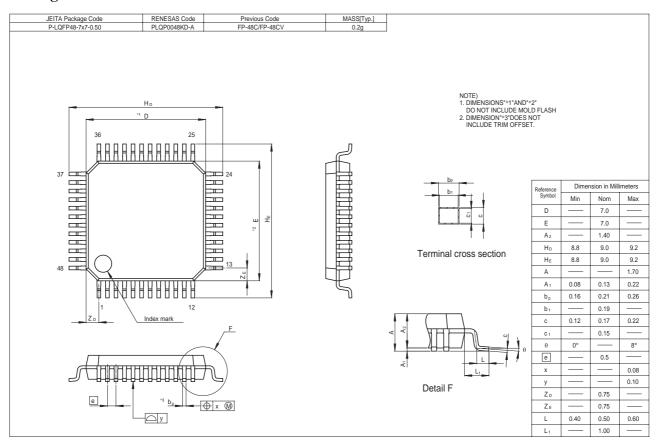

# **Package Dimensions**

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

- (ii) use of nontrammaple material of (iii) prevention against any maintention or misnap.

Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained here

- use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

**Renesas Technology America, Inc.** 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

| © 2005 Panagag Taghnalagy Corn | All rights reserved | Drinted in Japan |

|--------------------------------|---------------------|------------------|