# AN4124 Application note

Using SPC56EL60x fault collection and control unit (FCCU)

### Introduction

This application note describes in detail how to use the main features of the SPC56EL60x fault collection and control unit module (FCCU).

The fault collection and control unit offers a redundant hardware channel to collect errors and, as soon as a failure is detected, to lead the device to a safety state in a controlled way. No CPU intervention is required for collection and control operation.

The FCCU circuitry is checked at start-up (after boot) by the self-checking procedure. The FCCU is operative with a default configuration (without CPU intervention) immediately after the completion of the self-checking procedure.

Two classes of faults are identified based on the criticity and the related reactions.

Internal (that is, short or long functional reset, interrupt request) and external (EOUT signaling) reactions are statically defined or programmable based on the fault criticity.

The default configuration can be modified only in a specific FCCU state for application/test/debugging purposes.

# Contents

| 1        | FCCU   | J main features                                               |   |  |  |

|----------|--------|---------------------------------------------------------------|---|--|--|

| 2        | HW/S   | <i>N</i> recoverability fault                                 |   |  |  |

| 3        | Fault  | lual path: FCCU and RGM                                       | 8 |  |  |

|          | 3.1    | RGM module                                                    | 8 |  |  |

| 4        | Fault: | CF and NCF                                                    | 9 |  |  |

|          | 4.1    | Critical fault (CF)                                           | 9 |  |  |

|          | 4.2    | Non-critical fault (NCF)                                      | 1 |  |  |

| 5        | FCCU   | settings                                                      | 3 |  |  |

|          | 5.1    | Example 1: FCCU critical fault injection (no NMI assertion) 1 | 3 |  |  |

|          |        | 5.1.1 FCCU init                                               | 4 |  |  |

|          | 5.2    | Example 2: FCCU critical fault injection (NMI assertion)      | 5 |  |  |

|          |        | 5.2.1 FCCU init                                               | 6 |  |  |

|          | 5.3    | Example 3: FCCU - Non-critical fault injection                | 6 |  |  |

|          | 5.4    | LOCK FCCU configuration 1                                     | 8 |  |  |

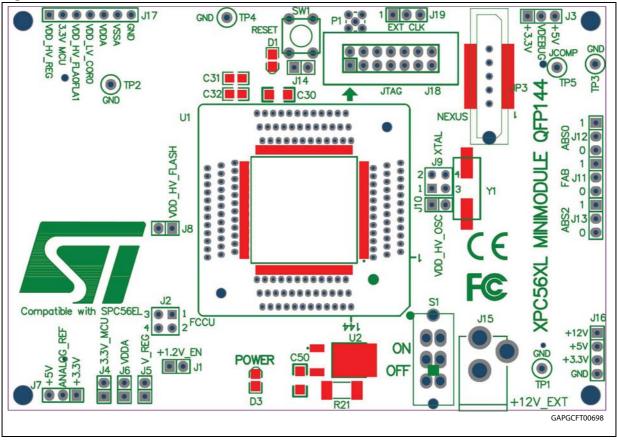

|          | 5.5    | Hardware: XPC56XL minimodule                                  | 8 |  |  |

| Appendix | A R    | dundancy and functions1                                       | 9 |  |  |

|          | A.1    | Path redundancy on critical error reaction                    | 9 |  |  |

|          | A.2    | General purpose function                                      | 1 |  |  |

|          |        | A.2.1 Config state                                            | 1 |  |  |

|          |        | A.2.2 Normal state                                            | 1 |  |  |

|          |        | A.2.3 Lock FCCU                                               | 1 |  |  |

|          |        | A.2.4 Read status register 2                                  | 1 |  |  |

|          |        | A.2.5 Clear fault                                             | 2 |  |  |

|          |        | A.2.6 Clear all critical faults                               | 3 |  |  |

|          |        | A.2.7 Clear all Non-critical faults 2                         | 3 |  |  |

|          |        | A.2.8 Read FCCU - state machine                               |   |  |  |

|          |        | A.2.9 Non-critical fault - enable                             |   |  |  |

|          |        | A.2.10 NCF - normal to alarm - read state                     |   |  |  |

|          |        | A.2.11 NCF - normal to alarm - clear state                    | 5 |  |  |

|                  | A.2.12     | IRQ status                             |  |  |

|------------------|------------|----------------------------------------|--|--|

| A.3              | General    | purpose functions                      |  |  |

|                  | A.3.1      | Example N1: fake NCF by external IRQ26 |  |  |

|                  | A.3.2      | Example N2: fake CF by external IRQ    |  |  |

| Appendix B       | Further ir | nformation                             |  |  |

| B.1              | Acronyn    | ns 30                                  |  |  |

| Revision history |            |                                        |  |  |

# List of tables

| Table 1. | RGM_FES register          | 3 |

|----------|---------------------------|---|

| Table 2. | Critical fault            | ) |

|          | Non-critical fault        |   |

| Table 4. | Acronyms                  | ) |

| Table 5. | Document revision history |   |

# List of figures

| Figure 1. | FCCU state machine                                |

|-----------|---------------------------------------------------|

| Figure 2. | XPC56EL minimodule                                |

| Figure 3. | Dual path faults                                  |

| Figure 4. | RGM/FCCU – no dual path faults                    |

| Figure 5. | RGM/FCCU – dual path faults (critical faults)     |

| Figure 6. | RGM/FCCU – dual path faults (Non-critical Faults) |

| Figure 7. | XPC56xxMB mother board                            |

| Figure 8. | NCF injection flow                                |

| Figure 9. | CF injection flow                                 |

## 1 FCCU main features

The FCCU features are:

- The fault control and collection unit (FCCU) is a hardware IP providing a central capability to control and collect faults reported by individual modules of the SoC.

- Faults are reported to the outside world via output pin(s), if no recovery is provided by SoC. No internal actions (such as IRQ, Reset) can be taken.

- The operation of the fault collection unit is independent of the CPU, so the FCCU provides a fault reporting mechanism even if the CPU is malfunctioning.

- The fault control and collection unit is developed specifically to increase the level of the safety of the system and ECU.

- The FCCU allows a redundant path to the RGM to enter failsafe mode in case of error.

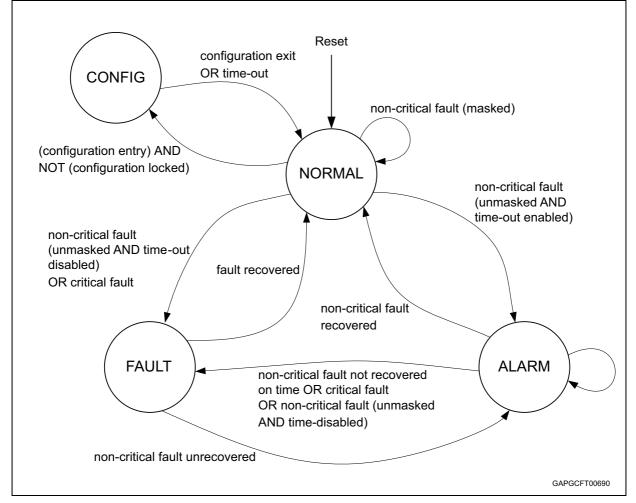

Below *Figure 1* FCCU-SM (state machine):

Figure 1. FCCU state machine

## 2 HW/SW recoverability fault

In general, the following definitions are applicable to fault management:

- HW recoverable fault: the fault indication is a level sensitive signal that is asserted until the cause of the fault is removed. Typically the fault signal is latched in an external module to the FCCU. The FCCU state transitions are consequently executed on the state changes of the input fault signal (fccu\_cf[] or fccu\_ncf[]). No SW intervention in the FCCU is required to recover the fault condition.

- SW recoverable fault: the fault indication is a signal asserted without a defined time duration. The fault signal is resynchronized and latched in the FCCU. The fault recovery is executed following a SW recovery procedure (status/flag register clearing).

The following types of reset are applicable:

- Destructive reset: any type of reset related to a power failure condition that implies a complete system reinitialization

- Long functional reset: implies FLASH and digital circuitry (with some exceptions, including FCCU, STCU) initialization

- Short functional reset: implies digital circuitry (with some exceptions, including FCCU, STCU) initialization

## 3 Fault dual path: FCCU and RGM

Due to the dual path, many faults (critical and not) reach the RGM and FCCU.

NMI can be mapped in RAM. For this reason the NMI is cleared after RESET condition.

In general, when a fault occurs, if it is mapped on RGM and FCCU, the RGM generates a RESET, independently of FCCU settings. After RESET (generated by fault) the system is in SAFE state. Looking in the FCCU CFSx status register (by procedure), it may recognize the fault, and react to it. After fault recovery the system transition can be: SAFE => RUN.

If the fault is mapped only on FCCU (as CF[20]), when it occurs the system resets or generates an NMI assertion, depending on FCCU settings. In RESET case, the FCCU generates a RESET by RGM.

Since the system stays in SAFE state, it does nothing. After the system transitions from SAFE to RUN (and fault is set), the system unmasks the NMI. By NMI ISR it is possible to clear the fault state registers.

### 3.1 RGM module

The reset generation module (MC\_RGM) centralizes the different reset sources and manages the reset sequence of the device.

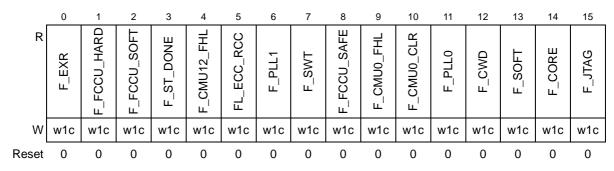

Table 1 shows the RGM\_FES (Functional Event Status) register bitmap.

#### Table 1. RGM\_FES register

## 4 Fault: CF and NCF

The FAULT state has a higher priority than the ALARM state, in the case of concurrent fault events (critical and non-critical) that occur in the NORMAL state. In case of concurrent critical faults, the fault reaction corresponds to the worst case (for example, a long functional reset is asserted if it has been programmed).

The ALARM to FAULT state transition occurs if a fault (unmasked and with time-out disabled) is asserted in the ALARM state.

Any critical fault (programmed to react with a hard or soft reaction) that occurs when the FCCU is already in the FAULT state causes an immediate hard or soft reaction (long or short functional reset).

The ALARM to NORMAL state transition occurs only if all the non-critical faults (including the faults that have been collected after entry to ALARM state) have been cleared (SW or HW recovery). Otherwise the FCCU will remain in the ALARM state.

The FAULT to NORMAL state transition occurs only if all the critical and non-critical faults (including the faults that have been collected after entry to FAULT/ALARM state) have been cleared (SW or HW recovery). Otherwise the FCCU remains in the FAULT state (if any critical fault is still pending) or returns to the ALARM state (if any non-critical fault is still pending and the time-out has not elapsed).

### 4.1 Critical fault (CF)

Below is the CF table:

| Critical fault | Source   | Signal  | Short/long/non<br>e default func.<br>reset | Set/clear<br>injection |

|----------------|----------|---------|--------------------------------------------|------------------------|

| CF[0]          | RCCUO[0] | rcc_out | Long                                       | Х                      |

| CF[1]          | RCCU1[0] | rcc_out | Long                                       | Х                      |

| CF[2]          | RCCUO[1] | rcc_out | Long                                       | Х                      |

| CF[3]          | RCCU1[1] | rcc_out | Long                                       | Х                      |

| CF[4]          | RCCUO[2] | rcc_out | Long                                       | Х                      |

| CF[5]          | RCCU1[2] | rcc_out | Long                                       | Х                      |

| CF[6]          | RCCUO[3] | rcc_out | Long                                       | Х                      |

| CF[7]          | RCCU1[3] | rcc_out | Long                                       | Х                      |

| CF[8]          | RCCUO[4] | rcc_out | Long                                       | Х                      |

| CF[9]          | RCCU1[4] | rcc_out | Long                                       | Х                      |

| CF[10]         | RCCUO[5] | rcc_out | Long                                       | Х                      |

| CF[11]         | RCCU1[5] | rcc_out | Long                                       | Х                      |

| CF[12]         | RCCUO[6] | rcc_out | Long                                       | Х                      |

#### Table 2. Critical fault

| Critical fault | Source                                                             | Signal                                                                 | Short/long/non<br>e default func.<br>reset | Set/clear<br>injection |

|----------------|--------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------|------------------------|

| CF[13]         | RCCU1[6]                                                           | rcc_out                                                                | Long                                       | Х                      |

| CF[14]         | SWT_0                                                              | Software watchdog timer                                                | Long                                       | —                      |

| CF[15]         | SWT_1                                                              | Software watchdog timer                                                | Long                                       | —                      |

| CF[16]         | MCM_NCE_0                                                          | ECC not correctable error                                              | Long                                       | —                      |

| CF[17]         | MCM_NCE_1                                                          | ECC not correctable error                                              | Long                                       | —                      |

| CF[18]         | ADC_CF_0                                                           | Internal self test (critical fault)                                    | _                                          | X (by ADC<br>itself)   |

| CF[19]         | ADC_CF_1                                                           | Internal self test (critical fault)                                    | _                                          | X (by ADC<br>itself)   |

| CF[20]         | STCU_CF                                                            | Bist results (critical faults)                                         | —                                          | Х                      |

| CF[21]         | LVD_HVD_1.2V                                                       | LVD/HVD BIST failure result in test mode                               | _                                          | x                      |

| CF[22]         | SSCM_XFER_ERR SSCM transfer error (during the STCU config loading) |                                                                        | _                                          | _                      |

| CF[23]         | LSM_DPM_ERR0 LSM <-> DPM runtime switch                            |                                                                        | Long                                       | Х                      |

| CF[24]         | LSM_DPM_ERR1                                                       | LSM <-> DPM runtime switch                                             | Long                                       | Х                      |

| CF[25]         | —                                                                  | —                                                                      | —                                          | —                      |

| CF[26]         | —                                                                  | —                                                                      | —                                          | —                      |

| CF[27]         | STCU                                                               | STCU fault condition (run in application mode)                         | Long                                       | _                      |

| CF[28]         | DFT0                                                               | Combination of safety critical signals from Test Control Unit (TCU)    | Long                                       | _                      |

| CF[29]         | DFT1                                                               | Combination of safety critical signals from Test Control Unit (TCU)    | Long                                       | _                      |

| CF[30]         | DFT2                                                               | Combination of safety critical signals from Test Control Unit (TCU)    | Long                                       | _                      |

| CF[31]         | DFT3                                                               | Combination of safety critical signals<br>from Test Control Unit (TCU) |                                            | _                      |

#### Table 2. Critical fault (continued)

# 4.2 Non-critical fault (NCF)

Table 3 is about the NCF table:

#### Table 3. Non-critical fault

| Non-<br>critical<br>fault | Source             | Signal                                            | Short/long/<br>none default<br>func reset | Fault<br>management | Polarity | Set/clear<br>injection |

|---------------------------|--------------------|---------------------------------------------------|-------------------------------------------|---------------------|----------|------------------------|

| NCF[0]                    | Core_0<br>watchdog | p_wrs[0]                                          | Long                                      | latched             | High     | —                      |

| NCF[1]                    | Core_0<br>watchdog | p_wrs[1]                                          | Long                                      | latched             | High     | —                      |

| NCF[2]                    | FM_PLL_0           | Loss of lock                                      | Long                                      | latched             | High     | —                      |

| NCF[3]                    | FM_PLL_1           | Loss of lock                                      | Long                                      | latched             | High     | —                      |

| NCF[4]                    | CMU_0              | Loss of XOSC clock                                | Long                                      | latched             | High     | —                      |

| NCF[5]                    | CMU_0              | Sysclk frequency out of range                     | Long                                      | latched             | High     | _                      |

| NCF[6]                    | CMU_1              | MOTC_CLK frequency out of range                   | Long                                      | latched             | High     | _                      |

| NCF[7]                    | CMU_2              | FRPE_CLK frequency out of range                   | Long                                      | latched             | High     | _                      |

| NCF[8]                    | MCM_ECN_0          | ECC 1-bit error correction notification           | _                                         | latched             | High     | _                      |

| NCF[9]                    | MCM_ECN_1          | ECC 1-bit error correction notification           | _                                         | latched             | High     | _                      |

| NCF[10]                   | ADC_NCF_0          | Internal self test (Non-critical fault)           | _                                         | latched             | High     | X (by ADC<br>itself)   |

| NCF[11]                   | ADC_NCF_1          | Internal self test (Non-critical fault)           | _                                         | latched             | High     | X (by ADC<br>itself)   |

| NCF[12]                   | STCU_NCF           | Bist results (Non-critical faults)                | _                                         | latched             | High     | х                      |

| NCF[13]                   | LVD_ 1.2V          | LVD BIST OK in test mode/<br>LVD NOK in user mode |                                           | latched             | High     | х                      |

| NCF[14]                   | HVD_ 1.2V          | HVD BIST OK in test mode/<br>HVD NOK in user mode | _                                         | latched             | High     | х                      |

| NCF[15]                   | LVD VREG           | LVD VREG fault detected by self-checking          | _                                         | latched             | High     | х                      |

| NCF[16]                   | LVD FLASH          | LVD FLASH fault detected by self-checking         | _                                         | latched             | High     | х                      |

| NCF[17]                   | LVD IO             | LVD IO fault detected by self-<br>checking        | _                                         | latched             | High     | х                      |

| NCF[18]                   | PMU                | Comparator fault detected by self-checking        |                                           | latched             | High     | _                      |

| NCF[19]                   | FLEXR_ECN          | ECC 1-bit error correction notification           |                                           | latched             | High     | _                      |

| Non-<br>critical<br>fault | Source      | Signal                    | Short/long/<br>none default<br>func reset | Fault<br>management | Polarity | Set/clear<br>injection |

|---------------------------|-------------|---------------------------|-------------------------------------------|---------------------|----------|------------------------|

| NCF[20]                   | FLEXR_NCE   | ECC not correctable error | —                                         | latched             | High     | _                      |

| NCF[21]                   | MC_ME       | Software device reset     | —                                         | latched             | High     | —                      |

| NCF[22]                   | BP_BALLAST0 | Bypass Ballast0           | —                                         | latched             | High     | —                      |

| NCF[23]                   | BP_BALLAST1 | Bypass Ballast1           | —                                         | latched             | High     | _                      |

| NCF[24]                   | BP_BALLAST2 | Bypass Ballast2           | —                                         | latched             | High     | _                      |

| NCF[25]                   | —           | —                         | —                                         | —                   | —        | —                      |

| NCF[26]                   | —           | —                         | —                                         | —                   | —        | _                      |

| NCF[27]                   | _           | —                         | —                                         | —                   | —        | _                      |

| NCF[28]                   | —           | —                         | —                                         | —                   | —        | _                      |

| NCF[29]                   | —           | —                         | —                                         | —                   | —        | _                      |

| NCF[30]                   | —           | —                         | —                                         | —                   | —        | —                      |

| NCF[31]                   | —           | —                         | —                                         | —                   | —        | _                      |

### Table 3. Non-critical fault (continued)

# 5 FCCU settings

Normally the FCCU is configured at start up. In any case, it is possible to manage some registers only in CONFIG state (according to IP Specification Block guide).

## 5.1 Example 1: FCCU critical fault injection (no NMI assertion)

We show the FCCU functionality by means of an example which uses fault injection (with fake functionality), in order to show the FCCU reaction. The example is without NMI assertion. The fault is checked and cleared by looking in the CFSx registers.

#### **Example description**

- Put FCCU in CONFIG state: set registers

- Return to NORMAL state by means of a procedure or by allowing timer out to elapse

- Inject (fake) faults

- After RESET (by RGM), verify, in SAFE state (without NMI), which fault was detected (FCCU\_CFS0 register)

- Clear the FCCU\_CFS0 register (by suitable procedure)

#### Example procedure

- After reset the FCCU automatically enters NORMAL state.

- Configure FCCU in CONFIG with Dual-rail Encoding Protocol.

- Write the key to the FCCU\_CTRLK register [OP1].

- Write the FCCU\_CTRL register (operation OP1).

- Emulate all (fake) SW/HW faults.

- FCCU\_CFG: (Configuration Register)

- SM = 1 (EOUT protocol (dual-rail, time-switching) fast switching mode)

- PS = 1 (fcc\_eout[1] active low, fcc\_eout[0] active low)

- FOM = 000 (Fault Output Mode selection = Dual-Rail (default state) [fccu\_eout[1:0] = outputs])

- FOP=0 (Fault Output Prescaler = Input clock frequency (ipg\_clk\_safe clock) is divided by 2048)

- Enter NORMAL state.

- Write the key into the FCCU\_CTRLK register [OP2].

- Write the FCCU\_CTRL register (operation OP2).

- Set fault by FCCU\_CFF registers (RESET assertion by RGM).

- Read and verify FCCU\_CFS0..3 by means of procedure (NMI was masked).

- Clear HW/SW faults from FCCU\_CFS0..3 by means of procedure.

#### Code

After the core initialization in main function the code is (NMI masked):

```

if (ME.GS.B.S_CURRENT_MODE == 2) { /* SAFE MODE */

if((FCCU_Clear_CRITICAL_Fault()) == PASS){

/* Test PASS */

}else{

while(1);

/* Test FAIL */

}

/* DRUN MODE */

}else{

/* ----- Test INIT ----- */

if((tc0 INIT()) == PASS) {

/* ----- Fake Fault ----- */

FCCU.CFF.R = 0; /* First Fault injection */

}else{

while(1);

/* Test FAIL */

}

/* -----END Test INIT ----- */

}

```

#### Description

At the beginning the microcontroller is in DRUN mode, the "else" condition is asserted, by  $tc0_INIT$  procedure. In the  $tc0_INIT$ , the FCCU will be configured. When the injection fault is asserted (FCCU.CFF.R = 0), the system will reset. After the start up, in main function the system is in SAFE mode (the NMI is masked). Then the "if" condition is asserted, and all faults are cleared.

#### 5.1.1 FCCU init

}

uint16\_t tc0\_INIT(void) {

### 5.2 Example 2: FCCU critical fault injection (NMI assertion)

In this example we show the fault injection (with fake functionality), in order to show an FCCU reaction. The example is with NMI assertion. The fault is checked and cleared inside the NMI subroutine by looking in the CFSx registers.

#### **Example description**

- Put FCCU in CONFIG state: set registers.

- Return to NORMAL state: by means of procedure or by allowing timer out to elapse.

- Inject (fake) faults.

- Verify that in SAFE state (NMI management), and that fault is detected (FCCU\_CFS0 register).

- Clear the FCCU\_CFS0 register (by suitable procedure).

#### Example procedure

- After the reset the FCCU automatically enters NORMAL state.

- Configure FCCU in CONFIG with Dual-rail Encoding Protocol.

- Write the key to the FCCU\_CTRLK register [OP1].

- Write the FCCU\_CTRL register (operation OP1).

- Emulate all (fake) SW/HW faults.

- FCCU\_CFG\_TO = 0x7 (Set Timer Out)

- FCCU\_CFG: (Configuration Register)

- SM = 1 (EOUT protocol (dual-rail, time-switching) fast switching mode)

- PS = 1 (fcc\_eout[1] active low, fcc\_eout[0] active low)

- FOM = 000 (Fault Output Mode selection = Dual-Rail (default state) [fccu\_eout[1:0] = outputs])

- FOP = 0 (Fault Output Prescaler= Input clock frequency (ipg\_clk\_safe clock) is divided by 2048)

- FCCU\_CFS\_CFG0 = 0 (No reset reaction)

- Enter NORMAL state.

- Write the key to the FCCU\_CTRLK register [OP2].

- Write the FCCU\_CTRL register (operation OP2).

- Set fault by FCCU\_CFF registers (no RESET assertion).

- NMI assertion: NMI\_ISR managing

- Read and verify FCCU\_CFS0..3 by means of procedure.

- Clear HW/SW faults from FCCU\_CFS0..3 by means of procedure.

#### Code

After the core initialization in main function the code is:

#### Description

First the microcontroller is in DRUN mode, the "if" condition is asserted, by the tc0\_INIT procedure. The FCCU is configured in the tc0\_INIT. Next the CF 20 is injected (in order to generate an NMI, without RESET). When the injection fault is asserted (FCCU.CFF.R = 20), the system asserts NMI. In NMI ISR the fault is cleared and the system enters RUN mode.

### 5.2.1 FCCU init

```

uint16_t tc0_INIT(void) {

/* ----- CONFIG State ----- */

FCCU.CFG_TO.R = 0x7; /* Set Timer Out CCONFIG STATE to 8.192 ms */

FCCU CONFIG STATE();/* CONFIG state */

FCCU.CFG.B.SM = 1; /* EOUT protocol (dual-rail, time-switching) fast switching

mode*/

FCCU.CFG.B.PS = 1; /* fcc eout[1] active low, fcc eout[0] active low */

FCCU_CFG_FOM_Config(CFG_FOM0); /* CFG_FOM0 = Dual-Rail (default state)

[fccu_eout[1:0] = outputs] */

FCCU_CFG_FOP_Config(0); /* Fault Output Prescaler= Input clock frequency

(ipg_clk_safe clock) is divided by 2 x 1024 */

/* Set the Critical Fault reaction */

FCCU.CFS CFG0.R = 0; /* No reset reaction */

/* ----- NORMAL State ----- */

FCCU NORMAL STATE();/* NORMAL state */

return (PASS);

}

```

### 5.3 Example 3: FCCU - Non-critical fault injection

In this example we show fault injection (with fake functionality), in order to show an FCCU reaction. The example is with FAULT\_ISR assertion. The fault is checked and cleared in FAULT\_ISR subroutine by looking in the CFSx registers.

#### **Example description**

- Put FCCU in CONFIG state: set registers.

- Return to NORMAL state: by means of procedure or by allowing timer out to elapse.

- Inject (fake) faults (NCF N. 12).

- Verify that in RUN state (FAULT\_ISR management), and that fault is detected (FCCU\_NCFS0 register).

- Clear the FCCU\_NCFS0 register (by suitable procedure).

#### **Example procedure**

- After the reset the FCCU automatically enters NORMAL state.

- Configure FCCU in CONFIG with Dual-rail Encoding Protocol.

- Write the key to the FCCU\_CTRLK register [OP1].

- Write the FCCU\_CTRL register (operation OP1).

- Emulate all (fake) SW/HW faults.

- FCCU\_CFG\_TO=0x7 (Set Timer Out)

- FCCU\_CFG: (Configuration Register)

- SM=1 (EOUT protocol (dual-rail, time-switching) fast switching mode)

- PS=1 (fcc\_eout[1] active low, fcc\_eout[0] active low)

- FOM=000 (Fault Output Mode selection= Dual-Rail (default state) [fccu\_eout[1:0]= outputs])

- FOP=0 (Fault Output Prescaler= Input clock frequency (ipg\_clk\_safe clock) is divided by 2 x 1024)

- FCCU\_NCFS\_CFG0 = 0 (No reset reaction)

- FCCU\_NCFE0 = 0xFFFFFFF; (Enable FCCU to move to ALARM or FAULT State)

- FCCU\_NCF\_TOE0 = 0xFFFFFFF; (FCCU moves into the ALARM state if the respective fault is enabled (NCFEx is set))

- FCCU\_NCF\_TO = 0xFFFFFFF; (Non-critical fault time-out)

- Enter NORMAL state.

- Write the key to the FCCU\_CTRLK register [OP2].

- Write the FCCU\_CTRL register (operation OP2).

- Set fault by FCCU\_NCFF registers (NCF N. 12).

- ISR assertion: FAULT\_ISR managing (ISR N. 250)

- Read and verify FCCU\_NCFS0..3 by means of procedure.

- Clear HW/SW faults from FCCU\_NCFS0..3 by means of procedure.

#### Code

After the core initialization in main function the code is:

#### Description

At the beginning the micro is in DRUN mode. The FCCU is configured in the tc1\_INIT. Next the NCF 12 is set. When the injection fault is asserted (FCCU.NCFF.R = 12), the system asserts FAULT ISR. In FAULT ISR the fault is cleared and the system enters RUN mode.

### 5.4 LOCK FCCU configuration

The configuration state is used to modify the default configuration of the FCCU only. A subset of the FCCU registers, dedicated to defining the FCCU configuration (global configuration, reactions to fault, time-out, non-critical fault masking), can be accessed in write mode, in the CONFIG state only.

The CONFIG state is accessible in NORMAL state only and only if the configuration is not locked. The configuration lock can be disabled only by a global reset of the FCCU. To lock the FCCU see *Section A.2.3* 0 function.

### 5.5 Hardware: XPC56XL minimodule

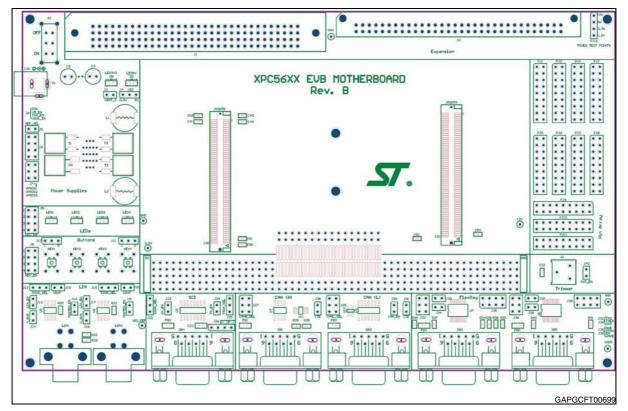

The examples are executed by XPC56EL minimodule, using the motherboard. The motherboard provides common functionality used in most applications, such as serial communication interface, CAN transceivers, SPI bus, I/O pins, power supply, buttons and LEDs. The minimodule provides a minimum setup for the microprocessor, for example, socket for the processor, crystal oscillator and debug interface. *Figure 2* displays the XPC56XL minimodule layout.

#### Figure 2. XPC56EL minimodule

# Appendix A Redundancy and functions

### A.1 Path redundancy on critical error reaction

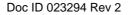

All faults detected are reported to the central Fault Collection and Control Unit (FCCU) and RGM. Depending on the particular fault, the FCCU puts the device into the appropriate configured Fail-Safe state. This prevents propagation of faults to system level.

Critical errors detected normally are forwarded independently by each channel to RGM and FCCU. The state of the RGM is forwarded to the FCCU. The FCCU forwards an additional reset request to the RGM. This strategy is used as it drastically decreases the common mode failure on the Reset path.

For some faults:

- The fault is triggered to the FCCU.

- FCCU reacts independently of the RGM.

- Fault reaction depends on the FCCU settings.

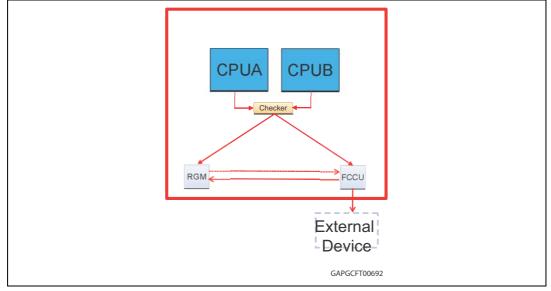

#### Figure 4. RGM/FCCU – no dual path faults

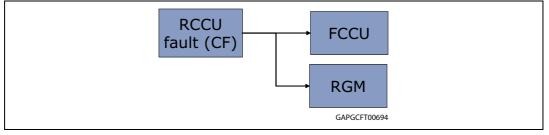

For some faults (Critical Faults):

- RGM and FCCU react to the fault independently.

- RGM resets the device (LR).

- FCCU is not reset by RGM reset.

- FCCU takes some action depending on the configuration.

- FCCU signals the fault externally.

- after the reset the device enters SAFE mode.

- NMI

#### Figure 5. RGM/FCCU – dual path faults (critical faults)

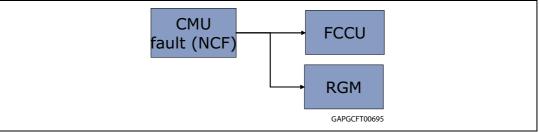

For some faults (Non-critical Faults):

- RGM and FCCU react to the fault independently/

- RGM reaction is configurable.

- IRQ

- FCCU takes some action depending on the configuration.

- FCCU waits for the NCF timeout.

- FCCU signals the fault externally.

- device enters SAFE mode

- NMI

#### Figure 6. RGM/FCCU – dual path faults (Non-critical Faults)

### A.2 General purpose function

Below are some general purpose functions, settinf and clearing registers.

#### A.2.1 Config state

uint32\_t FCCU\_CONFIG\_STATE(void) {

}

### A.2.2 Normal state

uint32\_t FCCU\_NORMAL\_STATE(void) {

#### A.2.3 Lock FCCU

}

uint32\_t FCCU\_LOCK(void) {

}

#### A.2.4 Read status register

```

uint32_t FCCU_CFS_Read(uint32_t CFS_number, uint32_t* CFS_Value) {

uint32_t exit_value= 0;/* Returned value = ERROR */

uint32_t Reg_Selection = 0;/* Register Selection [0..3] */

if (CFS_number <= 127) {

FCCU.CTRL.B.OPR = CTRL OPR9; /* Set the OP9 */

while(FCCU.CTRL.B.OPS != CTRL_OPS3); /* wait for the completion of the

operation */

Reg Selection = (CFS number/32); /* INT(CFS number/32)*/

switch (Reg_Selection) {

case 0 : *CFS_Value = (FCCU.CFS0.R >> (CFS_number%32)) & 1;

/* Read the critical fault latched state \star/

break;

case 1 : *CFS_Value = (FCCU.CFS1.R >> (CFS_number%32)) & 1;

/* Read the critical fault latched state */

break;

case 2 : *CFS Value = (FCCU.CFS2.R >> (CFS number%32)) & 1;

```

```

/* Read the critical fault latched state */

break:

case 3 : *CFS Value = (FCCU.CFS3.R >> (CFS number%32)) & 1;

/* Read the critical fault latched state */

break;

default: *CFS_Value = (FCCU.CFS3.R >> (CFS_number%32)) & 1;

/* Read the critical fault latched state */

break;

}

/* Returned value = SUCCESS */

exit value = 1;

}

else {

/* ERROR*/

};

return(exit_value);

```

#### A.2.5 Clear fault

}

```

uit32_t FCCU_CFS_Clear(uint32_t CFS_number) {

/* Register Selection [0..3] */

uint32_t Reg_Selection = 0;

/* Support variable */

uint32_t Support = 0;

uint32_t CFS_Value;

if (CFS_number <= 127) {

Reg_Selection = (CFS_number/32); /* INT(CFS_number/32)*/

switch (Reg Selection) {

case 0 : Support = FCCU.CF_CFG0.R;

break;

case 1 : Support = FCCU.CF CFG1.R;

break;

case 2 : Support = FCCU.CF_CFG2.R;

break;

case 3 : Support = FCCU.CF_CFG3.R;

break;

default: Support = FCCU.CF CFG3.R;

break;

}

Support = (Support >> (CFS_number%32)) & 0x1;

if (Support == CFG SW) { /* SW recoverable fault*/

do{

switch (Reg_Selection) {

case 0 : FCCU.CFK.R = CFK_Key; /* set the Critical fault key */

FCCU.CFS0.R = (uint32_t) (1 << (CFS_number%32));</pre>

/* reset the critical fault state */

break;

case 1 : FCCU.CFK.R = CFK Key; /* set the Critical fault key */

FCCU.CFS1.R = (uint32_t) (1 << (CFS_number%32));</pre>

/* reset the critical fault state */

break;

case 2 : FCCU.CFK.R = CFK_Key; /* set the Critical fault key */

FCCU.CFS2.R = (uint32 t) (1 << (CFS number%32));</pre>

/* reset the critical fault state */

break;

case 3 : FCCU.CFK.R = CFK_Key; /* set the Critical fault key */

FCCU.CFS3.R = (uint32 t) (1 << (CFS number%32));</pre>

/* reset the critical fault state */

break:

default: FCCU.CFK.R = CFK Key; /* set the Critical fault key */

FCCU.CFS3.R = (uint32_t) (1 << (CFS_number%32));</pre>

/* reset the critical fault state */

```

```

break;

}

while(FCCU.CTRL.B.OPS != CTRL OPS3); /* wait for the completion of

the operation */

if ( FCCU CFS Read(CFS number, &CFS Value)) {

if (CFS_Value == 0) {

exit_value = 1;  /* Returned value = SUCCESS */

}

}

}while(CFS Value==1);

}

else {

/* HW recoverable fault*/

}

};

return(exit_value);

```

A.2.6 Clear all critical faults

}

```

uint16 t FCCU Clear CRITICAL Fault(void) {

tU32 CFS_Value;

uint8_t tc0_error = 0;/* Error counter */

/* ----- Read State ----- */

if(FCCU_CFS_Read(Num_Fault, &CFS_Value)){

if (CFS_Value == 1) {/* The fault was latched correctly */

if((RGM.FES.R & 0x0080) == 0x0080){

/* Retun from FCCU SAFE mode reset */

FCCU_CFS_Clear(Num_Fault); /* Clear the fault by procedure */

RGM.FES.R = 0xFFFF; /* Clear FER register */

ME.MCTL.R = (DRUN_MODE << 28 \mid 0x00005AF0); /* Mode & Key */

ME.MCTL.R = (DRUN_MODE << 28 | 0x0000A50F); /* Mode & Key *

/* Wait for mode entry to complete */

while(ME.GS.B.S_MTRANS==1);

/* Check DRUN mode has been entered */

while(ME.GS.B.S_CURRENT_MODE!=DRUN_MODE);

tc0 error = 0;

/* Error counter */

}else{

/* No fault was latched */

}

}else{

/* Read State ERROR */

if(tc0_error == 0)

return(PASS);

return(FAIL);

```

```

}

```

A.2.7 Clear all Non-critical faults

}

}

```

/* Retun from FCCU SAFE mode reset */

FCCU_NCFS_Clear(Num_Fault); /* Clear the fault */

RGM.FES.R = 0xFFFF; /* Clear FER register */

ME.MCTL.R = (DRUN_MODE << 28 | 0x00005AF0);/* Mode & Key */

ME.MCTL.R = (DRUN_MODE << 28 | 0x0000A50F);/* Mode & Key */

/* Wait for mode entry to complete */

while(ME.GS.B.S_MTRANS==1);

/* Check DRUN mode has been entered */

while(ME.GS.B.S_CURRENT_MODE!=DRUN_MODE);

/* Error counter */

tc1 error = 0;

}else{

/* Not NON-Critical fault was latched */

}

}else{

/* Read State ERROR */

}

}

if(tc1_error == 0)

return(PASS);

return(FAIL);

```

#### A.2.8 Read FCCU - state machine

```

uint32_t FCCU_STATUS_Read(uint32_t* STATUS_Value) {

uint32_t exit_value= 0; /* Returned value = ERROR */

FCCU.CTRL.B.OPR = CTRL OPR3; /* Set the OP3 */

while(FCCU.CTRL.B.OPS != CTRL_OPS3); /* wait for the completion of

the operation */

*STATUS Value = FCCU.STAT.R; /* Read the STATUS Register */

exit value = 1;

/* Returned value = SUCCESS */

return(exit value);

```

#### A.2.9 Non-critical fault - enable

```

uint32_t FCCU_NCF_Enable(uint32_t NCFE_number, uint32_t NCFE_Value) {

uint32_t exit_value= 0; /* Returned value = ERROR */

uint32_t Reg_Selection = 0;/* Register Selection [0..3] */

if (NCFE_number <= 127) {

Reg Selection = (NCFE number/32); /* INT(NCFE number/32)*/

if (NCFE Value == NCFE En) {

switch (Reg Selection) {

case 0 :

FCCU.NCFE0.R |= (uint32 t) (NCFE En << (NCFE number%32));</pre>

/* Enable the non-critical fault */

break;

FCCU.NCFE1.R |= (uint32_t) (NCFE_En << (NCFE_number%32));</pre>

case 1 :

/* Enable the non-critical fault */

break;

FCCU.NCFE2.R |= (uint32 t) (NCFE En << (NCFE number%32));</pre>

case 2 :

/* Enable the non-critical fault */

break;

case 3 : FCCU.NCFE3.R |= (uint32 t) (NCFE En << (NCFE number%32));</pre>

/* Enable the non-critical fault */

break;

FCCU.NCFE3.R |= (uint32 t) (NCFE En << (NCFE number%32));</pre>

default:

/* Enable the non-critical fault */

break;

}

}else{

```

```

switch (Reg Selection) {

case 0 : FCCU.NCFE0.R &= (uint32_t) ~(NCFE_En << (NCFE_number%32));</pre>

/* Disable the non-critical fault */

break;

case 1 : FCCU.NCFE1.R &= (uint32 t) ~(NCFE En << (NCFE number%32));</pre>

/* Disable the non-critical fault */

break:

case 2 : FCCU.NCFE2.R &= (uint32_t) ~(NCFE_En << (NCFE_number%32));</pre>

/* Disable the non-critical fault */

break:

case 3 : FCCU.NCFE3.R &= (uint32 t) ~(NCFE En << (NCFE number%32));</pre>

/* Disable the non-critical fault */

break;

default: FCCU.NCFE3.R &= (uint32 t) ~(NCFE En << (NCFE number%32));</pre>

/* Disable the non-critical fault */

break:

}

}

};

return(exit value);

}

```

#### A.2.10 NCF - normal to alarm - read state

```

uint32_t FCCU_NAFS_Read(uint32_t* NAFS_Value) {

uint32_t exit_value= 0; /* Returned value = ERROR */

FCCU.CTRL.B.OPR = CTRL OPR4; /* Set the OP4 */

while(FCCU.CTRL.B.OPS != CTRL_OPS3); /* wait for the completion of the

operation */

*NAFS Value = FCCU.NAFS.R; /* Read the NAFS latched state */

exit value = 1;

/* Returned value = SUCCESS */

return(exit value);

```

#### A.2.11 NCF - normal to alarm - clear state

```

uint32_t FCCU_NAFS_Clear(void) {

uint32_t exit_value= 0; /* Returned value = ERROR */

FCCU.CTRL.B.OPR = CTRL OPR13; /* Set the OP13 */

while(FCCU.CTRL.B.OPS != CTRL_OPS3); /* wait for the completion of the

operation */

exit_value = 1;

/* Returned value = SUCCESS */

return(exit value);

}

```

#### A.2.12 **IRQ** status

}

```

uint32 t FCCU IRQ Status(uint32 t CFG TO STAT, uint32 t* ALRM STAT,

uint32 t* NMI STAT){

uint32 t exit value= 0; /* Returned value = ERROR */

if (CFG TO STAT == 1) {

FCCU.IRQ_STAT.B.CFG_TO_STAT |= 1;/* Clear the Configuration

Time Out Error */

}else{

FCCU.IRQ_STAT.B.CFG_TO_STAT &= ~(1);/* No effect on bit */

}

*ALRM_STAT = FCCU.IRQ_STAT.B.ALRM_STAT;/* Read Alarm Interrupt Status */

*NMI STAT = FCCU.IRQ STAT.B.NMI STAT;/* Read NMI Interrupt Status */

```

```

exit_value= 1;

return(exit_value);

}

```

### A.3 General purpose functions

Two examples have been developed to show the features of FCCU. The examples have been implemented on the XPC56xxMB. The XPC56xxMB was plugged to XPC56EL minimodule with SPC56ELX 144 pins.

Figure 7. XPC56xxMB mother board

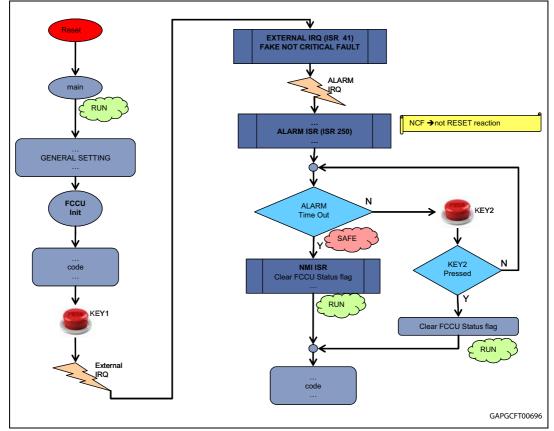

### A.3.1 Example N1: fake NCF by external IRQ

In this example we show the NCF fault injection (by external IRQ functionality), in order to show an FCCU reaction. The example includes ALARM and NMI ISR assertion. The fault is checked and cleared with a subroutine by looking in the NCFSx registers.

Two external buttons have been used to inject and clear the NCF (KEY 1 and KEY 2) and LED1 on the motherboard has been used to view the fault status. To connect the two buttons to input pins (interrupt), we need to connect J8 pin 1B to JP9 pin 1, and J8 pin 2B to JP9 pin 2.

The flow is:

- Press key1: to inject asynchronous external IRQ (ISR)

- External IRQ (ISR)

- Blinking LED1

- Fake NCF

- FCCU STATE = ALARM -> ALARM IRQ (ISR)

- Alarm IRQ (ISR)

- Wait for ALARM-time-out (5 s) or check External push button (KEY2)

- If alarm-timeout

- FCCU STATE = FAULT -> NMI IRQ (without RESET):

- DEVICE STATE = SAFE

- LED1 off

- Clear FCCU FAULT and return to main

- If KEY 2 pressed

- LED1 off

- Clear FCCU FAULT and return to main

#### Figure 8. NCF injection flow

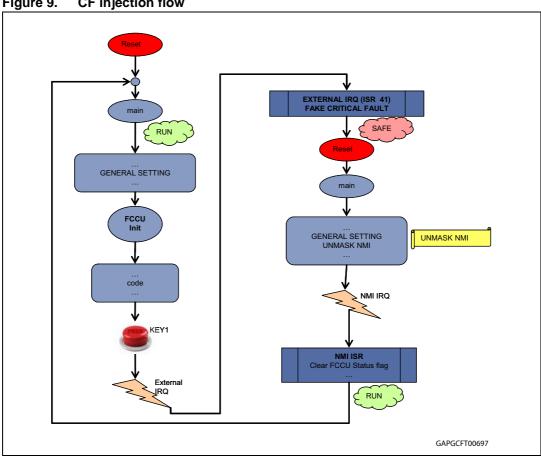

### A.3.2 Example N2: fake CF by external IRQ

In this example we show the CF fault injection (by external IRQ funtionality), in order to show an FCCU reaction. The example includes NMI ISR assertion. The fault is checked and cleared with subroutine by looking in the CFSx registers.

This example employs the CF external button (KEY 1) to inject and clear, and the LED1 on the motherboard to view the fault. To connect the button to input pins (interrupt), we need to connect J8 pin 1B to JP9 pin 1.

The flow is:

- Blink LED1

- Press KEY1: to inject asynchronous external IRQ (ISR)

- External IRQ (ISR)

- Fake CF

- LED1 off

- FCCU STATE = FAULT

- DEVICE STATE = SAFE

- RESET

- NMI IRQ (ISR)

- After RESET: unmask NMI

- NMI IRQ (ISR)

- Clear FCCU FAULT and return to main

Figure 9. **CF** injection flow

# Appendix B Further information

## B.1 Acronyms

#### Table 4. Acronyms

| Acronym | Name                              |

|---------|-----------------------------------|

| CRC     | Cyclic redundancy check           |

| DMA     | Direct memory access              |

| FCCU    | Fault control and collection unit |

| INTC    | Interrupt controller              |

| MCU     | Microcontroller unit              |

| PIT     | Periodic interrupt timer          |

| TCD     | Transfer control descriptor       |

# **Revision history**

| Table 5. | Document revision history |

|----------|---------------------------|

|----------|---------------------------|

| Date        | Revision | Changes             |

|-------------|----------|---------------------|

| 02-Aug-2012 | 1        | Initial release.    |

| 17-Sep-2013 | 2        | Updated disclaimer. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com