# AN11130

# Bias module for 50 V GaN demonstration boards Rev. 1 — 8 December 2011

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | GaN, bias                                                                                                                                                                                                                 |

| Abstract | This application note describes a bias controller module for GaN HEMT RF power transistors. It provides constant quiescent drain current with temperature, special bias and power sequencing, and overcurrent protection. |

**AN11130 NXP Semiconductors**

# Bias module for 50 V GaN demonstration boards

# **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| v.1 | 20111208 | initial version |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### Bias module for 50 V GaN demonstration boards

# 1. Introduction

GaN HEMT RF power transistors require temperature-compensated gate bias voltages, similar to LDMOS devices, to maintain constant quiescent drain currents with temperature. They are depletion mode devices requiring special bias and power sequencing compared to LDMOS devices. This application note describes a bias controller module which provides these functions, and overcurrent protection.

# 2. Bias sequencing

The most important consideration for DC with GaN HEMTs, is the bias sequencing. There are two issues to consider:

- Never apply drain voltage when the gate is at 0 V, as the device draws excessive drain current. Thus, any GaN bias controller must include sequenced drain voltage switching.

- For a given V<sub>GS</sub>, GaN HEMTs are likely to be potentially unstable at lower V<sub>DS</sub>.

Therefore, decrease the gate voltage to below the pinch-off voltage V<sub>P</sub> (such as -3 V) while the drain voltage is being turned on and off.

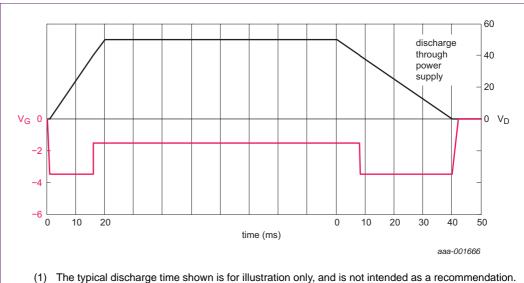

<u>Figure 1</u> illustrates recommended power-up and power-down sequences for the drain and gate voltages.

It is important that V<sub>GS</sub> is held at a voltage of less than V<sub>P</sub> until V<sub>DS</sub> is less than approximately 10 V.

Fig 1. Gate and drain voltage sequence

#### Bias module for 50 V GaN demonstration boards

# 3. Gate current

Because the GaN HEMT gate terminal is a Schottky diode, bias generators must provide significant amounts of both positive and negative gate current:

- GaN HEMTs have higher gate leakage currents than comparable LDMOS devices.

The negative gate current can be as high as 500 μA/mm of gate periphery at elevated junction temperatures; the gate current evaluates to –5 mA for a 100 W device operating at 200 °C junction temperature.

- When the device is driven into saturation, rectified positive gate current flows into the gate diode. At heavy RF compression, this gate current can exceed 1 mA/mm of gate periphery causing a possible gate current of 30 mA for a 100 W device.

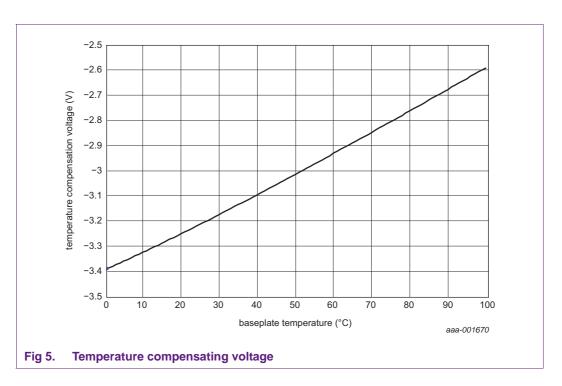

# 4. Temperature compensation

Similar to LDMOS devices, the gate threshold voltage for GaN devices is approximately proportional to temperature. The gate threshold voltage is the voltage required to maintain a constant quiescent drain current, which for NXP Semiconductors GaN devices, is about +1 mV/ $^{\circ}$ C junction temperature. However, practical temperature compensation circuits are obliged to monitor case temperature, where the temperature change is typically only half the junction temperature change. Thus, the bias controller must increase V<sub>GS</sub> by about +2 mV/ $^{\circ}$ C.

# 5. Summary

The characteristics of the bias controller module described in the following section are summarized in Table 1.

Table 1. Summary of bias controller characteristics

| Drain voltage                         | 12 V to 80 V [1] |

|---------------------------------------|------------------|

| Gate voltage                          | −3 V to −1 V [1] |

| Gate voltage adjustment range         | 700 mV typical   |

| Gate voltage temperature compensation | +2 mV/°C typical |

| Gate current, negative                | ≤ −10 mA         |

| Gate current, positive                | ≥ 100 mA         |

| Gate voltage ripple                   | ≤ 2 mV (p-p)     |

| Switched drain current                | ≥ 40 A [2]       |

<sup>[1]</sup> Resistor values may have to be changed for part of range.

<sup>[2]</sup> Dependent upon PCB layout.

Bias module for 50 V GaN demonstration boards

# 6. Circuit description

# 6.1 Negative voltage generation

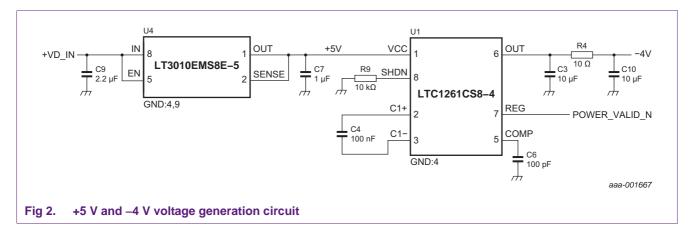

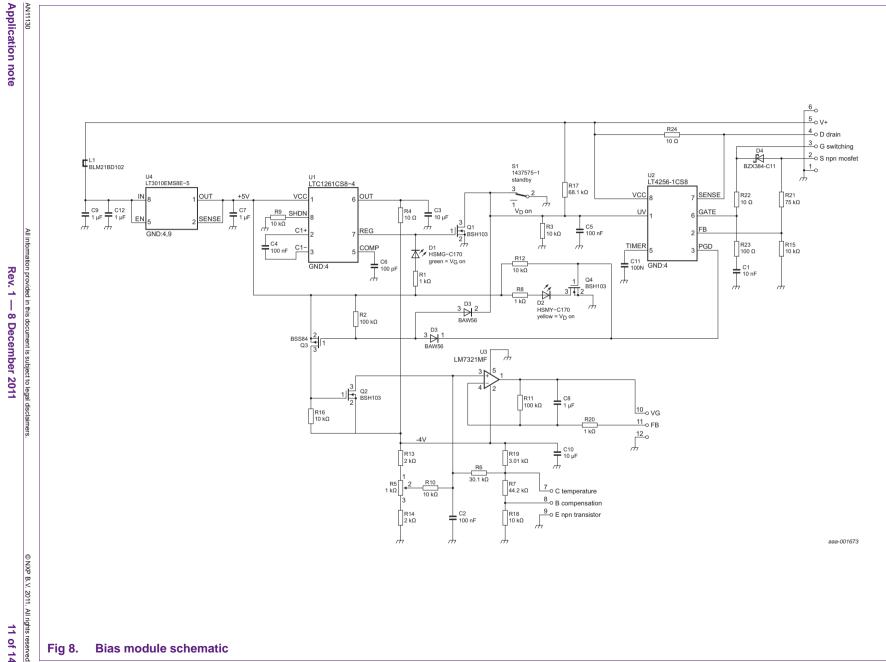

The bias controller uses a switched-capacitor voltage inverter, U1, to generate a regulated –4 V from a single positive supply. The +5 V supply is generated from the high-voltage drain supply by linear regulator U4.

U1 operates at a switching frequency of approximately 550 kHz; C3, R4, and C10 are used to reduce output ripple to less than 2 mV (p-p).

When the output voltage is within 5 % of the -4 V set value, the REG output goes LOW. The REG output LOW signal acts as an active-LOW (power valid) signal to enable drain power to the GaN device.

# 6.2 Drain voltage switching

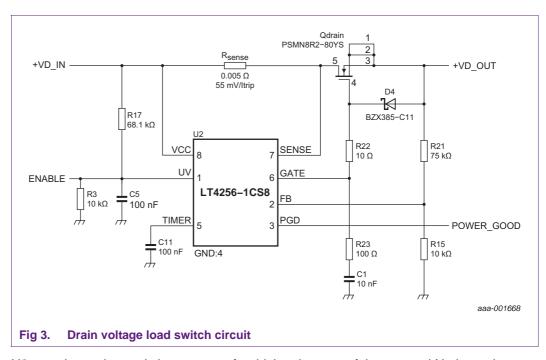

Most lower power HEMT bias controllers use a P-channel power MOSFET as the drain voltage load switch. This has the advantage of simplicity, often requiring nothing more than level-shifting transistors between the voltage inverter 'power valid' signal and the MOSFET gate. However, as load currents increase above 2 A to 5 A, the required MOSFET becomes large and expensive. Consequently, this bias controller uses a common hot-swap controller IC, U2 to drive an inexpensive N-channel MOSFET.

#### Bias module for 50 V GaN demonstration boards

U2 contains an internal charge pump for driving the gate of the external N-channel MOSFET, Qdrain. It also includes a programmable ramp-up rate, and optional overcurrent fault detection and foldback current limiting. If the voltage drop across sense resistor Rsense exceeds 55 mV, U2 disconnects power from the drain, and leaves it latched off until power is cycled.

Qdrain is a low-cost high-density TrenchMOS device in a small power SO8 package. It has a typical on-resistance of less than 10 m $\Omega$  and a drain current limit of more than 80 A.

# 6.3 Temperature compensation

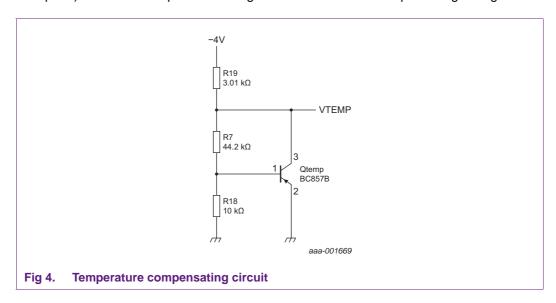

The bias controller uses a small-signal PNP transistor (mounted in contact with the baseplate) to monitor temperature and generate a +8 mV/°C compensating voltage.

AN11130

### Bias module for 50 V GaN demonstration boards

# 6.4 Gate voltage adjustment

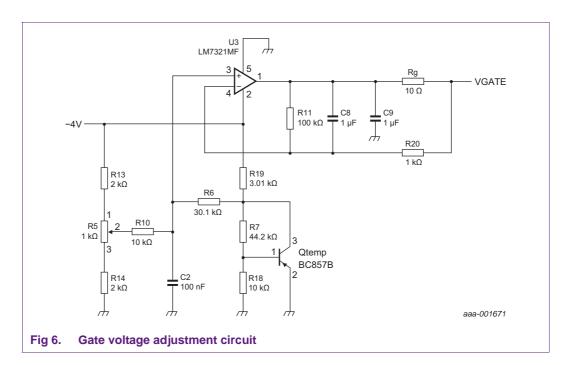

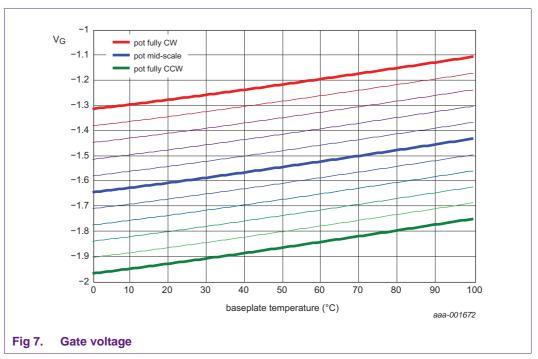

A variable voltage derived from the -4 V supply is summed with the temperature monitor voltage to generate a temperature-compensated gate voltage. R13 and R14 are selected to set the desired gate voltage trim range, and R6 is selected to provide the desired amount of temperature compensation. Figure 6 shows typical values for  $V_{GS} = -1.6$  V.

U3 is a dual rail-to-rail high-current operational amplifier chosen because it is stable into any capacitive load. It can deliver more than 100 mA of output current to meet the positive gate current requirements of most GaN HEMTs.

### Bias module for 50 V GaN demonstration boards

The output impedance of the bias source is low (less than 1  $\Omega$ ) because of the feedback around operational amplifier U3. However, HEMT applications usually require a series gate resistor of 5  $\Omega$  to 20  $\Omega$ , instead of a bias inductor, to ensure low-frequency device stability.

Because the GaN HEMT quiescent gate current can increase at high temperatures, a significant voltage drop can be developed across this gate resistor, increasing  $V_{GS}$  by 200 mV or more. This can be a serious problem because the increased gate voltage can push the HEMT operating point into a region of instability or even cause thermal runaway.

#### Bias module for 50 V GaN demonstration boards

One solution is to provide DC feedback from the HEMT gate terminal to the operational amplifier inverting input, allowing it to compensate for voltage dropped across gate resistor Rg. Feedback through R20 compensates for voltage dropped across Rg. To minimize RF non-linearity and memory effects, make sure that 1 / (R20  $\times$  C8) is less than the lowest modulation frequency of the RF signal.

#### 6.5 Resistor value selection

The resistor values in the schematic are for a 50 V device with a nominal  $V_{GS}$  of -2.1 V, +2 mV/°C  $V_{GS}$  temperature coefficient, and 11 A  $I_{DS}$  overcurrent sense. Other nominal operating conditions may require resistor value changes:

- R17 determines the supply voltage at which the drain is connected. R17 = R3 ( $V_D$  / 4 - 1), so  $V_D$  = 31 V with the 68.1 k $\Omega$  value in the design.

- R21 determines the supply voltage at which operating  $V_{GS}$  is applied. R21 = R15 ( $V_D$  / 4.45 – 1), so  $V_D$ (good) = 38 V with the 75.0 k $\Omega$  value in the design.

- Rsense determines the foldback current limit.  $I_{LIMIT} = 0.055$  / Rsense, so  $I_{LIMIT} = 11$  A with the 5 m $\Omega$  value in the design.

#### 6.6 Full schematic

The complete schematic of the bias controller combines the preceding subcircuits with 'glue circuitry' and several (possibly optional) additional convenience features.

- LEDs D1 and D2 provide visual indication of valid gate and drain voltages.

- Switch S1 allows the GaN amplifier to be placed easily in 'standby', where the nominal gate voltages are applied, but drain power is disconnected.

- When S1 is set to 'Vd on' and the drain supply is not fully on (ramping up or down), diode D3 and MOSFET Q3 turn on MOSFET Q2, pulling the gate voltage down to -4 V.

Table 2. Bias module bill of materials

| Component       | Description                     | Value           | Remarks        |

|-----------------|---------------------------------|-----------------|----------------|

| C9, C12         | capacitor, 100 V 10 % X7R, 1206 | 1 μF            |                |

| C7, C8          | capacitor, 50 V 10 % X7R, 0805  | 1 μF            |                |

| C2, C4, C5, C11 | capacitor, 50 V 10 % X7R, 0805  | 100 nF          |                |

| C6              | capacitor, 50 V 5 % NP0, 0805   | 100 pF          |                |

| C3, C10         | capacitor, 10 V 20 % X7R, 0805  | 10 μF           |                |

| C1              | capacitor, 50 V 10 % X7R, 0805  | 10 nF           |                |

| D1              | LED, green, 0805                |                 |                |

| D2              | LED, yellow, 0805               |                 |                |

| D4              | diode, Zener 11 V 300 mW        |                 | NXP BZX385-C11 |

| D3              | dual diode, common-cathode      |                 | NXP BAV74      |

| L1              | ferrite bead, 200 mA, 0805      | 1000 <u>mH?</u> |                |

| Q1, Q2, Q4      | transistor, N-ch MOS 30 V 0.8 A |                 | NXP BSH103     |

| Q3              | transistor, P-ch MOS 30 V 0.8 A |                 | NXP BSS84      |

| R13, R14        | resistor, 1 % 100 ppm CF, 0805  | 2.00 kΩ         |                |

| R5              | potentiometer, 5t cermet        | 1 kΩ            |                |

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

# Bias module for 50 V GaN demonstration boards

Table 2. Bias module bill of materials

| Component                          | Description                    | Value           | Remarks              |

|------------------------------------|--------------------------------|-----------------|----------------------|

| R19                                | resistor, 1 % 100 ppm CF, 0805 | 3.01 k $\Omega$ |                      |

| R7                                 | resistor, 1 % 100 ppm CF, 0805 | 44.2 kΩ         |                      |

| R3, R9, R10, R12, R15,<br>R16, R18 | resistor, 1 % 100 ppm CF, 0805 | 10.0 kΩ         |                      |

| R6                                 | resistor, 1 % 100 ppm CF, 0805 | 30.1 kΩ         |                      |

| R4, R22, R24                       | resistor, 1 % 100 ppm CF, 0805 | 10.0 kΩ         |                      |

| R1, R8, R20                        | resistor, 1 % 100 ppm CF, 0805 | 1.00 kΩ         |                      |

| R17                                | resistor, 1 % 100 ppm CF, 0805 | 68.1 kΩ         |                      |

| R23                                | resistor, 1 % 100 ppm CF, 0805 | 100 kΩ          |                      |

| R2, R11                            | resistor, 1 % 100 ppm CF, 0805 | 100 kΩ          |                      |

| R21                                | resistor, 1 % 100 ppm CF, 0805 | 75.0 kΩ         |                      |

| S1                                 | switch, SPDT right-angle SMD   |                 | Tyco 1437575-1       |

| U4                                 | voltage regulator, 5 V 100 mA  |                 | Linear LT3010EMS8E-5 |

| U1                                 | switching capacitor inverter   |                 | Linear LTC1261CS8-4  |

| U2                                 | hot swap controller            |                 | Linear LT4256-1CS8   |

| U3                                 | rail-rail opamp                |                 | National LM7321MF    |

# Bias module for 50 V GaN demonstration boards

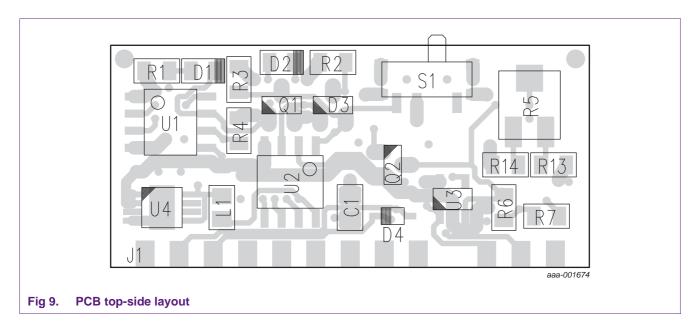

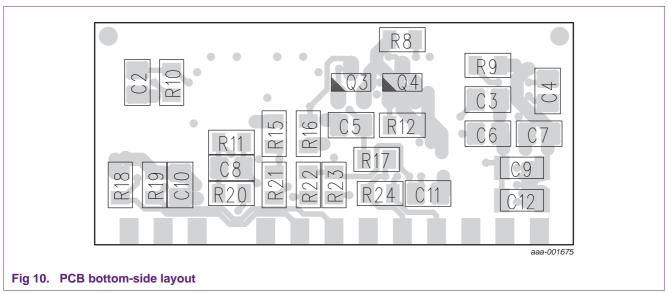

# 7. PCB layout

# 8. Abbreviations

Table 3. Abbreviations

| Acronym | Description                                       |

|---------|---------------------------------------------------|

| LDMOS   | Laterally Diffused Metal Oxide Semiconductor      |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor |

### Bias module for 50 V GaN demonstration boards

# 9. Legal information

## 9.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product

design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 9.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

**Application note**

**AN11130 NXP Semiconductors**

# Bias module for 50 V GaN demonstration boards

# 10. Contents

| 1   | Introduction 3                |

|-----|-------------------------------|

| 2   | Bias sequencing 3             |

| 3   | Gate current 4                |

| 4   | Temperature compensation 4    |

| 5   | Summary 4                     |

| 6   | Circuit description 5         |

| 6.1 | Negative voltage generation 5 |

| 6.2 | Drain voltage switching 5     |

| 6.3 | Temperature compensation 6    |

| 6.4 | Gate voltage adjustment       |

| 6.5 | Resistor value selection 9    |

| 6.6 | Full schematic 9              |

| 7   | PCB layout                    |

| 8   | Abbreviations 12              |

| 9   | Legal information             |

| 9.1 | Definitions                   |

| 9.2 | Disclaimers                   |

| 9.3 | Trademarks 13                 |

| 10  | Contents 14                   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2011.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 8 December 2011 Document identifier: AN11130