# **TLE9222**

TLE9222PX

# FlexRay Transceiver

# **Data Sheet**

Rev. 1.0, 2015-06-12

**Automotive Power**

# **Table of Contents**

| 1       | Overview                                 | 4    |

|---------|------------------------------------------|------|

| 2       | Block Diagram                            | 6    |

| 3       | Pin Configuration                        | 7    |

| 3.1     | Pin Assignment                           |      |

| 3.2     | Pin Definitions and Functions            |      |

| 4       | Functional Description                   | 9    |

| 4.1     | Operation Modes                          | 9    |

| 4.1.1   | BD_Normal Mode                           | . 10 |

| 4.1.2   | BD_Standby Mode                          | . 10 |

| 4.1.3   | BD_Off Condition                         | . 10 |

| 4.2     | Communication Controller Interface       | . 11 |

| 4.3     | Bus Guardian Interface                   | . 12 |

| 4.4     | Host Interface                           | . 12 |

| 4.5     | Power Supply Interface                   | . 14 |

| 4.5.1   | V <sub>CC</sub> Undervoltage Detection   | . 14 |

| 4.5.2   | V <sub>IO</sub> Undervoltage Detection   | . 14 |

| 4.5.3   | Power-up and Power-down                  | . 15 |

| 4.6     | Remote Wake-up                           | . 17 |

| 4.6.1   | Bus Wake-up Patterns                     | . 17 |

| 4.6.2   | Wake-up by Payload                       | . 18 |

| 4.7     | Fail Safe Functions and Flags            | . 19 |

| 4.7.1   | Overtemperature detection                | . 19 |

| 4.7.2   | Bus Error Detector                       | . 19 |

| 4.7.2.1 | RxD-TxD Compare                          | . 20 |

| 4.7.2.2 | Bus Overcurrent                          | . 20 |

| 4.7.3   | Transmitter Time-Out                     | . 20 |

| 4.7.4   | V <sub>IO</sub> Undervoltage-flag        | . 20 |

| 4.7.5   | SPI-error flag                           | . 20 |

| 4.7.6   | Error flag                               | . 20 |

| 4.7.7   | Mode Flags                               |      |

| 4.8     | SPI Interface and Status Register        |      |

| 4.8.1   | Read-out procedure                       | . 22 |

| 5       | General Product Characteristics          |      |

| 5.1     | Absolute Maximum Ratings                 |      |

| 5.2     | Functional Range                         |      |

| 5.3     | Thermal Resistance                       | . 24 |

| 6       | Electrical Characteristics               | . 25 |

| 6.1     | Functional Device Characteristics        | . 25 |

| 6.2     | Diagrams                                 | . 34 |

| 7       | Application Information                  | . 37 |

| 7.1     | ESD Robustness according to IEC61000-4-2 | . 37 |

| 7.2     | Bus Interface Simulation Model Parameter | . 37 |

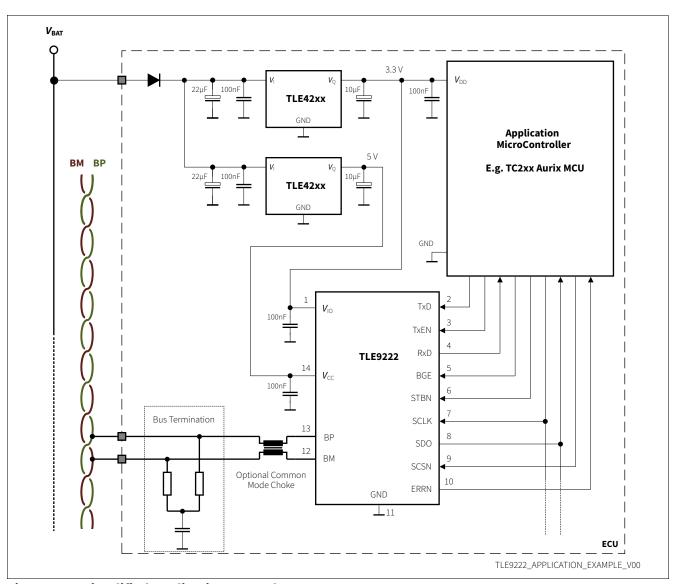

| 7.3     | Application Example                      | . 38 |

# **TLE9222**

| 9   | Revision History                                           | 42 |

|-----|------------------------------------------------------------|----|

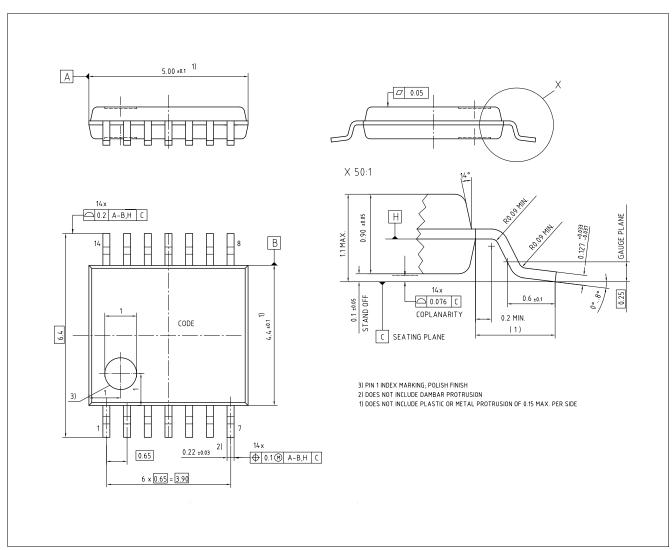

| 8   | Package Outlines                                           | 41 |

| 7.6 | Further Application Information                            | 40 |

| 7.5 | Minimizing ECU current consumption through BD_Standby mode | 40 |

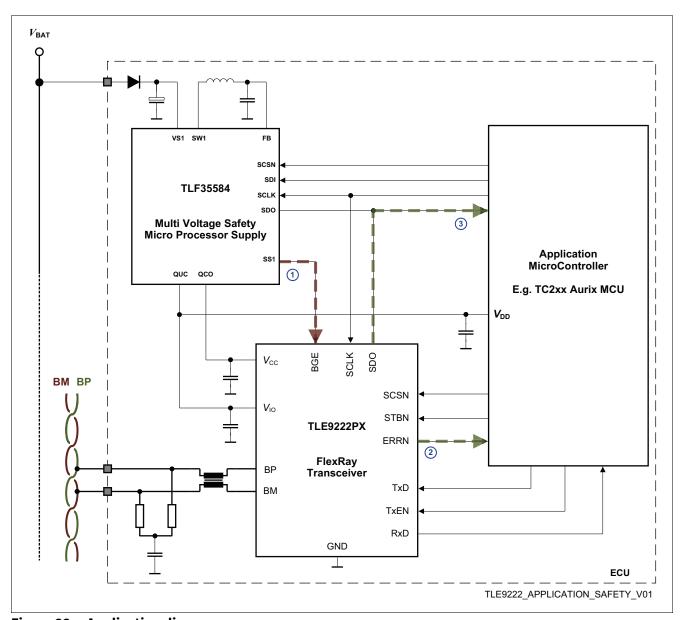

| 7.4 | Implementation of ECU Functional Safety concepts           | 39 |

# FlexRay Transceiver TLE9222

# 1 Overview

#### **Features**

- Compliant with the FlexRay Electrical Physical Layer Specification version 3.0.1 and ISO 17458-4

- Optimized for time triggered in-vehicle networks with data transmission rates from 1 Mbit/s up to 10 Mbit/s

- · Supports minimum bit times down to 60 ns

- · Automatic voltage adaptation on the digital interface pins

- Bus failure protection and error detection

- Very high ESD robustness; ± 8 kV according to IEC61000-4-2

- Optimized for high Electromagnetic Compatibility (EMC);

Very low emission and high immunity to interference

- Green Product (RoHS compliant)

- AEC Qualified

#### **Modes of Operation and Wake-up Features**

- Low power standby operation mode with very low quiescent current consumption

- Remote wake-up detection via wake-up patterns and a dedicated wake-up frame

#### **Protection and Diagnostic**

- Short-circuit protection on the bus pins

- Overtemperature protection

- Undervoltage monitoring of the  $V_{CC}$  power supply and the  $V_{IO}$  logic voltage level reference

- Error and wake-up indication on the ERRN output

- · Status register for detailed diagnostic information through a simplified SPI interface

- Integrated Bus Guardian interface with enhanced safety feedback path

- Bus pins high impedance when device unpowered

## **Description**

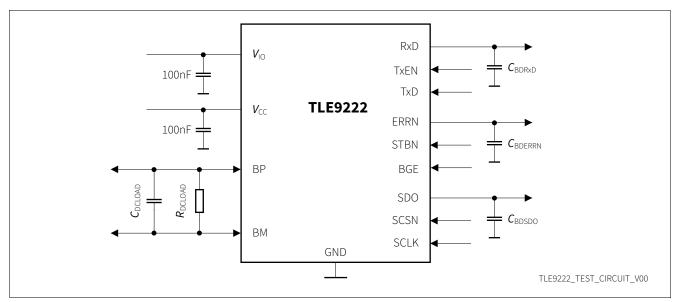

The TLE9222 FlexRay transceiver is designed for data transmission rates from 1 Mbit/s up to 10 Mbit/s according to the FlexRay Electrical Physical Layer Specification 3.0.1. The Bus Driver (BD) realizes the physical interface between a FlexRay node and the communication channel. It provides differential transmit and receive capability to the bus, allowing the node bidirectional time-multiplexed binary data stream transfer. In

| Туре       | Package     | Marking              |

|------------|-------------|----------------------|

| TLE9222PX  | PG-TSSOP-14 | 9222                 |

| Data Shoot | 1           | Pov. 1.0, 2015 06 12 |

PG-TSSOP-14

#### Overview

addition to transmit and receive functions, the TLE9222 provides low power standby operation, supply voltage monitoring (undervoltage detection) as well as bus failure detection and represents an ESD-protection barrier between the bus and the ECU.

The TLE9222 supports the following FlexRay functional classes:

- Functional class "Bus driver bus guardian interface"

- Functional class "Bus driver logic level adaptation"

- Functional class "Bus driver remote wakeup"

- Functional class "Bus driver increased voltage amplitude transmitter"

In BD\_Standby mode the quiescent current is decreased to a minimal level while still being able to detect wake-up requests on the bus.

Fail Safe features, like failure detection and the power supply monitoring, combined with an easy accessible status register support requirements for safety related applications with extended diagnostic features.

The TLE9222 is internally protected against transients on the bus pins, BP and BM. This makes it possible to use the TLE9222 for implementing ECUs without additional external bus protection circuitry while fulfilling ESD and ISO pulse requirements of car manufacturers. With its excellent EMC performance the TLE9222 provides a very high immunity against RF disturbances over a broad frequency range and transmits only a minimal level of electromagnetic emission onto the bus.

The TLE9222 is integrated in a RoHS compliant PG-TSSOP-14 package. Using the latest Infineon Smart Power Technology it is especially tailored to withstand the harsh conditions of the automotive environment and qualification according to the AEC-Q100 standard.

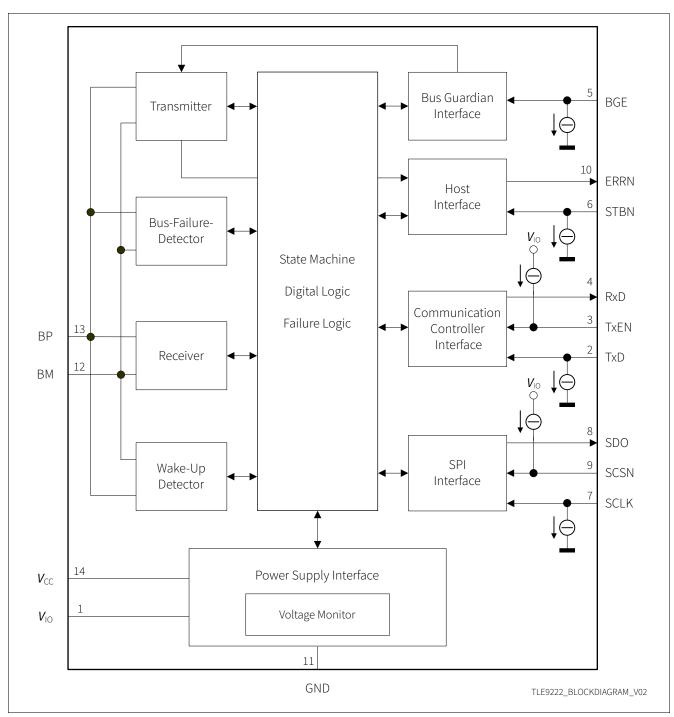

# **Block Diagram**

# 2 Block Diagram

Figure 1 Block diagram

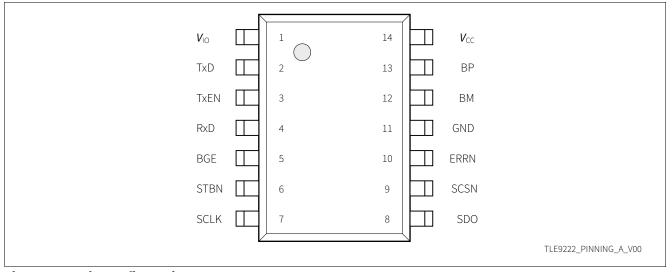

# **Pin Configuration**

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin configuration

# 3.2 Pin Definitions and Functions

| Pin | Symbol          | Function                                                                                                                                         |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>IO</sub> | Digital Reference Voltage; Digital reference voltage supply for the logic input and output pins, 100 nF decoupling capacitor to GND recommended. |

| 2   | TxD             | Transmit Data Input; Integrated pull-down to GND.                                                                                                |

| 3   | TxEN            | Transmitter Enable Not Input; Logical "low" to enable the transmitter output stage, Integrated pull-up to $V_{\rm IO}$ .                         |

| 4   | RxD             | <b>Receive Data Output;</b> Output voltage level adapted to the voltage level of $V_{10}$ .                                                      |

| 5   | BGE             | Bus Guardian Enable Input; Logical "high" to enable the transceiver output stage, Integrated pull-down to GND.                                   |

| 6   | STBN            | Standby Not Mode Control Input; Digital input for mode selection, logical "high" for BD_Normal mode, Integrated pull-down to GND.                |

| 7   | SCLK            | SPI Clock Input; Integrated pull-down to GND.                                                                                                    |

# **TLE9222**

# **Pin Configuration**

| Pin | Symbol          | Function                                                                                        |

|-----|-----------------|-------------------------------------------------------------------------------------------------|

| 8   | SDO             | SPI Data Output;                                                                                |

| 9   | SCSN            | SPI Chip Select Not Input; Integrated pull-up to $V_{10}$ .                                     |

| 10  | ERRN            | Error Not Diagnosis Output; Logical "low" in failure cases or when wake-up pattern detected.    |

| 11  | GND             | Ground;                                                                                         |

| 12  | ВМ              | <b>Bus Line Minus;</b> Negative input / output terminal of the FlexRay bus.                     |

| 13  | ВР              | Bus Line Plus; Positive input / output terminal of the FlexRay bus.                             |

| 14  | V <sub>cc</sub> | Supply Voltage; Transceiver 5V supply voltage, 100 nF decoupling capacitors to GND recommended. |

# 4 Functional Description

The TLE9222 realizes the physical interface between the FlexRay node and the communication channel. Differential transmit and receive capability to the FlexRay bus is provided, allowing the node bidirectional time multiplexed binary data stream transfer.

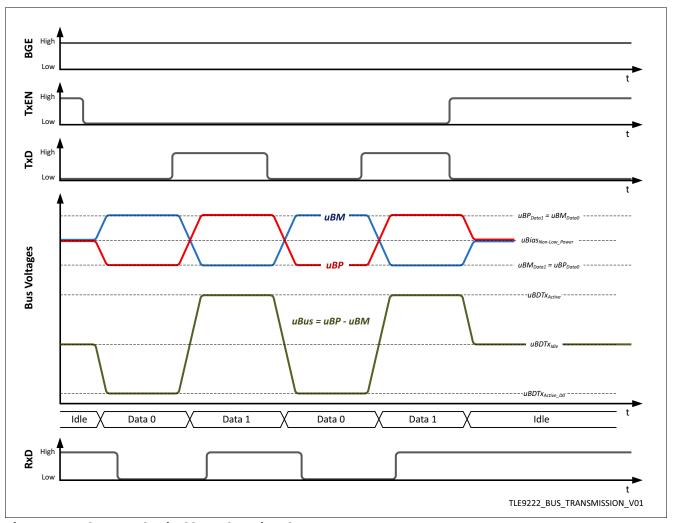

The differential bus voltage is measured between two signal lines, denoted BP (Bus Plus) and BM (Bus Minus), defined as uBUS = uBP - uBM. Three different bus states are defined for the FlexRay bus; Idle, Data\_0 and Data\_1. For the Idle state no differential voltage is driven to BP or to BM. The common mode bus biasing level will depend on the operation mode of all nodes on the bus. For the Data\_1 state a positive differential voltage is driven between BP and BM, whereas for the Data\_0 state a negative differential voltage is driven between BP and BM.

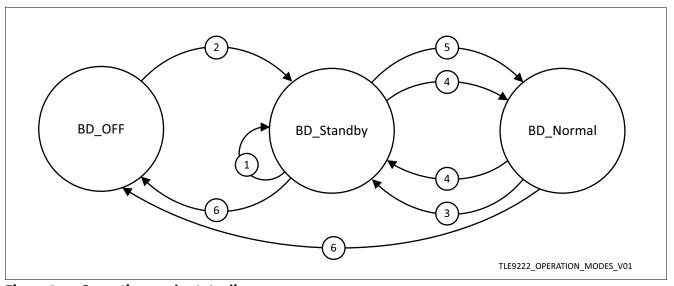

# 4.1 Operation Modes

The TLE9222 supports two functional operation modes, BD\_Normal mode and BD\_Standby mode. In addition, the BD\_Off condition describes the behavior of the TLE9222 when unsupplied.

Mode transitions of the TLE9222 are triggered by host commands, undervoltage events and during power-up /-down, see **Figure 3** and **Table 1**.

Figure 3 Operation mode state diagram

Table 1 Operation mode transitions

| Nr | <b>Reason for transition</b>                                                                             | Comment                                                           |  |  |  |

|----|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| 1  | Wake-up detection                                                                                        | -                                                                 |  |  |  |

| 2  | Power-on detection Supply voltage sufficiently supplied via $V_{CC}$ after being unpowered.              |                                                                   |  |  |  |

| 3  | Undervoltage detection After $V_{CC}$ and / or $V_{IO}$ undervoltage detection, BD_Standby mode is force |                                                                   |  |  |  |

| 4  | Host command Triggered by host command.                                                                  |                                                                   |  |  |  |

| 5  | Undervoltage recovery                                                                                    | Undervoltage recovery while host command requests BD_Normal mode. |  |  |  |

| 6  | Power-off                                                                                                | Supply voltage falls below the power-on threshold.                |  |  |  |

# 4.1.1 BD\_Normal Mode

In BD\_Normal mode all interfaces and functions of the TLE9222 are in operating condition. The communication controller interface is fully active; the RxD output reflects the data on the bus pins, the TxD drives the data to the transmitter and the TxEN input enables or disables the transmitter. When the transmitter is activated, fail safe functionality like the transmitter time-out, overtemperature detection and bus error detection are also enabled. The bus biasing is connected to  $V_{\rm CC}$  / 2 via the internal common mode resistors. With the RxEN flag in the status register the bus states idle or active can be read out through the SPI interface.

The host interface is active and fully functional, as well as status register read-out on the SPI interface. Through the bus guardian interface, the transmitter can be activated or disabled.

The wake-up detector is active, but received wake-up information is not flagged while in BD\_Normal mode.

The power supply interface including voltage monitor on both  $V_{\rm CC}$  and  $V_{\rm IO}$  is active. Undervoltage events are signalled on the ERRN output and in the status register, and trigger a mode transition to BD\_Standby mode. BD\_Normal mode can only be entered with a valid host command while both power supplies are within their operational range.

# 4.1.2 BD\_Standby Mode

After power-up the TLE9222 automatically enters BD\_Standby, an idle mode with optimized low power consumption. In BD\_Standby mode neither sending nor receiving data is possible, both the transmitter and the receiver are disabled. The bus biasing is connected to GND through the internal common mode resistors.

The communication controller interface is inactive. The TxD and the TxEN inputs are not functional. The RxD output is used for signalling wake-up or error information, depending on the host command. The host interface is active and fully functional, as well as status register read-out on the SPI interface.

The bus guardian interface is inactive and detection of bus transmission through the RxEN flag in the status register is not possible. The bus failure detector is not active, no bus failure can be detected.

The wake-up detector is active and signals wake-up requests on the ERRN and RxD outputs while the host command is BD\_Standby mode.

The power supply interface with voltage monitoring on both  $V_{\rm CC}$  and  $V_{\rm IO}$  is active. If the TLE9222 is forced to BD\_Standby mode because of undervoltage events while the host command is BD\_Normal mode, this is signalled on the ERRN output. Additionally, the information is stored in the status register.

## 4.1.3 BD Off Condition

The TLE9222 enters the BD\_Off condition when the  $V_{\rm CC}$  power supply drops below the  $uBDPDV_{\rm CC}$  power-on-reset threshold. In this state the transmitter and the receiver are turned off, the wake-up function is not operational, the RxD and ERRN outputs are "low" and the SDO output is in high impedance state. If the  $V_{\rm IO}$  reference supply is available, the logical inputs are set to their default states as given in **Table 2**.

Table 2 Logic inputs when unconnected / default states

| Input Signal | Default State |

|--------------|---------------|

| TxD          | Low           |

| TxEN         | High          |

| STBN         | Low           |

| BGE          | Low           |

Table 2 Logic inputs when unconnected / default states

| Input Signal | Default State |

|--------------|---------------|

| SCSN         | High          |

| SCLK         | Low           |

#### 4.2 Communication Controller Interface

The communication controller interface is the link between the TLE9222 and the FlexRay communication controller, comprising three digital signals:

- TxEN (Transmit Data Enable Not) input

- TxD (Transmit Data) input

- RxD (Receive Data) output

The logical I/O levels of all three digital pins are adapted to the  $V_{10}$  digital reference voltage supply.

Figure 4 FlexRay physical layer bus signals

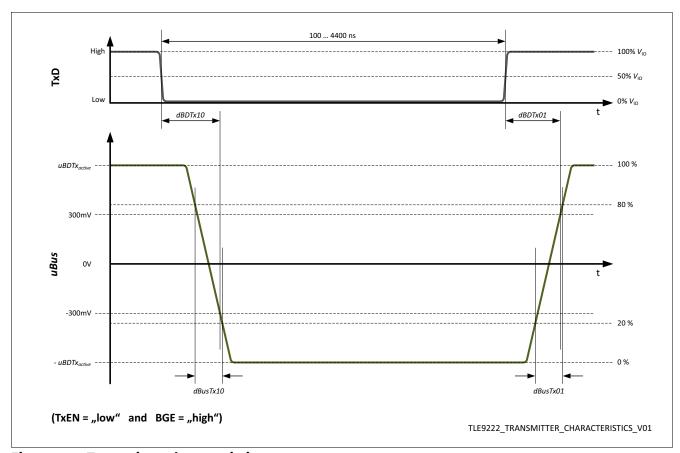

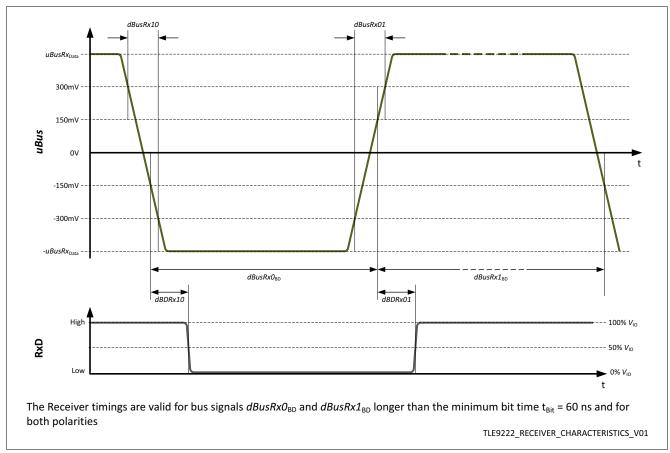

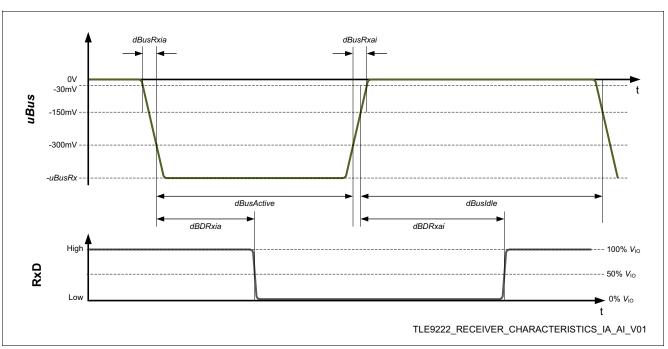

The communication controller interface drives the serial digital data stream available on the TxD input to the FlexRay bus via the transmitter. Simultaneously the receiver of the TLE9222 monitors the data on the FlexRay bus and transfers the data to a serial digital data stream back to the RxD output. A logical "low" signal on the

TxD input drives a Data\_0 signal on the FlexRay bus; a Data\_0 signal on the FlexRay bus results in a logical "low" signal on the RxD output. Vice versa a logical "high" on TxD drives a Data\_1 signal on the FlexRay bus and results in a logical "high" signal on the RxD output. The RxD output is also used to signal wake-up events while the transceiver is in BD\_Standby mode.

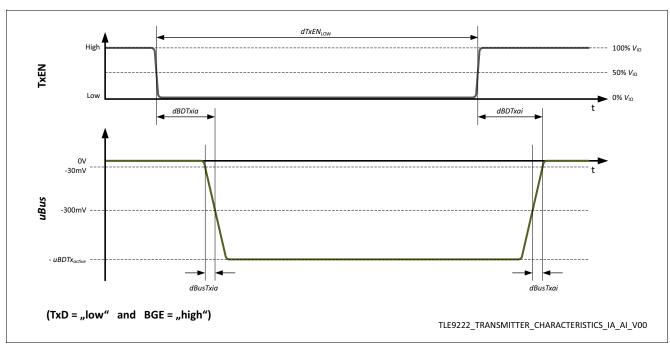

The TxEN input is only functional in BD\_Normal mode and requires a transition from "high" to "low" for initiating bus transmissions. After TxEN has been set "low" while the BGE input is "high", a "low" level on the TxD input enables the transmitter.

For avoiding unintentional blocking of the FlexRay bus in case of failures, the transmitter is protected with a time-out function. In case a time-out occurs, the transmitter will automatically be disabled and the error will be signalled by the ERRN output and in the status register. A more detailed description of this fail safe function is given in **Chapter 4.7.3**.

## 4.3 Bus Guardian Interface

The bus guardian interface allows an external supervision device to immediate interrupt any bus transmission of the TLE9222. A logical "low" signal on the BGE input disables the transmitter of the TLE9222 while operating in BD\_Normal mode, regardless of the signals on the TxD and TxEN inputs.

For increasing the ECU system safety level, an enhanced redundant feedback path has been implemented for the bus guardian interface. A monitoring circuit directly at the transmitter output stages provides reliable feedback by setting the ERRN output "low" and indication with the BGE flag in the status register after the transmitter has been disabled through the Bus Guardian interface.

The logical I/O level of the BGE input is adapted to the digital reference voltage level  $uV_{IO}$ . Together with the TxEN input, the BGE input is monitored for the transmitter time-out function (see **Chapter 4.7.3**).

Additionally, the status register includes the RxEN (Receive Enable NOT) flag that indicates activity (Data\_0 or Data\_1) on the FlexRay bus. This detection is only active in BD\_Normal Mode. The RxEN bit can be read out with the SPI Interface as described in **Chapter 4.8**.

## 4.4 Host Interface

The host interface enables the host to control the operation mode of the TLE9222 and to flag status information. The host interface is implemented using *hard wired signals*, *Option A* according to the FlexRay EPL Spec. 3.0.1.

Table 3 Host Command

| STBN | Resulting operation mode |

|------|--------------------------|

| High | BD_Normal                |

| Low  | BD_Standby               |

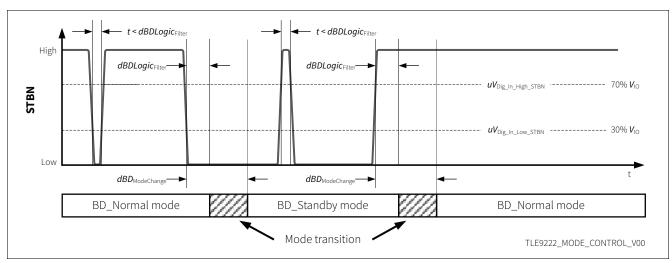

The STBN (Standby Not) input controls the operation mode of the TLE9222. Unless the TLE9222 is being forced to BD\_Standby mode because of undervoltage events, the host command will set operation mode as given in **Table 3**. Mode change by host command is completed within the time  $dBD_{\text{ModeChange}}$  after the host command is applied. Voltage spikes on the STBN input that are shorter than  $dBDLogic_{\text{Filter}}$  are filtered out and ignored.

Figure 5 Mode control with the STBN input

The ERRN output is used to signal events detected by the TLE9222 to the host controller. Depending on the provided host command, the ERRN output indicates errors or wake-up events, see **Table 4**. The TLE9222 reacts on and signals these events on the ERRN output within the time *dReactionTime*<sub>ERRN</sub>. Detailed information about the detected events as given in **Table 4** can be read out from the status register with the SPI interface as described in **Chapter 4.8**.

Table 4 Signalling on the ERRN and RxD pins

| STBN            | STBN ERRN RxD Cause / Comment Effect |                             |                                             |                                                                                                       |  |  |

|-----------------|--------------------------------------|-----------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| BD_No           | rmal mod                             | de                          |                                             |                                                                                                       |  |  |

| High            | High                                 | High /<br>Low <sup>1)</sup> | Default condition for BD_Normal mode        | _                                                                                                     |  |  |

| High            | Low                                  | High /                      | Bus error detected                          | -                                                                                                     |  |  |

|                 |                                      | Low <sup>1)</sup>           | Transmitter time-out detected               | Transmitter disabled                                                                                  |  |  |

|                 |                                      |                             | Overtemperature event detected              | Transmitter disabled                                                                                  |  |  |

|                 |                                      |                             | BGE input "low"                             | Transmitter disabled                                                                                  |  |  |

|                 |                                      |                             | SPI error detected                          | -                                                                                                     |  |  |

| BD_Sta          | andby mo                             | de                          |                                             |                                                                                                       |  |  |

| Low             | High                                 | High                        | Default condition for BD_Standby mode       | -                                                                                                     |  |  |

| Low             | Low                                  | Low                         | Bus wake-up detected                        | -                                                                                                     |  |  |

| High            | Low                                  | High                        | V <sub>CC</sub> undervoltage detected       | Forced BD_Standby mode                                                                                |  |  |

| X <sup>2)</sup> | Low                                  | Low                         | V <sub>IO</sub> undervoltage detected       | Forced BD_Standby mode, logic inputs follow default states (see <b>Table 2</b> ) SDO "high impedance" |  |  |

| BD_OF           | F conditi                            | on                          |                                             |                                                                                                       |  |  |

| X <sup>2)</sup> | Low                                  | Low                         | uV <sub>CC</sub> below uBDPDV <sub>CC</sub> | -                                                                                                     |  |  |

<sup>1)</sup> Depending on bus state; RxD "low" when Data\_0 is detected, RxD "high" when Data\_1 is detected or when bus is Idle

<sup>2)</sup> X = "Don't care"

A "low" output level on the ERRN pin is latched. To reset the ERRN event and the status register either a correct read-out of the status register or a mode change by the host command is required, given that the error condition has been resolved.

# 4.5 Power Supply Interface

The TLE9222 is powered by the  $V_{\rm CC}$  pin which shall be connected to a voltage supply with nominal 5 V. Additionally, the TLE9222 provides the  $V_{\rm IO}$  reference voltage pin for all digital inputs and outputs. The voltages at the  $V_{\rm CC}$  and  $V_{\rm IO}$  pins are monitored for detection of undervoltage events.

# 4.5.1 $V_{CC}$ Undervoltage Detection

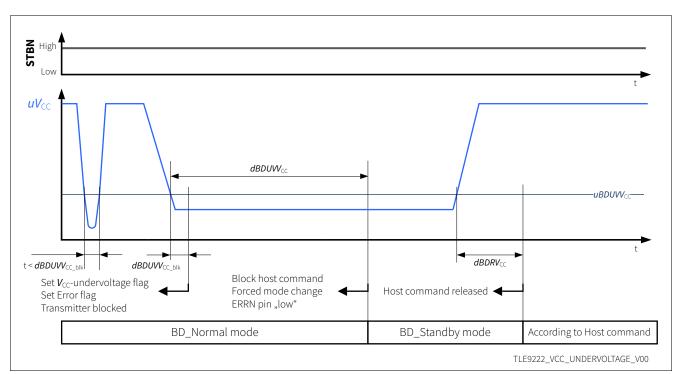

The TLE9222 detects undervoltage events on the  $V_{\rm CC}$  pin if the voltage  $uV_{\rm CC}$  falls below the undervoltage detection threshold  $uBDUVV_{\rm CC}$  for a time  $t > dBDUVV_{\rm CC\_blk}$ . Upon detection the  $V_{\rm CC}$ -undervoltage flag and the error flag are set. In case the TLE9222 is in BD\_Normal mode, the transmitter will be disabled and the ERRN output will go "low" after the time  $dReactionTime_{\rm ERRN}$ . After the time  $dBDUVV_{\rm CC}$  the TLE9222 will force a transition to BD\_Standby, regardless of the host command (see **Figure 6**).

Figure 6 V<sub>cc</sub> undervoltage detection

The TLE9222 recovers from a  $V_{CC}$  undervoltage event after the time  $t > dBDRV_{CC}$  following the voltage  $uV_{CC}$  rise above the undervoltage detection threshold  $uBDUVV_{CC}$ . This will release the host command and change operation mode accordingly.

# 4.5.2 $V_{10}$ Undervoltage Detection

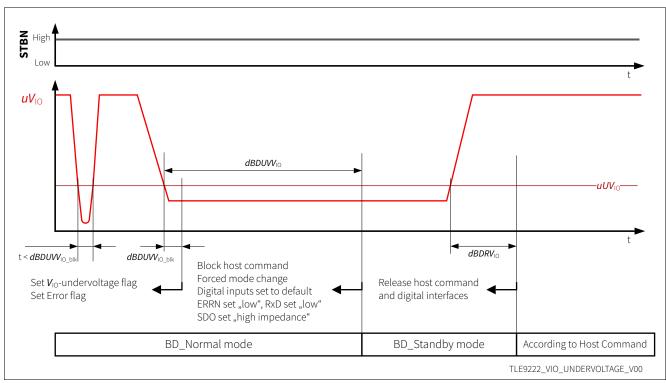

The  $V_{\rm IO}$  undervoltage detection is similar to that on the  $V_{\rm CC}$  supply. Undervoltage events on the  $V_{\rm IO}$  pin are detected if the voltage  $uV_{\rm IO}$  falls below the undervoltage detection threshold  $uUV_{\rm IO}$  for a time  $t > dBDUVV_{\rm IO\_blk}$ . Upon detection the  $V_{\rm IO}$ -undervoltage flag and the error flag are set. While an undervoltage event is present on the  $V_{\rm IO}$  pin, the reference threshold levels of all digital input and output pins are invalid. Therefore, the

TLE9222 blocks the host interface, communication controller interface, SPI interface and the bus guardian interface. The digital outputs RxD and ERRN are set "low" and all digital input pins follow their default levels (see **Table 2**). The SDO output is set to high impedance state. After the time *dBDUVV*<sub>IO</sub> the TLE9222 will force a transition to BD\_Standby mode.

Figure 7  $V_{10}$  undervoltage detection

The TLE9222 will recover from a  $V_{IO}$  undervoltage event after the time  $t > dBDRV_{IO}$  following the voltage  $uV_{IO}$  rise above the undervoltage detection threshold  $uUV_{IO}$ . This will release the SPI interface and host command, and change mode accordingly (see **Figure 7**).

## 4.5.3 Power-up and Power-down

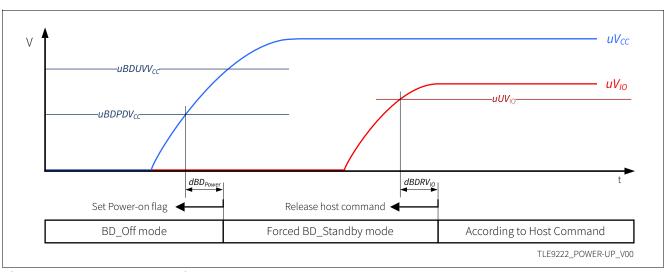

The TLE9222 will remain in BD\_Off condition as long as the voltage on the  $V_{\rm CC}$  supply pin,  $uV_{\rm CC}$ , is below the power-down threshold  $uBDPDV_{\rm CC}$ . When  $uV_{\rm CC}$  is ramped up higher than  $uBDPDV_{\rm CC}$  the TLE9222 powers up and begins initialization of the BD\_Standby mode within the time  $dBD_{\rm Power}$ . After both voltages  $uV_{\rm CC}$  and  $uV_{\rm IO}$  have risen above their respective undervoltage detection thresholds ( $uBDUVV_{\rm CC}$  and  $uUV_{\rm IO}$ , respectively), the digital interfaces will be released and the full functionality of the device will be available. The power-on event can be identified with the corresponding flag in the status register and mode change according to the host command will then be initiated (see **Figure 8**).

Figure 8 Power-up behavior

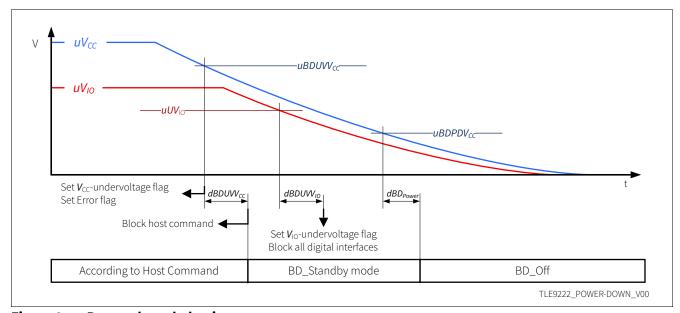

The power-down sequence of the TLE9222 is shown in **Figure 9**. As the voltage at the  $V_{CC}$  supply pin,  $uV_{CC}$ , falls below the undervoltage threshold the  $V_{CC}$ -undervoltage flag and the error flag are set. After the detection time for  $V_{CC}$  undervoltage  $dBDUVV_{CC}$  the TLE9222 blocks the host command and automatically enters BD\_Standby mode.

Figure 9 Power-down behavior

While the TLE9222 is being powered down, the behavior on the digital interface level shift reference pin  $V_{\rm IO}$  is very similar to the  $V_{\rm CC}$  supply pin. As  $uV_{\rm IO}$  falls below the undervoltage threshold the undervoltage timer is started and the  $V_{\rm IO}$ -undervoltage flag is set. If  $V_{\rm CC}$  is not already in undervoltage condition, the error flag is also set. After the detection time for  $V_{\rm IO}$  undervoltage,  $dBDUVV_{\rm IO}$ , the TLE9222 blocks the host command (if not already blocked because of  $V_{\rm CC}$  undervoltage) and all digital interfaces and enters BD\_Standby mode.

When the voltage at the  $V_{CC}$  supply pin,  $uV_{CC}$ , falls below the power-on threshold  $uBDPDV_{CC}$  the TLE9222 enters BD\_Off condition within the time  $dBD_{Power}$ .

# 4.6 Remote Wake-up

The TLE9222 detects and signals a remote wake-up request after correct reception of a bus wake-up pattern or wake-up payload in a FlexRay data frame while operating in BD\_Standby mode. When the valid wake-up pattern or wake-up payload is detected, the TLE9222 signals the request with the remote wake-up flag in the status register and on the RxD and ERRN outputs within the time dBDWakeupReaction<sub>Remote</sub>.

The wake-up detector is also active in BD\_Normal mode, but wake-up requests are only flagged when the TLE9222 is in BD\_Standby mode.

# 4.6.1 Bus Wake-up Patterns

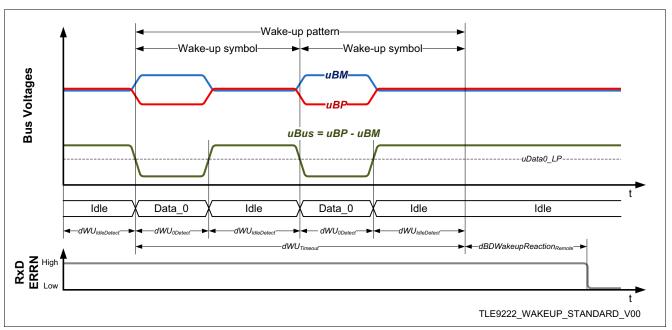

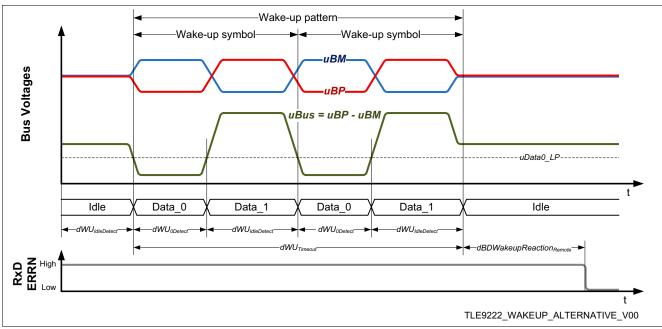

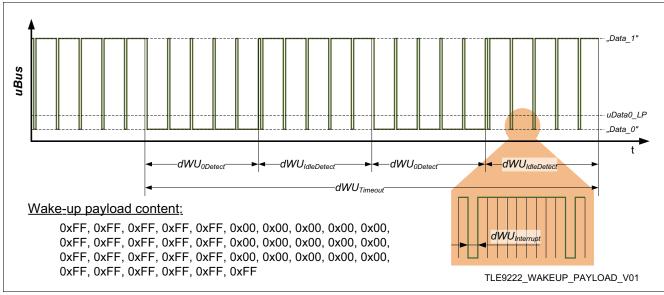

A wake-up pattern consists of at least two wake-up symbols. A wake-up symbol on the FlexRay bus is defined as either a phase of Data\_0 followed by a phase of Idle, or alternatively as a phase of Data\_0 followed by a phase of Data\_1. A valid remote wake-up event is detected with the reception of at least two consecutive wake-up symbols on the bus within the time  $dWU_{\text{Timeout}}$  (see **Figure 10** and **Figure 11**).

Figure 10 Standard wake-up pattern

The Data\_0 phases have to be longer than the time  $dWU_{\rm 0Detect}$  while the Idle or Data\_1 (alternative wake-up pattern) phases have to be longer than the time  $dWU_{\rm IdleDetect}$ . The TLE9222 detects and signals both the standard and the alternative wake-up patterns without any behavioral differences.

Figure 11 Alternative wake-up pattern

# 4.6.2 Wake-up by Payload

In addition to wake-up detection by wake-up patterns, the TLE9222 also supports wake-up requests by a specific payload within the data field of a FlexRay communication frame with data transmission rate of 10 Mbit/s.

A dedicated Byte Start Sequence (BSS) is transmitted before each byte of the payload within the FlexRay data frame. The BSS consists of one "high" bit followed by one "low" bit. For transmitting a "Data\_0" byte on the FlexRay bus, the FlexRay controller sends 10 bits, the "high" bit and the "low" bit as part of the BSS followed by the eight "low" data bits (HL=BSS; LLLLLLLL="Data\_0"). For sending a "Data\_1" byte the FlexRay controller sends the "high" bit and the "low" bit, followed by the eight consecutive "high" data bits (HL=BSS; HHHHHHHHH= "Data\_1") (see Figure 12).

Figure 12 Wake-up by payload

# 4.7 Fail Safe Functions and Flags

In addition to power supply undervoltage detection, the TLE9222 provides several functions for detection of local or remote failures with corresponding status flags. These errors are signalled with the ERRN output and can be read out from the status register. When local errors are detected, the TLE9222 initiates fail safe procedures for device self protection and prevention of communication channel interruption.

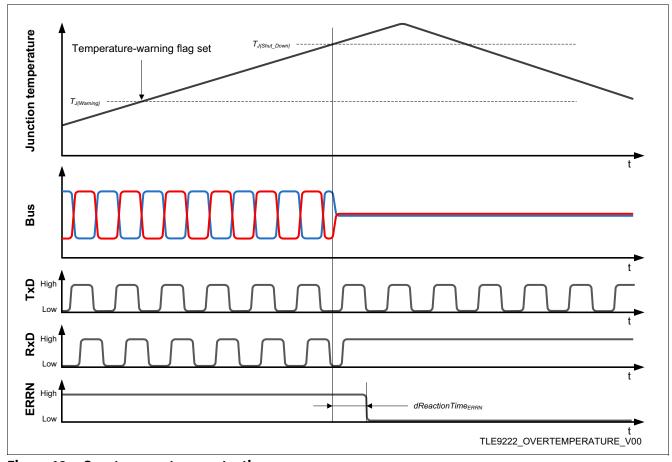

# 4.7.1 Overtemperature detection

The transmitter of the TLE9222 is protected against overtemperature events when active in BD\_Normal mode. If the junction temperature rises above the  $T_{J(warning)}$  threshold the temperature-warning flag in the status register is set. If the junction temperature continues to rise and exceeds the  $T_{J(Shut_Down)}$  threshold, the transmitter will be disabled and the overtemperature event will be flagged by the temperature-high flag in the status register and signalled with the ERRN output.

Figure 13 Overtemperature protection

# 4.7.2 Bus Error Detector

The bus error detector monitors the FlexRay bus for identifying external failures which may lead to corrupt data transmission and reception. With the RxD-TxD compare function and the bus overcurrent monitoring, bus errors are detected and signalled with the bus error flag. The bus error detector is only enabled in BD\_Normal mode while the transmitter is active.

# 4.7.2.1 RxD-TxD Compare

When the TLE9222 transmits data on the bus (TxEN "low" and BGE "high"), the digital input data on TxD is compared with the received data on the RxD output. If the data is not identical, a failure condition is identified. Both the positive and the negative edges on the TxD input signal triggers an internal comparator to compare the TxD signal with the RxD signal. The results are stored in an internal error counter. When the internal error counter exceeds 10 reported comparison failures, the bus error flag will be set. The error counter is reset when the transmitter is deactivated.

#### 4.7.2.2 Bus Overcurrent

The BP and BM bus pins have implemented current sensors for detection of overcurrent conditions in the direction in or out of the pins. Detection of overcurrent is the typical signature of a short circuit of one of the bus lines to the ground or a supply line.

#### 4.7.3 Transmitter Time-Out

For avoiding unintentional blocking of the FlexRay bus in case of e.g. a malfunctioning microcontroller or short circuits on the PCB, the transmitter is protected with a time-out function. When the transmitter is activated for bus transmission while in BD\_Normal mode, with a "low" signal on TxEN and "high" on BGE, a timer is started. In case a time-out occurs, the transmitter will automatically be disabled and the failure will be signaled on the ERRN output and in the status register.

The transmitter timer is reset when the transmitter is deactivated with either TxEN or BGE.

# 4.7.4 $V_{10}$ Undervoltage-flag

During  $V_{10}$  undervoltage events, the SPI register is blocked and can not be read out. After undervoltage recovery, depending on host command and the status of other register flags, the  $V_{10}$ -undervoltage flag may or may not be set. Please refer to **Chapter 4.7.6**.

## 4.7.5 SPI-error flag

The SPI-error flag is used for indication of incorrect SPI read-out procedure, please find detailed description in **Chapter 4.8.1**.

# 4.7.6 Error flag

If any local errors or bus errors are detected, the respective bit in the status register is flagged together with the error flag (bit 12). If the error flag is set, but no other error contributing flags in the status register set, then this indicates that a  $V_{\rm IO}$  undervoltage event has occurred in the past but recovery has already taken place.

While the error flag is set and the host command on the STBN input is "high", the ERRN output is "low".

## 4.7.7 Mode Flags

The mode flag in the status register indicates the current operating mode of the TLE9222, regardless of the applied host command. If the TLE9222 is in BD\_Standby mode, bit 1 will be "low". If the current operation mode is BD\_Normal, bit 1 will be "high". The mode flag will only toggle during an operation mode change, i.e. not be reset by SPI register read-out. The mode indication can be beneficial for the host when the TLE9222 is forced to a different mode than requested with the host command during  $V_{CC}$  undervoltage events.

# 4.8 SPI Interface and Status Register

The TLE9222 has a 16-bit SPI interface for reading out the internal status register. The bits in the register reflects detailed flags regarding external events such as wake-up and power-on recognition, detection of errors / warnings and operation mode indication, see **Table 5**.

Table 5

Bit definition of the status register

| Bit    | Name                                 | Indication                                                                     | Comment                                                           |

|--------|--------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Bit 0  | Remote wake-up                       | "Low": Remote wake-up detected                                                 | -                                                                 |

|        | flag                                 | "High": -                                                                      | -                                                                 |

| Bit 1  | Mode flag                            | "Low": BD_Standby mode                                                         | -                                                                 |

|        |                                      | "High": BD_Normal mode                                                         | -                                                                 |

| Bit 2  | BGE flag                             | "Low": Transmitter disabled by Bus Guardian, BGE input "low" in BD_Normal mode | Error, will trigger Bit 12 → "low"                                |

|        |                                      | "High": -                                                                      | -                                                                 |

| Bit 3  | RxEN flag                            | "Low": Bus activity ongoing                                                    | Not latched                                                       |

|        |                                      | "High": Bus idle                                                               | -                                                                 |

| Bit 4  | Power-on flag                        | "Low": Power-on detected                                                       | -                                                                 |

|        |                                      | "High": -                                                                      | -                                                                 |

| Bit 5  | Bus-error flag                       | "Low": Bus error detected                                                      | Error, will trigger Bit 12 → "low"                                |

|        |                                      | "High": -                                                                      | -                                                                 |

| Bit 6  | Temperature-high                     | "Low": Overtemperature detected                                                | Error, will trigger Bit 12 → "low"                                |

|        | flag                                 | "High": -                                                                      | -                                                                 |

| Bit 7  | Transmitter time-                    | "Low": Transmitter activation time-out                                         | Error, will trigger Bit 12 → "low"                                |

|        | out flag                             | "High": -                                                                      | -                                                                 |

| Bit 8  | <i>V</i> <sub>CC</sub> -undervoltage | "Low": V <sub>CC</sub> Undervoltage detected                                   | Error, will trigger Bit 12 → "low"                                |

|        | flag                                 | "High": –                                                                      | -                                                                 |

| Bit 9  | V <sub>IO</sub> -undervoltage        | "Low": V <sub>IO</sub> Undervoltage detected                                   | Error, will trigger Bit 12 → "low"                                |

|        | flag                                 | "High": -                                                                      | -                                                                 |

| Bit 10 | SPI-error flag                       | "Low": SPI error detected                                                      | Error, will trigger Bit 12 → "low"                                |

|        |                                      | "High": -                                                                      | -                                                                 |

| Bit 11 | Temperature-                         | "Low": High temperature warning                                                | -                                                                 |

|        | warning flag                         | "High": -                                                                      | -                                                                 |

| Bit 12 | Error flag                           | "Low": Error(s) detected                                                       | Error, will trigger ERRN output "low" if signal on STBN is "high" |

|        |                                      | "High": No errors detected                                                     | -                                                                 |

| Bit 13 | Reserved                             | Always "High"                                                                  | -                                                                 |

| Bit 14 | Reserved                             | Always "Low"                                                                   | -                                                                 |

| Bit 15 | Even parity bit                      | "Low": Odd parity of Bit 0 to Bit 14                                           | -                                                                 |

|        |                                      | "High": Even parity of Bit 0 to Bit 14                                         | -                                                                 |

All the flags in the status register are "active low", the default level is "high".

The RxEN flag indicates ongoing bus transmission. As soon as the bus state returns to idle, this flag is set "high".

The wake-up, power-on and error flags and their corresponding status register bits are latched "low". A mode change by host command or a correct SPI status bit register read-out will reset these flags, given that the error condition has been resolved.

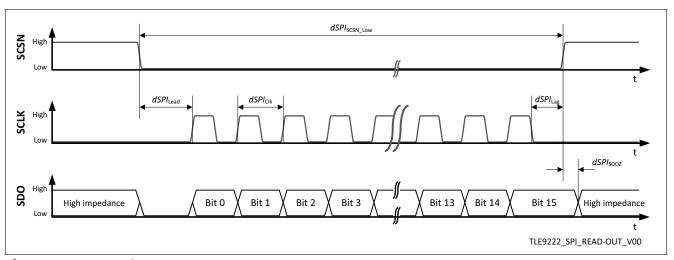

# 4.8.1 Read-out procedure

The SPI interface of the TLE9222 is enabled by the SCSN (SPI Chip Select Not) input. While SCSN is "high", the SDO (SPI Data Output) output is in a high impedance state and clock signals on the SCLK input are ignored. The read-out procedure is initiated with a "low" signal on SCSN, which will cause the SDO output to be set "low" (see **Figure 13**). After the time  $dSPI_{Lead}$  the status register data can be shifted out on the SDO output synchronized with the rising edge of a clock signal on the SCLK input. With a clock signal period of  $dSPI_{Clk}$ , the TLE9222 supports SPI data rates in the range 10 kbit/s to 4 Mbit/sIf a transition on SCSN from "high" to "low" is detected while SCLK is "high", this would be identified as a SPI error.

Within the SCSN period, the time  $dSPI_{SCSN\_Low}$  while the signal on SCSN is "low", exactly 16 clock cycles are expected for a correct read-out procedure. Incorrect SPI access, with more or less than 16 SCLK cycles or wrong timing, is protected by the SPI timer. If the read-out time  $dSPI_{SCSN\_Low}$  expires, the SDO output is set to "high impedance" within the time  $dSPI_{SDOZ}$ . Additionally the error flag and SPI-error flag in the status register will be set, while the state of all other latched bits are left unchanged.

Figure 14 SPI read-out

After a correct SPI read-out process, the information on the ERRN output and the flags in the status register are refreshed. Next SPI read-out can be initiated after SCSN is set "high" for the time *dSPI*<sub>Interframe</sub>.

The SPI interface is available in both BD\_Normal mode and BD\_Standby mode, but SPI readout should not occur at the same time as a mode change with the host interface, the time  $dBD_{ModeChange}$  must be respected. The SPI register is also blocked during undervoltage conditions on  $V_{10}$ .

While the TLE9222 is set in BD\_Standby with host command (pin STBN = "low") and no wake-up or errors have been detected, the SPI interface requires an enable time of  $dSPI_{LeadStbOK}$  from SCSN goes "low" until the first rising edge on the clock signal on the SCLK input can be applied.

#### **General Product Characteristics**

# 5 General Product Characteristics

# 5.1 Absolute Maximum Ratings

# Table 6 Absolute Maximum Ratings 1)

All voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                                                          | Symbol                  | Values |      |                               | Unit | Note or               | Number   |  |

|--------------------------------------------------------------------|-------------------------|--------|------|-------------------------------|------|-----------------------|----------|--|

|                                                                    |                         | Min.   | Тур. | Max.                          |      | <b>Test Condition</b> |          |  |

| Voltages                                                           | 1                       | 1      |      |                               | 11   | 1                     | I.       |  |

| Supply Voltage V <sub>CC</sub>                                     | $uV_{CC}$               | -0.3   | -    | 6.0                           | V    | _                     | P_5.1.1  |  |

| Digital Reference Voltage V <sub>IO</sub>                          | $uV_{10}$               | -0.3   | _    | 6.0                           | V    | _                     | P_5.1.2  |  |

| DC voltage on pin BP                                               | uBP                     | -40    | -    | 40                            | V    | _                     | P_5.1.3  |  |

| DC voltage on pin BM                                               | иВМ                     | -40    | -    | 40                            | V    | _                     | P_5.1.4  |  |

| DC voltage on logic input pins TxD,<br>TxEN, BGE, STBN, SCSN, SCLK | uV <sub>Logic_in</sub>  | -0.3   | -    | 6.0                           | V    | -                     | P_5.1.5  |  |

| DC voltage on logic output pins RxD, ERRN, SDO                     | uV <sub>Logic_out</sub> | -0.3   | -    | <i>uV</i> <sub>10</sub> + 0.3 | V    | -                     | P_5.1.6  |  |

| Currents                                                           | 1                       | 1      |      |                               | 1    | 1                     | ı        |  |

| Output Current on pin RxD                                          | iRxD                    | -40    | _    | 40                            | mA   | _                     | P_5.1.7  |  |

| Output Current on pin ERRN                                         | iERRN                   | -40    | -    | 40                            | mA   | _                     | P_5.1.8  |  |

| Output Current on pin SDO                                          | iSDO                    | -40    | _    | 40                            | mA   | _                     | P_5.1.9  |  |

| Temperature                                                        |                         |        | •    |                               |      |                       |          |  |

| Junction Temperature                                               | T <sub>j</sub>          | -40    | _    | 150                           | °C   | _                     | P_5.1.10 |  |

| Storage Temperature                                                | $T_{\rm stg}$           | -55    | -    | 150                           | °C   | _                     | P_5.1.11 |  |

| ESD Susceptibility                                                 | ,                       | •      |      | *                             | *    | •                     |          |  |

| ESD Susceptibility to GND on BP and BM                             | uESD <sub>Ext</sub>     | -8     | -    | 8                             | kV   | HBM <sup>2)</sup>     | P_5.1.12 |  |

| ESD Susceptibility to GND all other pins                           | uESD <sub>Int</sub>     | -2     | -    | 2                             | kV   | HBM <sup>2)</sup>     | P_5.1.13 |  |

| ESD Susceptibility to GND all pins                                 | uESD <sub>CDM</sub>     | -750   | _    | 750                           | V    | CDM <sup>3)</sup>     | P_5.1.14 |  |

- 1) Not subject to production test, specified by design.

- 2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5k  $\Omega$ , 100 pF).

- 3) ESD susceptibility, Charged Device Model "CDM" ESDA STM5.3.1 or ANSI/ESD S.5.3.1.

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **General Product Characteristics**

# 5.2 Functional Range

Table 7 Operating Range

| Parameter                                 | Symbol           |      | Values |      |    | Note or               | Number  |

|-------------------------------------------|------------------|------|--------|------|----|-----------------------|---------|

|                                           |                  | Min. | Тур.   | Max. |    | <b>Test Condition</b> |         |

| Supply Voltage V <sub>CC</sub>            | $uV_{CC}$        | 4.75 | -      | 5.25 | V  | _                     | P_5.2.1 |

| Digital Reference Voltage V <sub>IO</sub> | uV <sub>IO</sub> | 3.0  | -      | 5.25 | ٧  | -                     | P_5.2.2 |

| Junction Temperature                      | T <sub>J</sub>   | -40  | -      | 150  | °C | _                     | P_5.2.3 |

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### 5.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

Table 8 Thermal Resistance 1)

| Parameter                   | Symbol              |      | Value | S                     | Unit | Note or | Number  |

|-----------------------------|---------------------|------|-------|-----------------------|------|---------|---------|

|                             | Min. Typ. Max.      | Max. |       | <b>Test Condition</b> |      |         |         |

| Thermal Resistance          |                     | -    | +     |                       |      | -       | *       |

| Junction to Ambient         | $R_{thJA}$          | _    | 120   | -                     | K/W  | 2)      | P_5.3.1 |

| Thermal Shutdown Junction T | emperature          |      | 1     |                       |      |         |         |

| Thermal warning temp.       | $T_{J(warning)}$    | 150  | 160   | 170                   | °C   | _       | P_5.3.2 |

| Thermal shut-down temp.     | $T_{J(Shut\_Down)}$ | 170  | 180   | 190                   | °C   | _       | P_5.3.3 |

| Thermal shutdown hysteresis | ΔΤ                  | -    | 6     | _                     | K    | _       | P_5.3.4 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-7 at natural convection on FR4 2s2p board; The TLE9222 (PGTSSOP-14) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu).

# **6** Electrical Characteristics

# **6.1** Functional Device Characteristics

# Table 9 Electrical Characteristics

| Parameter                                            | Symbol                   |      | Value | S    | Un | <b>Note or Test Condition</b>                                                                                               | Number   |  |

|------------------------------------------------------|--------------------------|------|-------|------|----|-----------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                      |                          | Min. | Тур.  | Max  | it |                                                                                                                             |          |  |

| Current Consumption V <sub>cc</sub> Powe             | r Supply                 |      |       | •    |    |                                                                                                                             |          |  |

| Current Consumption in BD_Normal mode                | iV <sub>CC</sub>         | -    | 33    | 40   | mA | Transmitter active                                                                                                          | P_6.1.1  |  |

| Current Consumption in BD_Normal mode                | iV <sub>CC_idle</sub>    | _    | 6     | 15   | mA | Transmitter idle;                                                                                                           | P_6.1.2  |  |

| Current Consumption in BD_Standby mode               | iV <sub>CC_Stb_150</sub> | -    | 30    | 40   | μΑ | T <sub>J</sub> ≤ 150°C;<br>No bus activity or local<br>errors detected; Logic<br>inputs in default states;<br>ERRN = "high" | P_6.1.3  |  |

| Current Consumption in BD_Standby mode               | iV <sub>CC_Stb_85</sub>  | -    | 17    | 25   | μΑ | T <sub>J</sub> ≤ 85°C; No bus activity<br>or local errors detected;<br>Logic inputs in default<br>states; ERRN = "high"     | P_6.1.4  |  |

| Current Consumption in BD_Off condition              | iV <sub>CC_Off</sub>     | -    | -     | 35   | μΑ | Logic inputs in default states;                                                                                             | P_6.1.5  |  |

| Current Consumption V <sub>10</sub> Refere           | ence                     |      |       |      |    |                                                                                                                             |          |  |

| Current Consumption in BD_Normal mode                | iV <sub>IO</sub>         | -    | 0.15  | 0.5  | mA | -                                                                                                                           | P_6.1.6  |  |

| Current Consumption in BD_Standby mode               | iV <sub>IO_Stb</sub>     | -    | 1     | 5    | μΑ | No bus activity or local<br>errors detected; Logic<br>inputs in default states;<br>ERRN = "high"                            | P_6.1.7  |  |

| Current Consumption in BD_Off condition              | iV <sub>IO_Off</sub>     | -    | -     | 5    | μΑ | Logic inputs in default states                                                                                              | P_6.1.8  |  |

| Undervoltage Detection V <sub>CC</sub> Pov           | ver Supply               | •    | •     |      |    |                                                                                                                             |          |  |

| Undervoltage detection threshold on V <sub>CC</sub>  | uBDUVV <sub>CC</sub>     | 4.0  | 4.25  | 4.75 | V  | _                                                                                                                           | P_6.1.9  |  |

| Undervoltage detection hysteresis on V <sub>CC</sub> | uBDUVV <sub>CC_Hy</sub>  | _    | 100   | _    | mV | _                                                                                                                           | P_6.1.10 |  |

# **Table 9 Electrical Characteristics** (cont'd)

| Parameter                                                   | Symbol                        |      | Value | S   | Un | Note or Test Condition                                                    | Number   |  |

|-------------------------------------------------------------|-------------------------------|------|-------|-----|----|---------------------------------------------------------------------------|----------|--|

|                                                             |                               | Min. | Тур.  | Max | it |                                                                           |          |  |

| Power-on reset threshold                                    | uBDPDV <sub>CC</sub>          | 1.5  | 2.5   | 3.5 | ٧  | -                                                                         | P_6.1.11 |  |

| Transition time to BD_Standby mode after power-up           | dBD <sub>Power</sub>          | _    | 50    | 100 | μs | $V_{\rm CC} > uBDPDV_{\rm CC}$                                            | P_6.1.12 |  |

| Undervoltage filter time                                    | dBDUVV <sub>CC_blk</sub>      | 3    | _     | 10  | μs | 1)                                                                        | P_6.1.13 |  |

| Undervoltage detection time                                 | dBDUVV <sub>CC</sub>          | 3    | 40    | 100 | μs | Time between under-<br>voltage event and forced<br>mode change            | P_6.1.14 |  |

| Undervoltage recovery time                                  | dBDRV <sub>CC</sub>           | 3    | 40    | 100 | μs | Time between undervoltage recovery and forced mode change                 | P_6.1.15 |  |

| Undervoltage Detection $V_{10}$ Ref                         | erence                        |      |       |     |    |                                                                           |          |  |

| Undervoltage detection threshold on $V_{10}$                | $uUV_{1O}$                    | 2.5  | 2.7   | 3.0 | V  | _                                                                         | P_6.1.16 |  |

| Undervoltage detection hysteresis on V <sub>IO</sub>        | uBDUVV <sub>IO_Hys</sub>      | -    | 30    | _   | mV | -                                                                         | P_6.1.17 |  |

| Undervoltage filter time                                    | dBDUVV <sub>IO_blk</sub>      | 1    | _     | 10  | μs | 1)                                                                        | P_6.1.18 |  |

| Undervoltage detection time                                 | dBDUVV <sub>IO</sub>          | 1    | 40    | 100 | μs | Time between under-<br>voltage event and forced<br>mode change            | P_6.1.19 |  |

| Undervoltage recovery time                                  | dBDRV <sub>IO</sub>           | 1    | 40    | 100 | μs | Time from recovery until possible mode change                             | P_6.1.20 |  |

| Digital Output RxD                                          |                               | l.   | 11    |     |    | ,                                                                         |          |  |

| High level output voltage                                   | uV <sub>Dig_Out_High</sub>    | 80   | _     | 100 | %  | Relative to $uV_{10}$ ; $iRxD_{H} = -2 \text{ mA}$ ;                      | P_6.1.21 |  |

| Low level output voltage                                    | uV <sub>Dig_Out_Low_</sub>    | -    | -     | 20  | %  | Relative to $uV_{IO}$ ;<br>$iRxD_L = 2 \text{ mA}$ ;                      | P_6.1.22 |  |

| Output voltage while $uV_{10}$ is in undervoltage condition | uV <sub>Dig_Out_UV_R</sub> xD | -    | -     | 250 | mV | $uV_{IO} < uUV_{IO}$ ;<br>100 kΩ load to GND;                             | P_6.1.23 |  |

| Output voltage while in BD_Off condition                    | uV <sub>Dig_Out_Off_R</sub>   | -    | -     | 100 | mV | 100 kΩ load to GND;                                                       | P_6.1.24 |  |

| Rise time on the RxD output                                 | dBDRxD <sub>R15</sub>         | -    | 2     | 6   | ns | 20 % $\rightarrow$ 80% of $uV_{IO}$ ;<br>$C_{BDRxD} = 15 \text{ pF}$      | P_6.1.25 |  |

| Fall time on the RxD output                                 | dBDRxD <sub>F15</sub>         | -    | 2     | 6   | ns | 80 % $\rightarrow$ 20% of $uV_{IO}$ ;<br>$C_{BDRXD} = 15 \text{ pF}$      | P_6.1.26 |  |

| Rise time on the RxD output                                 | dBDRxD <sub>R25</sub>         | -    | 3     | 8   | ns | $20 \% \rightarrow 80\% \text{ of } uV_{IO};$ $C_{BDRxD} = 25 \text{ pF}$ | P_6.1.27 |  |

# **Table 9 Electrical Characteristics** (cont'd)

| Parameter                                                   | Symbol                                           |      | Value | S   | Un | <b>Note or Test Condition</b>                                             | Number   |

|-------------------------------------------------------------|--------------------------------------------------|------|-------|-----|----|---------------------------------------------------------------------------|----------|

|                                                             |                                                  | Min. | Тур.  | Max | it |                                                                           |          |

| Fall time on the RxD output                                 | dBDRxD <sub>F25</sub>                            | _    | 3     | 8   | ns | 80 % → 20% of $uV_{10}$ ;<br>$C_{BDRxD} = 25 \text{ pF}$                  | P_6.1.28 |

| Sum of rise and fall time on the RxD output                 | dBDRxD <sub>R15</sub> +<br>dBDRxD <sub>F15</sub> | _    | 4     | 12  | ns | $C_{\rm BDRxD} = 15  \rm pF;$                                             | P_6.1.29 |

| Difference of rise and fall time on the RxD output          | $ dBDRxD_{R15} - dBDRxD_{F15} $                  | -    | 1     | 2.5 | ns | $C_{\rm BDRxD} = 15  \rm pF;$                                             | P_6.1.30 |

| Sum of rise and fall time on the RxD output                 | dBDRxD <sub>R25</sub> +<br>dBDRxD <sub>F25</sub> | _    | 6     | 13  | ns | $C_{\rm BDRxD} = 25  \rm pF;$                                             | P_6.1.31 |

| Difference of rise and fall time on the RxD output          | dBDRxD <sub>R25</sub> -<br>dBDRxD <sub>F25</sub> | -    | 1     | 2.5 | ns | $C_{\rm BDRxD} = 25  \rm pF;$                                             | P_6.1.32 |

| Digital Output ERRN                                         | 1                                                |      |       |     |    |                                                                           | 11.      |

| High level output voltage                                   | uV <sub>Dig_Out_High</sub>                       | 80   | -     | 100 | %  | Relative to $uV_{10}$ ; $iERRN_H = -2 \text{ mA}$ ;                       | P_6.1.33 |

| Low level output voltage                                    | uV <sub>Dig_Out_Low_</sub>                       | -    | -     | 20  | %  | Relative to $uV_{10}$ ; $iERRN_L = 2 \text{ mA}$ ;                        | P_6.1.34 |

| Output voltage while $uV_{IO}$ is in undervoltage condition | uV <sub>Dig_Out_UV_E</sub>                       | -    | -     | 250 | mV | $uV_{10} < uUV_{10}$ ;<br>100 kΩ load to GND;                             | P_6.1.35 |

| Output voltage while in BD_Off condition                    | uV <sub>Dig_Out_UFF_</sub>                       | -    | -     | 100 | mV | 100 kΩ load to GND;                                                       | P_6.1.36 |

| Rise time on the ERRN output                                | dBDERRN <sub>R25</sub>                           | -    | 3     | 8   | ns | 1); 20 % $\rightarrow$ 80% of $uV_{10}$ ;<br>$C_{BDERRN} = 25 \text{ pF}$ | P_6.1.37 |

| Fall time on the ERRN output                                | dBDERRN <sub>F25</sub>                           | -    | 3     | 8   | ns | 1); 80 % $\rightarrow$ 20% of $uV_{10}$ ;<br>$C_{BDERRN} = 25 \text{ pF}$ | P_6.1.38 |

| Reaction time on the ERRN pin                               | dReactionTi<br>me <sub>ERRN</sub>                | -    | 5     | 30  | μs | -                                                                         | P_6.1.39 |

| Digital Output SDO                                          | 1                                                |      | 1     |     |    |                                                                           | 1        |

| High level output voltage                                   | uV <sub>Dig_Out_High</sub>                       | 80   | -     | 100 | %  | Relative to $uV_{10}$ ; $iSDO_{H} = -2 \text{ mA}$ ;                      | P_6.1.40 |

| Low level output voltage                                    | uV <sub>Dig_Out_Low_</sub>                       | -    | -     | 20  | %  | Relative to $uV_{10}$ ; $iSDO_L = 2 \text{ mA}$ ;                         | P_6.1.41 |

| Leakage current while in high impedance state               | iBDSDO <sub>Z</sub>                              | -1   | -     | 1   | μΑ | 0V < <i>uSDO</i> < <i>uV</i> <sub>IO</sub> ;<br>SCSN = "high"             | P_6.1.42 |

| Rise time on the SDO output                                 | dBDSDO <sub>R25</sub>                            | -    | 3     | 8   | ns | 1); 20 % $\rightarrow$ 80% of $uV_{10}$ ;<br>$C_{BDSDO} = 25 \text{ pF}$  | P_6.1.43 |

| Fall time on the SDO output                                 | dBDSDO <sub>F25</sub>                            | -    | 3     | 8   | ns | 1); 80 % $\rightarrow$ 20% of $uV_{10}$ ;<br>$C_{BDSDO} = 25 \text{ pF}$  | P_6.1.44 |

# **Table 9 Electrical Characteristics** (cont'd)

| Parameter                                                | Symbol                       | Values |      |          | Un | <b>Note or Test Condition</b>         | Number   |

|----------------------------------------------------------|------------------------------|--------|------|----------|----|---------------------------------------|----------|

|                                                          |                              | Min.   | Тур. | Max<br>• | it |                                       |          |

| Reaction time for setting SDO output to "high impedance" | dSPI <sub>SDOZ</sub>         | -      | _    | 250      | ns | 1)                                    | P_6.1.45 |

| Digital Input TxD                                        |                              | 1      |      |          |    |                                       | 1        |

| Threshold for detecting logical "high"                   | uBDLogic_1                   | _      | _    | 60       | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.46 |

| Threshold for detecting logical "low"                    | uBDLogic_0                   | 40     | _    | _        | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.47 |

| High level input current                                 | iBDLogic_1                   | 20     | _    | 200      | μΑ | -                                     | P_6.1.48 |

| Low level input current                                  | iBDLogic_0                   | -1     | -    | 1        | μΑ | -                                     | P_6.1.49 |

| Input capacitance on pin TxD                             | C_BDTxD                      | -      | _    | 5        | pF | 1)                                    | P_6.1.50 |

| Digital Input TxEN                                       |                              |        |      |          |    |                                       |          |

| Threshold for detecting logical "high"                   | uV <sub>Dig_In_High_T</sub>  | _      | _    | 70       | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.51 |

| Threshold for detecting logical "low"                    | uV <sub>Dig_In_Low_T</sub>   | 30     | _    | _        | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.52 |

| High level input current                                 | i <sub>Dig_In_High_TxE</sub> | -1     | _    | 1        | μΑ | -                                     | P_6.1.53 |

| Low level input current                                  | i <sub>Dig_In_Low_TxE</sub>  | -200   | _    | -20      | μΑ | -                                     | P_6.1.54 |

| Input capacitance on pin TxEN                            | C_BDTxEN                     | -      | -    | 5        | pF | 1)                                    | P_6.1.55 |

| Maximum transmitter activation time                      | dBDTxActive<br>Max           | 1500   | _    | 2600     | μs | -                                     | P_6.1.56 |

| Digital Input BGE                                        | ,                            |        |      |          |    |                                       | 1        |

| Threshold for detecting logical "high"                   | uV <sub>Dig_In_High_B</sub>  | _      | _    | 70       | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.57 |

| Threshold for detecting logical "low"                    | uV <sub>Dig_In_Low_B</sub>   | 30     | -    | -        | %  | Relative to <i>uV</i> <sub>IO</sub> ; | P_6.1.58 |

| High level input current                                 | i <sub>Dig_In_High_BGE</sub> | 20     | -    | 200      | μΑ | -                                     | P_6.1.59 |

| Low level input current                                  | i <sub>Dig_In_Low_BGE</sub>  | -1     | -    | 1        | μΑ | -                                     | P_6.1.60 |

| Transmitter activation delay BGE, Idle → active          |                              | -      | 50   | 75       | ns | $R_{\rm DCLOAD} = 40 \Omega$          | P_6.1.61 |

| Transmitter deactivation delay BGE, Active → idle        | dBDBGEai                     | -      | 50   | 75       | ns | $R_{\rm DCLOAD} = 40 \ \Omega$        | P_6.1.62 |

| Input capacitance on pin BGE                             | C_BDBGE                      | _      | _    | 5        | pF | 1)                                    | P_6.1.63 |

# **Table 9 Electrical Characteristics** (cont'd)

| Parameter                                        | Symbol                       |      | Value | S        | Un | <b>Note or Test Condition</b>                                                     | Number   |

|--------------------------------------------------|------------------------------|------|-------|----------|----|-----------------------------------------------------------------------------------|----------|

|                                                  |                              | Min. | Тур.  | Max<br>• | it |                                                                                   |          |

| Threshold for detecting logical "high"           | UV <sub>Dig_In_High_S</sub>  | _    | _     | 70       | %  | Relative to $uV_{10}$ ;                                                           | P_6.1.64 |

| Threshold for detecting logical "low"            | uV <sub>Dig_In_Low_S</sub>   | 30   | -     | _        | %  | Relative to $uV_{IO}$ ;                                                           | P_6.1.65 |

| High level input current                         | i <sub>Dig_In_High_STB</sub> | 20   | -     | 200      | μΑ | -                                                                                 | P_6.1.66 |

| Low level input current                          | i <sub>Dig_In_Low_STB</sub>  | -1   | -     | 1        | μΑ | -                                                                                 | P_6.1.67 |

| Mode transition time after applying host command | dBD <sub>ModeChang</sub>     | _    | -     | 100      | μs | -                                                                                 | P_6.1.68 |

| Filter time for detection of host commands       | dBDLogic <sub>Filte</sub>    | 2    | -     | 6        | μs | -                                                                                 | P_6.1.69 |

| Input capacitance on pin STBN                    | C_BDSTBN                     | -    | _     | 5        | pF | 1)                                                                                | P_6.1.70 |

| Digital Input SCLK                               |                              | •    |       |          | •  |                                                                                   | •        |

| Threshold for detecting logical "high"           | UV <sub>Dig_In_High_S</sub>  | _    | _     | 70       | %  | Relative to $uV_{10}$ ;                                                           | P_6.1.71 |

| Threshold for detecting logical "low"            | UV <sub>Dig_In_Low_S</sub>   | 30   | -     | _        | %  | Relative to <i>uV</i> <sub>IO</sub> ;                                             | P_6.1.72 |

| High level input current                         | i <sub>Dig_In_High_SCL</sub> | 20   | _     | 200      | μΑ | -                                                                                 | P_6.1.73 |

| Low level input current                          | i <sub>Dig_In_Low_SCL</sub>  | -1   | -     | 1        | μΑ | -                                                                                 | P_6.1.74 |

| SPI clock period                                 | dSPI <sub>Clock</sub>        | 0.25 | _     | 100      | μs | -                                                                                 | P_6.1.75 |

| SPI enable time                                  | dSPI <sub>Lead</sub>         | 250  | -     | _        | ns | _                                                                                 | P_6.1.76 |

| SPI enable time                                  | dSPI <sub>LeadStbOK</sub>    | 4    | _     | _        | μs | BD_Standby mode;<br>No Wake or errors<br>detected; STBN = "low";<br>ERRN = "high" | P_6.1.77 |

| SPI disable time                                 | dSPI <sub>Lag</sub>          | 250  | _     | _        | ns | $C_{\rm BDSDO} = 25  \rm pF$                                                      | P_6.1.78 |

| Input capacitance on pin SCLK                    | C_BDSCLK                     | _    | _     | 5        | pF | 1)                                                                                | P_6.1.79 |

| Digital Input SCSN                               |                              |      |       |          |    |                                                                                   |          |

| Threshold for detecting logical "high"           | UV <sub>Dig_In_High_S</sub>  | _    | -     | 70       | %  | Relative to $uV_{10}$ ;                                                           | P_6.1.80 |

| Threshold for detecting logical "low"            | uV <sub>Dig_In_Low_S</sub>   | 30   | -     | _        | %  | Relative to <i>uV</i> <sub>IO</sub> ;                                             | P_6.1.81 |

# **Table 9 Electrical Characteristics** (cont'd)

| Parameter                                                             | Symbol                            |      | Value | s   | Un | Note or Test Condition                           | Number   |

|-----------------------------------------------------------------------|-----------------------------------|------|-------|-----|----|--------------------------------------------------|----------|

|                                                                       |                                   | Min. | Тур.  | Max | it |                                                  |          |