| MW8209 Datasheet              |

|-------------------------------|

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

| MW8209                        |

| USB 2.0 FLASH DISK CONTROLLER |

| Data Sheet                    |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

#### **KEY FEATURS**

### USB 2.0 Interface compatible with Mass Storage Device Class

- Integrated USB 2.0 PHY

- Supports USB High Speed and Full Speed

- Suspend and Resume operations

### Most Widely FLASH Support

- Supports all type of NAND Flash devices ST, Hynix, Samsung, Toshiba, Micron, Infineon and Renesas

- Supports AND, AG-AND, SuperAND Flash from Renesas

- Reed-Solomon Encoder/Decoder on-the-fly correction

(5 bytes of a 528-byte block)

- Flash identification support

- Up to 16MB/s for read and 9MB/s for write operations with single channel

#### Supply Management

- Single 5.0V operation

- Integrated 5.0V-3.3V voltage regulator

- Integrated 3.3V-1.8V voltage regulator

### ■ Embedded 8-bit Single Cycle MCU

- 80C51 compatible 8-bit Microprocessor

#### USB 2.0 low-power device compliant

- Less than 80mA during write operation

- Less than 500µA in suspend mode

#### Clock Management

Integrated PLL for generating core and

USB 2.0 clock sources using an external 12 MHz crystal

### Development support

- Complete reference design including schematics, BOM and Gerber files

- Supports Windows XP, Windows 2K, Windows ME, Linux and MacOS. Drivers available for Windows 98 SE

#### Abundance GPIO for Application Usage

- Up to 28 GPIOs

- Integrated I<sup>2</sup>C Logic

- Integrated UART Logic

### Flexible Boot Mode Select

Configurable Boot from I<sup>2</sup>C Logic,

IO Logic

### 64BIT Chip ID support

- The 64bit Chip ID is unique and can be read out by user for any application purpose

### Multi-partition support

Each partition can be defined as one of CDROM, HDD, ZIP or Secure-Disk

### Data Protection

- Write protect switch control

- Public/Private partitions support

#### Design For downgrade FLASH support

- Optimized hardware unit for fast and efficiency disk scanning

- Up to 5bits per 528bytes block ECC of random error

- Up to 5bytes per 528bytes block ECC of total error

#### Sectors Management

-

- Support wear-level arithmetic

- Support bad block dynamic exclusion arithmetic

- Dual-Channel Support for High Speed Application and up to 8 banks FLASH

- Up to 18MB/s write and 29MB/s read

- Up to 12 FLASH chips in series

- Support Serial-EEPROM

- Bootability support

- Support HDD mode and ZIP mode

- Device configurable Parameters :

- USB Vendor ID/Product ID (VID/PID), Serial Number and USB strings with foreign language support

- SCSI strings

- LED outputs Mode

- Adjustable Flash bus frequency to reach highest performance

- Code update in the Flash or E<sup>2</sup>PROM

- LQFP48 7mmx7mm Lead-Free package

- Fabricated in 0.18um CMOS process

# **Table of Contents**

| 1 INTRODUCTION                       | 5    |

|--------------------------------------|------|

| 2 PIN DESCRIPTION                    | . 7  |

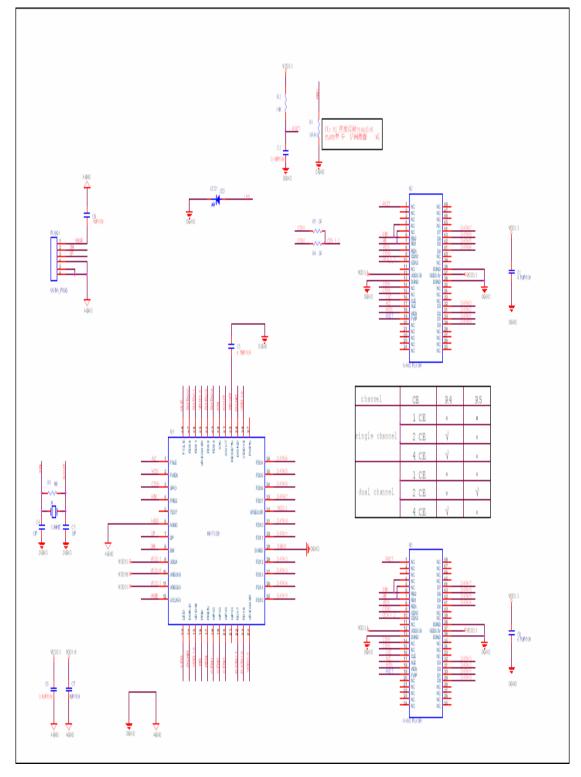

| 3 APPLICATION SCHEMATICS             | . 10 |

| 4 ELECTRICAL CHARACTERISTICS         | . 11 |

| 4.1 PARAMETER CONDITIONS             | 11   |

| 4.1.1 Minimum and Maximum values     | 11   |

| 4.1.2 Typical values                 | 11   |

| 4.1.3 Typical curves                 | 11   |

| 4.1.4 Loading capacitor              | 11   |

| 4.1.5 Pin input voltage              | 11   |

| 4.2 ABSOLUTE MAXIMUM RATINGS         | 12   |

| 4.2.1 Voltage Characteristics        | 12   |

| 4.2.2 Current Characteristics        | 12   |

| 4.2.3 Thermal Characteristics        | 12   |

| 4.3 OPERATING CONDITIONS             | 13   |

| 4.3.1 General Operating Conditions   | 13   |

| 4.4 SUPPLY CURRENT CHARACTERISTICS   | 13   |

| 4.4.1 RUN and SUSPEND Modes          | 13   |

| 4.5 CLOCK AND TIMING CHARACTERISTICS | 14   |

| 4.5.1 Crystal Oscillator             | 14   |

| 4.6 I/O PORT PIN CHARACTERISTICS     | 15   |

| 4.6.1 General Characteristics        | 15   |

| 4.6.2 USB (Universal Bus Interface)  | 16   |

| 5 PACKAGE MECHANICAL DATA            | . 17 |

| 6 DEVICE ORDERING INFORMATION        | . 18 |

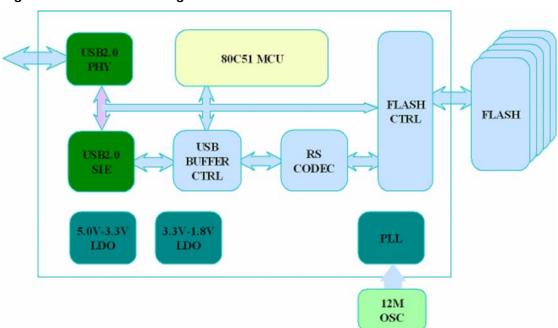

#### 1 INTRODUCTION

The MW8209 is a USB 2.0 high-speed Flash Drive controller. The USB 2.0 high-speed interface including PHY and function supports USB 2.0 Mass Storage Device Class.

The Mass Storage Controller Interface combined with the Reed-Solomon Encoder/Decoder on-the-fly correction (5-byte on 528-byte data blocks) provides a flexible, high transfer rate solution for interfacing a wide of range Flash memory device types. The internal 60 MHz PLL driven by the 12MHz Oscillator is used to generate the 480MHz frequency for the USB 2.0 PHY.

The Integrated 80C51 MCU runs the application program from the internal ROM and RAM. USB data and patch code are stored in internal RAM.

I/O ports provide functions for EEPROM, LED and write protect switch control. The internal 5.0V to 3.3V and 3.3V to 1.8V voltage regulator provides the 3.3V and 1.8V supply voltage to the digital part of the circuit.

MW8209 has optimized internal structure and techniques designed special for MLC process. With dual-channel and up to 5bytes ECC support, make MLC present excellence performance as SLC NAND Flash.

MW8209 supports all the FLASH on the today's market. Include normal SLC/MLC NAND flash, AND/AG-AND and Super-AND flash produced by Renesas, Or-NAND flash produce by Micron. It supports 8bit/16bit bus spec, with big/small or large page type of all kinks of FLASH. With advanced I/O pad process, the controller can support wide I/O voltage range from 1.8V to 3.3V LVCMOS logic.

MW8209 has a very flexible and configurable interface and internal resource for future FLASH compatible.

MW8209 supports boot from NAND flash, I<sup>2</sup>C bus or GPIO logic. Which make support for future flash process be possible. The firmware can be downloaded to NAND flash or E<sup>2</sup>PROM via on chip bus logic. The boot-loader resided in the inner ROM will load the outer codes if necessary.

The code in the NAND or E<sup>2</sup>PROM can be used for multi-purpose. For example, implement user-defined functions such as USB finger-scanner, USB-Key and USB-Ad Disk. In such application, mounting E<sup>2</sup>PROM via On-Chip I<sup>2</sup>C bus prefer to a NAND flash device.

MW8209 has a UID generating unit implemented by especial process. Which can generate a Unique Identify Code for each die. The UID is 64bits long and can be read out by private command. The ID can be used for the application that requires high security. For example, finance market, personal identify, high security data storage, protecting your Intellectual Property and so on.

MW8209 has consider this impenetrate its design cycle. Now our controller has optimized hardware unit for fast and efficiency disk scanning. It provides scan patterns like memory BIST algorithm. And there are several scan pattern can be configured by user. With our special hardware support, the disk scanning will achieved the fastest speed and highest efficiency.

The Controller supports on-chip I $^2$ C and UART logic. Together with the C51 compatible MCU core, make it very suitable for value-extended produce. The I $^2$ C bus and UART can be interface to many miscellaneous peripherals. The controller also provide up to 28 GPIO . All the GPIO can be programmed to input or output pins respectively, support to interface more I/O devices or user-defined control logic.

Figure 1. Device Block Diagram

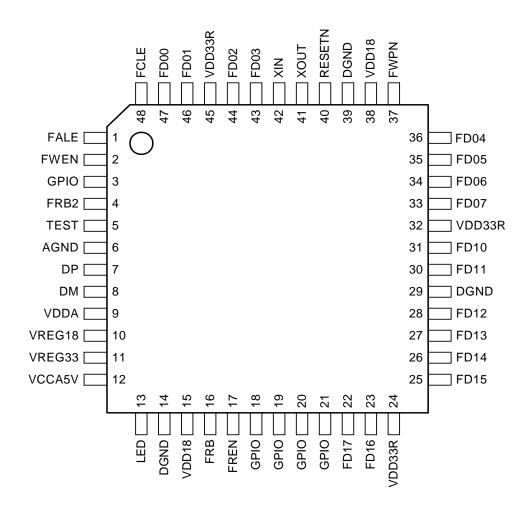

### 2 PIN DESCRIPTION

Figure 2. 48-Pin TQFP Package Pin-out

### PIN DESCRIPTION (Cont'd) - MW8209 Compatible

### Legend / Abbreviations for tables:

Type: I = input, O = output, S = supply Input level: A = Dedicated analog input

In/Output level: CT = CMOS 0.3VDD/0.7VDD with input trigger

TT= TTL 0.8V / 2V with Schmitt trigger

Output level: D8 = 8mA drive

D4 = 4mA drive

D2 = 2mA drive

DZ ZIIII T GIIVC

### Table 1. Power Supply

| LQFP48 Pin Name Type Description | LQFP48 |

|----------------------------------|--------|

|----------------------------------|--------|

| Pin |        |   |                                |  |

|-----|--------|---|--------------------------------|--|

| 6   | AGND   | S | Analog GND for USB PLUG        |  |

| 10  | VREG18 | S | Internal LDO 1.8V output       |  |

| 9   | VDDA   | S | Analog Voltage Input 3.3V      |  |

| 11  | VREG33 | S | Internal LDO 3.3V output       |  |

| 12  | VCCA5V | S | Power Supply Input 5.0V (VBUS) |  |

| 14  | DGND   | S | Digital Ground                 |  |

| 15  | VDD18  | S | Core Voltage Input 1.8V        |  |

| 24  | VDD33R | S | I/O Voltage Input 3.3V         |  |

| 29  | DGND   | S | Digital Ground                 |  |

| 32  | VDD33R | S | I/O Voltage Input 3.3V         |  |

| 38  | VDD18  | S | Core Voltage Input 1.8V        |  |

| 39  | DGND   | S | Digital Ground                 |  |

| 45  | VDD33R | S | I/O Voltage Input 3.3V         |  |

# Table 2. Control & System

| LQFP48<br>Pin | Pin Name | Type | Description                         |

|---------------|----------|------|-------------------------------------|

| 40            | RESETN   | I    | Controller Reset , Low Level Active |

| 5             | TEST     | I    | Test Mode Select                    |

| 42            | XIN      | I    | 12MHz OSC Input                     |

| 41            | XOUT     | О    | 12MHz OSC Output                    |

### Table 3. USB 2.0 Interface

| LQFP48<br>Pin | Pin Name | Type | Description |

|---------------|----------|------|-------------|

| 7             | DP       | I/O  | USB2 DATA + |

| 8             | DM       | I/O  | USB2 DATA - |

Table 4. General Purpose IO Ports / Mass Storage IOs

| LQFP48 | Pin Name | Type | Main Function                      | Alternate |

|--------|----------|------|------------------------------------|-----------|

| Pin    |          |      |                                    | Function  |

| 13     | LED      | 0    | Bus Transmit LED Driver            |           |

| 47     | FD00     | I/O  | FLASH Data Bus 0 (Chan.1)          | GPIO      |

| 46     | FD01     | I/O  | FLASH Data Bus 1 (Chan.1)          | GPIO      |

| 44     | FD02     | I/O  | FLASH Data Bus 2 (Chan.1)          | GPIO      |

| 43     | FD03     | I/O  | FLASH Data Bus 3 (Chan.1)          | GPIO      |

| 36     | FD04     | I/O  | FLASH Data Bus 4 (Chan.1)          | GPIO      |

| 35     | FD05     | I/O  | FLASH Data Bus 5 (Chan.1)          | GPIO      |

| 34     | FD06     | I/O  | FLASH Data Bus 6 (Chan.1)          | GPIO      |

| 33     | FD07     | I/O  | FLASH Data Bus 7 (Chan.1)          | GPIO      |

| 37     | FWPN     | 0    | FLASH Write Protect enable, Active | GPIO      |

|        |          |      | Low                                |           |

| 2      | FWEN     | 0    | FLASH Write Enable                 | GPIO      |

# MW8209 Datasheet

| 1  | FALE | 0   | FLASH Address Latch       | GPIO |

|----|------|-----|---------------------------|------|

| 48 | FCLE | 0   | FLASH Command Latch       | GPIO |

| 17 | FREN | 0   | FLASH Read Enable         | GPIO |

| 16 | FRB  | I   | FLASH Read/Busy (Chan.1)  | GPIO |

| 31 | FD10 | I/O | FLASH Data Bus 0 (Chan.2) | GPIO |

| 30 | FD11 | I/O | FLASH Data Bus 1 (Chan.2) | GPIO |

| 28 | FD12 | I/O | FLASH Data Bus 2 (Chan.2) | GPIO |

| 27 | FD13 | I/O | FLASH Data Bus 3 (Chan.2) | GPIO |

| 26 | FD14 | I/O | FLASH Data Bus 4 (Chan.2) | GPIO |

| 25 | FD15 | I/O | FLASH Data Bus 5 (Chan.2) | GPIO |

| 23 | FD16 | I/O | FLASH Data Bus 6 (Chan.2) | GPIO |

| 22 | FD17 | I/O | FLASH Data Bus 7 (Chan.2) | GPIO |

| 4  | FRB2 | I   | FLASH Read/Busy (Chan.2)  | GPIO |

| 3  | GPIO | I/O |                           | GPIO |

| 18 | GPIO | I/O |                           | GPIO |

| 19 | GPIO | I/O |                           | GPIO |

| 20 | GPIO | I/O |                           | GPIO |

| 21 | GPIO | I/O |                           | GPIO |

Figure 3. Application Schematic Sheet

# 4 ELECTRICAL CHARACTERISTICS

### **4.1 PARAMETER CONDITIONS**

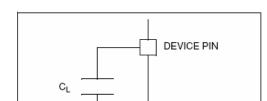

Figure 4. Pin loading conditions

Unless otherwise specified, all voltages are referred to VSS (Digital Ground).

#### 4.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the Devices with an ambient temperature at  $T_A$ =25°C and  $T_A$ = $T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3  $\Sigma$ ).

#### 4.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$ =25°C, VCCA5 = 5.0V or VDD33A=3.3V with internal LDO bypass. They are given only as design guidelines and are not tested.

#### 4.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 4.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 4.

#### 4.2 ABSOLUTE MAXIMUM RATINGS

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the Device. This is a stress rating only and functional operation of the Device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 5

| Symbol                 | Ratings                    | Max. Value | Unit |

|------------------------|----------------------------|------------|------|

| VDD33A                 | Supply Voltage             | 3.6        | V    |

| DP 、DM                 | Input Voltage On Pin       | 5.5        | V    |

| $V_{\mathrm{IN}}$      | Input Voltage On other Pin | 3.6        | V    |

| V <sub>ESD</sub> (HBM) | ESD for Human Body Mode    | 2000       | V    |

| V <sub>ESD</sub> (MM)  | ESD for Machine Mode       | 200        | V    |

### 4.2.1 Voltage Characteristics with internal LDO (VCC = VCCA5 = 5.0V supply)

### Table 6

| Symbol                 | Ratings                    | Max. Value | Unit |

|------------------------|----------------------------|------------|------|

| VCCA5                  | Supply Voltage             | 5.5        | V    |

| DP 、DM                 | Input Voltage On Pin       | 5.5        | V    |

| $V_{IN}$               | Input Voltage On other Pin | 3.6        | V    |

| V <sub>ESD</sub> (HBM) | ESD for Human Body Mode    | 2000       | V    |

| $V_{ESD}(MM)$          | ESD for Machine Mode       | 200        | V    |

### **4.2.2** Current Characteristics (Digital Parts)

#### Table 7

| Symbol               | Ratings                                      | Max. Value | Unit |

|----------------------|----------------------------------------------|------------|------|

| $I_{\mathrm{VDD33}}$ | Total Current into VDD33 lines (source)      | 65         | mA   |

| $I_{VSS}$            | Total Current out of VSS ground lines (sink) | 65         | mA   |

### 4.2.3 Thermal Characteristics

#### Table 8

| Symbol    | Ratings                   | Min. Value | Max. Value | Unit                   |

|-----------|---------------------------|------------|------------|------------------------|

| $T_{STG}$ | Storage temperature range | -40        | 125        | $^{\circ}\!\mathbb{C}$ |

| $To_T$    | Operating temperature     | 0          | 70         | $^{\circ}\!\mathbb{C}$ |

### **4.3 OPERATING CONDITIONS**

# 4.3.1 General Operating Conditions without internal LDO

### Table 9

| Symbol | Parameter                 | Conditions | Min | Max | Unit       |

|--------|---------------------------|------------|-----|-----|------------|

| VDD33  | Power Supply              |            | 3.0 | 3.6 | V          |

| Ta     | Ambient temperature range |            | 0   | 70  | $^{\circ}$ |

### 4.3.1 General Operating Conditions with internal LDO

### Table 10

| Symbol | Parameter    | Conditions | Min | Max | Unit |

|--------|--------------|------------|-----|-----|------|

| VCCA5  | Power Supply |            | 4.5 | 5.5 | V    |

| Ta | Ambient temperature range | 0 | 70 | ${\mathbb C}$ |

|----|---------------------------|---|----|---------------|

#### 4.4 SUPPLY CURRENT CHARACTERISTICS

#### 4.4.1 RUN and SUSPEND Modes

Table 11

| Symbol            | Parameter                      | Conditions  | Min | Тур | Max | Unit |

|-------------------|--------------------------------|-------------|-----|-----|-----|------|

| $I_{\mathrm{DD}}$ | Supply current in RUN mode     | fosc = 12M  |     |     | 55  | mA   |

| $I_{\mathrm{DD}}$ | Supply current in SUSPEND mode | Vreg33=3.3V |     |     | 250 | μА   |

|                   |                                | Ta = +25°C  |     |     |     |      |

#### 4.5 CLOCK AND TIMING CHARACTERISTICS

Subject to general operating conditions for VDD33, fosc, and TA.

### 4.5.1 Crystal Oscillator

The Device internal clock is supplied from a crystal oscillator. All the information given in this paragraph are based on characterization results with specified typical external components. In the application the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal manufacturer for more details (frequency, package, accuracy...).

Table 12

| Symbol            | Parameter                         | Conditions             | Min | Тур | Max | Unit |

|-------------------|-----------------------------------|------------------------|-----|-----|-----|------|

| Fosc              | Oscillator frequency              |                        |     | 12  |     | Mhz  |

| CK <sub>ACC</sub> | Total crystal oscillator accuracy | abs. value + temp + ag |     |     | ±60 | Ppm  |

| Aosc              | Crystal oscillator duty cycle     |                        | 45  | 50  | 55  | %    |

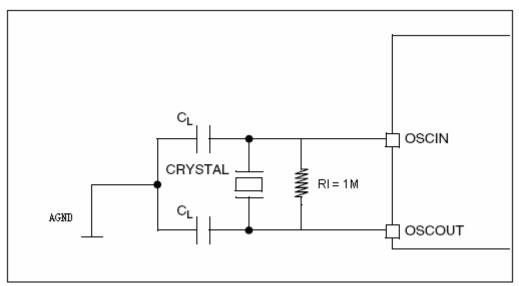

Figure 6. Typical Application with a Crystal

#### Note

1. The crystal oscillator duty cycle has to be adjusted through the two CL capacitors. Refer to the crystal manufacturer for more details. Typically,  $C_L = 12pF$

- 2.  $R_L = 1M \Omega$  for matching internal PLL (Opt.)

- 3. Depending on the crystal power dissipation, a serial resistor RsOscout may be added. Refer to the crystal manufacturer for more details. (Opt.)

#### 4.6 I/O PORT PIN CHARACTERISTICS

#### 4.6.1 General Characteristics

Subject to general operating conditions for VDD33, fosc, and T<sub>A</sub> unless otherwise specified.

Table 13

| Symbol             | Parameter                | Conditions     | Min | Тур | Max | Unit |

|--------------------|--------------------------|----------------|-----|-----|-----|------|

| $V_{\mathrm{IL}}$  | Input low level voltage  |                |     |     | 0.4 | V    |

| $V_{\mathrm{IH}}$  | Input high level voltage | TTL ports      | 1.5 |     |     | V    |

| $V_{\mathrm{hys}}$ | Schmitt trigger voltage  |                |     |     |     | mV   |

|                    | hysteresis <sup>1)</sup> |                |     |     |     |      |

| $I_{\rm L}$        | Input leakage current    | VSS≤VIN≤VDD33, |     | 1   |     | μА   |

|                    |                          | standard I/Os  |     |     |     |      |

| R <sub>PU</sub>    | Weak pull-up equivalent  | VIN=VSS        | 4.7 |     | 60  | kΩ   |

|                    | resistor <sup>2)</sup>   | VDD33=3.3V     |     |     |     |      |

#### Notes:

- 1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

- 2. The  $R_{PU}$  pull-up equivalent resistor is based on a resistive transistor. This data is based on characterization results, tested in production at VDD33 max.

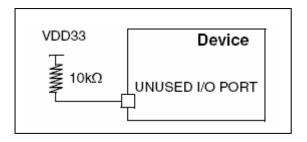

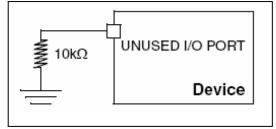

Figure 7. Two typical Applications with unused I/O Pin

#### 4.6.2 USB (Universal Bus Interface)

Table 14. USB Interface: DC Characteristics

| USB DC Electrical Characteristics |           |            |      |      |      |      |

|-----------------------------------|-----------|------------|------|------|------|------|

| Symbol                            | Parameter | Conditions | Min. | Typ. | Max. | Unit |

| $I_{\mathrm{DDsuspend}}$ | Suspend Current         | VDD33=3.3V, regulator | 0.2 1) |     | 0.25 1) | mA |

|--------------------------|-------------------------|-----------------------|--------|-----|---------|----|

|                          |                         | ON and PHY OFF        |        |     |         |    |

| $R_{PU}$                 | Pull-up Resistor 1)     |                       | 4.7    |     | 60      | ΚΩ |

| Full Speed I             | Mode (DP / DM)          |                       |        |     |         |    |

| V <sub>OH</sub>          | High Level Output       |                       |        | 3   |         | V  |

|                          | Voltage                 |                       |        |     |         |    |

| $V_{OL}$                 | Low Level Output        |                       |        | 0.2 |         | V  |

|                          | Voltage                 |                       |        |     |         |    |

| $V_{CRS}$                | Crossover Voltage       |                       | 1.4    |     | 1.9     | V  |

| High Speed I             | Mode (DP / DM)          |                       |        |     |         |    |

| V <sub>HSOH</sub>        | HS Data Signalling High |                       |        | 400 |         | mV |

| V <sub>HSOL</sub>        | HS Data Signalling Low  |                       |        | 10  |         | mV |

#### **Notes:**

- 1. Not tested in production, guaranteed by characterization.

- 2. In order to reach this value, the software must force the regulator into power down mode and the I/Os compensation cell off.

**Table 15. USB Interface: Timing**

| USB DC Ele          | USB DC Electrical Characteristics |                      |      |        |      |  |  |

|---------------------|-----------------------------------|----------------------|------|--------|------|--|--|

| Symbol              | Parameter                         | Conditions           | Min. | Max.   | Unit |  |  |

| Full Speed I        | Full Speed Mode (DP / DM)         |                      |      |        |      |  |  |

| $T_{FR}$            | Rise Time                         | C <sub>L</sub> =50pF | 10   | 15     | ns   |  |  |

| $T_{\mathrm{FF}}$   | Fall Time                         | C <sub>L</sub> =50pF | 10   | 15     | ns   |  |  |

| High Speed I        | Mode (DP / DM)                    |                      |      |        |      |  |  |

| T <sub>HSR</sub>    | Rise Time                         | $R_L$ =45 $\Omega$   |      | 500 1) | ps   |  |  |

| T <sub>HSF</sub>    | Fall Time                         | $R_L$ =45 $\Omega$   |      | 500 1) | ps   |  |  |

| T <sub>HSDRAT</sub> | HS Data Rate                      |                      |      | 480    | Mb/s |  |  |

### **Notes:**

1. Not tested in production, guaranteed by characterization.

### 5 PACKAGE MECHANICAL DATA

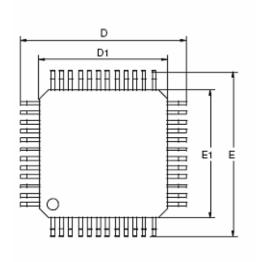

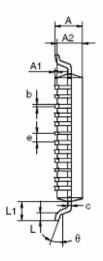

Figure 8. 48-Pin Thin Quad Flat Package

| Dim.   |      | mm   |       |        | inches | ;     |

|--------|------|------|-------|--------|--------|-------|

| Dilli. | Min  | Тур  | Max   | Min    | Тур    | Max   |

| Α      |      |      | 1.20  |        |        | 0.063 |

| A1     | 0.05 |      | 0.15  | 0.002  |        | 0.006 |

| A2     | 0.95 | 1.00 | 1.05  | 0.053  | 0.055  | 0.057 |

| b      | 0.17 | 0.22 | 0.27  | 0.007  | 0.009  | 0.011 |

| С      | 0.09 |      | 0.20  | 0.004  |        | 0.008 |

| D      |      | 9.00 |       |        | 0.354  |       |

| D1     |      | 7.00 |       |        | 0.276  |       |

| E      |      | 9.00 |       |        | 0.354  |       |

| E1     |      | 7.00 |       |        | 0.276  |       |

| е      |      | 0.50 |       |        | 0.020  |       |

| θ      | 0°   | 3.5° | 7°    | 0°     | 3.5°   | 7°    |

| L      | 0.45 | 0.60 | 0.75  | 0.018  | 0.024  | 0.030 |

| L1     |      | 1.00 |       |        | 0.039  |       |

|        |      | N    | umbei | of Pir | ıs     |       |

| N      |      |      | 4     | 8      |        |       |

# 6 DEVICE ORDERING INFORMATION

Table 16. Feature comparison table (sample)

| Part Number | Package             | Operation Voltage | Temperature Range |

|-------------|---------------------|-------------------|-------------------|

| MW8209      | LQFP\LQFP48 7mmx7mm | 3.0V ~ 3.6V       | 0℃ ~70℃           |

|             |                     |                   |                   |

| Part Number | Product Info.          | Memo                                |

|-------------|------------------------|-------------------------------------|

| MW8209      | USB2.0 Disk Controller | USB2.0 Mass Storage Disk Controller |

|             |                        |                                     |