## High-Speed Dual Pin Electronic

### AD53522

#### **FEATURES**

1000 MHz Toggle Rate

Driver/Comparator/Active Load and Dynamic Clamp

Included

Inhibit Mode Function 100-Lead LQFP Package with Built-In Heat Sink Driver

48  $\Omega$  Output Resistance 800 ps Tr/Tf for a 3 V Step

Comparator

1.1 ns Propagation Delay at 3 V

Load

±40 mA Voltage Programmable Current Range 50 ns Settling Time to 15 mV

#### **APPLICATIONS**

Automatic Test Equipment Semiconductor Test Systems Board Test Systems Instrumentation and Characterization Equipment

#### PRODUCT DESCRIPTION

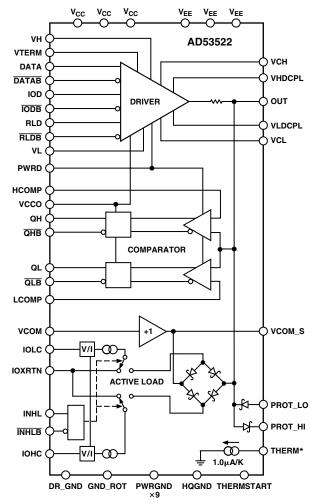

The AD53522 is a complete, high-speed, single-chip solution that performs the pin electronics functions of driver, comparator, and active load (DCL) for ATE applications. In addition, the driver contains a dynamic clamp function and the active load contains an integrated Schottky diode bridge.

The driver is a proprietary design that features three active states: Data High Mode, Data Low Mode, and Term Mode, as well as an Inhibit State. In conjunction with the integrated dynamic clamp this facilitates the implementation of a high-speed active termination. The output voltage range is -0.5 V to +6.5 V to accommodate a wide variety of test devices.

The dual comparator, with an input range equal to the driver output range, features PECL compatible outputs. Signal tracking capability is in the range of 3 V/ns.

The active load can be set for up to 40 mA load current.  $I_{OH}$ ,  $I_{OL}$ , and the buffered VCOM are independently adjustable. On-board Schottky diodes provide high-speed switching and low capacitance.

Also included on the chip is an on-board temperature sensor that gives an indication of the silicon surface temperature of the DCL. This information can be used to measure  $\theta_{JC}$  and  $\theta_{JA}$

#### **FUNCTIONAL BLOCK DIAGRAM**

\*ONLY 1 (ONE) THERM PER DEVICE

or flag an alarm if proper cooling is lost. Output from the sensor is a current sink that is proportional to absolute temperature. The gain is trimmed to a nominal value of 1.0  $\mu$ A/k $\Omega$ . As an example, the output current can be sensed by using a 10 k $\Omega$  resistor connected from 10 V to the THERM ( $I_{OUT}$ ) pin. A voltage drop across the resistor will be developed that equals: 10 k $\Omega$  × 1  $\mu$ A/k $\Omega$  = 10  $\mu$ V/k $\Omega$  = 2.98 V at room temperature.

# AD53522—SPECIFICATIONS

| Spec<br>No. | Parameter                                                            | Conditions                                                                                                      | Min        | Typ <sup>2</sup> | Max  | Unit    | Spec <sup>3</sup><br>Perf |

|-------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|------------------|------|---------|---------------------------|

|             | DIFFERENTIAL INPUT CHARAGE (DATA to DATAb, IOD to IODb, RLD to RLDb) | CTERISTICS                                                                                                      |            |                  |      |         |                           |

| 1           | Voltage Range                                                        | Note: Inputs are from Same Logic Type Family                                                                    | 0          |                  | +3.3 | V       | N                         |

| 2           | Differential Voltage with LVPECL levels                              | Differential Voltage with Note: AC Tests Performed $\pm 400 \pm 600 \pm$                                        |            | ±1000            | mV   | P       |                           |

| 3           | Bias Current                                                         | $V_{IN} = 1.5 \text{ V}, 2.5 \text{ V}$                                                                         | -250       |                  | +250 | μΑ      | P                         |

| 4           | REFERENCE INPUTS Bias Currents                                       | Max Value Measured During Linearity Tests                                                                       | -50        |                  | +50  | μΑ      | P                         |

| 10          | OUTPUT CHARACTERISTICS Logic High Range                              | Data = H, VH = $-0.4$ V to $+6.5$ V,<br>VI = $-0.5$ V (VT = 0 V, VH meets<br>test 20, 21, and 22 specs)         | -0.4       |                  | +6.5 | V       | P                         |

| 11          | Logic Low Range                                                      | Data = L, $VL = -0.5 V$ to +6.4 V,<br>VH = 6.5 V ( $VT = 0 V$ , $VL$ meets                                      | -0.5       |                  | +6.4 | V       | P                         |

| 12          | Amplitude [VH–VL]                                                    | test 30, 31, and 32 specs)<br>VL = -0.05 V, VH = +0.05 V,<br>VT = 0 V and VL = -0.5 V,<br>VH = +6.5 V, VT = 0 V | +0.1       |                  | +7.0 | V       | P                         |

|             | ABSOLUTE ACCURACY                                                    |                                                                                                                 |            |                  |      |         |                           |

| 20          | VH Offset                                                            | Data = H, VH = 0 V, VL = $-0.5$ V, VT = $+3$ V                                                                  | -50        |                  | +50  | mV      | P                         |

| 21          | VH Gain Error                                                        | Data = H, VH = $-0.4$ V to $+6.5$ V,<br>VL = $-0.5$ V, VT = $+3$ V                                              | -0.3       |                  | +0.3 | % of VH | P                         |

| 22          | Linearity Error                                                      | Data = H, VH = $-0.4$ V to $+6.5$ V,<br>VL = $-0.5$ V, VT = $+3$ V                                              | <b>-5</b>  |                  | +5   | mV      | P                         |

| 30          | VL Offset                                                            | Data = L, VL = 0 V, VH = 6.5 V,<br>VT = 3 V                                                                     | -50        |                  | +50  | mV      | P                         |

| 31          | VL Gain Error                                                        | Data = L, $VL = -0.5 V$ to +6.4 V,<br>VH = +6.5 V, $VT = +3 V$                                                  | -0.3       |                  | +0.3 | % of VL | P                         |

| 32          | Linearity Error                                                      | Data = L, VL = -0.5 V to +6.4 V,<br>VH = +6.5 V, VT = +3 V                                                      | <b>-</b> 5 |                  | +5   | mV      | P                         |

| 33          | Offset Temperature Coefficient                                       | VL = 0 V, VH = 5 V, VT = 0 V                                                                                    |            | 0.5              |      | mV/°C   | N                         |

| 40          | OUTPUT RESISTANCE<br>VH = -0.3 V                                     | $VL = -0.5 \text{ V}, VT = 0 \text{ V}, I_{OUT} = +1,$<br>+30 mA                                                | +46        |                  | +50  | Ω       | N                         |

| 41          | VH = +6.5 V                                                          | $VL = -0.5 \text{ V}, VT = 0 \text{ V}, I_{OUT} = -1,$<br>-30 mA                                                | +46        |                  | +50  | Ω       | P                         |

| 42          | VL = -0.5 V                                                          | $VH = +6.5 \text{ V}, VT = 0 \text{ V}, I_{OUT} = +1,$<br>+30 mA                                                | +46        |                  | +50  | Ω       | P                         |

| 43          | VL = +6.4 V                                                          | $VH = +6.5 \text{ V}, VT = 0 \text{ V}, I_{OUT} = -1,$ $-30 \text{ mA}$                                         | +46        |                  | +50  | Ω       | N                         |

| 44          | VH = +2.5 V                                                          | $VL = 0 \text{ V}, VT = 0 \text{ V}, I_{OUT} = -30 \text{ mA}$ (Trim Point)                                     |            | +47.5            |      | Ω       | P                         |

| 50          | Dynamic Current Limit                                                | Cbyp = 39 nF, VH = +6.5 V,<br>VL = -0.5 V, VT = 0 V                                                             | +100       |                  |      | mA      | N                         |

| 51          | Static Current Limit                                                 | Output to -0.5 V, VT = 0 V,<br>VL = -0.5 V, VT = 0 V, DATA = H                                                  | -120       |                  | -60  | mA      | P                         |

| 52          | Static Current Limit                                                 | Output to +6.5 V, VH = +6.5 V,<br>VL = -0.5 V, VT = 0 V, DATA = L                                               | +60        |                  | +120 | mA      | P                         |

-2- REV. 0

| Spec<br>No. | Parameter                      | Conditions                                                                   | Min       | Typ <sup>2</sup> | Max       | Unit                  | Spec <sup>3</sup><br>Perf |

|-------------|--------------------------------|------------------------------------------------------------------------------|-----------|------------------|-----------|-----------------------|---------------------------|

|             | VTERM                          |                                                                              |           |                  |           |                       |                           |

| 60          | Voltage Range                  | TERM MODE, VTERM = -0.3 V                                                    | -0.3      |                  | +6.3      | V                     | P                         |

|             |                                | to $+6.3 \text{ V}$ , $\text{VL} = 0 \text{ V}$ , $\text{VH} = +3 \text{ V}$ |           |                  |           |                       |                           |

|             |                                | (VTERM meets test 61, 62,                                                    |           |                  |           |                       |                           |

|             |                                | and 63 specs)                                                                |           |                  |           |                       | _                         |

| 61          | VTERM Offset                   | TERM MODE, VTERM = 0 V,                                                      | -50       |                  | +50       | mV                    | P                         |

| 60          | WEEDIN Coin France             | VL = 0 V, VH = 3 V                                                           | 0.2       |                  | 10.2      | 0/ - 637              | D.                        |

| 62          | VTERM Gain Error               | TERM MODE, VTERM = -0.3 V<br>to +6.3 V, VL = 0 V, VH = +3 V                  | -0.3      |                  | +0.3      | % of V <sub>SET</sub> | P                         |

| 63          | VTERM Linearity Error          | TERM MODE, VTERM = $-0.3 \text{ V}$                                          | <b>-5</b> |                  | +5        | mV                    | P                         |

| 03          | VIEWVIEMCATRY ETFOR            | to +6.3 V, VL = 0 V, VH = +3 V                                               | _5        |                  | 13        | 111 4                 | *                         |

| 64          | Offset Temperature Coefficient | VTERM = 0 V, VL = 0 V, VH = 3 V                                              |           | +0.5             |           | mV/°C                 | N                         |

| 70          | Output Resistance DC           | $I_{OUT}$ = +30 mA, -1 mA, VTERM =                                           | +46       |                  | +50       | Ω                     |                           |

|             |                                | -0.3  V, VH = 3  V, VL = 0  V                                                |           |                  |           |                       | N                         |

|             |                                | $I_{OUT} = -30 \text{ mA}$ , +1 mA, VTERM =                                  |           |                  |           |                       |                           |

|             |                                | +6.3  V, VH = 3  V, VL = 0  V                                                |           |                  |           |                       | N                         |

|             |                                | $I_{OUT} = \pm 30 \text{ mA}, \pm 1 \text{ mA}, \text{VTERM} =$              |           |                  |           |                       |                           |

|             |                                | +2.5  V, VH = 3  V, VL = 0  V                                                |           |                  |           |                       | P                         |

| 72          | PSRR, Drive, or TERM Mode      | $+V_S$ , $-V_S \pm 1\%$                                                      |           | 17.8             |           | mV/V                  | N                         |

| 73          | Static Current Limit           | Output to -0.3 V, VTERM = +6.3 V                                             |           |                  | -60       | mA                    | P                         |

| 74          | Static Current Limit           | Output to $+6.3 \text{ V}$ , VTERM = $-0.3 \text{ V}$                        | +60       |                  | +120      | mA                    | P                         |

|             | DYNAMIC PERFORMANCE, DR        | IVE                                                                          |           |                  |           |                       |                           |

|             | (VH and VL)                    |                                                                              |           |                  |           |                       |                           |

| 80          | Propagation Delay Time         | Measured at $50\%$ , VL = 0 V,                                               | 1.25      | 1.4              | 1.55      | ns                    | P                         |

|             |                                | VH = 3 V, into 500 $\Omega$                                                  |           | _                |           | , a                   |                           |

| 81          | Propagation Delay T.C.         | Measured at $50\%$ , VL = $0$ V,                                             |           | 2                |           | ps/°C                 | N                         |

| 82          | Delay Matching, Edge-to-Edge   | VH = 3 V, into 500 $\Omega$                                                  |           |                  | 200       |                       | P                         |

| 02          | Delay Matching, Edge-to-Edge   | Measured at 50%, VL = 0 V,<br>VH = 3 V, into 500 $\Omega$                    |           |                  | 200       | ps                    | r                         |

|             |                                | V11 = 3 V, Into 300 22                                                       |           |                  |           |                       |                           |

|             | RISE AND FALL TIMES            |                                                                              |           |                  |           |                       |                           |

| 90          | 200 mV Swing                   | Measured 20%–80%, VL = $-0.1 \text{ V}$ ,                                    |           | 0.25             |           | ns                    | N                         |

| 0.1         | 1 V Coming                     | VH = +0.1 V, into 50 $\Omega$                                                |           | 0.2              |           |                       | NT.                       |

| 91          | 1 V Swing                      | Measured 20%–80%, VL = 0 V,<br>VH = 1 V, into 50 $\Omega$                    |           | 0.3              |           | ns                    | N                         |

| 92          | 3 V Swing                      | Measured $10\%-90\%$ , VL = 0 V,                                             |           | 0.8              |           | ns                    | N                         |

| 92          | J V Swing                      | VH = 3 V, into 50 $\Omega$                                                   |           | 0.0              |           | 113                   | 1                         |

| 93          | 3 V Swing                      | Measured $10\%-90\%$ , VL = 0 V,                                             |           | 0.8              |           | ns                    | N                         |

| , ,         | J V U Mag                      | VH = 3 V, into 500 $\Omega$                                                  |           | 0.0              |           | 110                   | - '                       |

| 93A         | 3 V Swing                      | Measured $20\%-80\%$ , VL = 0 V,                                             | 0.450     | 0.560            | 0.670     | ns                    | P                         |

|             |                                | VH = 3 V, into 500 $\Omega$                                                  |           |                  |           |                       |                           |

| 94          | 5 V Swing                      | Measured $10\%-90\%$ , VL = 0 V,                                             |           | 1.2              | 1.5       | ns                    | N                         |

|             |                                | VH = 5 V, into 500 $\Omega$                                                  |           |                  |           |                       |                           |

|             | RISE AND FALL TIME TEMPER      | ATURE COEFFICIENT                                                            |           |                  |           |                       |                           |

| 100         | 1 V Swing                      | (per test 91)                                                                |           | ±2               |           | ps/°C                 | N                         |

| 101         | 3 V Swing                      | (per test 92)                                                                |           | ±2               |           | ps/°C                 | N                         |

| 102         | 5 V Swing                      | (per test 94)                                                                |           | $\pm 4$          |           | ps/°C                 | N                         |

| 110         | Overshoot and Preshoot         | VL, $VH = -0.1 V$ , $+0.1 V$ ,                                               | 0 – 50    |                  | 0 + 50    | % of Step             | N                         |

|             |                                | Driver Terminated into 50 $\Omega$                                           |           |                  |           | + mV                  |                           |

|             |                                | VL, VH = 0.0 V, 3 V,                                                         | -6.0 - 50 | )                | +6.0 + 50 | % of Step             | N                         |

|             |                                | Driver Terminated into 50 $\Omega$                                           |           |                  |           | + mV                  |                           |

| -           | SETTING TIME                   |                                                                              |           |                  |           |                       |                           |

| 120         | to 15 mV                       | VL = 0 V, $VH = 0.5 V$ , Driver                                              |           | 50               |           | ns                    | N                         |

| -           |                                | Terminated into 50 $\Omega$                                                  |           |                  |           |                       |                           |

|             |                                |                                                                              |           |                  |           |                       |                           |

REV. 0 -3-

# **SPECIFICATIONS** (continued)

# $DRIVER^1 \ \ ({\tt continued})$

| Spec<br>No. | Parameter                                          | Conditions                                                                    | Min Typ <sup>2</sup> | Max       | Unit              | Spec <sup>3</sup><br>Perf |

|-------------|----------------------------------------------------|-------------------------------------------------------------------------------|----------------------|-----------|-------------------|---------------------------|

| 130         | Delay Change vs. Pulsewidth 30 ns/90 ns, DC = 25%  | VL/VH = 0/3, $PW = 2.5  ns/7.5  ns$ ,                                         | 25                   | 75        | ps                | N                         |

| 131         | Delay Change vs. Duty Cycle                        | VL = 0 V, VH = 3 V, Duty Cycle (DC) 5 to 95%, T = 40 ns                       | 25                   |           | ps                | N                         |

| 140         | MINIMUM WIDTH PULSE 1 V Swing                      | Meas 50% point width $V_{OUT}$ AC Swing = 0.9 × $V_{OUT}$ DC                  | 0.6                  | 0.6       |                   | N                         |

| 141         | 3 V Swing                                          | Swing Terminated, 50 $\Omega$ Load on Transmission Line                       | 1.5                  |           | ns                | N                         |

| 142         | Toggle Rate                                        | VH = 1 V, VL = 0 V, Terminated to 50 $\Omega$ , V <sub>OUT</sub> > 300 mV p-p | 1000                 |           | MHz               | N                         |

|             | DYNAMIC PERFORMANCE, IN                            |                                                                               |                      |           |                   |                           |

| 150         | Delay Time, Active to Inhibit                      | Measured at 50%, VH = 4 V,<br>VL = 0 V, VTT = 2                               | 1.7                  | 2.0       | ns                | P                         |

| 151         | Delay Time, Inhibit to Active                      | Measured at 50%, VH = 4 V,<br>VL = 0 V, VTT = 2                               | 1.7                  | 2.2       | ns                | P                         |

| 152         | Delay Time Matching,<br>Inhibit to Active          | Measured at 50%, VH = 4 V,<br>VL = 0 V, VTT = 2                               | 150                  | 250       | ps                | P                         |

| 153         | Delay Time Matching,<br>Active to Inhibit          | Measured at 50%, $VH = 4 V$ ,                                                 | 150                  | 250       | ps                | P                         |

| 160         | I/O Spike                                          | VL = 0 V, VTT = 2<br>VH = 0 V, VL = 0 V                                       |                      | 200       | mV p-p            | N                         |

| 170         | Rise, Fall Time, Active to Inhibit                 | VL = 0 V, VTT = 2 (20%/80%                                                    |                      | 1.2       | ns                | N                         |

| 171         | Rise, Fall Time, Inhibit<br>to Active              | of 1 V Output)  VH = 4 V, VL = 0 V, VTT = 2 (20%/80% of 1 V Output)           |                      | 0.6       | ns                | N                         |

|             | DVNIAMIC DEDECTMANICE VI                           | +                                                                             |                      |           |                   |                           |

| 180         | DYNAMIC PERFORMANCE, VI<br>Delay Time, VH to VTERM | Measured at 50%, VL = VH = 2 V,<br>  VTERM = 0 V, VTT = 0 V                   | 1.5                  | 1.9       | ns                | P                         |

| 181         | Delay Time, VL to VTERM                            | Measured at 50%, VL = VH = 0 V,<br>VTERM = 2 V, VTT = 0 V                     | 1.6                  | 1.9       | ns                | P                         |

| 182         | Delay Time, VTERM to VH                            | Measured at 50%, VL = VH = 2 V,<br>VTERM = 0 V, VTT = 0 V                     | 1.6                  | 2.0       | ns                | P                         |

| 183         | Delay Time, VTERM to VL                            | Measured at 50%, VL = VH = 0 V,<br>VTERM = 2 V, VTT = 0 V                     | 1.6                  | 2.0       | ns                | P                         |

| 190         | Overshoot and Preshoot                             | VH/VL, VTERM = (0 V, 2 V),<br>(0 V, 6 V)                                      | -6.0 + 50            | +6.0 + 50 | % of Step<br>+ mV | N                         |

| 191A        | VTERM Rise Time, VL to<br>VT, Normal Mode          | VL, VH = 0 V, VTERM = 2 V, 20%-80%                                            |                      | 1.0       | ns                | N                         |

| 191B        | VTERM Rise Time, VT to<br>VH, Normal Mode          | VL, VH = 2 V, VTERM = 0 V, 20%-80%                                            |                      | 0.6       | ns                | N                         |

| 192A        | VTERM Fall Time, VT to<br>VL, Normal Mode          | VL, VH = 0 V, VTERM = 2 V, 20%-80%                                            |                      | 0.6       | ns                | N                         |

| 192B        | VTERM Fall Time, VH to<br>VT, Normal Mode          | VL, VH = 2V, VTERM = 0 V, 20%–80%                                             |                      | 1.0       | ns                | N                         |

-4- REV. 0

# COMPARATOR<sup>1</sup>

| Spec<br>No. | Parameter                                     | Conditions                                                                     | Min   | Typ <sup>2</sup> | Max         | Unit                                  | Spec <sup>3</sup><br>Perf |

|-------------|-----------------------------------------------|--------------------------------------------------------------------------------|-------|------------------|-------------|---------------------------------------|---------------------------|

|             | DC INPUT CHARACTERISTICS                      |                                                                                |       |                  |             |                                       |                           |

| 200         | VCCO Range                                    |                                                                                | 2.0   |                  | 4.5         |                                       | N                         |

| 201         | Offset Voltage (Vos)                          | Common-Mode Voltage = 0 V                                                      | -25   |                  | +25         | mV                                    | P                         |

| 202         | Offset Voltage Drift                          | Common-Mode Voltage = 0 V                                                      |       | 50               |             | μV/°C                                 | N                         |

| 203         | HCOMP, LCOMP                                  | Over Linearity Range                                                           | -50   |                  | +50         | μA                                    | P                         |

|             | BIAS CURRENTS                                 |                                                                                |       |                  |             |                                       |                           |

| 206         | Voltage Range (V <sub>CM</sub> )              |                                                                                | -0.5  |                  | +6.5        | V                                     | P                         |

| 207         | Differential Voltage (V <sub>DIFF</sub> )     |                                                                                |       |                  | +7          | V                                     | P                         |

| 208         | Gain Error                                    | $V_{IN} = -0.5 \text{ V to } +6.5 \text{ V}$                                   | -0.25 |                  | 0.0         | %FSR                                  | N                         |

| 209         | Linearity Error                               | $V_{IN} = -0.5 \text{ V to } +6.5 \text{ V}$                                   | -2    |                  | +2          | mV                                    | N                         |

| 210         | Extended Range Operation                      | HCOMP, LCOMP = -1, output                                                      | -1.0  |                  |             | V                                     | P                         |

|             | DIOMETE OF MEDITIES                           | toggle V <sub>OUT</sub> from -0.9 V to -1.1 V                                  |       |                  |             |                                       |                           |

| 220         | DIGITAL OUTPUTS Logic "1" Voltage QX          | Q or Qb, 150 $\Omega$ to GND,                                                  | VCCO  | 1.05             | VCCO - 0.85 | $ _{\mathbf{V}}$                      | P                         |

| 220         | Logic 1 Voltage QA                            | $\Omega$ or Q0, 150 $\Omega$ to Qb                                             | VCCO. | -1.05            | VCCO - 0.83 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | F                         |

| 221         | Logic "0" Voltage QXb                         | Q or Qb, 150 $\Omega$ to GND,                                                  | VCCO  | 2.2              | VCCO - 1.5  | $ _{V}$                               | P                         |

| 221         | Logic 0 Voltage QAb                           | $150 \Omega$ from Q to Qb                                                      | VCCO  | -2.2             | VCCO - 1.5  | \ \ \                                 | 1                         |

| 222         | Logic Differential, QX-QXb                    | Q or Qb, 150 $\Omega$ to GND,                                                  | 0.65  | 0.9              | 1.15        | V                                     | P                         |

|             | Logic Differential, QII QIIO                  | $150 \Omega$ from Q to Qb                                                      | 0.03  | 0.7              | 1.13        | *                                     | 1                         |

| 225         | Slew Rate                                     | Q or Qb (20 – 80% of output,                                                   |       | 380              |             | ps                                    | N                         |

|             |                                               | 150 $\Omega$ from Q to Qb)                                                     |       |                  |             |                                       |                           |

|             | CHANNEL COMPARATOR SWIT                       | CCHING PERFORMANCE                                                             |       |                  |             |                                       |                           |

|             | PROPAGATION DELAY                             |                                                                                |       |                  |             |                                       |                           |

| 240         | Input to Output                               | $V_{IN} = 3 \text{ V p-p, } 2 \text{ V/ns}$                                    | 0.7   |                  | 1.1         | ns                                    | P                         |

| 241         | Propagation Delay Temp. Co.                   | $V_{IN} = 3 \text{ V p-p, } 2 \text{ V/ns}$                                    |       | 1.0              |             | ps/°C                                 | N                         |

|             | Prop Delay Change with                        |                                                                                |       |                  |             |                                       |                           |

| 250         | respect to:                                   | V = 0 V = 2 V                                                                  |       | 100              |             |                                       | \                         |

| 250<br>260  | Slew Rate: 1, 2, 3 V/ns<br>Amplitude: 500 mV, | $V_{IN} = 0 V \text{ to } 3 V$                                                 |       | 120              |             | ps                                    | N                         |

| 200         | 1.0 V, 3.0 V                                  | $V_{IN} = 1.0 \text{ V/ns}$                                                    |       | 100              |             | ps                                    | N                         |

| 270         | Equivalent Input Rise Time                    | $V_{IN} = 1.0 \text{ V/Hs}$<br>$V_{IN} = 0 \text{ V to 2 V}, < 80 \text{ ps},$ |       | 275              |             | ps<br>ps                              | N                         |

| 210         | Equivalent input Rise Time                    | 20%-80% Rise Time                                                              |       | 213              |             | Ps                                    | 1                         |

|             |                                               | Driver in VTERM = 0 V                                                          |       |                  |             |                                       |                           |

| 280         | Pulsewidth Linearity                          | $V_{IN} = 0 \text{ V to } 3 \text{ V}, 2 \text{ V/ns}, PW =$                   |       |                  | 50          | ps                                    | N                         |

|             | 1 also with Emourity                          | 3, 4, 5, 10 ns, Driver Hi-Z mode                                               |       |                  | 30          |                                       | 1                         |

| 281         | Settling Time                                 | Settling to $\pm 8 \text{ mV}$ , $V_{IN} = 0 \text{ V}$ to                     |       | 25               |             | ns                                    | N                         |

|             | S                                             | 3 V, Driver Hi-Z mode                                                          |       |                  |             |                                       |                           |

| 282         | Hysteresis                                    | -                                                                              |       | 6                |             | mV                                    | N                         |

| 290         | Comparator Propagation                        | $V_{IN} = 0 \text{ V to } 3 \text{ V}, 2 \text{ V/ns}$                         |       |                  | 125         | ps                                    | P                         |

|             | Delay Matching, HCOMP                         |                                                                                |       |                  |             |                                       |                           |

|             | to LCOMP                                      |                                                                                |       |                  |             |                                       |                           |

| _           | INPUT CHARACTERISTICS                         |                                                                                |       |                  |             |                                       |                           |

|             | INHL, INHLb                                   | See Driver Spec No. 1                                                          |       |                  |             |                                       |                           |

| 300         | Input Voltage                                 | VIOH = 1 V, VIOL = 1 V,                                                        | 0     |                  | 3.3         | V                                     | P                         |

| 201         | DHH DHHI B' C                                 | VCOM = 2 V, VDUT = 0 V                                                         | 250   |                  | . 250       |                                       | D                         |

| 301         | INHL, INHLb Bias Current                      | INHL, INHLb = 0 V, 3.3 V,<br>AC Tests 0.2 V and 0.8 V                          | -250  |                  | +250        | μΑ                                    | P                         |

| 302         | VIOH Current Program Range,                   | VDUT = 0.8 V, 6.5 V                                                            | 0     |                  | 4.0         | v                                     | $ _{\mathbf{P}}$          |

| JU4         | , 1011 Guitein Hogiain Nange,                 | 1 DOI = 0.0 Y, 0.3 Y                                                           | "     |                  | 1.0         | l *                                   | 1*                        |

REV. 0 -5-

# **SPECIFICATIONS** (continued)

# ACTIVE LOAD<sup>1</sup>

| Spec<br>No. | Parameter                                                                                        | Conditions                                                                                                                                                                | Min                              | Typ <sup>2</sup> | Max   | Unit              | Spec <sup>3</sup><br>Perf |

|-------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------|-------------------|---------------------------|

|             | BIAS CURRENT                                                                                     | VIOH = 0 V, 4 V                                                                                                                                                           |                                  |                  |       |                   |                           |

| 303         | VIOL Current Program Range,                                                                      |                                                                                                                                                                           |                                  |                  |       |                   |                           |

|             | IOL = 0  mA to  40  mA                                                                           | VDUT = -0.5 V, +5.2 V                                                                                                                                                     | 0                                | 0 4.0            |       | V                 | P                         |

| 304         | IOH, VIOL Input                                                                                  | VIOL = 0 V, 4 V and                                                                                                                                                       | VIOL = 0 V, 4 V  and $-300 +300$ |                  |       | μA                | P                         |

| 305         | IOXRTN Range                                                                                     | IOL = +40 mA, IOH = -40 mA,<br>VDUT = -0.5 V, +6.5 V                                                                                                                      |                                  | -0.5, +6         | 5.5   | V                 | N                         |

| 310         | VDUT Range                                                                                       | IOL = +40 mA, IOH = -40 mA,<br> VDUT - VCOM > 1.3 V                                                                                                                       | -0.5                             |                  | +6.5  | V                 | P                         |

| 311         | VDUT Range, IOH = 0 mA to -40 mA                                                                 | VDUT – VCOM > 1.3 V                                                                                                                                                       | 0.8                              |                  | 6.5   | V                 | P                         |

| 312         | VDUT Range, IOL =<br>0 mA to +40 mA                                                              | VCOM – VDUT > 1.3 V                                                                                                                                                       | -0.5                             |                  | +5.2  | V                 | P                         |

|             | OUTPUT CHARACTERISTICS                                                                           |                                                                                                                                                                           |                                  |                  |       |                   |                           |

| 320         | Accuracy Gain Error, Load Current, Normal Range Calculated at 1 mA and 40 mA points <sup>2</sup> | IOL, IOH = 25 $\mu$ A – 40 mA,<br>VCOM = 0 V, VDUT = $\pm$ 2 V and<br>IOL = 25 $\mu$ A to 40 mA, VCOM =<br>+6.5 V, VDUT = +5.2 V and<br>IOH = 25 $\mu$ A to 40 mA, VCOM = | -0.35                            |                  | +0.35 | %I <sub>SET</sub> | P                         |

| 321         | Load Offset                                                                                      | -0.5 V, VDUT = +0.8 V<br>Calculated from Intercept of 1 mA                                                                                                                | -300                             |                  | +300  | μА                | P                         |

| 322<br>323  | Load Nonlinearity Output Current Temperature                                                     | and 40 mA Points IOL, IOH from 25 μA to 40 mA Measured at IOH, IOL = 200 μA                                                                                               | -80                              | < ±3             | +80   | μΑ<br>μΑ/°C       | P<br>N                    |

| 324         | COEFFICIENT<br>IOH Extended Range                                                                | Driver Inhibited, IOH = 1 mA,<br>Change in IOH from VTT =<br>0 V to VTT = -1.0 V                                                                                          | 2                                |                  |       | %                 | P                         |

| -           | VCOM BUFFER                                                                                      |                                                                                                                                                                           |                                  |                  |       |                   | +                         |

| 330         | VCOM Buffer Offset Error                                                                         | IOL, $IOH = 40$ mA, $VCOM = 0$ V                                                                                                                                          | -50                              |                  | +50   | mV                | P                         |

| 331         | VCOM Buffer Bias Current                                                                         | VCOM = 0 V                                                                                                                                                                | -20                              |                  | +20   | μA                | P                         |

| 332         | VCOM Buffer Gain Error                                                                           | IOL, IOH = 40 mA, VCOM =                                                                                                                                                  | -4                               |                  | +4    | %                 | P                         |

| 333         | VCOM Buffer Linearity Error                                                                      | -0.5 V to +6.5 V<br>IOL, IOH = 40 mA, VCOMI =<br>-0.5 V to +6.5 V                                                                                                         | -10                              |                  | +10   | mV                | P                         |

|             | DYNAMIC PERFORMANCE                                                                              |                                                                                                                                                                           |                                  |                  |       |                   |                           |

|             | Propagation Delay                                                                                |                                                                                                                                                                           |                                  |                  |       |                   |                           |

| 340         | ± I <sub>MAX</sub> to INHIBIT                                                                    | VTT = +2  V, VCOM = +4/0  V,<br>IOL = +20  mA, IOH = -20  mA                                                                                                              | 1.0                              | 1.3              | 2.0   | ns                | P                         |

| 341         | INHIBIT to $\pm$ I <sub>MAX</sub>                                                                | VTT = +2  V, VCOM = +4/0  V,<br>IOL = +20  mA, IOH = -20  mA                                                                                                              | 1.2 1.8 2.4                      |                  | 2.4   | ns                | P                         |

| 342         | Propagation Delay Matching                                                                       | Matching = (Test 340 Value) – (Test 341 Value)                                                                                                                            | -1.0 +1.0                        |                  | ns    | P                 |                           |

| 350         | I/O Spike                                                                                        | VCOM = 0 V, IOL = +20 mA,<br>IOH = -20 mA                                                                                                                                 |                                  | 250              |       | mV                | N                         |

| 360         | Settling Time to 15 mV                                                                           | IOL = $+20$ mA, IOH = $-20$ mA,<br>50 $\Omega$ Load, to $\pm 15$ mV                                                                                                       |                                  | 50               |       | ns                | N                         |

| 361         | Settling Time to 4 mV                                                                            | IOL = $+20$ mA, IOH = $-20$ mA,<br>50 $\Omega$ Load, to $\pm 4$ mV                                                                                                        |                                  | 10               |       | μs                | N                         |

-6- REV. 0

### DYNAMIC CLAMP PART<sup>1</sup>

| Spec<br>No. | Parameter                                     | Conditions                                                                              | Min       | Typ <sup>2</sup> | Max  | Unit | Spec <sup>3</sup><br>Perf |

|-------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|-----------|------------------|------|------|---------------------------|

| 400         | Input Voltage VCH                             |                                                                                         | 2         |                  | 7.5  | V    | P                         |

| 401         | Input Voltage VCL                             |                                                                                         | -1.5      |                  | +4   | V    | P                         |

| 402         | Input Bias Current VCH/VCL                    | Over range spec #401, 402                                                               | -250      |                  | +250 | μA   | P                         |

| 410         | VCH, VCL Offset Error                         | $I_{TEST} = 1 \text{ mA}$                                                               | -250      |                  | +250 | mV   | P                         |

| 411         | VCH, VCL Gain Error                           | $I_{TEST} = 1 \text{ mA}$                                                               | 0.96      |                  | 1.01 | V/V  | P                         |

| 420         | Static Current Capability                     |                                                                                         | 50        |                  | 75   | mA   | N                         |

| 430         | Incremental Resistance                        | 11 mA to 21 mA                                                                          | 45        | 48               | 52   | Ω    | P                         |

| 440         | VCHP, VCLP Protection                         |                                                                                         | 0.52      |                  | 0.64 | V    | P                         |

|             | Diodes Vf @ 500 μ                             |                                                                                         |           |                  |      |      |                           |

| 441         | Protection Diodes Max Current                 | For information only                                                                    |           |                  | 2    | mA   | N                         |

|             | TOTAL FUNCTION POWER DO                       | WN                                                                                      |           |                  |      |      |                           |

| 500         | PWRD Input Voltage                            |                                                                                         | 0         |                  | 5    | V    | P                         |

| 501         | PWRD Bias Current                             | PWRD trip point 1.4 V ± 0.15 V                                                          | -250      |                  | +250 | μA   | P                         |

| 503         | Power-Down Supply Reduction                   | VIOH = 0 V, VIOL = 0 V                                                                  | 35        |                  | 60   | %    | P                         |

| 504         | Power-Down Output                             |                                                                                         |           |                  |      |      |                           |

|             | Leakage Current                               | VIOH = 0 V, VIOL = 0 V,<br>$V_{OUT} = -0.5 \text{ V to } +5.5 \text{ V}$                | -20       |                  | +20  | nA   | P                         |

| 505         | Power-Down Output                             |                                                                                         |           |                  |      |      |                           |

|             | Leakage Current                               | VIOH = 0 V, VIOL = 0 V,<br>V <sub>OUT</sub> = 5.5 V to 6.5 V                            | -500      |                  | +500 | nA   | P                         |

| 600         | Output Leakage Current,                       |                                                                                         |           |                  |      |      |                           |

|             | $V_{OUT} = -0.5 \text{ V to } +6.5 \text{ V}$ |                                                                                         | -1        |                  | +1   | μA   | P                         |

| 601         | Output Leakage Current,                       |                                                                                         |           |                  |      |      |                           |

|             | $V_{OUT} = 0 V \text{ to } 5 V$               |                                                                                         | -500      |                  | +500 | nA   | P                         |

| 602         | Output Leakage Current,                       |                                                                                         |           |                  |      |      |                           |

|             | $V_{OUT} = -1 V$                              |                                                                                         | <b>-5</b> |                  | +5   | μA   | P                         |

| 605         | Output Capacitance                            | Driver and Load INHIBITED                                                               |           | 9.2              |      | pF   | N                         |

| 606         | Output Capacitance Term                       | Driver VTERM = 0 V,<br>Load INHIBITED                                                   |           | 2.5              |      | pF   | N                         |

|             | POWER SUPPLIES                                |                                                                                         |           |                  |      |      |                           |

| 610         | Total Supply Range                            |                                                                                         |           | 15               |      | V    | N                         |

| 620         | Positive Supply, VCC                          |                                                                                         |           | +10.5            |      | V    | N                         |

| 630         | Negative Supply, VEE                          |                                                                                         |           | -4.5             |      | V    | N                         |

| 640         | Positive Supply Current, VCC                  | Driver = Inhibit, I <sub>LOAD</sub> program = 40 mA, Load = Active                      |           | 465              | 570  | mA   | P                         |

| 650         | Negative Supply Current, VEE                  | Driver = Inhibit, I <sub>LOAD</sub> program = 40 mA, Load = Active                      |           | 475              | 600  | mA   | P                         |

| 651         | Comparator Supply Current                     | -                                                                                       |           |                  |      |      |                           |

|             | Overhead, VCCO                                | Driver = Inhibit, I <sub>LOAD</sub> program = 40 mA, Load = Active (I <sub>VCCO</sub> - |           |                  | 45   | mA   | P                         |

| 660         | Total Power Dissipation                       | (comparator logic output currents)) Driver = Inhibit, I <sub>LOAD</sub> program =       |           | 7.2              | 7.9  | W    | P                         |

| 661         | Total Power Dissipation                       | 40 mA, Load = Active Driver = Inhibit, I <sub>LOAD</sub> program =                      |           | 5.2              | 5.9  | w    | P                         |

|             | <del>-</del>                                  | 0 mA                                                                                    |           | 2. <b>-</b>      | 2.7  | "    |                           |

| 700         | Temperature Sensor                            |                                                                                         |           |                  |      | 1    |                           |

|             | Gain Factor                                   | $R_{LOAD} = 10 \text{ k}\Omega, V_{SOURCE} = 10.5 \text{ V}$                            |           | 1                |      | μA/K | N                         |

NOTES

Specifications are subject to change without notice.

REV. 0 -7-

$<sup>^1</sup>$ All temperature coefficients are measured at  $T_J$  = 75°C–95°C. In test figures, voltmeter loading is 1 MΩ or greater, scope probe loading is 100 kΩ in parallel with 0.6 pF.  $^2$ Typical Values are not tested or guaranteed. Nominal values are generated from design or simulation analyses and/or limited bench evaluations and are not tested

<sup>&</sup>lt;sup>2</sup>Typical Values are not tested or guaranteed. Nominal values are generated from design or simulation analyses and/or limited bench evaluations and are not tested or guaranteed.

<sup>&</sup>lt;sup>3</sup>Spec Perf: N = Nominal, O = Operating Condition, T = Typical, P = Production, Max Min

<sup>&</sup>lt;sup>4</sup>VTERM Linearity over the following condition: VL - 6 V < VTERM < VH + 6 V

<sup>&</sup>lt;sup>5</sup>All ac input values are referred to the source end of transmission line input.

<sup>&</sup>lt;sup>6</sup>All ac tests are performed with Driver in VTERM mode except where noted.

<sup>&</sup>lt;sup>7</sup>Rise time is calculated SQRT((comp out rt)\*\*2–(comp in rt)\*\*2)

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>                                  |

|------------------------------------------------------------------------|

| POWER SUPPLY VOLTAGE                                                   |

| V <sub>CC</sub> to GND                                                 |

| V <sub>EE</sub> to GND7 V                                              |

| $V_{CC}$ to $V_{EE}$                                                   |

| VCCO to GND                                                            |

| PWRGND, DRGND, GND_ROT, or HQGND ±0.4 V                                |

| OUTPUTS                                                                |

| V <sub>OUT</sub> Short Circuit Duration Indefinite <sup>2</sup>        |

| V <sub>OUT</sub> , Inhibit Mode +8.5 V, -2 V                           |

| $V_{OUT}$ , Inhibit Mode $VL - 5.5 V < V_{OUT} < VH + 5.5 V$           |

| VHDCPL Do Not Connect Except for Cap to $V_{CC}$                       |

| VLDCPL Do Not Connect Except for Cap to $V_{EE}$                       |

| QH, QHb, QL, QLB Maximum I <sub>OUT</sub> :                            |

|                                                                        |

| Continuous 50 mA                                                       |

| Continuous         50 mA           Surge         100 mA                |

|                                                                        |

| Surge                                                                  |

| Surge100 mATHERM11 V, 0 VDriver output capacitance, maximum10 pFINPUTS |

| Surge100 mATHERM11 V, 0 VDriver output capacitance, maximum10 pF       |

| Surge100 mATHERM11 V, 0 VDriver output capacitance, maximum10 pFINPUTS |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                  |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                  |

| INHL to INHLb                                                                        |

|--------------------------------------------------------------------------------------|

| VH, VL, VTERM to GND (Rseries $< 500 \Omega$ ) . $+7.5 \text{ V}$ , $-1.1 \text{ V}$ |

| VH to VL                                                                             |

| $(VH-VTERM)$ and $(VTERM-VL)$ $\pm 8~V$                                              |

| Reflection Clamps High/Low +8.5 V, -2 V                                              |

| Protection Clamp Breakdown Voltage 12 V                                              |

| Protection Clamps Current ±5 mA                                                      |

| $V_{OUT}$ to HCOMP or LCOMP                                                          |

| ENVIRONMENTAL                                                                        |

| Operating Temperature (Junction)                                                     |

| Storage Temperature65°C to +150°C                                                    |

| Lead Temperature (Soldering, 10 sec) <sup>3</sup> 260°C                              |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Absolute maximum limits apply individually, not in combination. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Output short circuit protection is guaranteed as long as proper heat sinking is employed to ensure compliance with the operating temperature limits.

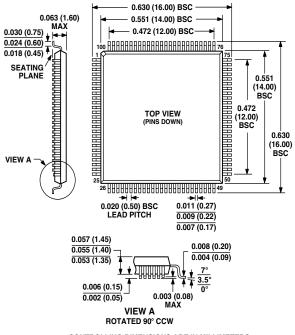

$^3$ To ensure lead coplanarity ( $\pm 0.002$  inches) and solderability, handling with bare hands should be avoided and the device should be stored in environments at 24 °C  $\pm 5$ °C (75°F  $\pm 10$ °F) with relative humidity not to exceed 65%.

#### **ORDERING GUIDE**

| Model      | Temperature | Package                                         | Package |

|------------|-------------|-------------------------------------------------|---------|

|            | Range       | Description                                     | Option  |

| AD53522JSQ | 0°C to 70°C | 100-Lead LQFP-EDQUAD<br>with Integral Heat Slug | SQ-100  |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD53522 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Table I. Driver Truth Table

| DATA | DATAb | IOD | IODb | RLD | RLDb | Output<br>State |

|------|-------|-----|------|-----|------|-----------------|

| 0    | 1     | 1   | 0    | X   | X    | VL              |

| 1    | 0     | 1   | 0    | X   | X    | VH              |

| X    | X     | 0   | 1    | 0   | 1    | INH and         |

|      |       |     |      |     |      | CLAMP           |

| X    | X     | 0   | 1    | 1   | 0    | VTERM           |

Table II. Comparator Truth Table

|                  |         | Output States |     |    |     |  |

|------------------|---------|---------------|-----|----|-----|--|

| V <sub>OUT</sub> |         | QH            | QHb | QL | QLb |  |

| > HCOMP          | > LCOMP | 1             | 0   | 1  | 0   |  |

| > HCOMP          | < LCOMP | 1             | 0   | 0  | 1   |  |

| < HCOMP          | > LCOMP | 0             | 1   | 1  | 0   |  |

| < HCOMP          | < LCOMP | 0             | 1   | 0  | 1   |  |

Table III. Active Load Truth Table

|                                                                                                                                  |      |       | Output States (including diode bridge) |                                 |                      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------|---------------------------------|----------------------|--|--|--|

| <b>VDUT</b>                                                                                                                      | INHL | INHLb | ЮН                                     | IOL                             | I(V <sub>OUT</sub> ) |  |  |  |

| <vcom< td=""><td></td><td>1</td><td><math>V(IOHC) \times +10 \text{ mA}</math></td><td>V(IOLC) × -10 mA</td><td>IOL</td></vcom<> |      | 1     | $V(IOHC) \times +10 \text{ mA}$        | V(IOLC) × -10 mA                | IOL                  |  |  |  |

| >VCOM                                                                                                                            | 0    | 1     | $V(IOHC) \times +10 \text{ mA}$        | $V(IOLC) \times -10 \text{ mA}$ | IOH                  |  |  |  |

| X                                                                                                                                | 1    | 0     | 0                                      | 0                               | 0                    |  |  |  |

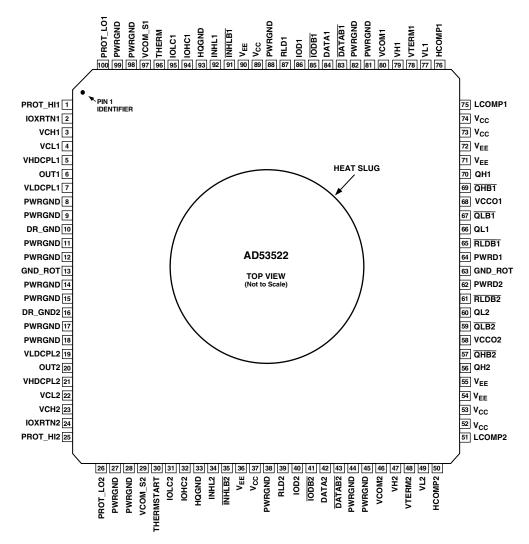

#### PIN CONFIGURATION

NOTE DIE IS MOUNTED TO THE BACK OF THE HEAT SLUG. THE PACKAGE IS MOUNTED TO THE BOARD, HEAT SLUG UP.

### PIN FUNCTION DESCRIPTIONS

| Pin Number | Mnemonic | Description                                                                                                                                              |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PROT_HI1 | Channel 1, output voltage sensing diode                                                                                                                  |

| 2          | IOXRTN1  | Current return path for the active load for channel 1. Typically connected to a power ground.                                                            |

| 3          | VCH1     | Analog input voltage that sets the reflection clamp high level of channel 1                                                                              |

| 4          | VCL1     | Analog input voltage that sets the reflection clamp low level of channel 1                                                                               |

| 5          | VHDCPL1  | Internal supply decoupling for the driver output stage of channel 1. This pin needs to be connected to $V_{\rm CC}$ through a 39 nF (minimum) capacitor. |

| 6          | OUT1     | Input/output for the driver, window comparator, reflection clamp, and the active load of channel 1                                                       |

| 7          | VLDCPL1  | Internal supply decoupling for the driver output stage of channel 1. This pin needs to be connected to $V_{\rm EE}$ through a 39 nF (minimum) capacitor. |

| 8          | PWRGND   | Power ground                                                                                                                                             |

| 9          | PWRGND   | Power ground                                                                                                                                             |

| 10         | DR_GND   | Analog ground                                                                                                                                            |

REV. 0 –9–

| Pin Number | Mnemonic        | Description                                                                                                                                                                                       |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | PWRGND          | Power ground                                                                                                                                                                                      |

| 12         | PWRGND          | Power ground                                                                                                                                                                                      |

| 13         | GND_ROT         | Analog ground                                                                                                                                                                                     |

| 14         | PWRGND          | Power ground                                                                                                                                                                                      |

| 15         | PWRGND          | Power ground                                                                                                                                                                                      |

| 16         | DR_GND          | Analog ground                                                                                                                                                                                     |

| 17         | PWRGND          | Power ground                                                                                                                                                                                      |

| 18         | PWRGND          | Power ground                                                                                                                                                                                      |

| 19         | VLDCPL2         | Internal supply decoupling for the driver output stage of channel 2. This pin needs to be connected to $V_{EE}$ through a 39 nF (minimum) capacitor.                                              |

| 20         | OUT2            | Input/output for the driver, window comparator, reflection clamp, and the active load of channel 2                                                                                                |

| 21         | VHDCPL2         | Internal supply decoupling for the driver output stage of channel 2. This pin needs to be connected to $V_{CC}$ through a 39 nF (minimum) capacitor.                                              |

| 22         | VCL2            | Analog input voltage that sets the reflection clamp high level of channel 2                                                                                                                       |

| 23         | VCH2            | Analog input voltage that sets the reflection clamp high level of channel 2                                                                                                                       |

| 24         | IOXRTN2         | Current return path for the active load for channel 2. Typically connected to a power ground.                                                                                                     |

| 25         | PROT_HI2        | Channel 2, output voltage sensing diode                                                                                                                                                           |

| 26         | PROT_LO2        | Channel 2, output voltage sensing diode                                                                                                                                                           |

| 27         | PWRGND          | Power ground                                                                                                                                                                                      |

| 28         | PWRGND          | Power ground                                                                                                                                                                                      |

| 29         | VCOM_S2         | Analog output voltage that represents a buffered VCOM1 input                                                                                                                                      |

| 30         | THERMSTART      | Temperature sensor startup pin. Normally not connected                                                                                                                                            |

| 31         | IOLC2           | Analog input voltage that programs the channel 2 active load source current                                                                                                                       |

| 32         | IOHC2           | Analog input voltage that programs the channel 2 active load sink current                                                                                                                         |

| 33         | HQGND           | Clean analog ground for the active load for channel 2                                                                                                                                             |

| 34         | INHL2           | One of two complementary inputs that control the inhibit mode for the active load bridge of channel 2                                                                                             |

| 35         | ĪNHLB2          | One of two complementary inputs that control the inhibit mode for the active load bridge of channel 2                                                                                             |

| 36         | $V_{EE}$        | Negative supply terminal                                                                                                                                                                          |

| 37         | V <sub>CC</sub> | Positive supply terminal                                                                                                                                                                          |