# AN4421 Application note

Migrating from M24LR to M24SR series

## Introduction

Both M24LRxx and M24SRxx dynamic tags can be accessed through the I<sup>2</sup>C-bus. This application note aims at helping to design an application able to interface through the I<sup>2</sup>C-bus either the M24LRxx<sup>(a)</sup> or the M24SRxx<sup>(b)</sup>. Some references are also made when accessing the standard M24xxx (EEPROM accessed through the I<sup>2</sup>C-bus).

a. Also accessible through RF (ISO15693 standard)

b. Also accessible through RF (ISO14443 standard)

## Contents

| 1 | Hardv | ware and AC/DC considerations                                                                                                               |  |  |  |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   | 1.1   | Hardware considerations 5                                                                                                                   |  |  |  |

|   | 1.2   | AC/DC characteristics                                                                                                                       |  |  |  |

|   |       | 1.2.1 AC/DC differences                                                                                                                     |  |  |  |

|   |       | 1.2.2 Pull resistor on SDA line                                                                                                             |  |  |  |

| 2 | Softw | are considerations                                                                                                                          |  |  |  |

|   | 2.1   | I <sup>2</sup> C-bus and standard EEPROM memories (M24xxx)                                                                                  |  |  |  |

|   | 2.2   | Differences when accessing a standard EEPROM (M24xxx) or<br>an M24LRxx dynamic tag (ISO15693) through the I <sup>2</sup> C-bus              |  |  |  |

|   | 2.3   | Differences when accessing an ISO15693 dynamic tag (M24LRxx) or<br>an ISO/IEC 1443 dynamic tag (M24SRxx) through the I <sup>2</sup> C-bus 9 |  |  |  |

| 3 | Revis | ion history                                                                                                                                 |  |  |  |

# List of tables

| Table 1. | Pinout differences between M24LRxx and M24SRxx devices | 5  |

|----------|--------------------------------------------------------|----|

| Table 2. | AC/DC differences between M24LRxx and M24SRxx devices  | 5  |

| Table 3. | Device select byte (first byte)                        | 7  |

| Table 4. | Standard EEPROM Device Select byte                     | 8  |

| Table 5. | M24LRxx Device Select byte                             | 8  |

| Table 6. | Document revision history1                             | 10 |

# List of figures

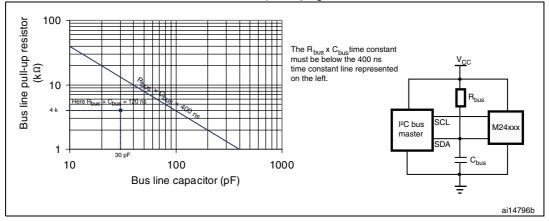

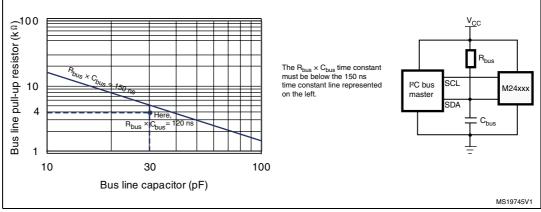

| Figure 1.              | Maximum Rbus value versus bus parasitic capacitance (Cbus) for an I2C bus at maximum frequency fC = 400 kHz      | 6 |

|------------------------|------------------------------------------------------------------------------------------------------------------|---|

| Figure 2.              | Maximum Rbus value versus bus parasitic capacitance (Cbus) for an I2C bus at maximum frequency fC = 1 MHz        | 6 |

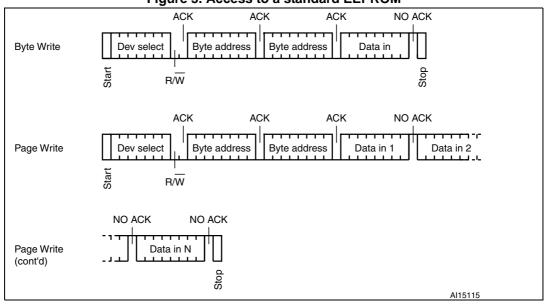

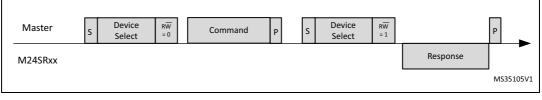

| Figure 3.<br>Figure 4. | Access to a standard EEPROM<br>Command+response sequence between the I <sup>2</sup> C-bus Master and the M24SRxx | 8 |

## **1** Hardware and AC/DC considerations

### 1.1 Hardware considerations

Both M24LRxx and M24SRxx devices are offered in an 8-pin package. The hardware differences between the two devices are detailed in *Table 1*.

|      | M24LRxx | M24SRxx    | Comments                                                                           |  |  |  |

|------|---------|------------|------------------------------------------------------------------------------------|--|--|--|

| Pin1 | E0      | RF disable | E0 input functionality is different from the RF disable input functionality        |  |  |  |

| Pin2 | AC0     | AC0        | Antenna coil                                                                       |  |  |  |

| Pin3 | AC1     | AC1        | Antenna coil                                                                       |  |  |  |

| Pin4 | Vss     | Vss        | Ground                                                                             |  |  |  |

| Pin5 | SDA     | SDA        | Serial Data                                                                        |  |  |  |

| Pin6 | SCL     | SCL        | Serial Clock                                                                       |  |  |  |

| Pin7 | E1      | GPO        | E1 input functionality is different from the General Purpose Output functionality. |  |  |  |

| Pin8 | Vcc     | Vcc        | Supply voltage                                                                     |  |  |  |

Table 1. Pinout differences between M24LRxx and M24SRxx devices

Although pin1 and pin7 differ between the M24SRxx and the M24LRxx, the I<sup>2</sup>C specific (and RF specific) inputs are identical for the M24SRxx and M24LRxx. Both M24LRxx and M24SRxx can therefore be accessed through the I<sup>2</sup>C-bus, on the same pins, SDA and SCL (pin5 and pin6). The only pin to connect differently is pin7 (input for the M24LRxx and output for the M24SRxx).

## **1.2 AC/DC** characteristics

### 1.2.1 AC/DC differences

*Table 2* summarizes the AC/DC differences to consider when designing an application moving from M24LRxx to M24SRxx (or reverse move).

|                               | M24LRxx                      | M24SRxx       | Comments                                           |  |  |  |

|-------------------------------|------------------------------|---------------|----------------------------------------------------|--|--|--|

| Vcc supply voltage            | 1.8 V / 5.5 V                | 2.7 V / 5.5 V |                                                    |  |  |  |

| Operating temperature range   | -40°C                        | / 85°C        |                                                    |  |  |  |

| Maximum clock frequency       | 400 kHz                      | 1 MHz         | See Section 1.2.2                                  |  |  |  |

| Supply current during a Write | 700 µA                       | 550 µA        | Worst case value, at max. SCL                      |  |  |  |

| Supply current during a Read  | 500 µA                       |               | frequency, no RF signal on<br>AC0/AC1, Vcc = 5.5 V |  |  |  |

| Write cycle (byte or page)    | te cycle (byte or page) 5 ms |               |                                                    |  |  |  |

Table 2. AC/DC differences between M24LRxx and M24SRxx devices

AN4421

#### 1.2.2 Pull resistor on SDA line

The I<sup>2</sup>C-bus specification defines the SDA output as an open drain so that, if two devices are in conflict while outputting a "1" and a "0" at the same time, this conflict cannot induce critical current peaks.

The "0" level is driven by the open drain output, while the "1" level is sourced with an external pull up resistor  $R_{bus}$ .

This R<sub>bus</sub> resistor value has to be:

- High enough so that the current flowing through R<sub>bus</sub> and SDA remains lower than the specified I<sub>ol</sub> value (a few mA)

- Reasonably low so that the cut-off frequency<sup>(a)</sup> defined with the SDA line parasitic capacitor C<sub>bus</sub> is higher than the maximum SCL clock frequency.

Depending on the application parasitic capacitor value  $R_{bus}$ ,  $C_{bus}$  can be defined as explained in *Figure 1* curves.

#### Figure 1. Maximum $R_{bus}$ value versus bus parasitic capacitance ( $C_{bus}$ ) for an I<sup>2</sup>C bus at maximum frequency $f_{C}$ = 400 kHz

Figure 2. Maximum  $R_{bus}$  value versus bus parasitic capacitance ( $C_{bus}$ ) for an I<sup>2</sup>C bus at maximum frequency  $f_{C} = 1$  MHz

a. The time constant =  $R_{bus} * C_{bus}$  defines the cut-off frequency:  $f_{cut-off} = \frac{1}{2} * PI * R_{bus} * C_{bus}$

DocID025682 Rev 1

47/

## 2 Software considerations

## 2.1 I<sup>2</sup>C-bus and standard EEPROM memories (M24xxx)

The I<sup>2</sup>C-bus specification defines a data transfer as a string of bytes inside which the first byte handles one RW bit defining the transfer direction: from Master to Slave or from Slave to Master.

| Device type identifier <sup>(1)</sup> |    |    |    | Chip | enable add | ress | RW |

|---------------------------------------|----|----|----|------|------------|------|----|

| b7                                    | b6 | b5 | b4 | b3   | b2         | b1   | b0 |

| 1                                     | 0  | 1  | 0  | E2   | E1         | E0   | RW |

Table 3. Device select byte (first byte)

1. The most significant bit, b7, is sent first.

M24xxx is always a slave device. To start a communication between the bus master and the slave device, the bus master must first initiate a Start condition. Following this, the bus master sends the Device select byte. The Device select byte consists of a 4-bit device type identifier and up to 3 Chip enable address bits. A Device type identifier handling any value other than 1010b (to select the memory) is not acknowledged by the memory device.

When the device select code is received, the memory device only responds if the Chip enable address is the same as the value decoded on the Ei inputs.

The 8th bit is the Read/Write bit (RW). This bit is set to 1 for Read (from Slave) and 0 for Write (to Slave) operations.

### 2.2 Differences when accessing a standard EEPROM (M24xxx) or an M24LRxx dynamic tag (ISO15693) through the I<sup>2</sup>C-bus

The standard EEPROMs are accessed, after a Start condition, with a sequence composed of the Device Select byte (where the RW bit defines the data transfer direction) followed by two address bytes and the data bytes. This sequence is ended by the bus Master sending a Stop condition, as in the Write sequence example shown in *Figure 3*.

Figure 3. Access to a standard EEPROM

The M24LRxx dynamic tags are accessed with the same Read and Write sequences as the sequences used for the standard EEPROM M24xxx, that is a sequence initiated with a Start condition and composed of the Device Select byte followed by the address bytes and the data bytes. This sequence is ended by the bus Master sending a Stop condition, as shown in *Figure 3*.

The difference between a standard EEPROM M24xxx and the M24LRxx comes from the Device Select byte content:

• The standard EEPROM Device Select byte is defined in Table 4.

#### Table 4. Standard EEPROM Device Select byte

|    | Device type | identifier <sup>(1)</sup> |    | Chip | enable addro | ess <sup>(2)</sup> | RW |

|----|-------------|---------------------------|----|------|--------------|--------------------|----|

| b7 | b6          | b5                        | b4 | b3   | b2           | b1                 | b0 |

| 1  | 0           | 1                         | 0  | E2   | E1           | E0                 | RW |

1. The most significant bit, b7, is sent first.

2. E0 bit and E1 bit are compared against the respective values read from external pins E0, E1 of the memory device.

• The M24LRxx Device Select byte is defined in Table 5.

| Table 5. | M24L | Rxx | Device | Select | b١ | /te |

|----------|------|-----|--------|--------|----|-----|

|          |      |     |        |        |    |     |

|    | Device type | identifier <sup>(1)</sup> |    | Chip              | enable addr | ess <sup>(2)</sup> | RW |

|----|-------------|---------------------------|----|-------------------|-------------|--------------------|----|

| b7 | b6          | b5                        | b4 | b3                | b2          | b1                 | b0 |

| 1  | 0           | 1                         | 0  | E2 <sup>(3)</sup> | E1          | E0                 | RW |

1. The most significant bit, b7, is sent first.

2. E0 bit and E1 bit are compared against the respective values read from external pins E0, E1 of the memory device.

3. E2 is not connected to any external pin, see M24LRxx for details.

DocID025682 Rev 1

The reader can see that bit E2 makes the difference between the two products; this has to be taken into account when developing the software routine accessing either a standard EEPROM or an M24LRxx dynamic tag.

### 2.3 Differences when accessing an ISO15693 dynamic tag (M24LRxx) or an ISO/IEC 1443 dynamic tag (M24SRxx) through the I<sup>2</sup>C-bus

The M24SRxx dynamic tags are accessed through the I<sup>2</sup>C-bus protocol where each byte is acknowledged by the device receiving the transmitted byte, but the sequence content is different from the M24LRxx sequence.

For the M24SRxx, the I<sup>2</sup>C communication is built on a system of command and reply exchange:

- 1. The I<sup>2</sup>C-bus Master starts the communication by sending a request, that is a Device Select byte with the RW bit set to 0 followed by the command field.

- 2. Once a valid request is received by the M24SRxx, it prepares its answer.

- 3. Then the I<sup>2</sup>C-bus Master sends a response request, that is a Device Select byte with the RW bit set to 1, followed by the data received from the M24SRxx.

*Figure 4* shows a simplified overview of the (command+response) sequence between the I<sup>2</sup>C-bus Master and the M24SRxx.

# Figure 4. Command+response sequence between the I<sup>2</sup>C-bus Master and the M24SRxx

<sup>1.</sup> S is the I<sup>2</sup>C Start condition.

- 2.  $R\overline{W}$  is the 8th bit of Device Select.

- 3. P is the I<sup>2</sup>C Stop condition.

- Note: The M24SRxx command response details are offered in the AN4433 (Storing data into the NDEF memory of M24SR).

## 3 Revision history

| Table 6. | Document | revision | history |

|----------|----------|----------|---------|

|----------|----------|----------|---------|

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 17-Mar-2014 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

> ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID025682 Rev 1