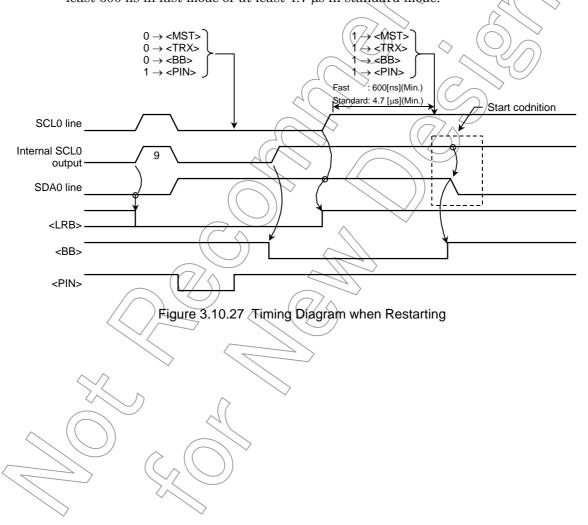

## **TOSHIBA**

# TLCS-900/H1 Series

TMP92CD54IFG

Tentative

## **TOSHIBA CORPORATION**

Semiconductor Company

## Preface

#### CMOS 32-bit Micro-controller

#### TMP92CD54IFG

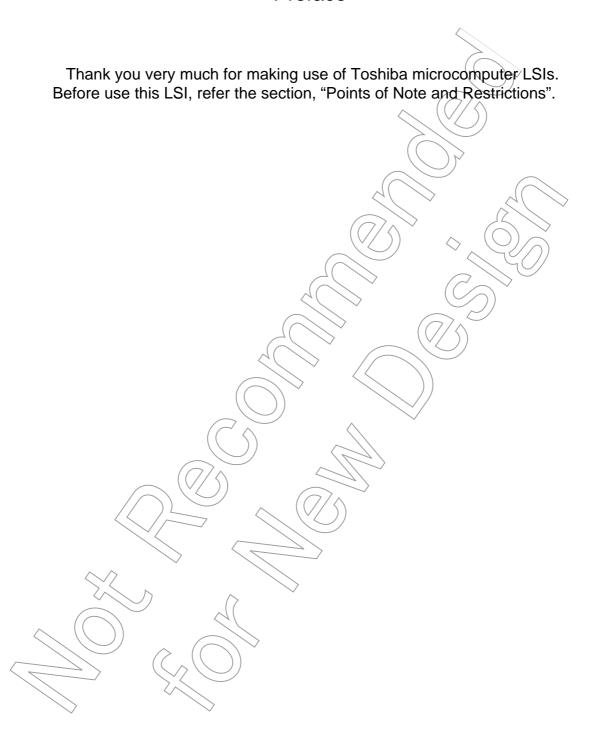

#### 1. Outline and Device Characteristics

The TMP92CD54I is a high-performance 32-bit microcontroller incorporating a Toshiba-proprietary CPU, the TLCS-900/H1 core. The TMP92CD54I is developed for various automotive equipments which require high-speed data processing.

Housed in a 100-pin mini-flat package, the TMP92CD54I is best suited for high-density implementation of user systems.

The characteristics of the TMP92CD54I are listed below:

(1) Toshiba-proprietary high-speed 32-bit CPU (TLCS-900/H1 CPU)

Fully-compatible with the instruction codes of the TLCS-900, TLCS-900/L, ELCS-900/L1,

TLCS-900/H and TLCS-900/H2

16 Mbytes of linear address space

General-purpose registers and register banks

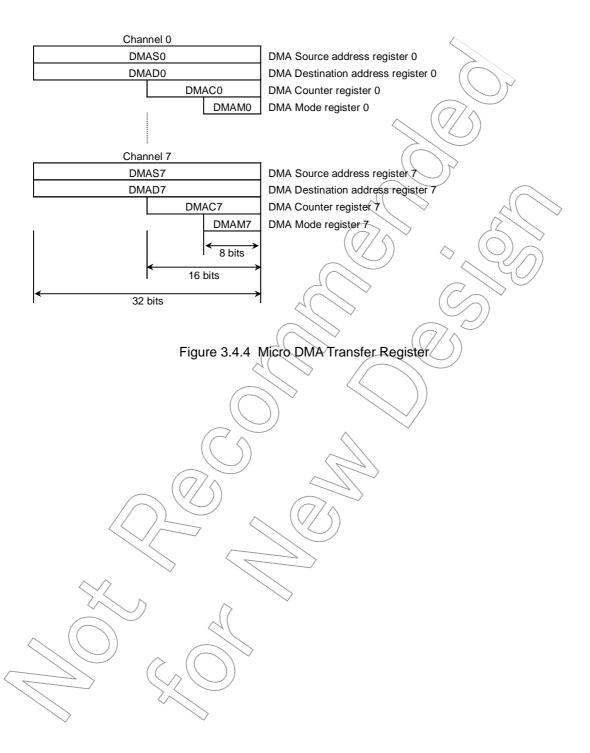

Micro DMA: 8 channels (250 ns/4 bytes at fc = 20 MHz)

Minimum instruction execution time: 50 ns (at fc = 20 MHz)

Internal data bus: 32-bit wide

(2) Internal memory

Internal RAM : 32K-byte (32 bit/one clock access time, can be used for instructions.

Internal ROM : 512K-byte Mask ROM

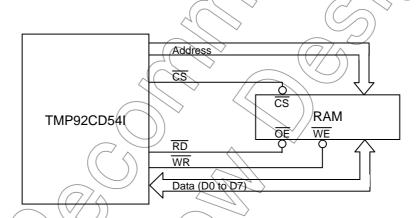

(3) External memory expansion

Expandable up to 16-Mbyte (for code and data)

External data bus: 8-bit wide (The upper address bus is not available when the built-in

I/Os are selected.)

(4) Memory controller (MEMC)

Chip select output: 1 channel

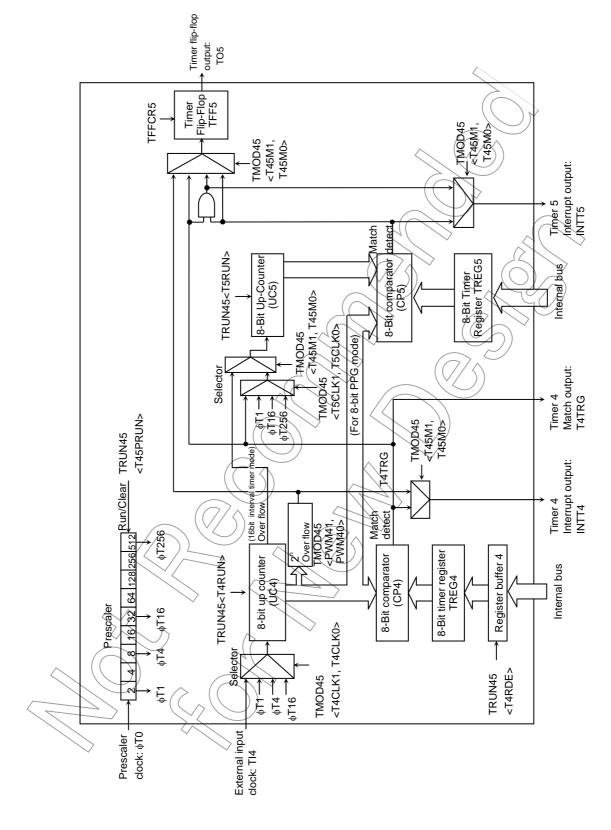

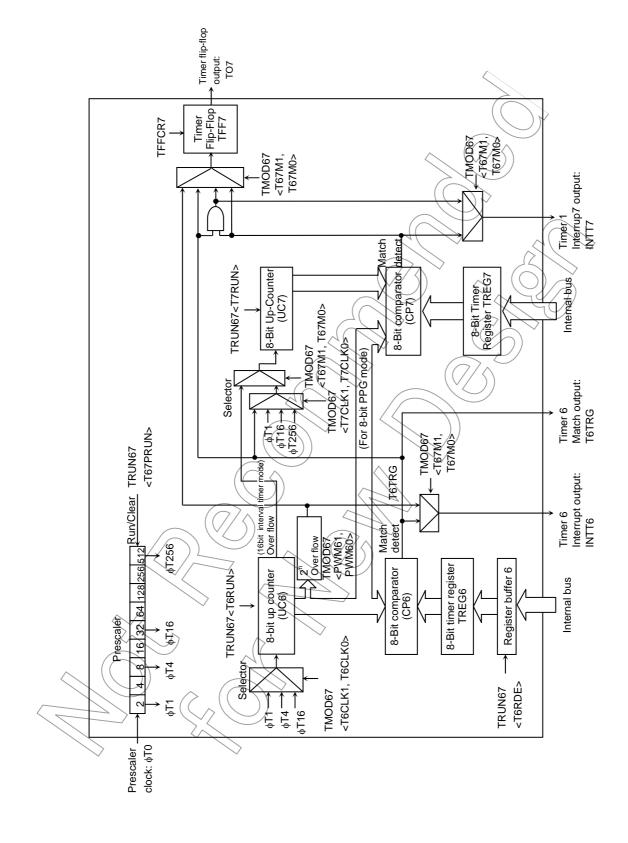

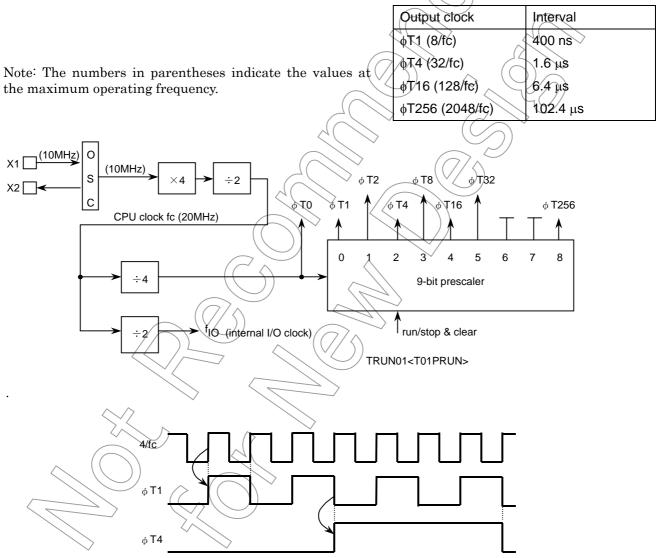

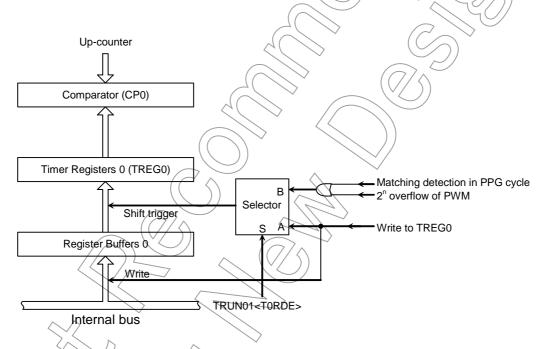

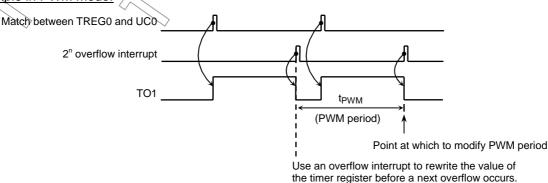

(5) 8-bit timer: 8 channels

8-bit interval timer mode (8 channels)

16-bit interval timer mode (4 channels)

8-bit programmable pulse generation (PRG) output mode (4 channels)

8-bit pulse width modulation (PWM) output mode (4 channels)

(6) 16-bit timer 2 channels

16-bit interval timer mode (2 channels)

16-bit event counter mode (2 channels)

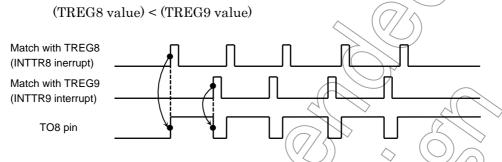

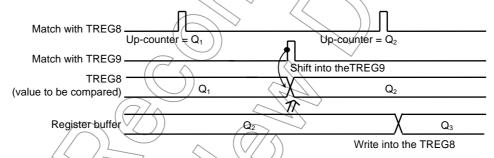

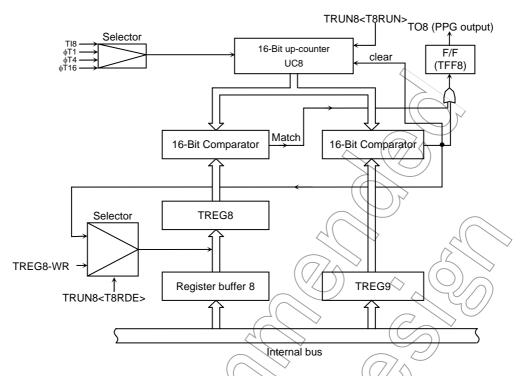

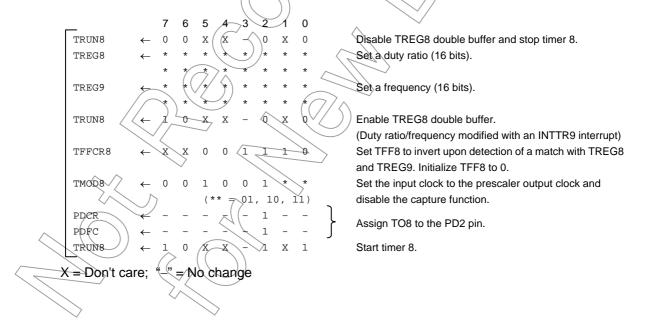

16-bit programmable pulse generation (PPG) output mode (2 channels)

Frequency measurement mode

Pulse width measurement mode

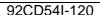

Time difference measurement mode

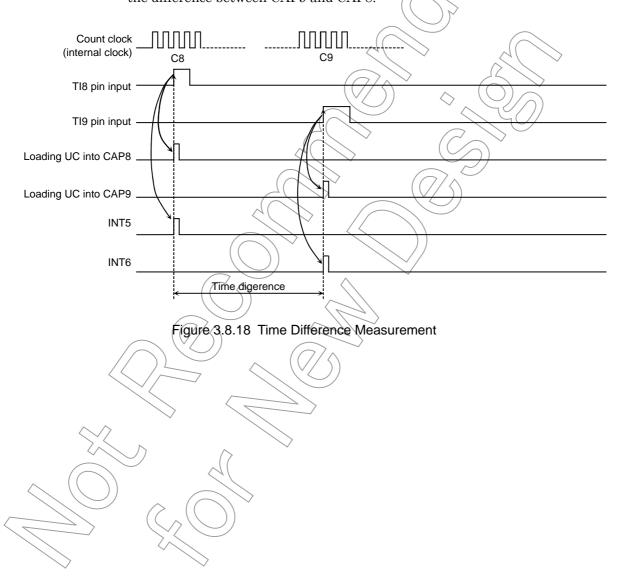

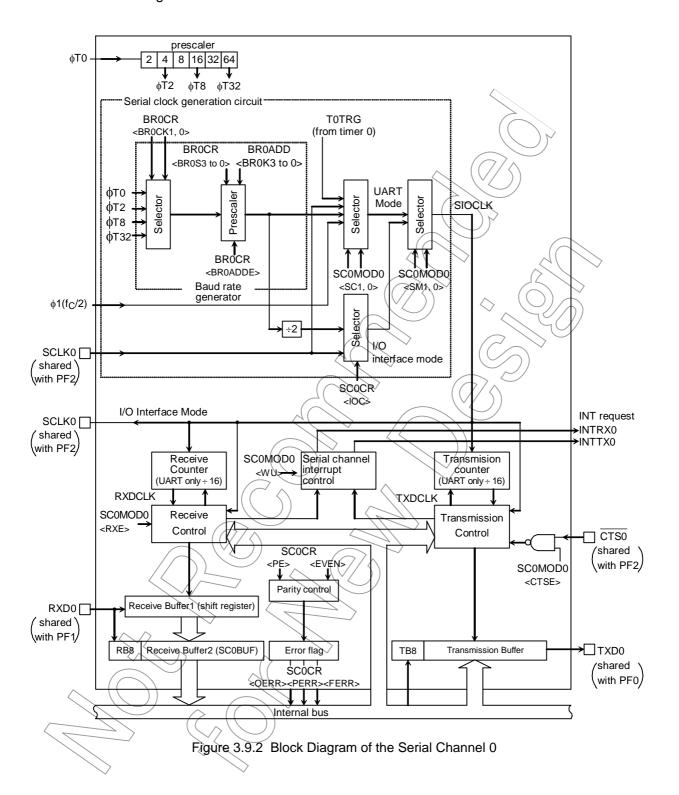

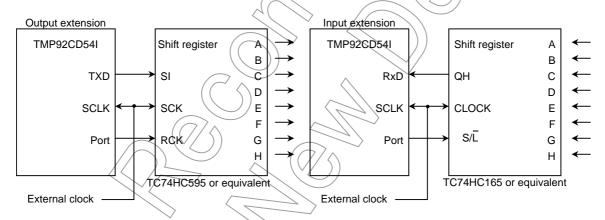

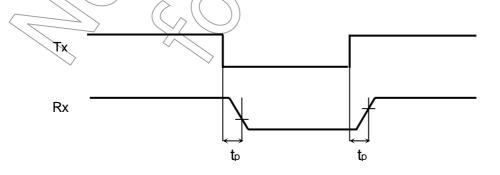

(7) Serial interface (SIO): 2 channels

I/O interface mode

Universal asynchronous receiver transmitter (UART) mode

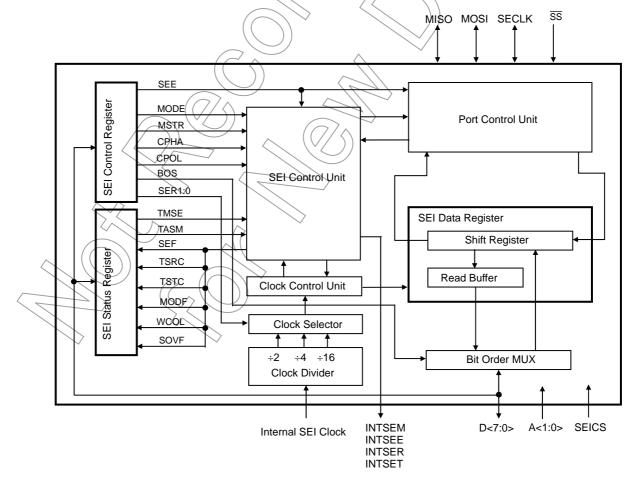

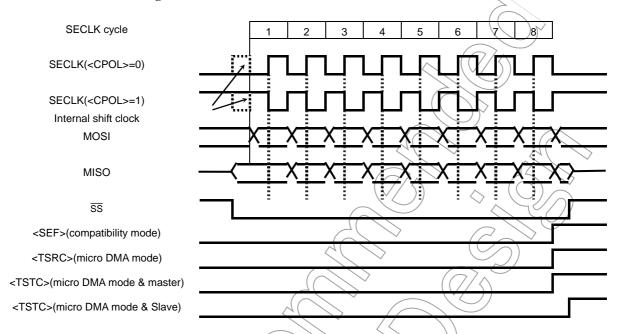

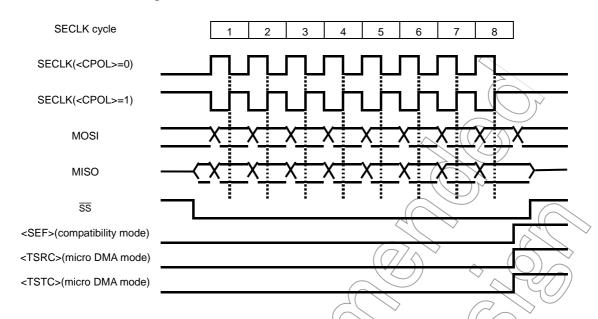

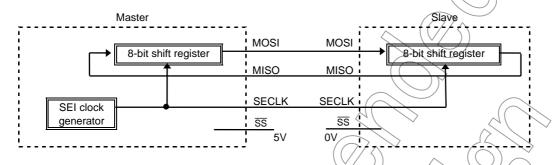

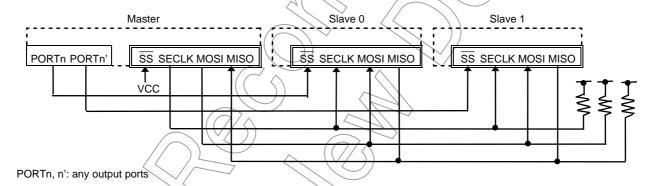

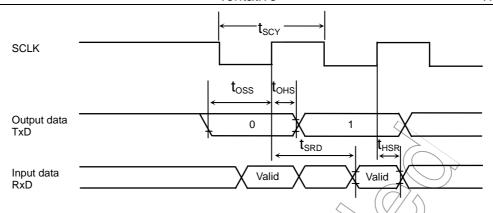

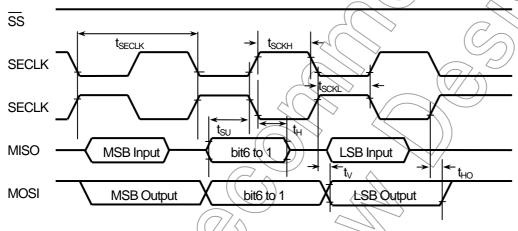

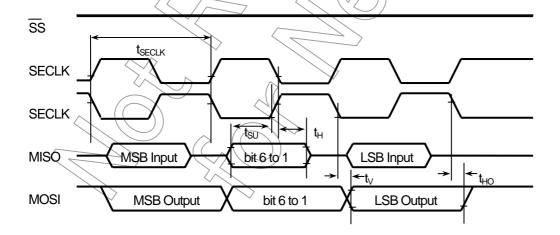

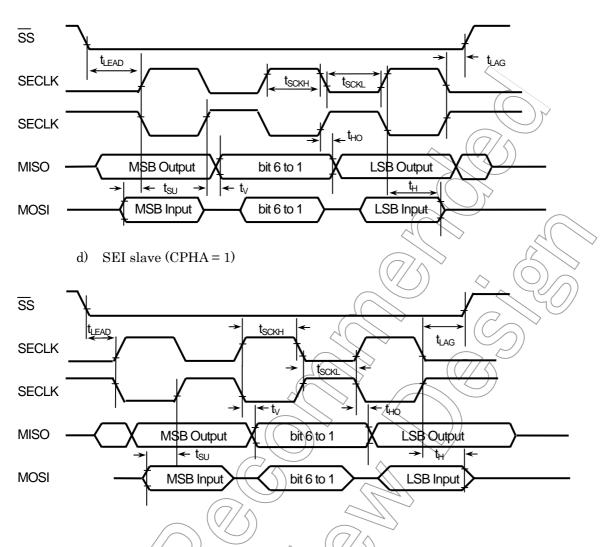

(8) Serial expansion interface (SEI): 1 channel

Baud rate 4M / 2M / 500Kbps at fc = 20MHz.

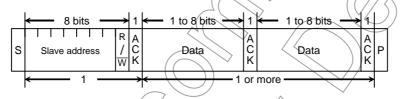

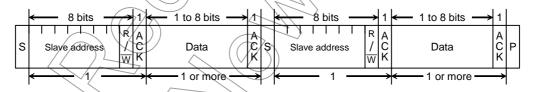

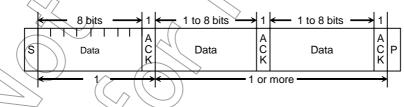

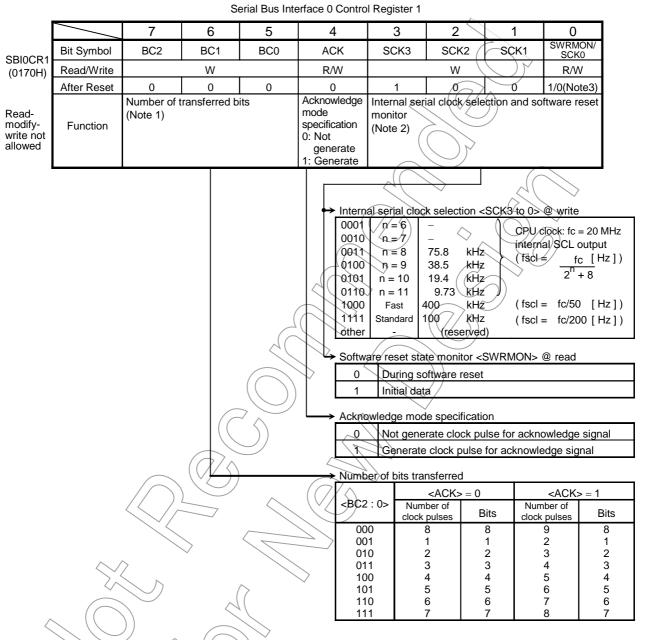

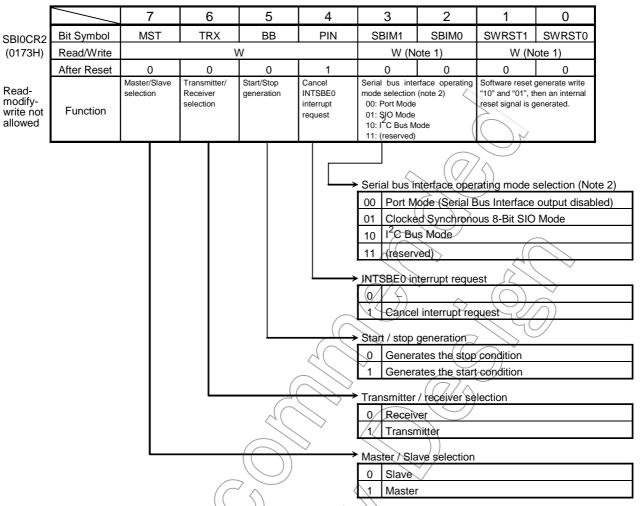

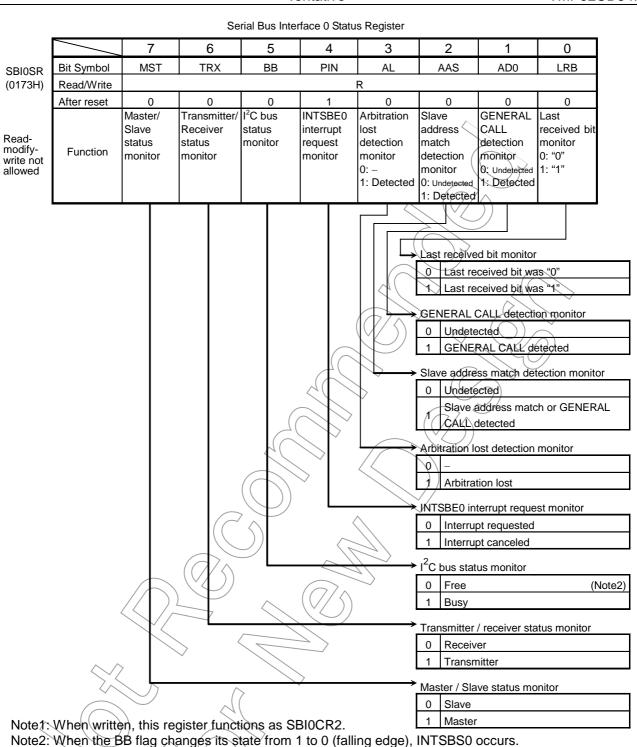

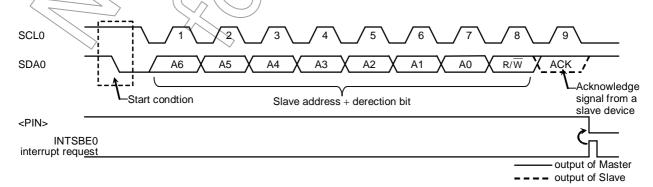

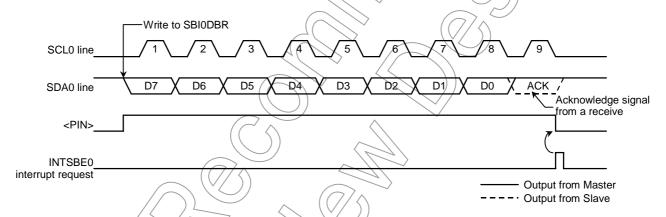

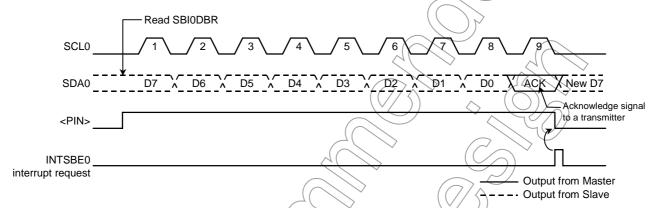

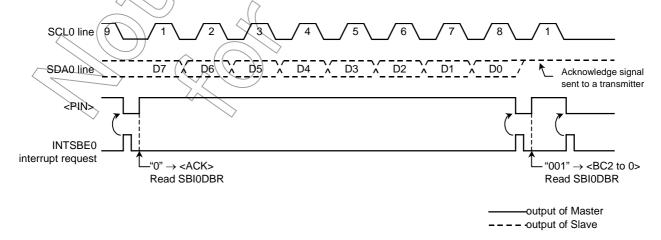

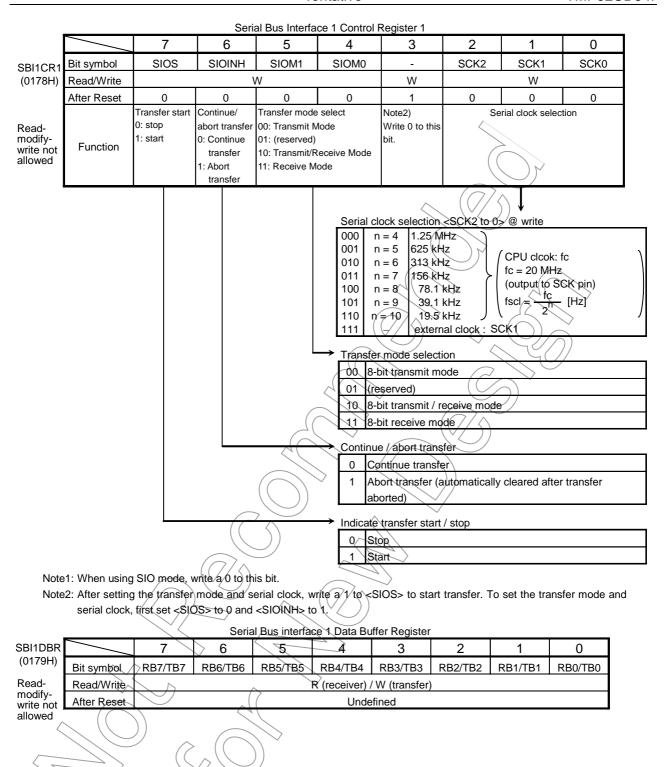

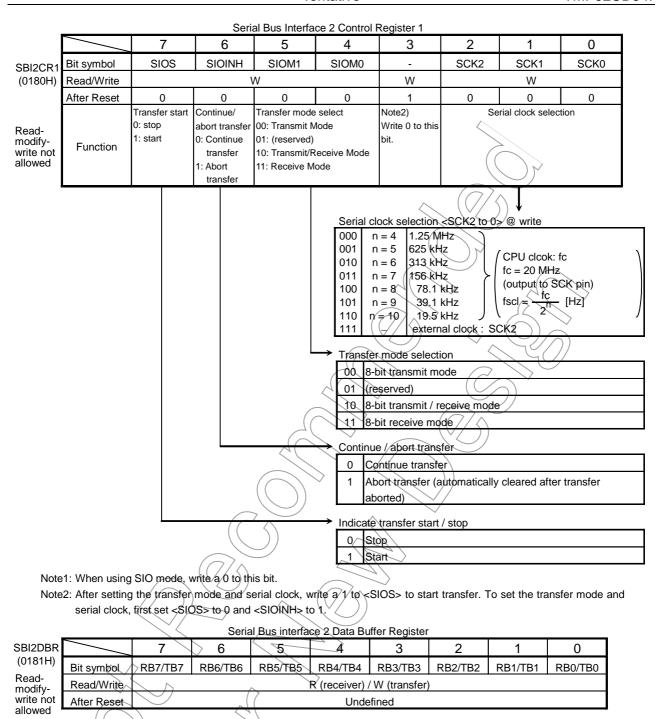

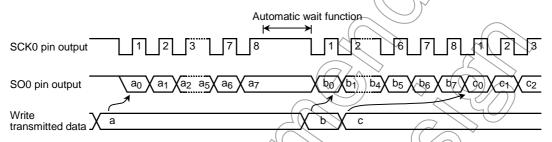

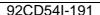

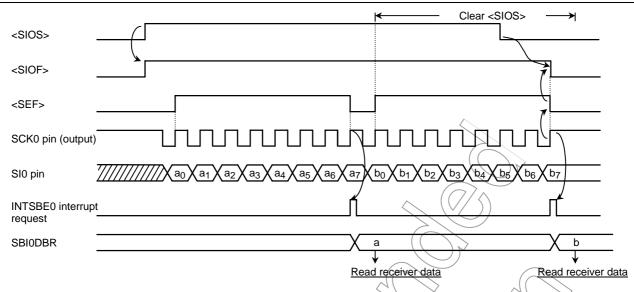

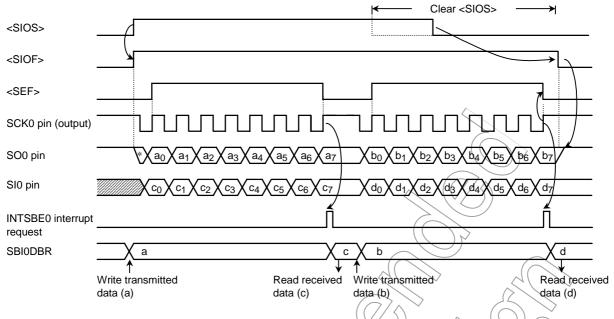

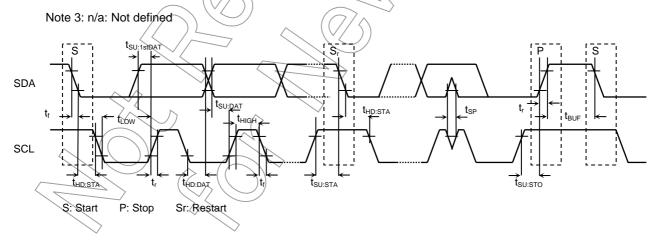

(9) Serial bus interface (SBI): 3 channels

Clock-synchronous 8-bit serial interface mode

I<sup>2</sup>C bus mode

92CD54I-1 2009-12-26

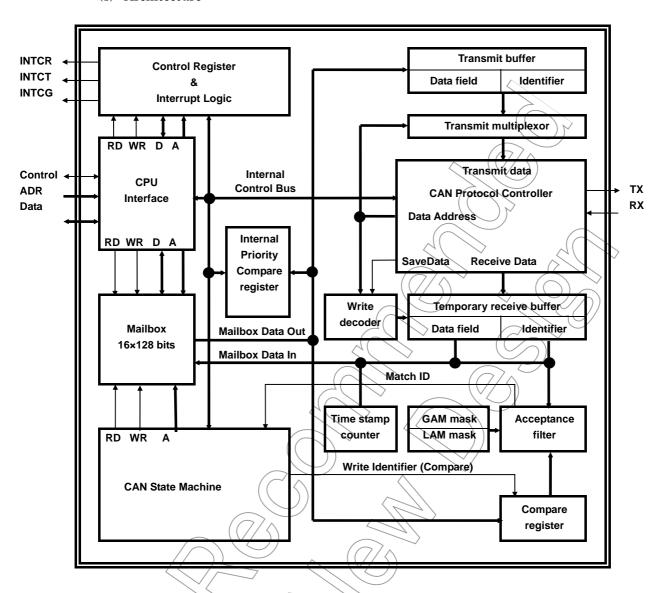

(10) CAN controller: 1 channel

Supports CAN version 2.0B.

16 mailboxes

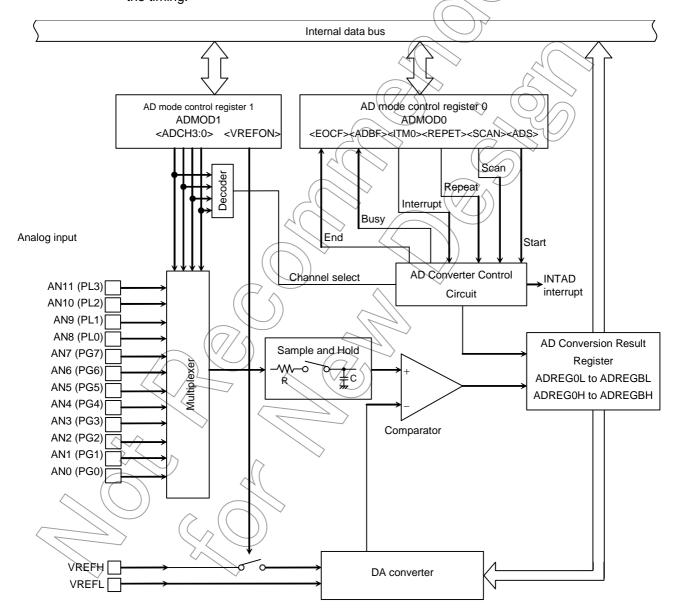

(11) 10-bit A/D converter (ADC): 12 channels

A/D conversion time: 8 µsec (at fc = 20 MHz)

Total tolerance: ± 3 LSB (excluding quantization error)

Scan mode for all 12 channels

- (12) Watch dog timer (WDT)

- (13) Timer for real-time clock (RTC)

Can operate with low-frequency oscillator only.

(14) Interrupt controller (INTC): 60 interrupt sources

9 interrupts from CPU (Software interrupts and undefined instruction interrupt)

42 internal interrupt vectors

9 external interrupt vectors (INT0 to INT7,  $\overline{NMI}$ )

- (15) I/O Port: 68 pins

- (16) Standby mode

Four modes: IDLE3, IDLE2, IDLE1 and STOP STOP mode can be released by 9 external inputs.

- (17) Internal voltage detection flag (RAMSTB)

- (18) Power supply voltage

$V_{CC5} = 4.5 \text{ V to } 5.25 \text{ V}$

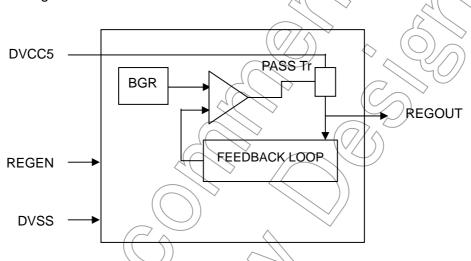

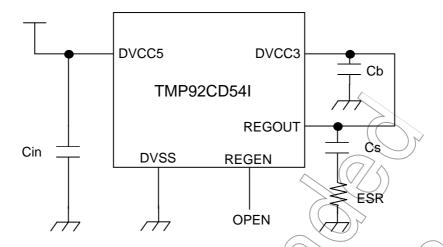

V<sub>CC3</sub> = 3.3 V (Connect REGOUT (built-in-voltage regulator output) to DVCC3.)

(19) Operating temperature: -40 to 85 degree C

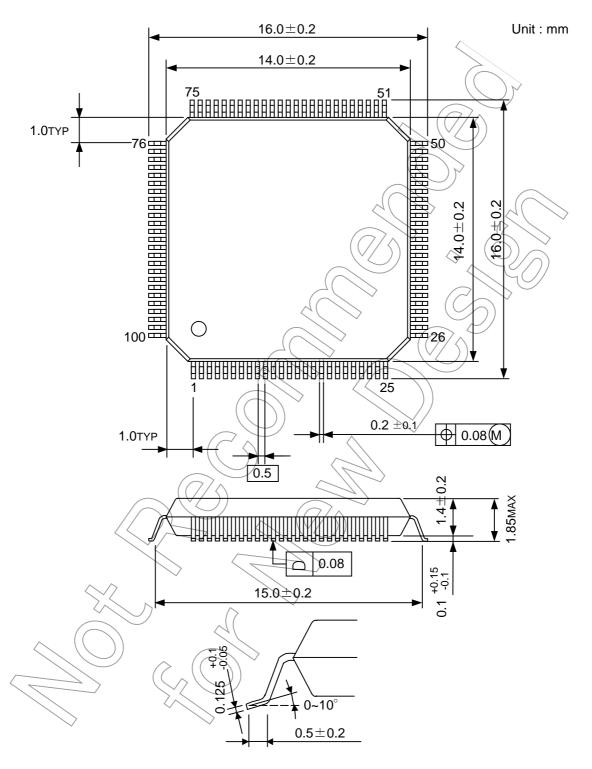

(20) Package: LQFP100-P-1414-0.50F

Figure 1.1 TMP92CD54I block diagram

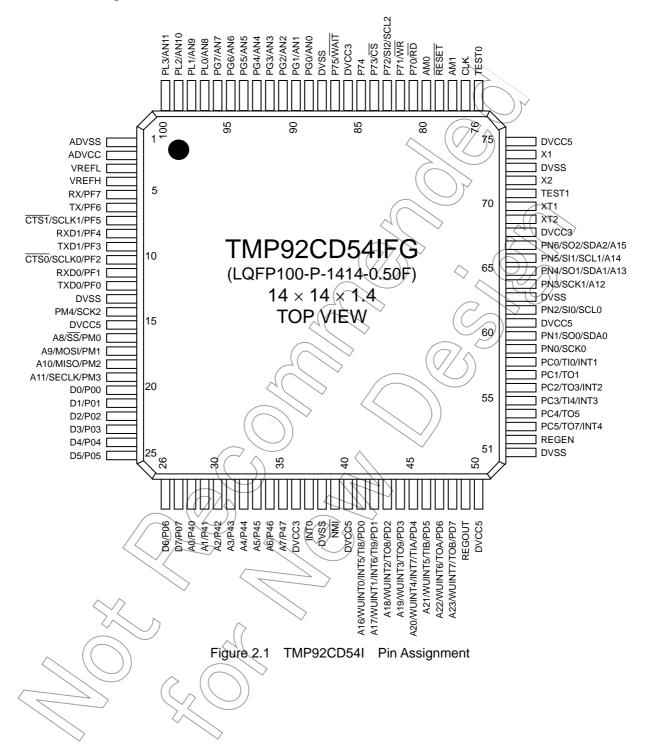

## 2. Pin Assignment and Functions

## 2.1 Pin Assignment

## 2.2 Pin names and functions

The names and functions of the input/output pins are described in are described in the Tables 2.2.1 to 2.2.4.

Table 2.2.1 Input/output pins (1/4)

| Pin name        | Pin<br>number    | Number of pins      | In/Out                                                                | Function                                                                              |  |  |

|-----------------|------------------|---------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

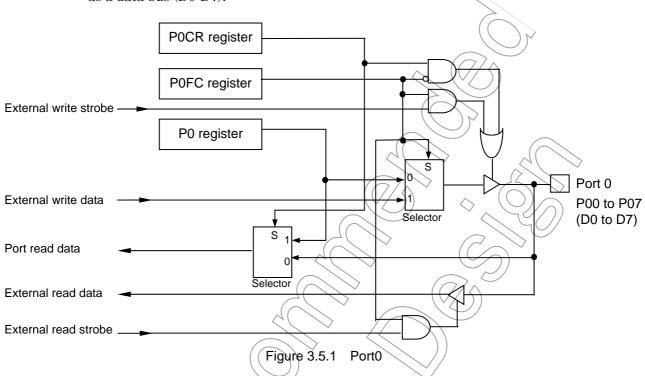

| P00 to P07      | 00 / 07          | (CMOS)              | in/out                                                                | Port 0: I/O port. Input or output specifiable in units of bits.                       |  |  |

| D0 to D7        | 20 to 27         | 0 to 27   8 () in/c |                                                                       | Data: Data bus 0 to 7.                                                                |  |  |

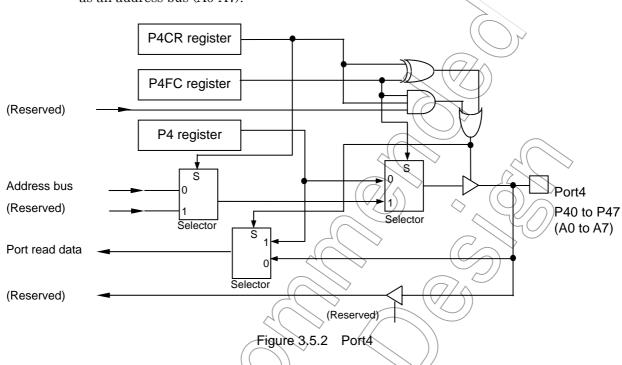

| P40 to P47      |                  |                     | in/out Port4: I/O port. Input or output specifiable in units of bits. |                                                                                       |  |  |

| A0 to A7        | 28 to 35         | 8                   | out                                                                   | Address: Address bus 0 to 7.                                                          |  |  |

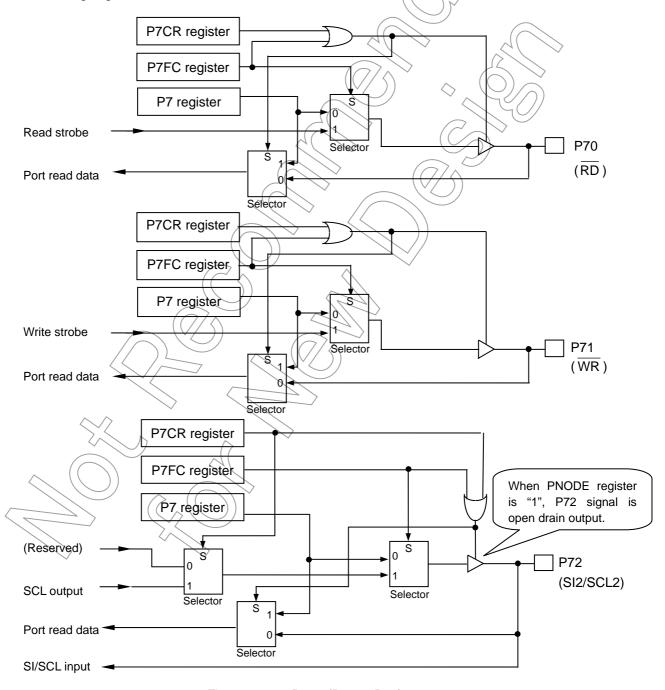

| P70             |                  |                     | in/out                                                                | Port70: I/O port.                                                                     |  |  |

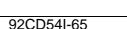

| RD              | 81               | 1                   | out                                                                   | Read: Outputs strobe signal to read external memory.                                  |  |  |

| P71             |                  |                     | in/out                                                                | Port 71: I/O port.                                                                    |  |  |

| $\overline{WR}$ | 82               | 1                   | out                                                                   | Write: Output strobe signal to write external memory.                                 |  |  |

| P72             |                  |                     |                                                                       | Port 72: I/O port.                                                                    |  |  |

| SI2             | 83               | 1                   | in/out                                                                | SBI channel 2: Input data at \$10 mode                                                |  |  |

| SCL2            |                  |                     |                                                                       | SBI channel 2: Clock input/output/at I/C mode                                         |  |  |

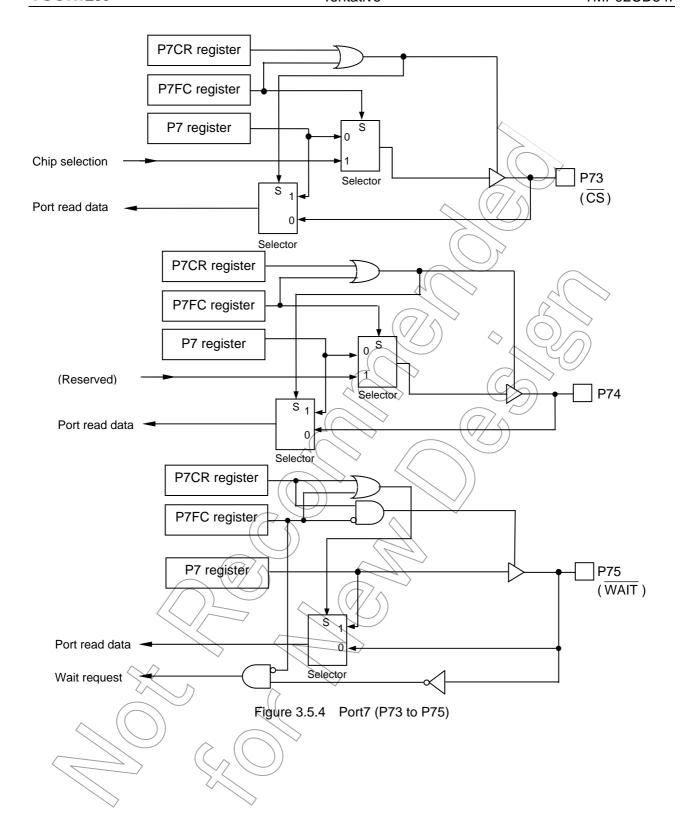

| <u>P73</u>      | 0.4              | 4                   | in/out                                                                | Port 73: I/O port.                                                                    |  |  |

| CS              | 84               | 1                   | out                                                                   | Chip select: Outputs "low" if address is within specified address area.               |  |  |

| P74             | 85               | 1                   | in/out                                                                | Port 74: I/O port.                                                                    |  |  |

| P75             |                  |                     | in/out                                                                | Port 75: I/O port                                                                     |  |  |

| WAIT            | 87               | 1                   | in                                                                    | Wait: Signal used to request CPU bus wait.                                            |  |  |

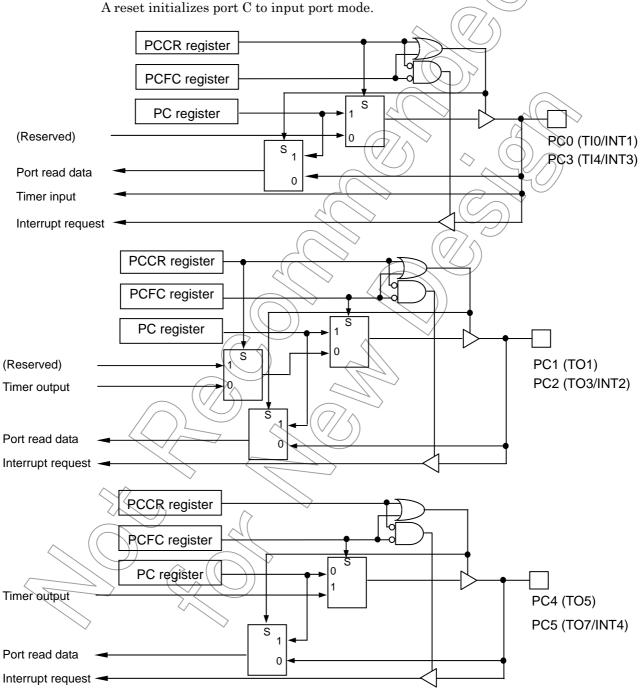

| PC0             |                  |                     | in/out                                                                | Port C0: I/O port.                                                                    |  |  |

| TIO             | 58               | 1                   | in                                                                    | Times input 0: Input his for times 0                                                  |  |  |

| INT1            |                  |                     | in                                                                    | Interrupt request pin 1: Rising-edge interrupt request pin.                           |  |  |

| PC1             |                  |                     | in/out                                                                | Port C1: I/O port.                                                                    |  |  |

| TO1             | 57               | 1                   | out                                                                   | Timer output 1. Output pin for timer 1.                                               |  |  |

| PC2             |                  |                     | in/out                                                                | Port C2; I/O port.                                                                    |  |  |

| TO3             | 56               | 1                   | out                                                                   | Timer output 3: Output pin for timer 3.                                               |  |  |

| INT2            |                  |                     | in                                                                    | Interrupt request pin 2: Rising-edge interrupt request pin.                           |  |  |

| PC3             |                  |                     | in/out//                                                              | Part C3: I/O port.                                                                    |  |  |

| TI4             | 55               | 1                   | in $\bigvee igg $                                                     | Timer input 4: Input pin for timer 4.                                                 |  |  |

| INT3            |                  | // )                | in                                                                    | Interrupt request pin 3/ Rising-edge interrupt request pin.                           |  |  |

| PC4             | F.4              |                     | in/out                                                                | Port C4: I/O port.                                                                    |  |  |

| TO5             | 54               | 1 ~                 | out                                                                   | Timer output 5: Output pin for timer 5.                                               |  |  |

| PC5             |                  |                     | in/out                                                                | Port C5; I/Q port.                                                                    |  |  |

| TO7             | 53               | 71                  | out                                                                   | Timer output 7: Output pin for timer 7.                                               |  |  |

| INT4            | 2/               | \ \ \               | in                                                                    | Interrupt request pin 4: Rising-edge interrupt request pin.                           |  |  |

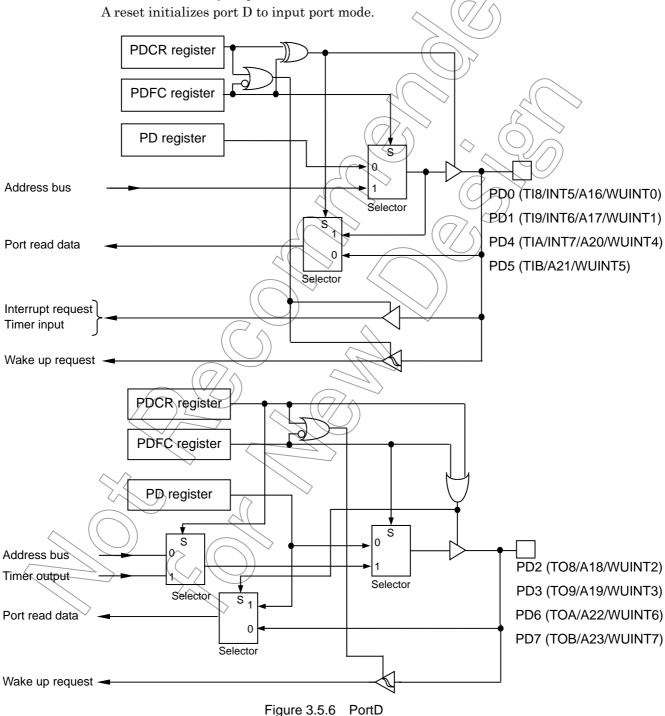

| PD0             |                  |                     | in/out                                                                | Port D0: I/O port.                                                                    |  |  |

| TI8             |                  |                     | in                                                                    | Timer input 8: Input pin for timer 8.                                                 |  |  |

| INT5            | 41               | 1                   | in (                                                                  | Interrupt request pin 5: Interrupt request pin with programmable rising/falling edge. |  |  |

| A16             |                  | (                   | out (                                                                 | Address: Address bus 16.                                                              |  |  |

| WUINTO          |                  |                     | in/                                                                   | Wake up input 0: Wake up request pin with                                             |  |  |

| DD4             |                  | 4                   |                                                                       | programmable rising, falling or both falling and rising edge.                         |  |  |

| PD1             | $\triangleright$ |                     | in/out                                                                | Port D1: I/O port.                                                                    |  |  |

| TI9             |                  |                     | in<br>in                                                              | Timer input 9: Input pin for timer 9.                                                 |  |  |

| INT6<br>A17     | 42               | 1                   | in                                                                    | Interrupt request pin 6: Rising-edge interrupt request pin.  Address: Address bus 17. |  |  |

| WUINT1          |                  |                     | out<br>in                                                             | Wake up input 1: Wake up request pin with                                             |  |  |

| VVOINT          |                  |                     | 1111                                                                  | programmable rising, falling or both falling and rising edge.                         |  |  |

| PD2             |                  |                     | in/out                                                                | Port D2: I/O port.                                                                    |  |  |

| TO8             |                  |                     | out                                                                   | Timer output 8: Output pin for timer 8                                                |  |  |

| A18             | 43               | 1                   | out                                                                   | Address: Address bus 18.                                                              |  |  |

| WUINT2          |                  |                     | in                                                                    | Wake up input 2: Wake up request pin with                                             |  |  |

|                 |                  |                     |                                                                       | programmable rising, falling or both falling and rising edge.                         |  |  |

Table 2.2.2 Input/output pins (2/4)

| Pin name    | Pin       | Number  | In/Out                                | Function                                                                                                |  |  |  |

|-------------|-----------|---------|---------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

|             | number    | of pins |                                       |                                                                                                         |  |  |  |

| PD3         |           |         | in/out                                | Port D3: I/O port.                                                                                      |  |  |  |

| TO9         |           | _       | out                                   | Timer output 9: Output pin for timer 9                                                                  |  |  |  |

| A19         | 44        | 1       | out                                   | Address: Address bus 19.                                                                                |  |  |  |

| WUINT3      |           |         | in                                    | Wake up input 3: Wake up request pin with programmable rising, falling or both falling and rising edge. |  |  |  |

| PD4         |           |         | in/out                                | Port D4: I/O port.                                                                                      |  |  |  |

| TIA         |           |         | in                                    | Timer input A: Input pin for timer A                                                                    |  |  |  |

| INT7        | 45        | 1       | in                                    | Interrupt request pin 7: Interrupt request pin with programmable rising/falling edge.                   |  |  |  |

| A20         |           |         | out                                   | Address: Address bus 20.                                                                                |  |  |  |

| WUINT4      |           |         | in                                    | Wake up input 4: Wake up request pin with programmable rising, falling or both falling and rising edge. |  |  |  |

| PD5         |           |         | in/out                                | Port D5: I/O port.                                                                                      |  |  |  |

| TIB         |           |         | in                                    | Timer input B: Input pin for timer B.                                                                   |  |  |  |

| A21         | 46        | 1       | out                                   | Address: Address bus 21.                                                                                |  |  |  |

| WUINT5      |           |         | in                                    | Wake up input 5: Wake up request pin with programmable rising, falling or both falling and rising edge: |  |  |  |

| PD6         |           |         | in/out                                | Port D6: I/O port.                                                                                      |  |  |  |

| TOA         |           |         | out                                   | Timer output A: Output pin for timer A.                                                                 |  |  |  |

| A22         | 47        | 1       | out                                   | Address: Address bus 22.                                                                                |  |  |  |

| WUINT6      |           |         | in                                    | Wake up input 6: Wake up request pin with                                                               |  |  |  |

| Welltie     |           |         |                                       | programmable rising, falling or both falling and rising edge.                                           |  |  |  |

| PD7         |           |         | in/out                                | Port D7: I/O port                                                                                       |  |  |  |

| ТОВ         |           |         | out                                   | Timer output B: Output pin for timer B.                                                                 |  |  |  |

| A23         | 48        | 1       | out                                   | Address: Address bus 23.                                                                                |  |  |  |

| WUINT7      |           |         | in                                    | Wake up input 7: Wake up request pin with                                                               |  |  |  |

|             |           |         |                                       | programmable rising, falling or both falling and rising edge.                                           |  |  |  |

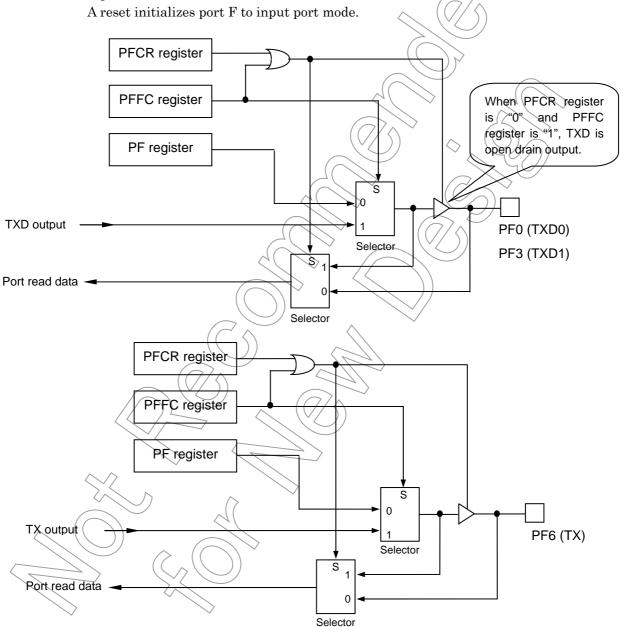

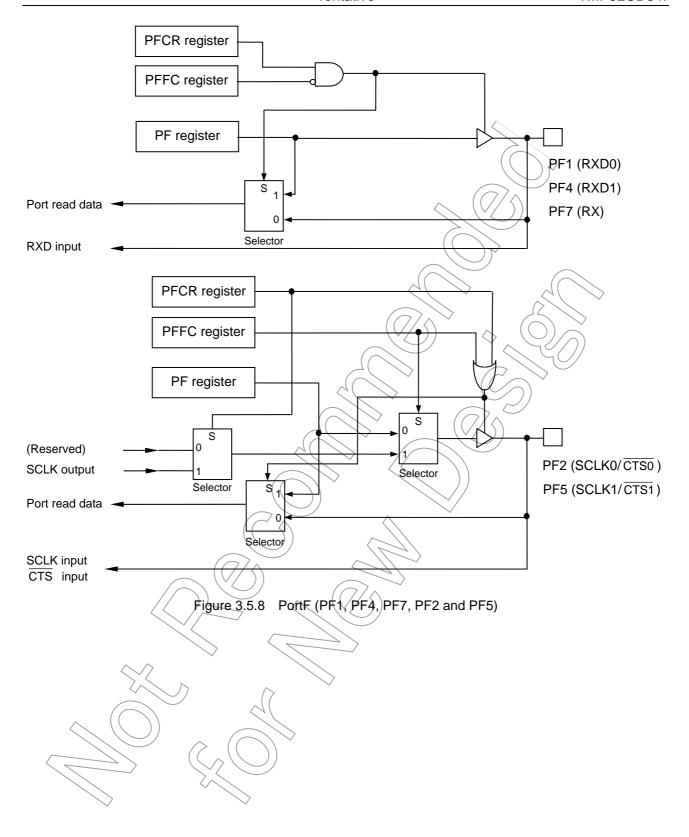

| PF0         | 12        | 4       | in/out                                | Port F0: I/O port.                                                                                      |  |  |  |

| TXD0        | 12        | 1       | out                                   | Serial interface channel 0: Transmission data.                                                          |  |  |  |

| PF1         | 4.4       | 4       | in/out /                              | Port F1: I/O port.                                                                                      |  |  |  |

| RXD0        | 11        | 1       | in                                    | Serial interface channel 0: Receive data.                                                               |  |  |  |

| PF2         |           |         | in/out                                | Port F2: I/O port.                                                                                      |  |  |  |

| SCLK0       | 10        | 1       | in/out//                              | Serial interface channel 9: Clock input/output.                                                         |  |  |  |

| CTS0        |           |         | in 🔍                                  | Serial interface channel 0; Data ready to send. (Clear-to-send)                                         |  |  |  |

| PF3         |           | // )    | in/out_                               | Port F3: (O port. )                                                                                     |  |  |  |

| TXD1        | 9         | 1       | out                                   | Serial interface channel 1: Transmission data.                                                          |  |  |  |

| PF4         |           |         | in/out                                | Port F4: I/O port.                                                                                      |  |  |  |

| RXD1        | 8         | 1       | ìn                                    | Serial interface channel 1: Receive data.                                                               |  |  |  |

| PF5         | $\sim$    | >       | in/out                                | Port F5: I/O port.                                                                                      |  |  |  |

| SCLK1       | 7         | 1 /     | in/out                                | Serial interface channel 1: Clock input/output.                                                         |  |  |  |

| CTS1        |           |         | in                                    | Serial interface channel 1: Data ready to send. (Clear-to-send)                                         |  |  |  |

| PF6         | . ((      |         | in/out                                | Port F6: I/O port.                                                                                      |  |  |  |

| TX          | 6         | "       | out /                                 | CAN: Transmission data.                                                                                 |  |  |  |

| PF7         |           | . (7    | in/out                                | Port F7: I/O port.                                                                                      |  |  |  |

| RX \        | 5         | 1       | m/                                    | CAN: Receive data.                                                                                      |  |  |  |

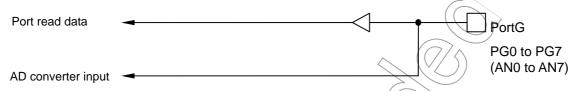

| PG0 to PG7  | 2011.22   |         | 'n                                    | Port G: Input-only port.                                                                                |  |  |  |

| AN0 to AN7  | 89 to 96  | 8       | in                                    | Analog input 0 to 7: AD converter input pins.                                                           |  |  |  |

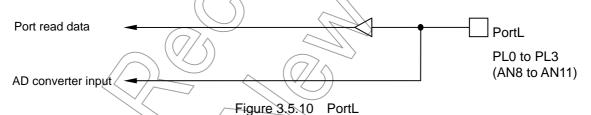

| PL0 to PL3  | 07 to 100 | 4       | in                                    | Port L0 to L3: Input-only port.                                                                         |  |  |  |

| AN8 to AN11 | 97 to 100 | 4       | in                                    | Analog input 8 to 11: AD converter input pins.                                                          |  |  |  |

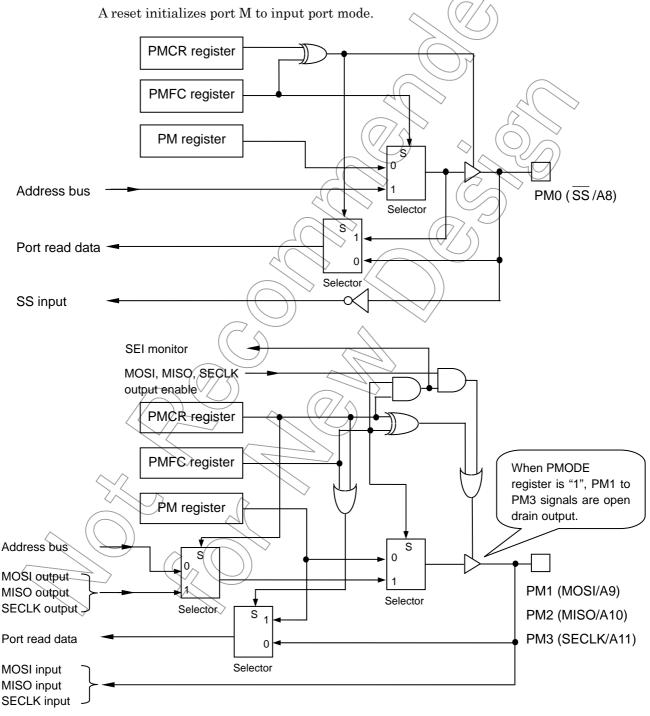

| PM0         |           |         | in/out                                | Port M0: I/O port.                                                                                      |  |  |  |

| SS          | 16        | 1       | in                                    | SEI: Slave select input.                                                                                |  |  |  |

| A8          |           |         | out                                   | Address: Address bus 8.                                                                                 |  |  |  |

| PM1         |           |         | in/out                                | Port M1: I/O port.                                                                                      |  |  |  |

| MOSI        | 17        | 1       | in/out                                | SEI: Master output, slave input.                                                                        |  |  |  |

| A9          |           |         | out                                   | Address: Address bus 9.                                                                                 |  |  |  |

|             | J         | l       | · · · · · · · · · · · · · · · · · · · |                                                                                                         |  |  |  |

Table 2.2.3 Input/output pins (3/4)

| Pin name | Pin<br>number | Number of pins | In/Out   | Function                                                                                                             |  |  |  |

|----------|---------------|----------------|----------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| PM2      |               |                | in/out   | Port M2: I/O port.                                                                                                   |  |  |  |

| MISO     | 18 1 in/o     |                | in/out   | SEI: Master input, slave output.                                                                                     |  |  |  |

| A10      |               |                | out      | Address: Address bus 10.                                                                                             |  |  |  |

| PM3      |               |                | in/out   | Port M3: I/O port.                                                                                                   |  |  |  |

| SECLK    | 19            | 1              | in/out   | SEI: Clock input/output.                                                                                             |  |  |  |

| A11      |               |                | out      | Address: Address bus 11.                                                                                             |  |  |  |

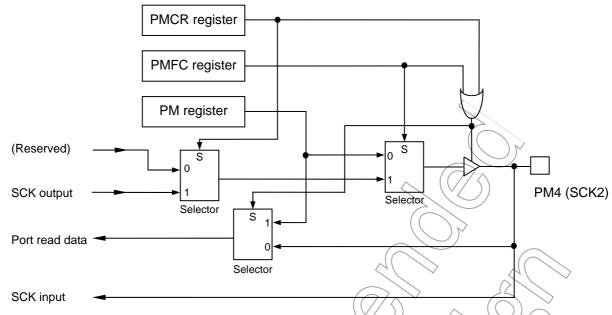

| PM4      | 14            | 1              | in/out   | Port M4: I/O port.                                                                                                   |  |  |  |

| SCK2     | 1-7           | '              | in/out   | SBI channel 2: Clock input/output at SIO mode                                                                        |  |  |  |

| PN0      | 59            | 1              | in/out   | Port N0: I/O port.                                                                                                   |  |  |  |

| SCK0     | 55            | '              | in/out   | SBI channel 0: Clock input/output at SIO mode.                                                                       |  |  |  |

| PN1      |               |                | in/out   | Port N1: I/O port.                                                                                                   |  |  |  |

| SO0      | 60            | 1              | out      | SBI channel 0: Output data input/output at SIO mode                                                                  |  |  |  |

| SDA0     |               |                | in/out   | SBI channel 0: Data input/output at IPC mode                                                                         |  |  |  |

| PN2      |               |                | in/out   | Port N2: I/O port.                                                                                                   |  |  |  |

| SI0      | 62            | 1              | in       | SBI channel 0: Input data at SIO mode                                                                                |  |  |  |

| SCL0     |               |                | in/out   | SBI channel 0: Clock input/output at 12°C mode                                                                       |  |  |  |

| PN3      |               |                | in/out   | Port N3: I/O port.                                                                                                   |  |  |  |

| SCK1     | 64            | 1              | in/out   | SBI channel 1: Clock input/output at SIO mode                                                                        |  |  |  |

| A12      |               |                | out      | Address: Address bus 12.                                                                                             |  |  |  |

| PN4      |               |                | in/out   | Port N4: I/O port.                                                                                                   |  |  |  |

| SO1      | 65            | 1              | out      | SBI channel 1: Output data at SIO mode                                                                               |  |  |  |

| SDA1     | 05   1        |                | in/out   | SBI channel 1. Data input/output at I <sup>2</sup> C mode                                                            |  |  |  |

| A13      |               |                | out      | Address: Address bus 13.                                                                                             |  |  |  |

| PN5      |               |                | in/out   | Port N5: I/Q port.                                                                                                   |  |  |  |

| SI1      | 66            | 1              | in       | SBI channel 1: Input data at SIO mode                                                                                |  |  |  |

| SCL1     | 00            | '              | in/out   | SBI channel 1. Clock input/output at 12C mode                                                                        |  |  |  |

| A14      |               |                | out      | Address: Address bus 14                                                                                              |  |  |  |

| PN6      |               |                | (        | Port N6; I/O port.                                                                                                   |  |  |  |

| SO2      | 67            | 1              | in/out \ | SBI channel 2: Output data at SIO mode                                                                               |  |  |  |

| SDA2     | 0.            | •              | out      | SBI-channel 2: data input output at I2C mode                                                                         |  |  |  |

| A15      |               |                |          | Address: Address bus 15.                                                                                             |  |  |  |

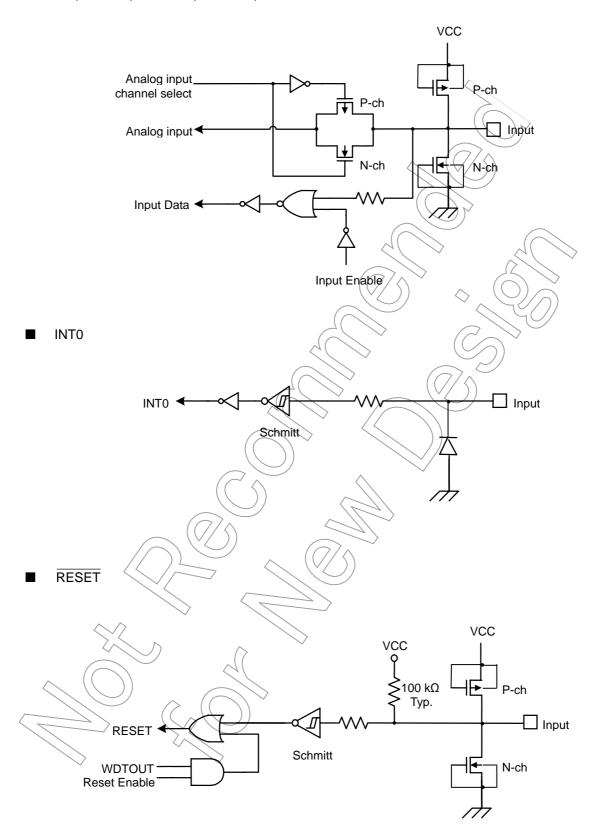

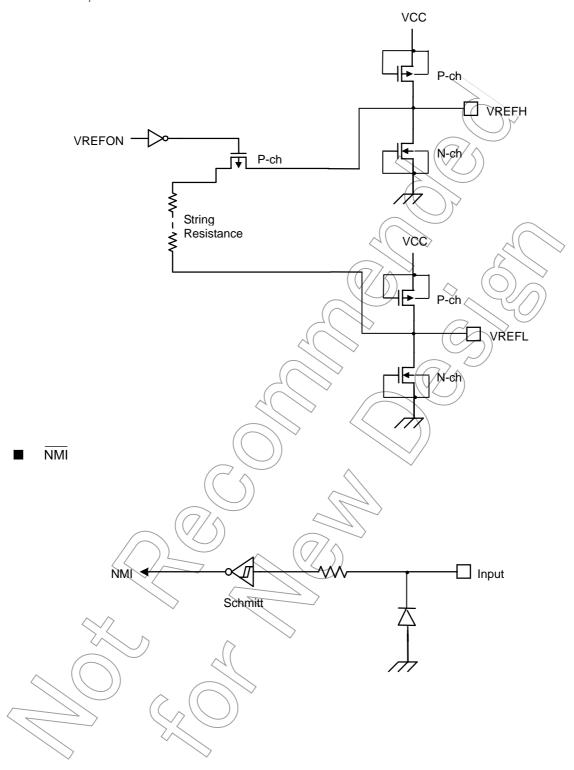

| NMI      | 39            | 1              | jn       | Non-maskable interrupt: Interrupt request pin with programmable falling or both falling and rising edge.             |  |  |  |

| INT0     | 37            | 1              | in       | Interrupt request pin 0: Interrupt request pin with programmable level or rising-edge.                               |  |  |  |

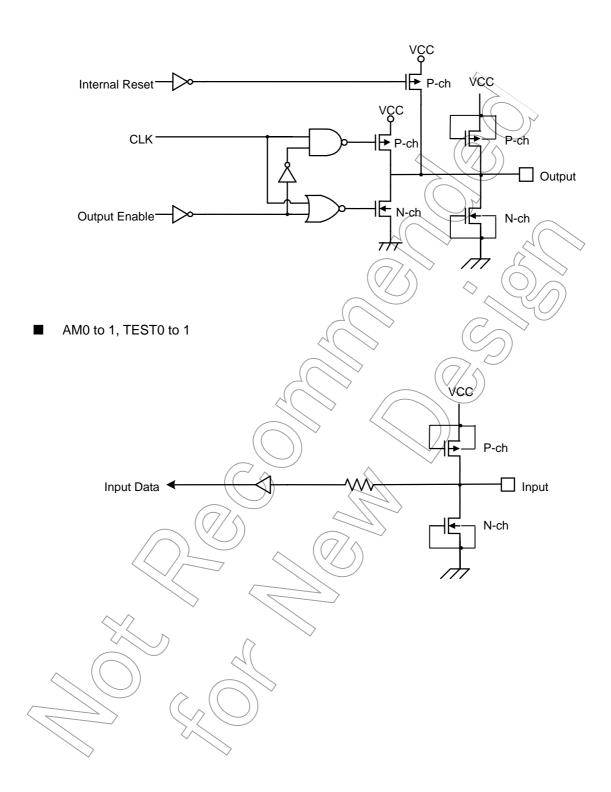

| AM0,1    | 80, 78        | 2              | in       | Address Mode selection: Connect AM0 pin to L and AM1 pin to H for Single Chip mode.                                  |  |  |  |

| TEST0,1  | 76, 71        | 2              | in       | Test mode pins: Should be tied to GND.                                                                               |  |  |  |

| CLK      | 77            | 1              | out      | Programmable clock output (with pull-up resistor)                                                                    |  |  |  |

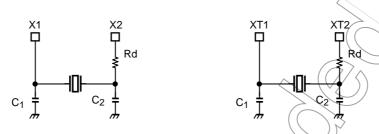

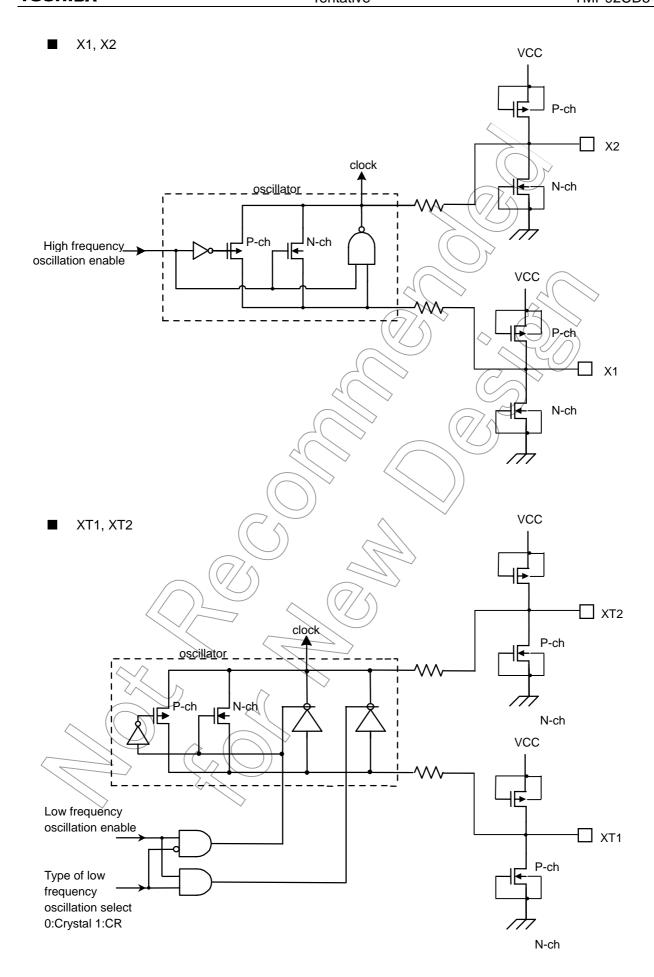

| X1/X2    | 74, 72        | 2)             | in/out   | High-frequency oscillator connecting pins: To drive these pins with an external clock, apply clock signals of 3.3 V. |  |  |  |

| XT1/XT2  | 70, 69        | 2              | in/out   | Low-frequency oscillator connecting pins: To drive these pins with an external clock, apply clock signals of 3.3 V.  |  |  |  |

| RESET    | 79            | 1              | in       | Reset: Initializes LSI (with pull-up resistor).                                                                      |  |  |  |

| VREFH    | 4             | 1              | in       | AD reference voltage high                                                                                            |  |  |  |

| VREFL    | 3             | 1              | in       | AD reference voltage low                                                                                             |  |  |  |

| ADVCC    | 2             | 1              | -        | Power supply pin for AD converter (+5V): Connect the ADVCC pin to 5-V power supply.                                  |  |  |  |

| ADVSS    | 1             | 1              | -        | GND pin for AD converter: Connect the ADVSS pin to GND (0V).                                                         |  |  |  |

Table 2.2.4 Input/output pins (4/4)

| Pin name | Pin<br>number             | Number of pins | In/Out | Function                                                                    |

|----------|---------------------------|----------------|--------|-----------------------------------------------------------------------------|

| DVCC5    | 15, 40,<br>50, 61, 75     | 5              | -      | Power supply pins (+5V): Connect all the DVCC5 pins to 5-V power supply.    |

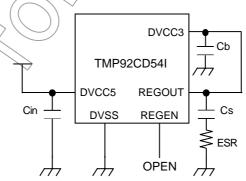

| DVCC3    | 36, 68, 86                | 3              | -      | Power supply pins (+3.3V): Connect all the DVCC3 pins to REGOUT pin.        |

| DVSS     | 13, 38, 51,<br>63, 73, 88 | 6              | -      | GND: Connect all DVSS pins to GND (0V).                                     |

| REGOUT   | 49                        | 1              | out    | Regulator output 3.3V: Connect capacitor to stabilize the regulator output. |

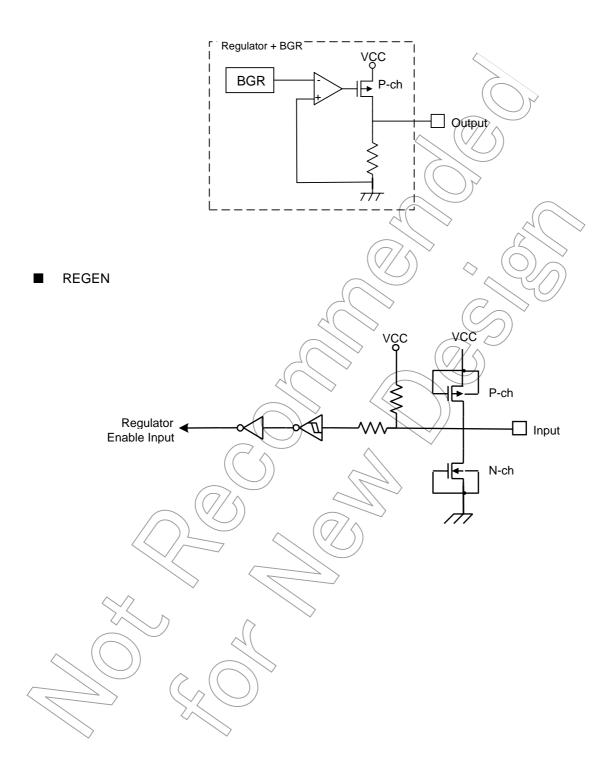

| REGEN    | 52                        | 1              | in     | Regulator enable pin: Should be set to H or OPEN (with pull-up resistor).   |

## 3. Operation

This section describes the basic functions and operations of the TMP92CD54I for each functional block.

#### 3.1 CPU

The TMP92CD54I incorporates a high-performance, high-speed 32-bit CPU, the TLCS-900/H1.

#### 3.1.1 CPU Overview

The TLCS-900/H1 is a high-performance, high-speed CPU based on the TLCS-900/L1 and has a built-in data bus extended to 32 bits to enable faster processing.

Table 3.1.1 shows an overview of the CPU built into the TMP92CD54I.:

| Table 3.                         | 1.1 CPU Overview                           |                                        |

|----------------------------------|--------------------------------------------|----------------------------------------|

| Properties                       | TLCS-900/H1                                |                                        |

| Width of CPU Address Bus         | 24 bit                                     |                                        |

| Width of CPU Data Bus            | 32 bit (// ))                              | $\rightarrow \bigcirc\bigcirc\bigcirc$ |

| Internal Operating Frequency     | 16 to 20MHz (fosc = 8 to 10MH              | z) ( )                                 |

| Minimum Bus Cycle (Internal RAM) | 1 clock access (50ns @ f <sub>OSC</sub> =  | 10MHz)                                 |

| Internal RAM                     | 32 bit 1 clock access                      | ý v                                    |

| Internal ROM                     | 32 bit interleave 2-1-1-1 clock a          | ccess                                  |

| Internal I/O                     | 8/16 bit 2 clock access                    | PORT, INTC,                            |

|                                  | $\vee$                                     | MEMC                                   |

| 4(                               | 8/16 bit 5 to 6 clock access               | SEI, SIO, WDT,                         |

|                                  |                                            | 8 bit Timer,                           |

|                                  | Y ))                                       | 16 bit Timer,                          |

|                                  |                                            | RTC, 10-bit ADC,                       |

|                                  | <u> </u>                                   | SBI, CAN                               |

| External Device                  | 8 bit 2 clock access (can insert           | wait cycles)                           |

| Minimum Instruction              | 1 clock (50ns at f <sub>OSC</sub> = 10MHz) |                                        |

| Execution Cycle                  |                                            |                                        |

| Conditional Jump                 | 2 clock (100ns at fosc = 10MH              | z)                                     |

| Instruction Queue Buffer         | 12 byte                                    | ·                                      |

| Instruction Set                  | Compatible with TLCS-900, 900              | 0/H, 900/L,                            |

|                                  | 900/L1 and 900/H2 (NORMAL                  | , MIN, MAX and LDX                     |

| $\rightarrow$                    | instructions are not supported)            |                                        |

| Micro DMA                        | 8 channels                                 |                                        |

#### 3.1.2 Reset

To apply a reset to the TMP92CD54I, drive the  $\overline{RESET}$  input pin Low for at least 4  $\mu s$  (when fosc = 10 MHz) when the internal oscillator and clock multiplier are operating stably with the supply voltage in the normal operating range.

The clock multiplier is bypassed during the reset period so that the system clock frequency, fc, becomes 5 MHz (when fosc = 10 MHz).

When a reset is accepted, the CPU operates as follows:

• Sets the Program Counter (PC) as follows in accordance with the Reset Vector stored at address FFFF00H to FFFF02H:

```

PC<0 to 7> ← data in location FFFF00H

PC<8 to 15> ← data in location FFFF01H

PC<16 to 23> ← data in location FFFF02H

```

- Sets the Stack Pointer (XSP) to 00000000H.

- Sets bits <IFF0 to IFF2> of the Status Register (SR) to 111 (thereby setting the Interrupt Level Mask Register to level 7).

- Clears bits <RFP0 to RFP1> of the Status Register to 00 (thereby selecting Register Bank 0).

When a reset is released, the CPU starts fetching and executing instructions according to the program counter (PC). The registers within the CPU other than those shown above remain unchanged.

A reset being accepted also causes the built-in I/O, input/output port and other pins to be initialized as follows:

- Initializes the internal O registers as table of "Special Function Register" in Section 5.

- Sets the port pins, including the pins that also act as internal I/O, to General-Purpose Input or Output Port Mode.

When the RESET input pin is driven High, the built-in clock multiplier starts operating and the internal reset is released after the setting time for the circuit (1.6384 ms when fosc = 10MHz) elapses.

Upon a power on reset, the control signals for the memory controller are unstable, possibly resulting in backup data being rewritten in external RAM connected to the TMP92CD54I.

When the RESET input pin goes Low, the input/output ports are initialized to input mode and the CLKOUT pin output setting is initialized to High-Z output. The CLKOUT pin outputs High because it is pulled up within the device. Since the pull-up circuit operates on the DVCC3 supply, however, the internal transistor on/off operation is not stable while the DVCC3 supply is rising, resulting in either a High-Z or High (pulled up) output.

## 3.1.3 Selecting a Startup Mode

Set TEST0 and TEST1 to GND, AM0 to Low and AM1 to High to select single-chip mode.

| т                | Table 3.1.2 Operation Mode Setup |               |               |             |  |  |  |  |

|------------------|----------------------------------|---------------|---------------|-------------|--|--|--|--|

| Operation Mode   |                                  | Mod           | e Setup inpu  | ut pin      |  |  |  |  |

| Operation widde  | RESET                            | AM1           | AM0           | TEST1 TEST0 |  |  |  |  |

| Single-chip Mode |                                  | Н             | L             | L           |  |  |  |  |

|                  |                                  |               | (             |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  |                                  |               | 4             |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  |                                  | 4             | $\Rightarrow$ |             |  |  |  |  |

|                  |                                  |               |               | (7/5)       |  |  |  |  |

|                  | 4(                               |               |               |             |  |  |  |  |

|                  |                                  | )             |               | ))          |  |  |  |  |

|                  |                                  | ,<br>         |               | ~           |  |  |  |  |

|                  | $\sim$                           |               |               |             |  |  |  |  |

|                  | ))                               |               | <b>→</b>      |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  | $\wedge$                         | $\rightarrow$ |               |             |  |  |  |  |

|                  | 4                                |               |               |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

|                  |                                  |               |               |             |  |  |  |  |

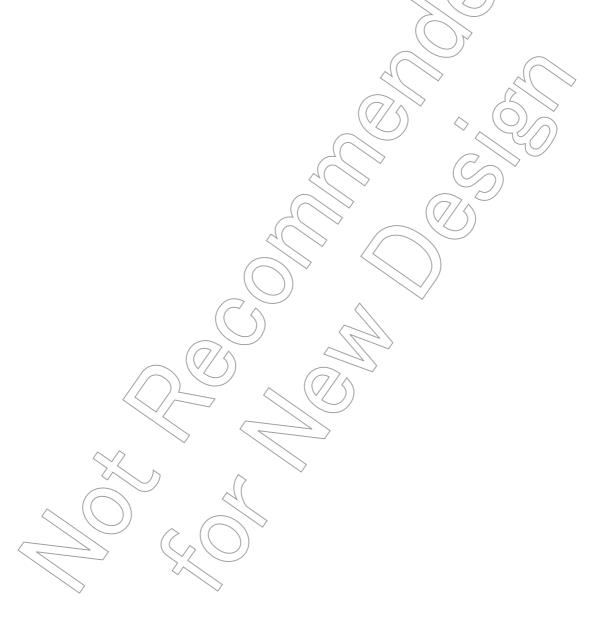

#### 3.2 Memory Map

Figure 3.2.1 shows a memory map of the TMP92CD541I.

Note 1: When an emulator is used, 64 Kbytes of the 16-Mbyte space are used to control the emulator and not available to the user.

Note 2: Accessing the emulator control space causes the WR and RD signals to be output. This should be taken into account when using expanded memory.

Note 3: The last 16 bytes (addresses FFFFF0H to FFFFFH) in the vector table are reserved as internal space and cannot be used.

Note 4: If memory devices having different bus widths are located at contiguous addresses, any access spanning those devices should not be executed with a single instruction. Such an attempt may prevent data from being read or written normally.

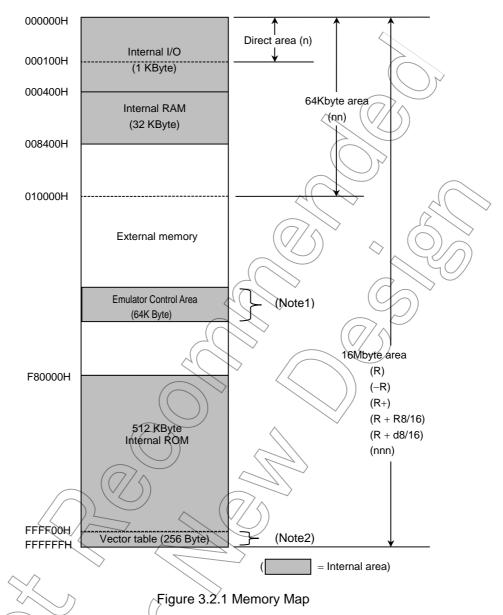

## 3.3 Clock Function and Standby Functions

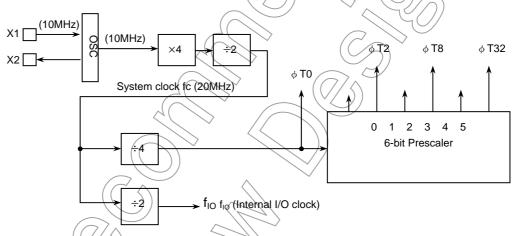

## 3.3.1 System Clock Block Diagram

#### 3.3.2 Standby Controller

#### (1) Halt Mode

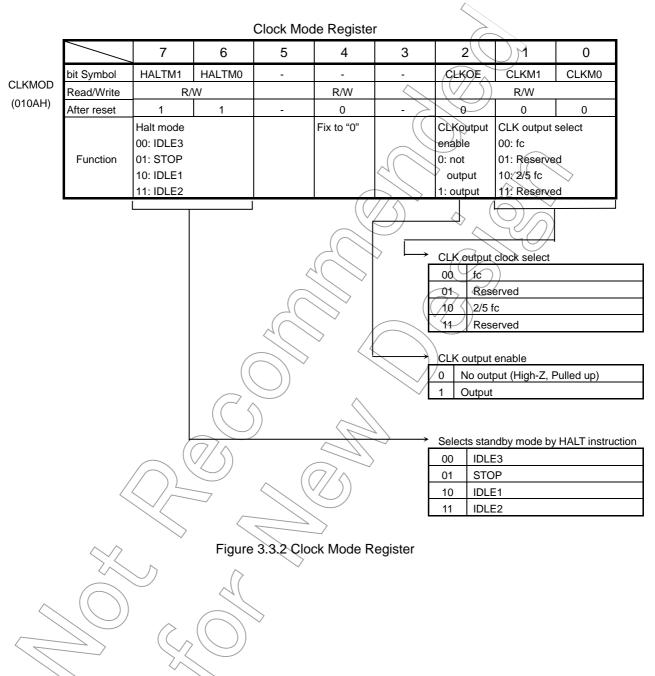

Executing the HALT instruction (stop instruction) sets the operating mode to any of IDLE2, IDLE1, IDLE3 and STOP depending on the setting of CLKMOD<HALTM1:0>.

The following shows whether individual blocks operate or stop in each mode:

1. IDLE2 mode: Only the CPU is stopped.

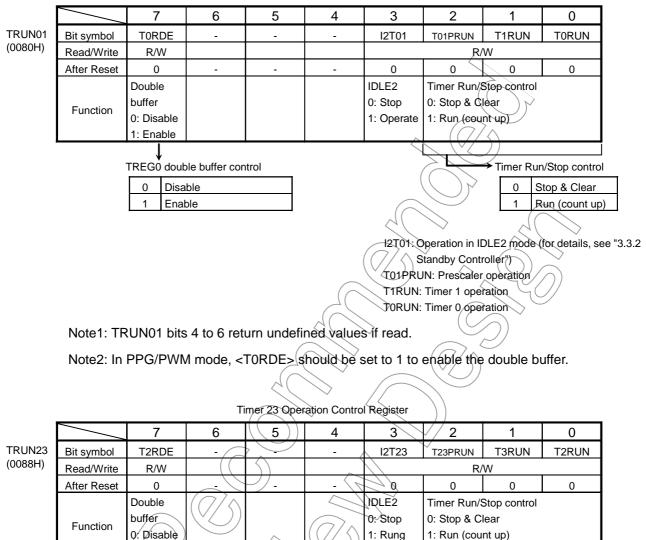

Each built-in I/O block has a bit that controls whether it operates or stops in IDLE2 mode. The bits shown in Table 3.3.1 are used to control the operation of built-in I/O blocks.

Table 3.3.1 the registers to control operation during Idle2 Mode

| Internal I/O  | SFR Registers             |

|---------------|---------------------------|

| TIMER0,TIMER1 | TRUN01 <i2t01></i2t01>    |

| TIMER2,TIMER3 | TRUN23 <i2t23></i2t23>    |

| TIMER4,TIMER5 | TRUN45 <i2t45></i2t45>    |

| TIMER6,TIMER7 | TRUN67 <i2t67></i2t67>    |

| TIMER8        | TRUN8<12T8>               |

| TIMERA        | TRUNA <i2ta></i2ta>       |

| SIO0          | SC0MØD1>12S0>             |

| SIO1          | SC1MOD1<12\$1>            |

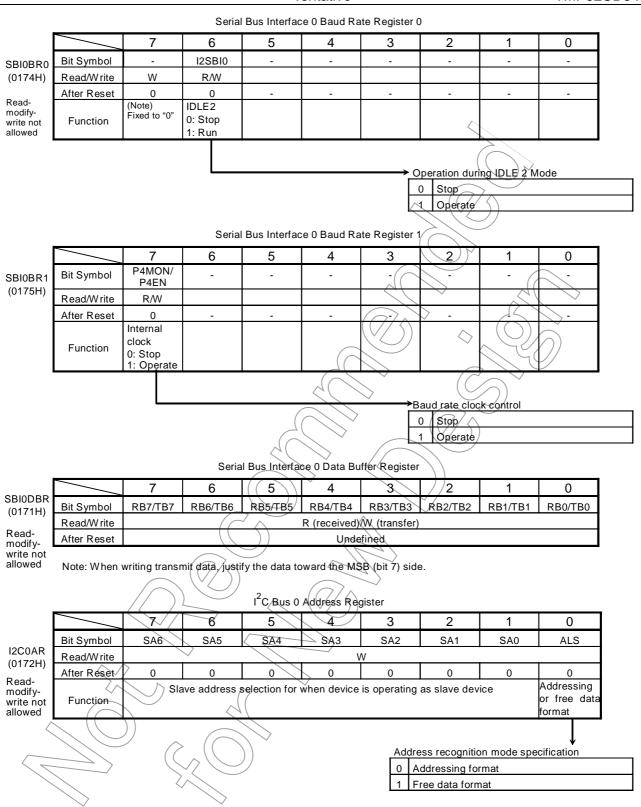

| SBI0          | SBI0BR0<12SBI0>           |

| SBI1          | SBI1BR0 <i2sbi1></i2sbi1> |

| SBI2          | SBI2BR0 <i2sbi2></i2sbi2> |

| A/D converter | ADMOD1 <i2ad></i2ad>      |

| WDT           | WDMOD <i2wdt></i2wdt>     |

|               |                           |

- 2. IDLE1 mode: Only the low-speed oscillator and high-speed oscillator operate.

- 3. IDLE3 mode: Only the low-speed oscillator and RTC operate.

- 4. STOP mode: All internal circuits are stopped.

Table 3.3.2 shows which blocks operate and stop during halt mode.

Table 3.3.2 I/O operation during Halt Modes

|       | // \                                             |                                                 | // ( \ |         |          |

|-------|--------------------------------------------------|-------------------------------------------------|--------|---------|----------|

|       | Halt Mode                                        | IDLE2                                           | ∕IDLĖ1 | IDLE3   | STOP     |

|       | CLKMOD <halt1:0>/</halt1:0>                      | 11                                              |        | 00      | 01       |

|       | CPU                                              |                                                 | Halt   |         |          |

|       | I/O ports                                        | Hold the same state<br>the HALT instruction was |        | See tab | le 3.3.5 |

| Block | 8-bit TMR, 16-bit TMR SIO, SBI A/D converter WDT | Selectable<br>See table 3.3.1                   |        | Stop    |          |

|       | RTC, XT1 CAN, SEI Interrupt controller           | Operational                                     |        |         |          |

#### (2) Releasing a halt mode

A halt mode can be released with a reset or an interrupt request. Available halt release sources depend on the state of the interrupt mask register <IFF2:0> and the halt mode.

Table 3.3.3 shows details.

#### · Release using an interrupt request

Whether a halt state is released with an interrupt request depends on the interrupt enable status. If the interrupt request level set before the execution of the HALT instruction is greater than or equal to the value stored in the interrupt mask register, the halt mode is released, followed by interrupt handling for that interrupt source, after which processing is started from the instruction next to the HALT instruction. If the interrupt request level is lower than the value in the interrupt mask register, the halt mode is not released (a nonmaskable interrupt, however, always causes the halt mode to be released and the interrupt to be handled, regardless of the mask register value).

Only an INTO interrupt, however, releases the halt mode even if the interrupt request level is lower than the value in the interrupt mask register. In that case, interrupt handling is not performed and processing is started from the instruction next to the HALT instruction (the INTO interrupt request flag maintains the value of "1").

#### · Release with a reset

A reset causes all halt modes to be released

To release STOP or IDLE3 mode, however, it requires a sufficient reset time (10 ms or longer when fosc = 10 MHz) for the internal oscillator to operate stably.

When a halt mode is released with a reset, the data in built-in RAM can hold the values it had immediately before entering the halt state but other settings are initialized (a release with an interrupt allows both RAM data and other settings to maintain their pre-halt values).

| Status of Received Interrupt |           |                                           | Interrupt Enabled (interrupt level) ≥ (interrupt mask) |       |                    | Interrupt Disabled (interrupt level) < (interrupt mask) |               |       |                      |        |

|------------------------------|-----------|-------------------------------------------|--------------------------------------------------------|-------|--------------------|---------------------------------------------------------|---------------|-------|----------------------|--------|

|                              | Halt mode |                                           |                                                        | ldle1 | Idle3              | Stop                                                    | ldle2         | ldle1 | Idle3                | Stop   |

|                              |           | NMI                                       | 0                                                      | 0     | ⊚ <sup>*1</sup>    | ⊚ <sup>*1</sup>                                         | =             | =     | =                    | =      |

|                              |           | INTWDT                                    | 0                                                      | ×     | ×                  | ×                                                       | - <           | -     | -                    | -      |

|                              |           | INT0                                      | 0                                                      | 0     | ⊚ <sup>*1 *2</sup> | ⊚ <sup>*1 *2</sup>                                      | 0             | 2 0   | O*1 *2               | O*1 *2 |

| g                            |           | INT0 [MASK]                               | 0                                                      | 0     | O*1 *2             | O*1 *2                                                  | 0 (           | 0     | O*1 *2               | O*1 *2 |

| clearance                    |           | INT1 to 7                                 | 0                                                      | ×     | ×                  | ×                                                       | ×             | \\    | ×                    | ×      |

| eal                          | Se        | INTT0 to 7                                | 0                                                      | ×     | ×                  | ×                                                       | (*)           | ×     | ×                    | ×      |

|                              | ource     | INTTR8 to B                               | 0                                                      | ×     | ×                  | ×<\                                                     | ( <b>k</b> // | )) ×  | ×                    | ×      |

| Halt state                   | တ         | INTTO8, INTTOA                            | 0                                                      | ×     | ×                  | ×                                                       |               | / ×   | ×                    | ×      |

| t st                         | nterrupt  | INTRX0 to 1, TX0 to 1                     | 0                                                      | ×     | ×                  | × ((                                                    | X             | ×     | ×                    | ×      |

| 1<br>Tig                     | err       | INTCR0, INTCT0, INTCG0                    | 0                                                      | ×     | ×                  | × \                                                     |               | ×     | ×                    | ×      |

| of F                         | Int       | INTSEM0, E0, R0, T0                       | 0                                                      | ×     | ×                  | (*)                                                     | ×             | ×     | ×                    | ×      |

|                              |           | INTSBE0, S0, E1, S1, E2, S2               | 0                                                      | ×     | ×                  | $\mathcal{A}(x)$                                        | ×             | × \(  | ×                    | ×      |

| Source                       |           | INTAD                                     | <u></u>                                                | ×     | ×                  | X                                                       | ×             | *     | ×                    | ×      |

| So                           |           | All the above-mentioned interrupts [MASK] | ×                                                      | ×     | *(7                | //×~                                                    | ×             | (X)   | ×                    | ×      |

|                              |           | INTRTC                                    | 0                                                      | 0     | @ <sup>\1</sup> \  | $\bigcup_{\lambda}$                                     | 6             | 6//   | )<br>9 <sup>*1</sup> | ×      |

|                              |           | INTRTC [MASK]                             | 0                                                      | 0 (   | (e)                | ×                                                       | 0             |       | /6"                  | ×      |

|                              |           | RESET                                     | 0                                                      | 0     | ( o )              | <b>)</b>                                                | •             |       | <b>©</b>             | 0      |

- Upon release from a halt, the CPU starts handling the interrupt (RESET causes the device to be initialized).

- O: Upon release from a halt, the CPU starts processing from the instruction next to the HALT instruction.

- $\times$ : Cannot be used to release a halt.

- : These combinations are not available because the interrupt priority level (interrupt request level) for nonmaskable interrupts is fixed to 7 (top priority).

- \*1: A halt is released after a warm-up time elapses.

- \*2: Any WUINT interrupt (WUINTO to 7) causes an INTO interrupt to occur.

- Note 1: To release a halt using a level-mode INTO interrupt in the interrupt-enabled state, hold it High until interrupt handling starts. If it is driven low before interrupt handling starts, the interrupt cannot be handled normally.

- Note 2: When using an INT5 to INT7 external interrupt in IDLE2 mode, set TRUN8<I2T8> and TRUNA<I2TA> to 1.

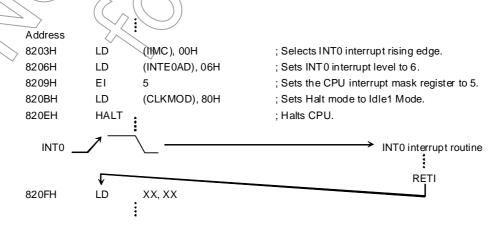

(Example - clearing IDLE1 Mode)

An INTO interrupt in edge mode is used to release a halt in IDLE1 mode.

#### (3) Operation in each mode

#### 1. IDLE2 Mode

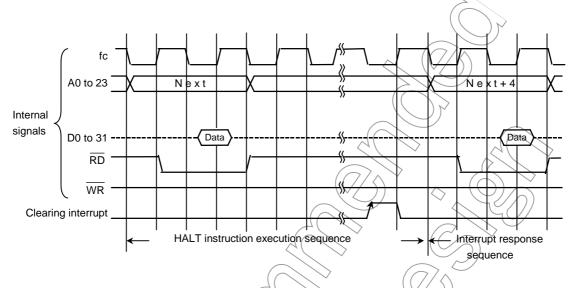

In IDLE2 mode, the system clock is supplied only to the built-in I/O blocks specified with the built-in I/O operation control bits and the CPU stops executing instructions.

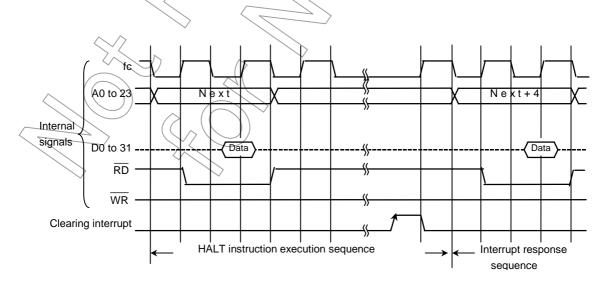

Figure 3.3.3 shows an example timing for releasing a halt state using an interrup.

Figure 3.3.3 Timing chart for Idle2 Mode Halt state cleared by interrupt

#### 2. IDLE1 mode

In IDLE1 mode, only the internal oscillator operates with the system clock for the CPU stopped.

In the halt state, interrupt request sampling is performed asynchronously to the system clock. The halt state is, however, released in sync with the system clock.

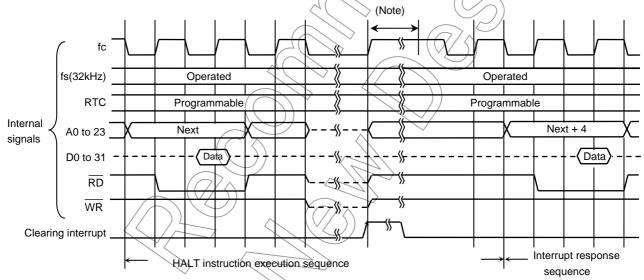

Figure 3.3.4 shows an example timing for releasing a halt state using an interrupt.

Figure 3.3.4 Timing chart for Idle1 Mode Halt state cleared by interrupt

#### 3. IDLE3 mode

In IDLE3 mode, all internal circuits other than the low-speed oscillator and RTC, including the high-speed oscillator, are stopped. The pin states in IDLE3 mode depends on the setting of WDMOD<DRVE>. Table 3.3.5 shows the states of pins in IDLE3 mode.

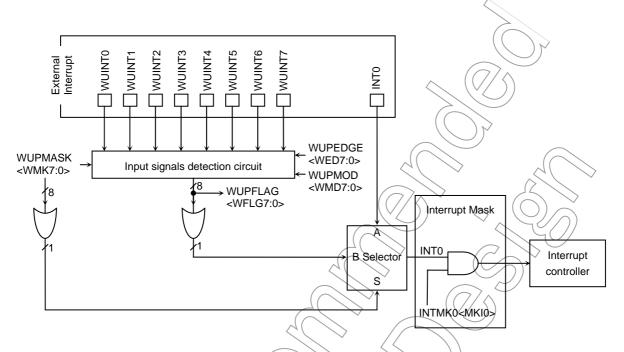

The halt state in IDLE3 mode can be released with an external interrupt using the  $\overline{\text{NMI}}$ , INT0, or WUINT0 to 7 pin (INT0 interrupt), an internal interrupt using INTRTC, or a reset.

Upon released from the halt state, the system clock output starts after the high-speed oscillator warm-up time and clock multiplier settling time elapse.

The warm-up time for the high-speed oscillator is counted using the warm-up counter within the TMP92CD54I. Once that counting ends, the device starts counting the settling time for the clock multiplier. This mechanism results in the high-speed oscillator warm-up time (1.6 ms) being included in the time required between the halt release signal being input and the system clock being output even in a system using an external oscillator that does not need oscillation settling time.

When using a reset to release a halt, ensure that the reset signal is held Low until the high-speed oscillator operates stably.

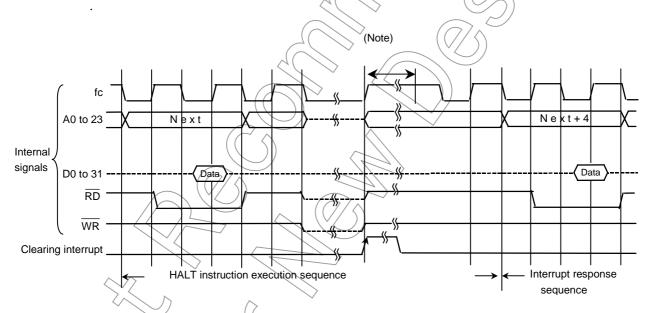

Figure 3.3.5 shows an example timing for releasing a halt state using an interrupt.

(Note); Once the halt state is released, interrupt handling starts after the oscillator startup time (tsta), warm-up time (approx. 1.6 ms) and clock multiplier settling time (approx. 1.6 ms) elapse. For details of the startup time (tsta), contact the oscillator manufacturer.

Figure 3.3.5 Timing chart for Idle3 Mode Halt state cleared by interrupt

#### 4. STOP mode

In STOP mode, all internal circuits are stopped. The pin states in STOP mode depends on the setting of WDMOD<DRVE>. Table 3.3.5 shows the states of pins in STOP mode.

The halt state in STOP mode can be released with an external interrupt using the NMI, INTO, or WUINTO to 7 pin (INTO interrupt) or a reset.

Upon released from the halt state, the system clock output starts after the high-speed oscillator warm-up time and clock multiplier settling time elapse.

The warm-up time for the high-speed oscillator is counted asing the warm-up counter within the TMP92CD54I. Once that counting ends, the device starts counting the settling time for the clock multiplier. This mechanism results in the high-speed oscillator warm-up time (1.6 ms) being included in the time required between the halt release signal being input and the system clock being output even in a system using an external oscillator that does not need oscillation settling time.

When using a reset to release a halt, ensure that the reset signal is held Low until the high-speed oscillator operates stably.

In STOP mode, the value of the RTCFC register is initialized even if the halt is released with an interrupt. It is, therefore, necessary to re-set RTCFC after releasing the halt.

(Note); Once the halt state is released, interrupt handling starts after the oscillator startup time (tsta), warm-up time (approx. 1.6 ms) and clock multiplier settling time (approx. 1.6 ms) elapse. For details of the startup time (tsta), contact the oscillator manufacturer...

Figure 3.3.6 Timing chart for Stop Mode Halt state cleared by interrupt

Table 3.3.4 Warming-up time and clock doubler stable time after clearance of Stop Mode and Idle3 Mode (@ fc=20MHz)

| Warm-up time              | 1.6 ms (2 <sup>14</sup> /f <sub>OSC</sub> ) |

|---------------------------|---------------------------------------------|

| Clock doubler stable time | 1.6 ms (2 <sup>14</sup> /f <sub>OSC</sub> ) |

|                           | $fc = 2 \times f_{osc}$                     |

Table 3.3.5 Pin states in IDLE3 and STOP Mode

| Pin Names                                                                | I/O         | <drve> = 0</drve>                                            | <drve> = 1</drve>                |  |  |  |

|--------------------------------------------------------------------------|-------------|--------------------------------------------------------------|----------------------------------|--|--|--|

| P00 to 07                                                                | Input Mode  | Inv                                                          | alid                             |  |  |  |

|                                                                          | Output Mode | Ou                                                           | tput                             |  |  |  |

|                                                                          | D0 to D7    | High-Z                                                       |                                  |  |  |  |

| P40 to 47/A0 to 7                                                        | Input Mode  | Inv                                                          | alid                             |  |  |  |

|                                                                          | Output Mode | High-Z                                                       | Output                           |  |  |  |

| P70,P71,P73 to 75/                                                       | Input Mode  | Inv                                                          | alid                             |  |  |  |

| $\overline{RD}$ , $\overline{WR}$ , $\overline{CS}$ to $\overline{WAIT}$ | Output Mode | High-Z                                                       | Output                           |  |  |  |

| P72/SI2/SCL2                                                             | Input Mode  | In                                                           | put                              |  |  |  |

|                                                                          | Output Mode | Input                                                        | Output                           |  |  |  |

| PC0 to PC5/TI0 to TO7                                                    | Input Mode  | lnv                                                          | alid                             |  |  |  |

|                                                                          | Output Mode | High-Z                                                       | Output                           |  |  |  |

| PD0 to PD7/TI8 to TOB                                                    | Input Mode  | la                                                           | put ) /                          |  |  |  |

|                                                                          | Output Mode | High-Z                                                       | Output                           |  |  |  |

|                                                                          | WUINT0 to 7 | A In                                                         | put                              |  |  |  |

| PF0 to PF7/TXD0 to RX                                                    | Input Mode  | lov                                                          | alid                             |  |  |  |

|                                                                          | Output Mode | High-Z                                                       | Output                           |  |  |  |

| PG0 to PG7/AN0 to AN7                                                    | Input Mode  | Inv                                                          | alid                             |  |  |  |

| PL0 to PL3/AN8 to AN11                                                   | Input Mode  | Inv                                                          | alid                             |  |  |  |

| PM0 to PM4                                                               | Input Mode  | Inv                                                          | alid                             |  |  |  |

| /SS to SCK2                                                              | Output Mode | High-Z                                                       | Output                           |  |  |  |

| PN0 to PN6                                                               | Input Mode  | Inv                                                          | alid                             |  |  |  |

| /SCK0 to SO2&SDA2                                                        | Output Mode | High-Z                                                       | Output                           |  |  |  |

| NMI                                                                      | Input       | \(\sqrt{\ln}\)                                               | put                              |  |  |  |

| INT0                                                                     | Input       | // In                                                        | put                              |  |  |  |

| RESET                                                                    | Input /     | In                                                           | ou <del>t</del>                  |  |  |  |

| AMO, AM1                                                                 | Input       | Inj                                                          | øut                              |  |  |  |

| TEST0, TEST1                                                             | Input       | )<br>In                                                      | put                              |  |  |  |

| X1                                                                       | Input ((    | Inv                                                          | alid                             |  |  |  |

| X2                                                                       | Output      |                                                              | l Output                         |  |  |  |

| XT1                                                                      | Input       |                                                              | (STOP)<br>RTCFC <xten>=1)</xten> |  |  |  |

| XT2                                                                      | Output      | H Level Output (STOP) Operate (IDLE3, RTCFC <xten>=1)</xten> |                                  |  |  |  |

| CLK                                                                      | Output      | H level output (CLF                                          | (MOD <clkoe>=0)</clkoe>          |  |  |  |

|                                                                          |             |                                                              | MOD <clkm1:0>=00)</clkm1:0>      |  |  |  |

|                                                                          |             | 7 of Liever Output (CL                                       | LKMOD <clkm1:0>=10)</clkm1:0>    |  |  |  |

Input : The input gate is functioning. Apply a Low or High level to prevent the input pin from floating

Output: Placed in the output state

Invalid : The input is invalid.

High-Z: High impedance.

Note) when RTCFC<XTEN>=1.

#### 3.4 Interrupts

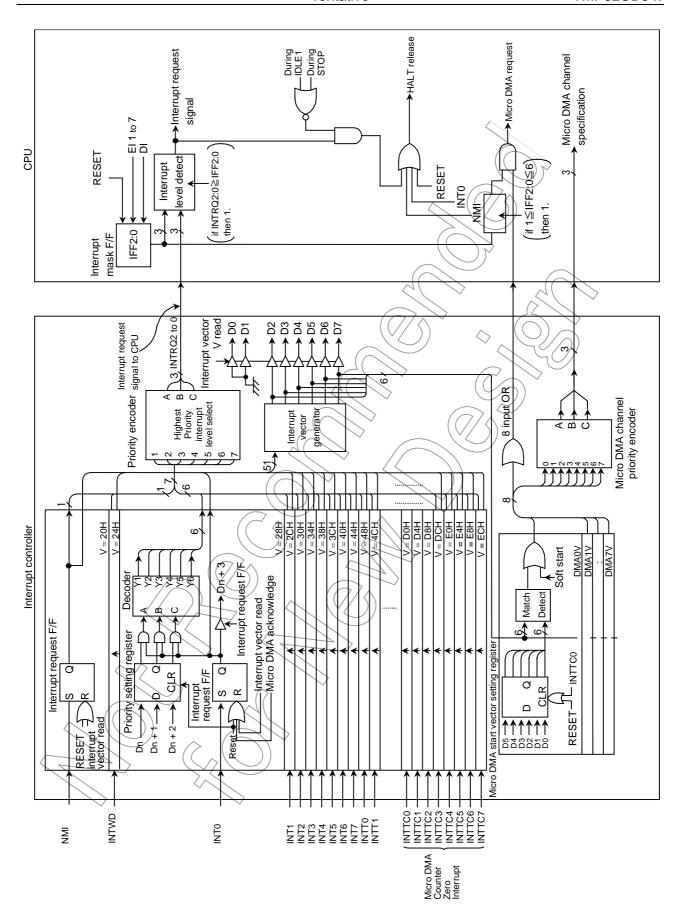

Interrupts for the TLCS-900/H1 are controlled using the CPU interrupt mask flip-flop (SR<IFF2:0>) and the interrupt controller.

The TMP92CD54I supports the following 60 interrupt sources:

Interrupts generated by CPU: 9 sources

- Software interrupts: 8 sources

- Illegal Instruction interrupt: 1 source

Internal interrupts: 42 sources

- Internal I/O interrupts: 34 sources

- Micro DMA Transfer End interrupts: 8 sources

External interrupts: 9 sources

• Interrupts on external pins (NMI, INTO to INT7)

Each interrupt source is assigned a unique interrupt vector number (fixed) and each maskable interrupt can be assigned one of six priority levels (variable). Nonmaskable interrupts have a fixed priority level of 7 (top priority).

When an interrupt occurs, the interrupt controller sends the priority level of that interrupt source to the CPU. When more than one interrupt occurs simultaneously, it sends the highest priority level to the CPU (the highest possible level is 7 for nonmaskable interrupts).

The CPU compares the sent priority level with the value in the CPU interrupt mask register (IFF2:0) and, if the priority level is higher than the interrupt mask register setting, accepts the interrupt.

Software interrupts and undefined instruction execution interrupts, however, occur independently of the IFF2:0 setting.

The value of the interrupt mask register SR<IFF2.0> can be modified using the EI instruction (EI num, where num specifies the contents of SR<IFF2.0>). For example, programming "EI 3" enables maskable interrupts having a priority level of 3 or higher, as specified with the interrupt controller, and nonmaskable interrupts to be accepted. Executing the EI or "EI 0" instruction enables all nonmaskable interrupts and maskable interrupts having a priority level of 1 or higher to be accepted. (Therefore, they are equivalent to "EI 1".)

The DI instruction (specifying 7 for SR<IFF2:0>) is functionally equivalent to "EI 7" and used to disable the acceptance of maskable interrupts because they have priority levels of 0 to 6. The EI instruction is effective immediately after it is executed.

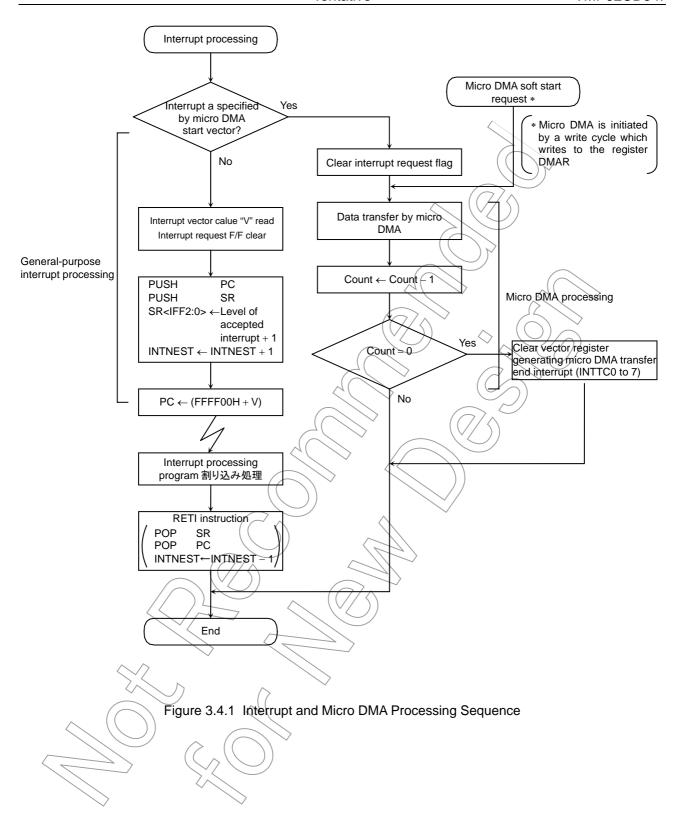

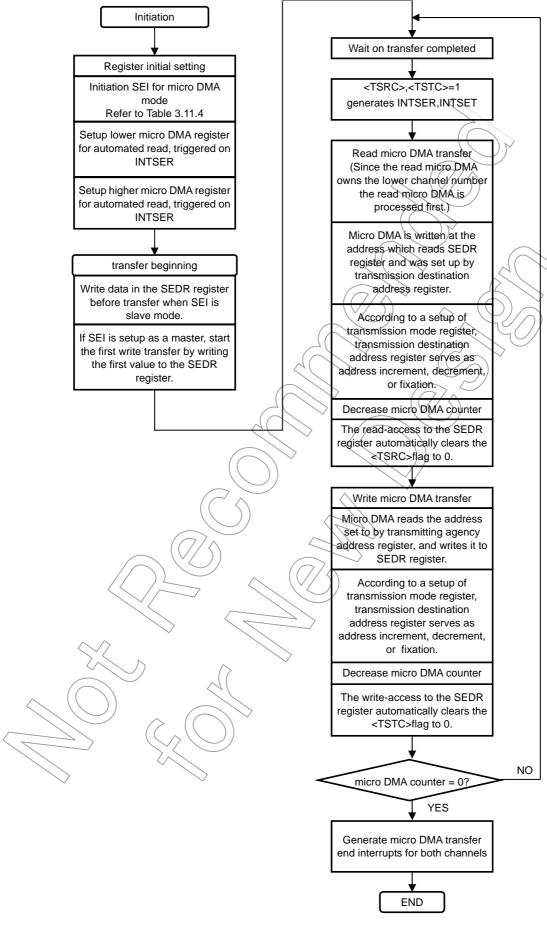

Interrupts for the TLCS-900/H1 also supports micro DMA handling mode in addition to the general-purpose interrupt handling mode described above. In micro DMA mode, the CPU automatically transfers data (1, 2, or 4 bytes). It enables fast data transfer to internal/external memory and built-in I/O.

Moreover, the TMP92CD54P supports a soft start function, which enables software to issue a micro DMA request, rather than given from an interrupt source.

Figure 3.4.1 shows the entire interrupt handling flow.

#### 3.4.1 General-purpose interrupt handling

When the CPU accepts an interrupt, it performs the following operation. For software interrupts issued by the CPU and undefined instruction execution interrupts, the CPU only performs steps (2), (4), and (5) without executing steps (1) and (3). The following steps are similar to those for the TLCS-900/L, TLCS-900/H, TLCS-900/L1, and TLCS-900/H2.

- (1) The CPU reads an interrupt vector from the interrupt controller.

If two or more interrupts having the same priority level occur simultaneously, the CPU issues an interrupt vector according to the default priorities (fixed: smaller vector values have higher priority) and clears the interrupt request.

- (2) The CPU pushes the program counter (PC) and status register (SR) into the stack area (pointed to by XSP).

- (3) Set the CPU interrupt mask register SR<IFF2:0> to the value of the accepted interrupt level plus one. If the value is 7, however, the value of 7 is set without being incremented.

- (4) Increment the interrupt nesting counter INTNEST by one.

- (5) The CPU jumps to the address indicated with the data at address (FFFF00H + interrupt vector) and then starts the interrupt handling routine.

Upon the completion of interrupt handling, usually use the RETL instruction to return to the main routine. This instruction restores the values of the program counter (PC) and status register (SR) from the stack and then decrement the interrupt nesting counter (INTNEST) by one.

The acceptance of nonmaskable interrupts cannot be disabled programmatically. On the other hand, maskable interrupts can be enabled or disabled programmatically and can be assigned priorities for each interrupt source (an interrupt level of 0 or 7 disables the interrupt request). The CPU accepts an interrupt if the priority level of the interrupt request is higher than the value of its interrupt mask register SR</FF2:0>. It then sets the mask register <IFF2:0> to the value of the accepted priority plus one. Therefore, if any interrupt having a priority higher than the interrupt currently being handled occurs, the CPU accepts that interrupt request, resulting in interrupt handling being nested.

If another interrupt request is issued while the CPU is performing steps (1) to (5) above for an interrupt it has accepted, the new interrupt request is sampled immediately after the first instruction of the interrupt handling routine is executed. The DI instruction can be used as the first instruction to prohibit the nesting of maskable interrupts.

Upon a reset, the CPU mask register SR<IFF2:0> is initialized to 7, which disables maskable interrupts.

In the TMP92CD54I, memory addresses FFFF00H to FFFFEFH (240 bytes) are assigned to the interrupt vector area. Table 3.4.1 shows the interrupt table.

Table 3.4.1 TMP92CD54I Interrupt Vectors and Micro DMA Start Vectors

| Default<br>Priority | Туре      | Interrupt Source and Source of Micro DMA Request | Vector Value   | Address refer to<br>Vector | Micro DMA<br>Start Vector |

|---------------------|-----------|--------------------------------------------------|----------------|----------------------------|---------------------------|

| 1                   |           | Reset or [SWI0] instruction                      | 0000H          | FFFF00H                    | Olari Polici              |

| 2                   |           | [SWI1] instruction                               | 0004H          | FFFF04H                    |                           |

| 3                   |           | Illegal instruction or [SWI2] instruction        | 0008H          | ⟨FFFF08H                   |                           |

| 4                   |           | [SWI3] instruction                               | 000CH          | FFEF0CH                    |                           |

|                     | Non       | [SWI4] instruction                               | 0010H          | FFFF10H                    |                           |

|                     | Maskable  | [SWI5] instruction                               | 0014H          | FPEF14H                    |                           |

| 7                   |           | [SWI6] instruction                               | 0014I1         | FFFF18H                    |                           |

| 8                   |           | [SWI7] instruction                               | 0616H          | FFFF1CH                    |                           |

| 9                   |           | NMI: pin input                                   | 0020H          | FFFF20H                    |                           |

| 10                  |           | INTWD: Watchdog Timer                            | 0020H          | FFFF24H                    |                           |

| -                   |           | Micro DMA                                        | 0024(1         | y 1 1 1 2 <del>4</del> 1 1 | _                         |

| 11                  |           | INT0: INT0 pin input (Note2)                     | 0028H          | FFFF28H                    | 0AH                       |

| 12                  |           |                                                  | 0026H          | FFFF2CH                    | 0BH                       |

|                     |           | INT1: INT1 pin input                             |                | 2//                        |                           |

| 13                  |           | INT2: INT2 pin input                             | 0030H<br>0034H | FFFF30H<br>FFFF34H         | 0CH<br>0DH                |

|                     |           | INT3: INT3 pin input                             | //             |                            |                           |

| 15                  |           | INT4: INT4 pin input                             | 0038H          | FFFF38H                    | 0EH                       |

| 16                  |           | INT5: INT5 pin input                             | 003CH          | EFFF3CH                    | 0FH                       |

| 17                  |           | INT6: INT6 pin input                             | 0040H          | FFFF40H<br>FFFF44H         | 10H                       |

| 18                  |           | INT7: INT7 pin input                             | 0044H          | 7-7/                       | 11H                       |

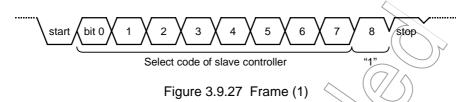

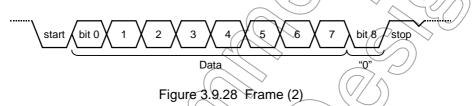

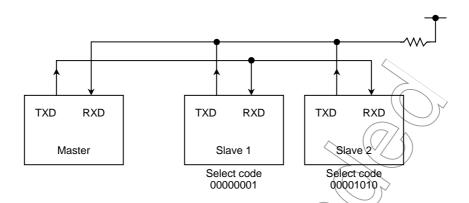

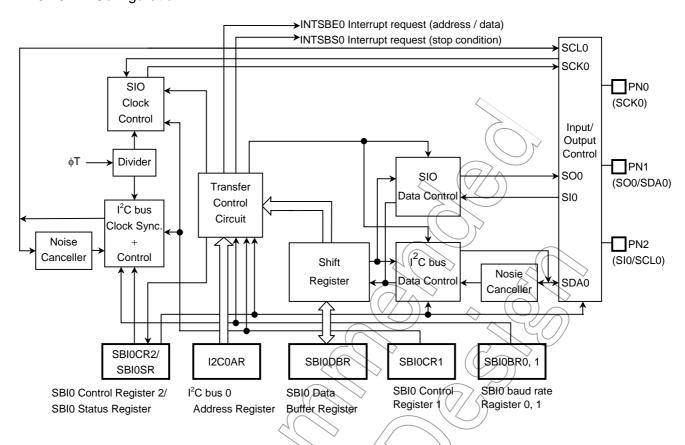

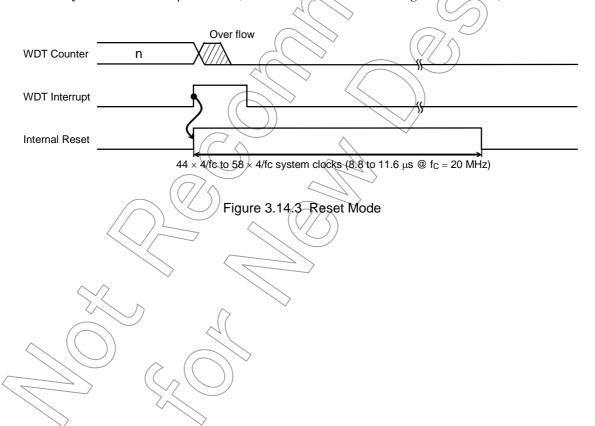

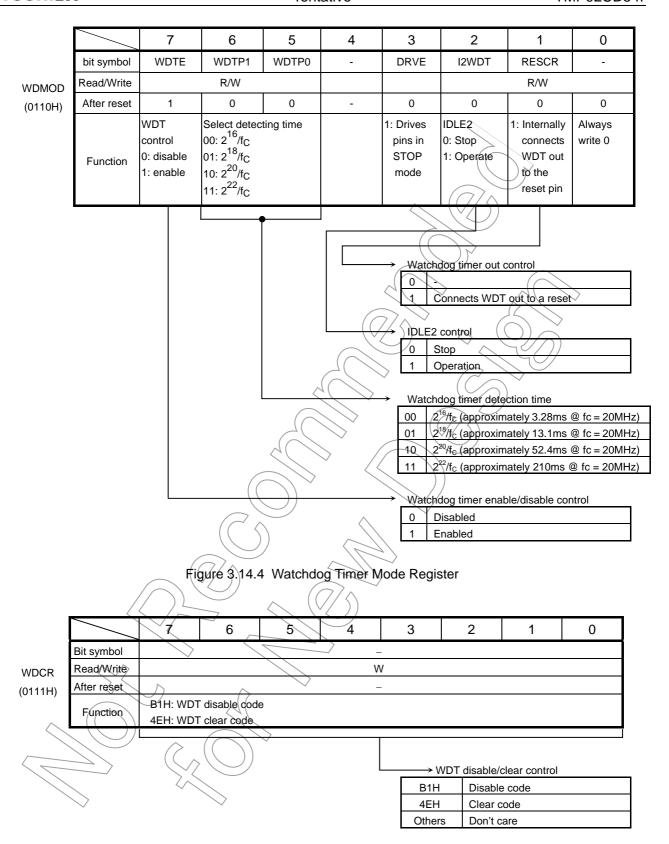

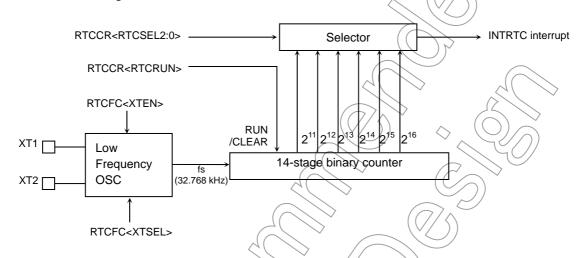

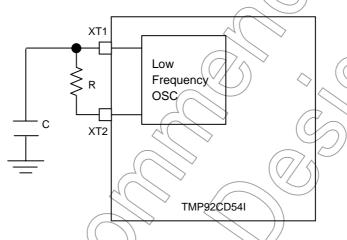

| 19                  |           | INTTO: 8-bit timer 0                             | 0048H          | FFFF48H                    | 12H                       |