## **CPRI and 10G Ethernet Data Recovery IC** with Amp/EQ from 614.4 Mbps to 10.3125 Gbps

**Data Sheet**

# ADN2905

### **FEATURES**

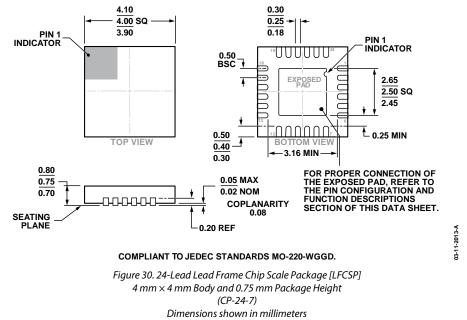

#### Serial CPRI data rates 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps, 3.072 Gbps, 4.9152 Gbps, 6.144 Gbps, and 9.8304 Gbps Ethernet data rates: 1.25 Gbps and 10.3125 Gbps No reference clock required Jitter performance superior to the SFF-8431 litter specifications Optional equalizer or 0 dB EQ input mode Quantizer sensitivity: 200 mV p-p typical (equalizer mode) Sample phase adjust (5.65 Gbps or greater) **Output polarity invert** I<sup>2</sup>C to access optional features Loss of lock (LOL) indicator **PRBS** generator/detector **Application aware power** 349.5 mW at 9.8304 Gbps, 0 dB EQ input mode 287.7 mW at 6.144 Gbps, 0 dB EQ input mode 249.3 mW at 3.072 Gbps, 0 dB EQ input mode Power supply: 1.2 V, flexible 1.8 V to 3.3 V, and 3.3 V 4 mm × 4 mm, 24-lead LFCSP

### **APPLICATIONS**

SFF-8431-compatible Ethernet: 10GE, 1GE, and CPRI: OS/L.6 up to OS/L.96

### **GENERAL DESCRIPTION**

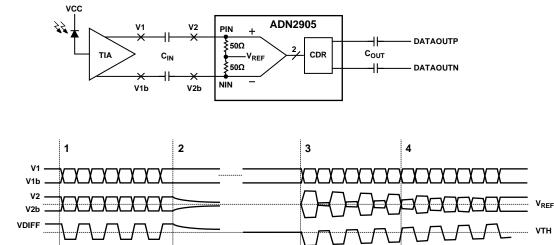

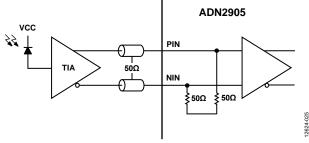

The ADN2905 provides the receiver functions of quantization and multirate data recovery at 614.4 Mbps, 1.2288 Gbps, 1.25 Gbps, 2.4576 Gbps, 3.072 Gbps, 4.9152 Gbps, 6.144 Gbps, 9.8304 Gbps, and 10.3125 Gbps, used in Common Public Radio Interface (CPRI) and gigabit Ethernet applications. The ADN2905 automatically locks to all the specified CPRI and Ethernet data rates without the need for an external reference clock or programming. The ADN2905 jitter performance exceeds the jitter requirement specified by SFF-8431.

The ADN2905 provides manual sample phase adjustment. Additionally, the user can select an equalizer or a 0 dB EQ as the input. The equalizer is either adaptive or can be manually set.

The ADN2905 also supports pseudorandom binary sequence (PRBS) generation, bit error detection, and input data rate readback features.

The ADN2905 is available in a compact 4 mm × 4 mm, 24-lead chip scale package (LFCSP). All ADN2905 specifications are defined over the ambient temperature range of -40°C to +85°C, unless otherwise noted.

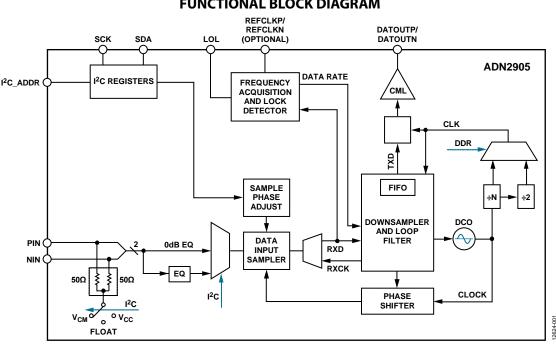

## FUNCTIONAL BLOCK DIAGRAM

#### Rev. A

Figure 1.

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014–2016 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

## TABLE OF CONTENTS

| Features                                                                |

|-------------------------------------------------------------------------|

| Applications1                                                           |

| General Description                                                     |

| Functional Block Diagram1                                               |

| Revision History                                                        |

| Specifications                                                          |

| Jitter Specifications                                                   |

| Output and Timing Specifications                                        |

| Timing Diagrams6                                                        |

| Absolute Maximum Ratings7                                               |

| Thermal Characteristics7                                                |

| ESD Caution7                                                            |

| Pin Configuration and Function Descriptions                             |

| Typical Performance Characteristics                                     |

| I <sup>2</sup> C Interface Timing and Internal Register Descriptions 10 |

| Register Map11                                                          |

## **REVISION HISTORY**

| 1/16—Rev 0. to Rev. A      |  |

|----------------------------|--|

| Changes to Figure 5        |  |

| Updated Outline Dimensions |  |

| Changes to Ordering Guide  |  |

#### 12/14—Revision 0: Initial Version

| Theory of Operation                                              | 15 |

|------------------------------------------------------------------|----|

| Functional Description                                           | 17 |

| Frequency Acquisition                                            | 17 |

| Edge Select                                                      | 17 |

| Passive Equalizer                                                | 18 |

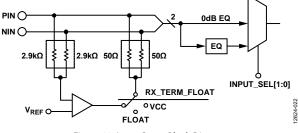

| 0 dB EQ                                                          | 18 |

| Lock Detector Operation                                          | 18 |

| Harmonic Detector                                                | 19 |

| Output Disable and Squelch                                       | 19 |

| I <sup>2</sup> C Interface                                       | 20 |

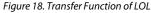

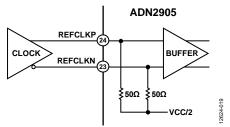

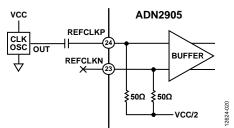

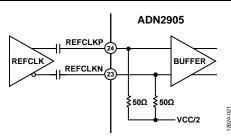

| Reference Clock (Optional)                                       | 20 |

| Additional Features Available via the I <sup>2</sup> C Interface | 22 |

| Input Configurations                                             | 24 |

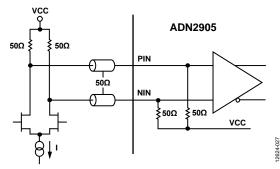

| DC-Coupled Application                                           | 26 |

| Outline Dimensions                                               | 27 |

| Ordering Guide                                                   | 27 |

## SPECIFICATIONS

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $VCC = VCC_{MIN}$  to  $VCC_{MAX}$ ,  $VCC1 = VCC1_{MIN}$  to  $VCC1_{MAX}$ ,  $VDD = VDD_{MIN}$  to  $VDD_{MAX}$ , VEE = 0 V, input data pattern = PRBS  $2^{23} - 1$ , ac-coupled (to 100  $\Omega$  differential termination load), I<sup>2</sup>C register default settings, unless otherwise noted.

| Parameter                                                          | Test Conditions/Comments                                                                           | Min    | Тур   | Max        | Unit  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|------------|-------|

| MULTIRATE SUPPORT RANGE                                            |                                                                                                    | 0.6144 |       | 10.3125    | Gbps  |

| INPUT—DC CHARACTERISTICS                                           |                                                                                                    |        |       |            |       |

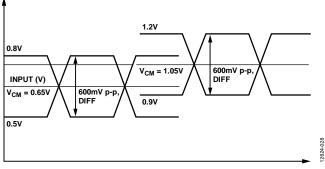

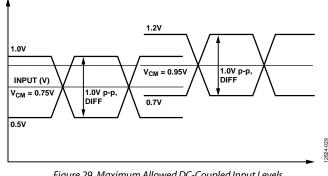

| Peak-to-Peak Differential Input                                    | PIN – NIN, see Figure 29                                                                           |        |       | 1.0        | v     |

| Input Resistance                                                   | Differential                                                                                       | 95     | 100   | 105        | Ω     |

| 0 dB EQ INPUT—CML COMPLIANT                                        |                                                                                                    |        |       |            |       |

| Input Voltage Range                                                | At PIN or NIN, dc-coupled, RX_TERM_FLOAT = 1<br>(floated)                                          | 0.5    |       | VCC        | V     |

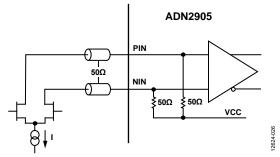

| Input Common-Mode Level                                            | DC-coupled (see Figure 28), 600 mV p-p differential,<br>RX_TERM_FLOAT = 1 (floated)                | 0.65   |       | VCC – 0.15 | V     |

| Differential Input Sensitivity                                     |                                                                                                    |        |       |            |       |

| CPRI × 16, 9.8304 Gbps                                             | AC-coupled, RX_TERM_FLOAT = 0 ( $V_{CM}$ = 1.2 V), bit<br>error rate (BER) = 1 × 10 <sup>-12</sup> |        | 250   |            | mV p- |

| EQUALIZER INPUT PATH                                               |                                                                                                    |        |       |            |       |

| Differential Input Sensitivity                                     | 15 inch FR-4, 100 $\Omega$ differential transmission line, adaptive EQ on                          |        |       |            |       |

| CPRI × 16, 9.8304 Gbps                                             | $BER = 1 \times 10^{-12}$                                                                          |        | 200   |            | mV p- |

| INPUT—AC CHARACTERISTICS                                           |                                                                                                    |        |       |            |       |

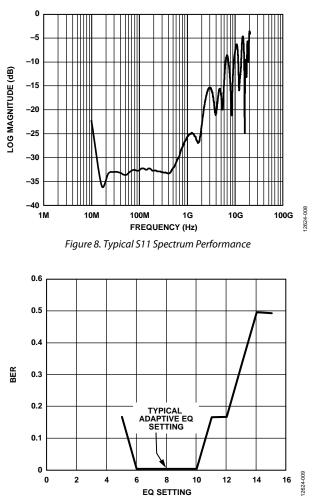

| S11                                                                | At 7.5 GHz, differential return loss, see Figure 8                                                 |        | -12   |            | dB    |

| LOSS OF LOCK (LOL) DETECT                                          |                                                                                                    |        |       |            |       |

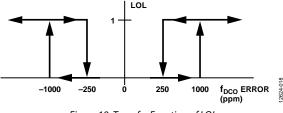

| Digital Control Oscillator (DCO)<br>Frequency Error for LOL Assert | With respect to nominal, data collected in lock to reference (LTR) mode                            |        | 1000  |            | ppm   |

| DCO Frequency Error for LOL Deassert                               | With respect to nominal, data collected in LTR mode                                                |        | 250   |            | ppm   |

| LOL Assert Response Time                                           | 2.4576 Gbps                                                                                        |        | 51    |            | μs    |

|                                                                    | 9.8304 Gbps                                                                                        |        | 18    |            | μs    |

| ACQUISITION TIME                                                   |                                                                                                    |        |       |            |       |

| Lock to Data (LTD) Mode                                            | 2.4576 Gbps                                                                                        |        | 0.5   |            | ms    |

|                                                                    | 9.8304 Gbps                                                                                        |        | 0.5   |            | ms    |

| Optional LTR Mode <sup>1</sup>                                     |                                                                                                    |        | 6.0   |            | ms    |

| DATA RATE READBACK ACCURACY                                        |                                                                                                    |        |       |            |       |

| Coarse Readback                                                    |                                                                                                    |        | ±5    |            | %     |

| Fine Readback                                                      | In addition to reference clock accuracy                                                            |        | ±100  |            | ppm   |

| POWER SUPPLY VOLTAGE                                               |                                                                                                    |        |       |            |       |

| VCC                                                                |                                                                                                    | 1.14   | 1.2   | 1.26       | V     |

| VDD                                                                |                                                                                                    | 2.97   | 3.3   | 3.63       | V     |

| VCC1                                                               |                                                                                                    | 1.62   | 1.8   | 3.63       | V     |

| POWER SUPPLY CURRENT                                               | 0 dB EQ input mode, clock output disabled                                                          |        |       |            |       |

| VCC                                                                | 2.4576 Gbps                                                                                        |        | 182.0 |            | mA    |

|                                                                    | 3.072 Gbps                                                                                         |        | 159.1 |            | mA    |

|                                                                    | 4.9152 Gbps                                                                                        |        | 180.8 |            | mA    |

|                                                                    | 6.144 Gbps                                                                                         |        | 190.5 |            | mA    |

|                                                                    | 9.8304 Gbps                                                                                        |        | 217.3 |            | mA    |

| VDD                                                                | 2.4576 Gbps                                                                                        |        | 8.6   |            | mA    |

|                                                                    | 3.072 Gbps                                                                                         |        | 9.0   |            | mA    |

|                                                                    | 4.9152 Gbps                                                                                        |        | 8.8   |            | mA    |

|                                                                    | 6.144 Gbps                                                                                         |        | 8.9   |            | mA    |

|                                                                    | 9.8304 Gbps                                                                                        |        | 9.1   |            | mA    |

| Parameter                   | Test Conditions/Comments                  | Min | Тур   | Max | Unit |

|-----------------------------|-------------------------------------------|-----|-------|-----|------|

| VCC1                        | 2.4576 Gbps                               |     | 31.7  |     | mA   |

|                             | 3.072 Gbps                                |     | 16.2  |     | mA   |

|                             | 4.9152 Gbps                               |     | 31.8  |     | mA   |

|                             | 6.144 Gbps                                |     | 16.1  |     | mA   |

|                             | 9.8304 Gbps                               |     | 32.8  |     | mA   |

| TOTAL POWER DISSIPATION     | 0 dB EQ input mode, clock output disabled |     |       |     |      |

|                             | 2.4576 Gbps                               |     | 305.7 |     | mW   |

|                             | 3.072 Gbps                                |     | 249.3 |     | mW   |

|                             | 4.9152 Gbps                               |     | 304.5 |     | mW   |

|                             | 6.144 Gbps                                |     | 287.7 |     | mW   |

|                             | 9.8304 Gbps                               |     | 349.5 |     | mW   |

| OPERATING TEMPERATURE RANGE |                                           | -40 |       | +85 | °C   |

<sup>1</sup> This typical acquisition specification applies to all selectable reference clock frequencies in the range of 11.05 MHz to 176.8 MHz.

### JITTER SPECIFICATIONS

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $VCC = VCC_{MIN}$  to  $VCC_{MAX}$ ,  $VCC1 = VCC1_{MIN}$  to  $VCC1_{MAX}$ ,  $VDD = VDD_{MIN}$  to  $VDD_{MAX}$ , VEE = 0 V, input data pattern = PRBS  $2^{23} - 1$ , ac-coupled to 100  $\Omega$  differential termination load,  $I^2C$  register default settings, unless otherwise noted.

| Table 2.                                |        |                                                    |     |      |     |      |  |  |  |

|-----------------------------------------|--------|----------------------------------------------------|-----|------|-----|------|--|--|--|

| Parameter                               | Symbol | Test Conditions/Comments                           | Min | Тур  | Max | Unit |  |  |  |

| TRANSMITTER JITTERS                     |        |                                                    |     |      |     |      |  |  |  |

| Deterministic Jitter                    | T_DJ   | CPRI = 9.8304 Gbps, K28.5 + D5.6 and K28.5 + D16.2 |     | 6.98 |     | ps   |  |  |  |

| Random Jitter                           | T_RJ   | CPRI = 9.8304 Gbps, K28.5 + D5.6 and K28.5 + D16.2 |     | 0.36 |     | ps   |  |  |  |

| Duty Cycle Distortion                   | T_DCD  | CPRI = 9.8304 Gbps, K28.5 + D5.6 and K28.5 + D16.2 |     | 0.57 |     | ps   |  |  |  |

| Total Jitter                            | ΤJ     | SFF-8431, 64B/66B, 10.3125 Gbps                    |     | 13.6 |     | ps   |  |  |  |

| Data Dependent Jitter                   | DDJ    | SFF-8431, PRBS 2 <sup>9</sup> – 1, 10.3125 Gbps    |     | 7.37 |     | ps   |  |  |  |

| Data Dependent Pulse<br>Width Shrinkage | DDPWS  | SFF-8431, PRBS 2 <sup>9</sup> – 1, 10.3125 Gbps    |     | 4.58 |     | ps   |  |  |  |

| Uncorrelated Jitter                     | UJ     | SFF-8431, 64B/66B, 10.3125 Gbps                    |     | 0.14 |     | ps   |  |  |  |

| RECEIVER JITTERS                        |        |                                                    |     |      |     |      |  |  |  |

| Total Jitter Tolerance                  | TLT    | SFF-8431, 10.3125 Gbps                             |     | 82.4 |     | ps   |  |  |  |

| 99% Jitter                              | J2     | SFF-8431, 10.3125 Gbps                             |     | 55.5 |     | ps   |  |  |  |

| Data Dependent Pulse<br>Width Shrinkage | DDPWS  | SFF-8431, 10.3125 Gbps                             |     | 33.7 |     | ps   |  |  |  |

### **OUTPUT AND TIMING SPECIFICATIONS**

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $VCC = VCC_{MIN}$  to  $VCC_{MAX}$ ,  $VCC1 = VCC1_{MIN}$  to  $VCC1_{MAX}$ ,  $VDD = VDD_{MIN}$  to  $VDD_{MAX}$ , VEE = 0 V, input data pattern = PRBS  $2^{23} - 1$ , ac-coupled to 100  $\Omega$  differential termination load, I<sup>2</sup>C register default settings, unless otherwise noted.

| Parameter                                   | Symbol                         | Test Conditions/Comments                                                                     | Min           | Тур            | Max   | Unit   |

|---------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------|---------------|----------------|-------|--------|

|                                             | Symbol                         |                                                                                              | 14111         | אני            | IVICA | Unit   |

| CML OUTPUT CHARACTERISTICS                  |                                |                                                                                              | 525           | 600            | (7)   |        |

| Data Differential Output Swing              |                                | 9.8304 Gbps, DATA_SWING[3:0] = 0xC (default)                                                 | 535           | 600            | 672   | mV p-p |

|                                             |                                | 9.8304 Gbps, DATA_SWING[3:0] = $0xF$ (maximum)                                               | 668           | 724            | 771   | mV p-p |

|                                             |                                | 9.8304 Gbps, DATA_SWING[3:0] = 0x4 (minimum)                                                 | 189           | 219            | 252   | mV p-p |

| Output Voltage                              |                                |                                                                                              |               |                |       |        |

| High V <sub>OH</sub>                        |                                | DC-coupled                                                                                   | VCC –<br>0.05 | VCC -          | VCC   | V      |

| Low                                         | V                              | DC coupled                                                                                   | 0.05<br>VCC – | 0.025<br>VCC – | VCC – | V      |

| Low                                         | V <sub>OL</sub>                | DC-coupled                                                                                   | 0.36          | 0.325          | 0.29  | V      |

| CML OUTPUT TIMING CHARACTERISTICS           |                                |                                                                                              | 0.50          | 0.525          | 0.29  |        |

| Rise Time                                   |                                | 20% to 80%, at 9.8304 Gbps, DATOUTN/DATOUTP                                                  | 17.4          | 32.6           | 46.5  | ps     |

| Rise fille                                  |                                | 20% to 80%, at 9.8304 Gbps, DATOUTIV/DATOUTIV<br>20% to 80%, at 9.8304 Gbps, CLKOUTN/CLKOUTP | 22.2          | 28.3           | 33.1  | -      |

| Fall Time                                   |                                |                                                                                              | 17.5          | 20.5<br>33     |       | ps     |

| Fail Time                                   |                                | 80% to 20%, at 9.8304 Gbps, DATOUTN/DATOUTP                                                  |               |                | 49.1  | ps     |

|                                             |                                | 80% to 20%, at 9.8304 Gbps, CLKOUTN/CLKOUTP                                                  | 23.9          | 29.2           | 33.7  | ps     |

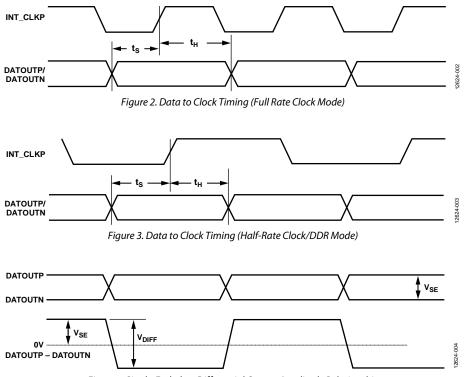

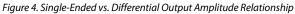

| Setup Time, Full Rate Clock                 | t <sub>s</sub>                 | See Figure 2                                                                                 |               | 0.5            |       | UI     |

| Hold Time, Full Rate Clock                  | t <sub>H</sub>                 | See Figure 2                                                                                 |               | 0.5            |       | UI     |

| Setup Time, DDR Mode                        | ts                             | See Figure 3                                                                                 |               | 0.5            |       | UI     |

| Hold Time, DDR Mode                         | t <sub>H</sub>                 | See Figure 3                                                                                 |               | 0.5            |       | UI     |

| <sup>2</sup> C INTERFACE DC CHARACTERISTICS |                                | LVTTL                                                                                        |               |                |       |        |

| Input Voltage                               |                                |                                                                                              |               |                |       |        |

| High                                        | VIH                            |                                                                                              | 2.0           |                |       | V      |

| Low                                         | V <sub>IL</sub>                |                                                                                              |               |                | 0.8   | V      |

| Input Current                               |                                | $V_{IN} = 0.1 \times VDD \text{ or } V_{IN} = 0.9 \times VDD$                                | -10.0         |                | +10.0 | μΑ     |

| Output Low Voltage                          | V <sub>OL</sub>                | $I_{OL} = 3.0 \text{ mA}$                                                                    |               |                | 0.4   | V      |

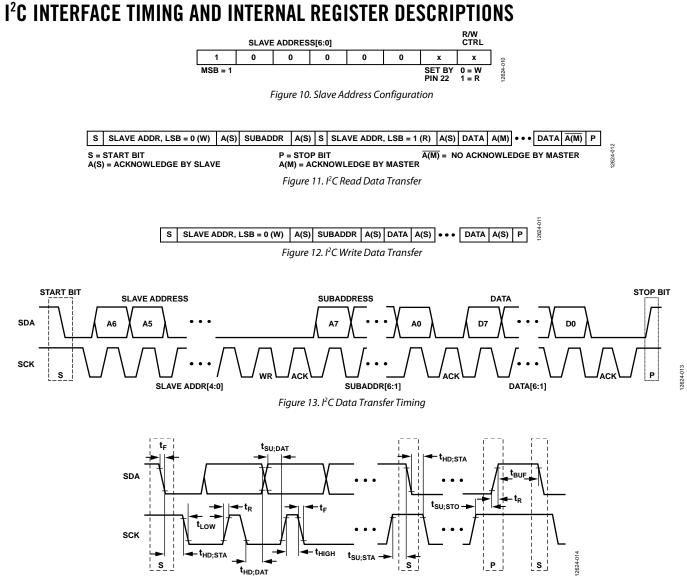

| I <sup>2</sup> C INTERFACE TIMING           |                                | See Figure 14                                                                                |               |                |       |        |

| SCK Clock Frequency                         |                                |                                                                                              |               |                | 400   | kHz    |

| SCK Pulse Width High                        | t <sub>HIGH</sub>              |                                                                                              | 600           |                |       | ns     |

| SCK Pulse Width Low                         | t <sub>LOW</sub>               |                                                                                              | 1300          |                |       | ns     |

| Start Condition Hold Time                   | t <sub>HD;STA</sub>            |                                                                                              | 600           |                |       | ns     |

| Start Condition Setup Time                  | t <sub>su;sta</sub>            |                                                                                              | 600           |                |       | ns     |

| Data Setup Time                             | t <sub>su;DAT</sub>            |                                                                                              | 100           |                |       | ns     |

| Data Hold Time                              | t <sub>HD;DAT</sub>            |                                                                                              | 300           |                |       | ns     |

| SCK/SDA Rise/Fall Time <sup>1</sup>         | t <sub>R</sub> /t <sub>F</sub> |                                                                                              | 20 +          |                | 300   | ns     |

|                                             | •R/ •F                         |                                                                                              | 0.1Cb         |                |       |        |

| Stop Condition Setup Time                   | t <sub>su;sto</sub>            |                                                                                              | 600           |                |       | ns     |

| Bus Free Time Between Stop and              | t <sub>BUF</sub>               |                                                                                              | 1300          |                |       | ns     |

| Start Conditions                            | 501                            |                                                                                              |               |                |       |        |

| LVTTL DC INPUT CHARACTERISITICS             |                                |                                                                                              |               |                |       |        |

| (I <sup>2</sup> C_ADDR)                     |                                |                                                                                              |               |                |       |        |

| Input Voltage                               |                                |                                                                                              |               |                |       |        |

| High                                        | V <sub>IH</sub>                |                                                                                              | 2.0           |                |       | V      |

| Low                                         | VIL                            |                                                                                              |               |                | 0.8   | V      |

| Input Current                               |                                |                                                                                              |               |                |       |        |

| High                                        | I <sub>IH</sub>                | $V_{IN} = 2.4 V$                                                                             |               |                | 5     | μΑ     |

| Low                                         | I <sub>IL</sub>                | $V_{IN} = 0.4 V$                                                                             | -5            |                |       | μA     |

| LVTTL DC OUTPUT CHARACTERISITICS            | 1                              |                                                                                              |               |                |       | 1      |

| (LOS/LOL)                                   |                                |                                                                                              |               |                |       |        |

| Output Voltage                              |                                |                                                                                              |               |                |       |        |

| High                                        | V <sub>OH</sub>                | I <sub>он</sub> = 2.0 mA                                                                     | 2.4           |                |       | v      |

| Low                                         | V <sub>OL</sub>                | $I_{OL} = -2.0 \text{ mA}$                                                                   |               |                | 0.4   | v      |

## **Data Sheet**

| Parameter                                   | Symbol          | Test Conditions/Comments                                           | Min   | Тур | Мах   | Unit   |

|---------------------------------------------|-----------------|--------------------------------------------------------------------|-------|-----|-------|--------|

| REFERENCE CLOCK CHARACTERISTICS             |                 | Optional LTR mode                                                  |       |     |       |        |

| Input Compliance Voltage (Single-<br>Ended) | V <sub>CM</sub> | No input offset, no input current, see Figure 21, ac-coupled input | 0.55  |     | 1.0   | V      |

| Minimum Differential Input Drive            |                 | See Figure 21, ac-coupled, differential input                      |       | 100 |       | mV p-p |

| Reference Frequency                         |                 |                                                                    | 11.05 |     | 176.8 | MHz    |

| Required Accuracy <sup>2</sup>              |                 | AC-coupled, differential input                                     |       | 100 |       | ppm    |

<sup>1</sup> C<sub>b</sub> is the total capacitance of one bus line in picofarads (pF). If mixed with high speed (HS) mode devices, faster rise/fall times are allowed (refer to the Philips *I*<sup>2</sup>*C Bus Specification*, Version 2.1).

<sup>2</sup> Required accuracy in dc-coupled mode is guaranteed by design as long as the clock common-mode voltage output matches the reference clock commonmode voltage range.

### **TIMING DIAGRAMS**

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| 1 4010 1.                                               |                 |

|---------------------------------------------------------|-----------------|

| Parameter                                               | Rating          |

| Supply Voltage (VCC = 1.2 V)                            | 1.26 V          |

| Supply Voltage (VDD and VCC1 = 3.3 V)                   | 3.63 V          |

| Maximum Input Voltage (REFCLKP/REFCLKN,<br>NIN/PIN)     | 1.26 V          |

| Minimum Input Voltage (REFCLKP/REFCLKN,<br>NIN/PIN)     | VEE- 0.4 V      |

| Maximum Input Voltage (SDA, SCK, I <sup>2</sup> C_ADDR) | 3.63 V          |

| Minimum Input Voltage (SDA, SCK, I <sup>2</sup> C_ADDR) | VEE - 0.4 V     |

| Maximum Junction Temperature                            | 125°C           |

| Storage Temperature Range                               | –65°C to +150°C |

| Lead Temperature (Soldering, 10 sec)                    | 300°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

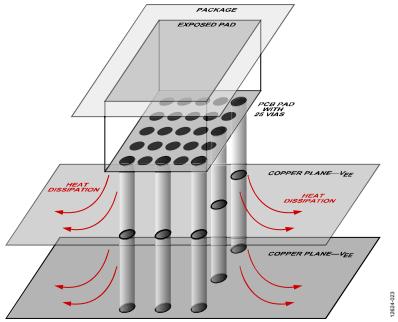

### THERMAL CHARACTERISTICS

#### **Thermal Resistance**

Thermal resistance is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages, for a 4-layer board with the exposed paddle soldered to VEE.

#### Table 5. Thermal Resistance

| Package Type  | $\theta_{JA}^{1}$ | $\theta_{JB}^{2}$ | $\theta_{JC}^{3}$ | Unit |

|---------------|-------------------|-------------------|-------------------|------|

| 24-Lead LFCSP | 45                | 5                 | 11                | °C/W |

<sup>1</sup> Junction to ambient.

<sup>2</sup> Junction to base.

<sup>3</sup> Junction to case.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

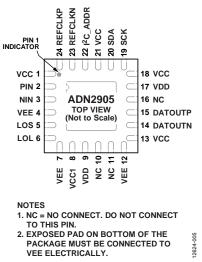

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

#### **Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic              | Type <sup>1</sup> | Description                                                                                                                                           |

|---------|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC                   | Р                 | 1.2 V Supply for Limiting Amplifier.                                                                                                                  |

| 2       | PIN                   | AI                | Positive Differential Data Input (CML).                                                                                                               |

| 3       | NIN                   | AI                | Negative Differential Data Input (CML).                                                                                                               |

| 4       | VEE                   | Р                 | Ground for Limiting Amplifier.                                                                                                                        |

| 5       | LOS                   | DO                | Loss of Signal Output (Active High).                                                                                                                  |

| 6       | LOL                   | DO                | Loss of Lock Output (Active High).                                                                                                                    |

| 7       | VEE                   | Р                 | Digital Control Oscillator (DCO) Ground.                                                                                                              |

| 8       | VCC1                  | Р                 | 1.8 V to 3.3 V DCO Supply.                                                                                                                            |

| 9       | VDD                   | Р                 | 3.3 V High Supply.                                                                                                                                    |

| 10      | NC                    | N/A               | No Connect. Do not connect to this pin. Leave this pin floating                                                                                       |

| 11      | NC                    | N/A               | No Connect. Do not connect to this pin. Leave this pin floating                                                                                       |

| 12      | VEE                   | Р                 | Ground for CML Output Drivers.                                                                                                                        |

| 13      | VCC                   | Р                 | 1.2 V Supply for CML Output Drivers.                                                                                                                  |

| 14      | DATOUTN               | DO                | Negative Differential Retimed Data Output (CML).                                                                                                      |

| 15      | DATOUTP               | DO                | Positive Differential Retimed Data Output (CML).                                                                                                      |

| 16      | NC                    | DI                | No Connect. Tie this pin to VEE (ground).                                                                                                             |

| 17      | VDD                   | Р                 | 3.3 V High Supply.                                                                                                                                    |

| 18      | VCC                   | Р                 | 1.2 V Core Digital Supply.                                                                                                                            |

| 19      | SCK                   | DI                | Clock for I <sup>2</sup> C.                                                                                                                           |

| 20      | SDA                   | DIO               | Bidirectional Data for I <sup>2</sup> C.                                                                                                              |

| 21      | VCC                   | Р                 | 1.2 V Core Supply.                                                                                                                                    |

| 22      | I <sup>2</sup> C_ADDR | DI                | $I^2C$ Address Setting. Sets the device $I^2C$ address to 0x80 when $I^2C\_ADDR = 0$ . Sets the device $I^2C$ address to 0x82 when $I^2C\_ADDR = 1$ . |

| 23      | REFCLKN               | DI                | Negative Reference Clock Input (Optional).                                                                                                            |

| 24      | REFCLKP               | DI                | Positive Reference Clock Input (Optional).                                                                                                            |

| N/A     | EPAD                  | Р                 | Exposed Pad (VEE). The exposed pad on the bottom of the device package must be connected to VEE electrically. The exposed pad works as a heat sink.   |

<sup>1</sup> P is power, AI is analog input, DI is digital input, DO is digital output, DIO is digital input/output, and N/A is not applicable.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}C$ , VCC = 1.2 V, VCC1 = 1.8 V, VDD = 3.3 V, VEE = 0 V, input data pattern = PRBS  $2^{15} - 1$ , ac-coupled inputs and outputs, unless otherwise noted.

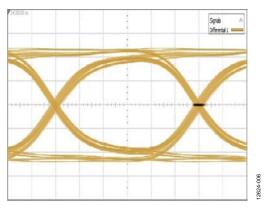

Figure 6. Output Eye Diagram at CPRI × 16 = 9.8304 Gbps, Time = 16.95 ps/div, Amplitude = 116 mV/div

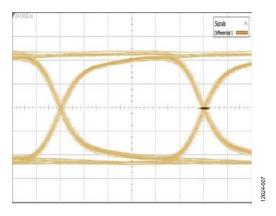

Figure 7. Output Eye Diagram at CPRI  $\times$  12 = 6.144 Gbps, Time = 27.13 ps/div, Amplitude = 118 mV/div

Figure 9. BER in Equalizer Mode vs. EQ Compensation at CPRI × 16 = 9.8304 Gbps (with a Signal of 400 mV p-p Differential, on 15 inch FR4 Traces, with Variant EQ Compensation, Including Adaptive EQ)

Figure 14. I<sup>2</sup>C Interface Timing Diagram

## **REGISTER MAP**

Writing to register bits other than those clearly labeled is not recommended and may cause unintended results.

| Reg. Name      | R/W | Addr.<br>(Hex) | Default<br>(Hex) | D7                 | D6                 | D5               | D4                 | D3                          | D2                             | D1                          | DO                  |  |  |

|----------------|-----|----------------|------------------|--------------------|--------------------|------------------|--------------------|-----------------------------|--------------------------------|-----------------------------|---------------------|--|--|

| Readback/Stat  | us  |                |                  |                    |                    |                  |                    |                             | 1                              |                             |                     |  |  |

| FREQMEAS0      | R   | 0x0            | N/A              |                    |                    |                  | FREQ0[7:0] (R      | RATE_FREQ[7:0               | )])                            |                             |                     |  |  |

| FREQMEAS1      | R   | 0x1            | N/A              |                    |                    |                  | FREQ1[7:0] (R      | ATE_FREQ[15:                | 8])                            |                             |                     |  |  |

| FREQMEAS2      | R   | 0x2            | N/A              |                    |                    |                  | FREQ2[7:0] (RA     | TE_FREQ[23:1                | 6])                            |                             |                     |  |  |

| FREQ_RB1       | R   | 0x4            | N/A              |                    | VCO                | SEL[7:0]         |                    |                             |                                |                             |                     |  |  |

| FREQ_RB2       | R   | 0x5            | N/A              | Х                  | FULLRATE           |                  | DIVRA              | ATE[3:0]                    |                                | VCC                         | )SEL[9:8]           |  |  |

| STATUSA        | R   | 0x6            | N/A              | х                  | Х                  | Reserved         | LOL status         | Reserved                    | Static LOL                     | Х                           | RATE_MEAS_<br>COMP  |  |  |

| General Contro | ol  |                |                  | •                  |                    | •                | •                  |                             | •                              | •                           |                     |  |  |

| CTRLA          | R/W | 0x8            | 0x10             | 0                  | (                  | CDR_MODE[2       | 2:0]               | 0                           | Reset static<br>LOL            | RATE_<br>MEAS_EN            | RATE_MEAS_<br>RESET |  |  |

| CTRLB          | R/W | 0x9            | 0x08             | SOFTWARE_<br>RESET | INIT_FREQ<br>_ACQ  | CDR<br>bypass    | LOL config         | 1                           | Reserved                       | 0                           | 0                   |  |  |

| CTRLC          | R/W | 0xA            | 0x05             | 0                  | 0                  | 0                | 0                  | 0                           | REFCLK_<br>PDN                 | 0                           | 1                   |  |  |

| FLL Control    |     |                |                  |                    |                    | _                |                    |                             |                                |                             |                     |  |  |

| LTR_MODE       | R/W | 0xF            | 0x00             | 0                  | LOL data           | FREF_F           | ANGE[1:0]          |                             | DATA_TO_REF_RATIO[3:0]         |                             |                     |  |  |

| DPLL Control   |     |                |                  |                    |                    |                  |                    |                             |                                |                             |                     |  |  |

| DPLLA          | R/W | 0x10           | 0x1C             | 0                  | 0                  | 0                | EDGE_S             | SEL[1:0]                    | TRANBW[2:0]                    |                             |                     |  |  |

| DPLLD          | R/W | 0x13           | 0x02             | 0                  | 0                  | 0                | 0                  | 0                           | Reserved DLL_SLEW[1:0]<br>to 0 |                             |                     |  |  |

| Phase          | R/W | 0x14           | 0x00             | 0                  | 0                  | 0                | 0                  |                             | SAMPLE_PHASE[3:0]              |                             |                     |  |  |

| LA_EQ          | R/W | 0x16           | 0x08             | RX_TERM_<br>FLOAT  | INPUT_             | SEL[1:0]         | ADAPTIVE_<br>EQ_EN | EQ_BOOST[3:0]               |                                |                             |                     |  |  |

| Output Contro  | l – |                |                  |                    |                    | _                | -                  |                             |                                |                             |                     |  |  |

| OUTPUTA        | R/W | 0x1E           | 0x00             | 0                  | 0                  | Data<br>squelch  | DATOUT_<br>DISABLE | 1                           | DDR_<br>DISABLE                | DATA_<br>POLARITY           | Reserved            |  |  |

| OUTPUTB        | R/W | 0x1F           | 0xCC             |                    | DATA_SW            | /ING[3:0]        |                    |                             | Res                            | served                      |                     |  |  |

| PRBS Control   |     |                |                  |                    |                    | _                | -                  |                             |                                |                             |                     |  |  |

| PRBS Gen 1     | R/W | 0x39           | 0x00             | 0                  | 0                  | DATA_<br>CID_BIT | DATA_<br>CID_EN    | 0                           | DATA_<br>GEN_EN                | DATA_GE                     | N_MODE[1:0]         |  |  |

| PRBS Gen 2     | R/W | 0x3A           | 0x00             |                    |                    |                  | DATA_CID           | LENGTH[7:0]                 |                                |                             |                     |  |  |

| PRBS Gen 3     | R/W | 0x3B           | 0x00             |                    |                    |                  |                    | DATA[7:0]                   |                                |                             |                     |  |  |

| PRBS Gen 4     | R/W | 0x3C           | 0x00             |                    |                    |                  | PROG_E             | PROG_DATA[15:8]             |                                |                             |                     |  |  |

| PRBS Gen 5     | R/W | 0x3D           | 0x00             |                    |                    |                  |                    | ATA[23:16]                  |                                |                             |                     |  |  |

| PRBS Gen 6     | R/W | 0x3E           | 0x00             |                    | -                  | 1                | PROG_D             | ATA[31:24]                  |                                | T                           |                     |  |  |

| PRBS Rec 1     | R/W | 0x3F           | 0x00             | 0                  | 0                  | 0                | 0                  | DATA_<br>RECEIVER_<br>CLEAR | DATA_<br>RECEIVER_<br>ENABLE   | DATA_RECEIVER_<br>MODE[1:0] |                     |  |  |

| PRBS Rec 2     | R   | 0x40           | 0x00             |                    | 1                  | 1                | PRBS_ERRO          | R_COUNT[7:0]                |                                | 1                           |                     |  |  |

| PRBS Rec 3     | R   | 0x41           | 0x00             |                    |                    |                  |                    |                             |                                |                             | PRBS_ERROF          |  |  |

| PRBS Rec 4     | R   | 0x42           | N/A              |                    | 1                  |                  | DATA_LO            | DADED[7:0]                  | I                              |                             | . –                 |  |  |

| PRBS Rec 5     | R   | 0x43           | N/A              |                    |                    |                  |                    | DADED[15:8]                 |                                |                             |                     |  |  |

| PRBS Rec 6     | R   | 0x44           | N/A              |                    |                    |                  |                    | ADED[23:16]                 |                                |                             |                     |  |  |

|                | R   | 0x45           | N/A              |                    | DATA_LOADED[31:24] |                  |                    |                             |                                |                             |                     |  |  |

## **Data Sheet**

|             |     | Addr. | Default |    |    |    |    |          |    |    |    |

|-------------|-----|-------|---------|----|----|----|----|----------|----|----|----|

| Reg. Name   | R/W | (Hex) | (Hex)   | D7 | D6 | D5 | D4 | D3       | D2 | D1 | D0 |

| ID/Revision |     |       |         |    |    |    | -  | <u>.</u> |    |    |    |

| REV         | R   | 0x48  | 0x54    |    |    |    |    | Rev[7:0] |    |    |    |

| ID          | R   | 0x49  | 0x15    |    |    |    |    | ID[7:0]  |    |    |    |

| HI_CODE     | R   | 0x20  | 0xAD    |    |    |    |    | Reserved |    |    |    |

| LO_CODE     | R   | 0x21  | 0x63    |    |    |    |    | Reserved |    |    |    |

<sup>1</sup> X means don't care.

<sup>2</sup> N/A means not applicable.

#### Table 8. Status Register, STATUSA (Address 0x6)

| Bit(s) | Bit Name       | Bit Description                                                         |

|--------|----------------|-------------------------------------------------------------------------|

| D5     | Reserved       | X                                                                       |

| D4     | LOL status     | 0 = locked                                                              |

|        |                | 1 = frequency acquisition mode                                          |

| D3     | Reserved       | X                                                                       |

| D2     | Static LOL     | 0 = no LOL event since last reset                                       |

|        |                | 1 = LOL event since last reset; clear using the reset static LOL bit    |

| D0     | RATE_MEAS_COMP | Rate measurement complete                                               |

|        |                | 0 = frequency measurement incomplete                                    |

|        |                | 1 = frequency measurement complete; clear using the RATE_MEAS_RESET bit |

#### Table 9. Control Register, CTRLA (Address 0x8)

| Bit(s)  | Bit Name         | Bit Description                                                                                                                                      |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7      | Reserved         | Reserved to 0.                                                                                                                                       |

| [D6:D4] | CDR_MODE[2:0]    | CDR modes.                                                                                                                                           |

|         |                  | 000 = lock to data (LTD).                                                                                                                            |

|         |                  | 010 = lock to reference (LTR).                                                                                                                       |

|         |                  | 001, 011 = reserved.                                                                                                                                 |

| D3      | Reserved         | Reserved to 0.                                                                                                                                       |

| D2      | Reset static LOL | In factory default mode, this bit is set to 0. In the static LOL mode, write 1 and then write 0 to clear static LOL bit (D2 of the status register). |

| D1      | RATE_MEAS_EN     | Fine data rate measurement enable. Set to 1 to initiate a rate measurement.                                                                          |

| D0      | RATE_MEAS_RESET  | Rate measurement reset. Set to 1 to clear a rate measurement.                                                                                        |

#### Table 10. Control Register, CTRLB (Address 0x9)

| Bit(s)  | Bit Name       | Bit Description                                                                                           |

|---------|----------------|-----------------------------------------------------------------------------------------------------------|

| D7      | SOFTWARE_RESET | Software reset. Write a 1 followed by a 0 to reset the device.                                            |

| D6      | INIT_FREQ_ACQ  | Initiate frequency acquisition. Write a 1 followed by a 0 to initiate a frequency acquisition (optional). |

| D5      | CDR bypass     | CDR bypass.                                                                                               |

|         |                | 0 = CDR enabled.                                                                                          |

|         |                | 1 = CDR bypassed.                                                                                         |

| D4      | LOL config     | LOL configuration.                                                                                        |

|         |                | 0 = normal LOL.                                                                                           |

|         |                | 1 = static LOL.                                                                                           |

| D3      | Reserved       | Reserved to 1.                                                                                            |

| D2      | Reserved       | Reserved to 0.                                                                                            |

| [D1:D0] | Reserved       | Reserved to 0.                                                                                            |

|         | Table 11. Control Register, CTREC (Ruless 0x1) |                                                                      |  |  |  |

|---------|------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| Bit(s)  | Bit Name                                       | Bit Description                                                      |  |  |  |

| [D7:D3] | Reserved                                       | Reserved to 0.                                                       |  |  |  |

| D2      | REFCLK_PDN                                     | Reference clock power-down. Write a 0 to enable the reference clock. |  |  |  |

| D1      | Reserved                                       | Reserved to 0.                                                       |  |  |  |

| D0      | Reserved                                       | Reserved to 1.                                                       |  |  |  |

#### Table 11. Control Register, CTRLC (Address 0xA)

#### Table 12. Lock to Reference Clock Mode Programming Register, LTR\_MODE<sup>1</sup> (Address 0xF)

| Bit(s)  | Bit Name               | Bit Description                             |

|---------|------------------------|---------------------------------------------|

| D7      | Reserved               | Reserved to 0                               |

| D6      | LOL data               | LOL data                                    |

|         |                        | 0 = CLK vs. reference clock during tracking |

|         |                        | 1 = CLK vs. data during tracking            |

| [D5:D4] | FREF_RANGE[1:0]        | f <sub>REF</sub> range                      |

|         |                        | 00 = 11.05 MHz to 22.1 MHz                  |

|         |                        | 01 = 22.1 MHz to 44.2 MHz                   |

|         |                        | 10 = 44.2 MHz to 88.4 MHz                   |

|         |                        | 11 = 88.4 MHz to 176.8 MHz                  |

| [D3:D0] | DATA_TO_REF_RATIO[3:0] | Data to reference ratio                     |

|         |                        | 0000 = 1/2                                  |

|         |                        | 0001 = 1                                    |

|         |                        | 0010 = 2                                    |

|         |                        | $N = 2^{(n-1)}$                             |

|         |                        | 1010 = 512                                  |

<sup>1</sup> Where DIV\_ $f_{REF}$  is the divided down reference referred to the 11.05 MHz to 22.1 MHz band (see the Reference Clock (Optional) section). Data Rate/2<sup>(LTR\_MODE[3:0] - 1)</sup> = REFCLK/2<sup>LTR\_MODE[5:4]</sup>

#### Table 13. DPLL Control Register, DPLLA (Address 0x10)

| Bit(s)  | Bit Name      | Bit Description                                                                                                                                                                                    |

|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [D7:D5] | Reserved      | Reserved to 0.                                                                                                                                                                                     |

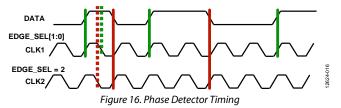

| [D4:D3[ | EDGE_SEL[1:0] | Edge for phase detection. See the Edge Select section for further details.                                                                                                                         |

|         |               | 00 = rising and falling edge data.                                                                                                                                                                 |

|         |               | 01 = rising edge data.                                                                                                                                                                             |

|         |               | 10 = falling edge data.                                                                                                                                                                            |

|         |               | 11 = rising and falling edge data.                                                                                                                                                                 |

| [D2:D0] | TRANBW[2:0]   | Transfer bandwidth. Scales transfer bandwidth. Default value is 4, resulting in the CPRI × 16:<br>9.8304 Gbps default BW shown in Table 2. See the Transfer Bandwidth section for further details. |

|         |               | Transfer BW = Default Transfer BW $\times$ (TRANBW[2:0]/4)                                                                                                                                         |

#### Table 14. DPLL Control Register, DPLLD (Address 0x13)

| Bit(s)  | Bit Name      | Bit Description                                                                 |

|---------|---------------|---------------------------------------------------------------------------------|

| [D7:D2] | Reserved      | Reserved to 0.                                                                  |

| [D1:D0] | DLL_SLEW[1:0] | DLL slew. Sets the BW of the DLL. See the DLL Slew section for further details. |

#### Table 15. Phase Control Register, Phase (Address 0x14)

| Bit(s)  | Bit Name          | Bit Description                                                                                                                                                                                      |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [D7:D4] | Reserved          | Reserved to 0.                                                                                                                                                                                       |

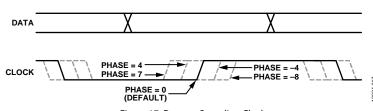

| [D3:D0] | SAMPLE_PHASE[3:0] | Adjusta the phase of the sampling instant for data rates above 5.65 Gbps in steps of 1/32 UI. This register is in twos complement notation. See the Sample Phase Adjust section for further details. |

#### Table 16. Input Stage Programming Register, LA\_EQ (Address 0x16)

| Bit(s)  | Bit Name       | Bit Description                                                                                    |

|---------|----------------|----------------------------------------------------------------------------------------------------|

| D7      | RX_TERM_FLOAT  | Receiver (Rx) termination float.                                                                   |

|         |                | 0 = termination common-mode driven.                                                                |

|         |                | 1 = termination common-mode floated.                                                               |

| [D6:D5] | INPUT_SEL[1:0] | Input stage select.                                                                                |

|         |                | 01 = equalizer.                                                                                    |

|         |                | 10 = 0  dB EQ mode.                                                                                |

|         |                | 00, 11 = undefined.                                                                                |

| D4      | ADAPTIVE_EQ_EN | Enable adaptive EQ.                                                                                |

|         |                | 0 = manual EQ control.                                                                             |

|         |                | 1 = adaptive EQ enabled.                                                                           |

| [D3:D0] | EQ_BOOST[3:0]  | Equalizer gain. These bits set the EQ gain. See the Passive Equalizer section for further details. |

#### Table 17. Output Control Register, OUTPUTA (Address 0x1E)

| Bit(s)  | Bit Name       | Bit Description          |

|---------|----------------|--------------------------|

| [D7:D6] | Reserved       | Reserved to 0            |

| D5      | Data squelch   | Squelch                  |

|         |                | 0 = normal data          |

|         |                | 1 = squelch data         |

| D4      | DATOUT_DISABLE | Data output disable      |

|         |                | 0 = data output enabled  |

|         |                | 1 = data output disabled |

| D3      | Reserved       | Reserved to 1            |

| D2      | DDR_DISABLE    | Double data rate         |

|         |                | 0 = DDR clock enabled    |

|         |                | 1 = DDR clock disabled   |

| D1      | DATA_POLARITY  | Data polarity            |

|         |                | 0 = normal data polarity |

|         |                | 1 = flip data polarity   |

| D0      | Reserved       | Reserved to 0            |

## Table 18. Output Swing Register, OUTPUTB (Address 0x1F)

| Bit(s)  | Bit Name        | Bit Description                                                                                                                                                 |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [D7:D4] | DATA_SWING[3:0] | Adjust data output amplitude. Step size is approximately 50 mV differential.<br>Default register value is 0xCH. Typical differential data output amplitudes are |

|         |                 | 0x1 to $0x3 =$ invalid.                                                                                                                                         |

|         |                 | 0x4 = 200  mV.                                                                                                                                                  |

|         |                 | 0x5 = 250  mV.                                                                                                                                                  |

|         |                 | 0x6 = 300  mV.                                                                                                                                                  |

|         |                 | 0x7 = 345 mV.                                                                                                                                                   |

|         |                 | 0x8 = 390 mV.                                                                                                                                                   |

|         |                 | 0x9 = 440  mV.                                                                                                                                                  |

|         |                 | 0xA = 485 mV.                                                                                                                                                   |

|         |                 | 0xB = 530  mV.                                                                                                                                                  |

|         |                 | 0xC = 575 mV.                                                                                                                                                   |

|         |                 | 0xD = 610  mV.                                                                                                                                                  |

|         |                 | 0xE = 640  mV.                                                                                                                                                  |

|         |                 | 0xF = 655 mV.                                                                                                                                                   |

| [D3:D0] | Reserved        | Default = 0xCH.                                                                                                                                                 |

## THEORY OF OPERATION

The ADN2905 implements a data recovery for CPRI data rates from 614.4 Mbps to 9.8304 Gbps. The front end is configurable to either equalize or 0 dB EQ the nonreturn-to-zero (NRZ) input waveform to full-scale digital logic levels, or to pass a full digital logic signal.

The user can choose from two input stages to process the data: a high-pass passive equalizer with up to 10 dB of boost at 5 GHz, or 0 dB EQ mode with approximately 250 mV p-p sensitivity at CPRI rate 9.8304 Gbps.

When the input signal is corrupted due to FR-4 or other impairments in the printed circuit board (PCB) traces, a passive equalizer can be one of the signal integrity options. The equalizer high frequency boost is configurable through the  $I^2C$ registers, in place of the factory default settings. A user enabled adaptation is included that automatically adjusts the equalizer to achieve the widest eye opening. The equalizer can be manually set for any data rate, but adaptation is available only at data rates greater than 5.5 Gbps.

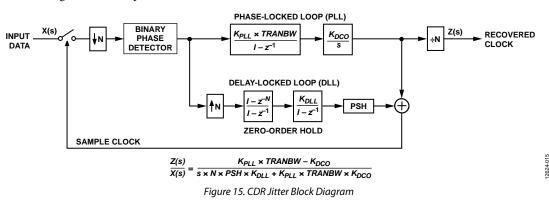

When a signal is presented to the data recovery, the ADN2905 acts as a delay-locked and phase-locked loop (PLL) circuit for clock recovery and data retiming from an NRZ encoded data stream. Input data is sampled by a high speed clock. A digital downsampler accommodates data rates spanning three orders of magnitude. Downsampled data is applied to a binary phase detector.

The phase of the input data signal is tracked by two separate feedback loops. A high speed, delay-locked loop (DLL) path cascades a digital integrator with a digitally controlled phase shifter on the digital control oscillator (DCO) clock to track the high frequency components of jitter. A separate phase control loop, composed of a digital integrator and DCO, tracks the low frequency components of jitter. The initial frequency of the DCO is set by a third loop that compares the DCO frequency with the input data frequency. This third loop also sets the decimation ratio of the digital downsampler. The delay-locked and phase-locked loops together track the phase of the input data. For example, when the clock lags the input data, the phase detector drives the DCO to a higher frequency and decreases the delay of the clock through the phase shifter; both of these actions reduce the phase error between the clock and data. Because the loop filter is an integrator, the static phase error is driven to zero.

Another view of the circuit is that the phase shifter implements the zero required for frequency compensation of a second-order phase-locked loop, and this zero is placed in the feedback path and, therefore, does not appear in the closed-loop transfer function. Because this circuit has no zero in the closed-loop transfer, jitter peaking is eliminated.

The delay-locked and phase-locked loops simultaneously provide wideband jitter accommodation and narrow-band jitter filtering. The simplified block diagram in Figure 15 shows that Z(s)/X(s) is a second-order, low-pass jitter transfer function that provides excellent filtering. The low frequency pole is formed by dividing the gain of the PLL by the gain of the DLL, where the upsampling and zero-order hold in the DLL has a gain approaching N at the transfer bandwidth of the loop. Note that the jitter transfer has no zero, unlike an ordinary, second-order phaselocked loop, which means that the main PLL has no jitter peaking. This no jitter peaking feature makes the circuit ideal for signal regenerator applications where jitter peaking in a cascade of regenerators can contribute to hazardous jitter accumulation.

The error transfer, e(s)/X(s), has the same high-pass form as an ordinary phase-locked loop up to the slew rate limit of the DLL with a binary phase detector. This transfer function is free to be optimized to give excellent wideband jitter accommodation because the jitter transfer function, Z(s)/X(s), provides the narrow-band jitter filtering.

The delay-locked and phase-locked loops contribute to overall jitter accommodation. At low frequencies of input jitter on the data signal, the integrator in the loop filter provides high gain to track large jitter amplitudes with small phase error. In this case, the oscillator is frequency modulated, and jitter is tracked as in an ordinary phase-locked loop. The amount of low frequency jitter that can be tracked is a function of the DCO tuning range. A wider tuning range provides more accommodation of low frequency jitter. The internal loop control word remains small for small jitter frequency, so that the phase shifter remains close to the center of its range and, therefore, contributes little to the low frequency jitter accommodation.

At medium jitter frequencies, the gain and tuning range of the DCO are not large enough to track input jitter. In this case, the DCO control word becomes large and saturates. As a result, the DCO frequency remains at an extreme of its tuning range. The

size of the DCO tuning range, therefore, has only a small effect on the jitter accommodation. The delay-locked loop control range is larger; therefore, the phase shifter tracks the input jitter. An infinite range phase shifter is used on the clock. Consequently, the minimum range of timing mismatch between the clock at the data sampler and the retiming clock at the output is limited by the depth of the FIFO to 32 UI.

There are two ways to acquire the data rate. The default mode is for the frequency to lock to the input data, where a finite state machine extracts frequency measurements from the data to program the DCO and loop division ratio so that the sampling frequency matches the data rate to within 250 ppm. The PLL is enabled, driving this frequency difference to 0 ppm. The second mode is to lock to reference (LTR), in which case the user provides a reference clock between 11.05 MHz and 176.8 MHz. Division ratios must be written to a serial port register.

## FUNCTIONAL DESCRIPTION FREQUENCY ACQUISITION