# AMD-K7™ System Clock Chip

#### **Recommended Application:**

AMD-K7 based systems

#### **Output Features:**

- 3 differential pair open drain CPU clocks (2.7V external pull-up; up to 150MHz achieviable through I<sup>2</sup>C)

- 2 AGPCLK @ 3.3V

- 8 PCI @3.3V, including 1 free running

- 1 48MHz @ 3.3V

- 1 24/48MHz @ 3.3V

- 2- REF @3.3V. 14.318MHz.

#### **Features:**

- Up to 150MHz frequency support

- Support power management: CPU, PCI, stop and Power down Mode from I<sup>2</sup>C programming.

- Spread spectrum for EMI control -0.5% down spread

- Uses external 14.318MHz crystal

- FS pins for frequency select

#### **Key Specifications:**

- CPU CPU: <250ps

- AGP-AGP: <250ps</li>

- PCI PCI: <400ps

- CPU SDRAM\_OUT: <400ps

- CPU-AGP <250ps</li>

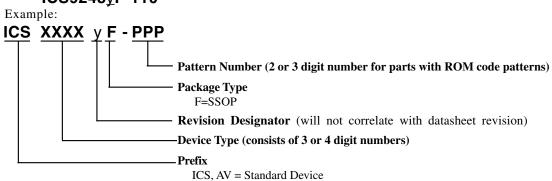

### **Pin Configuration**

48-Pin 300mil SSOP

\* Internal 120K pullup resistor on indicated inputs \*\* Internal 240K pullup resistor on indicated inputs

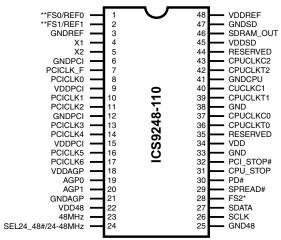

#### **Block Diagram**

### **Functionality**

| FS2 | FS1 | FS0 | CPU,<br>SDRAM | PCI   | AGP   |

|-----|-----|-----|---------------|-------|-------|

| 0   | 0   | 0   | 90            | 30.00 | 60.00 |

| 0   | 0   | 1   | 95            | 31.67 | 63.33 |

| 0   | 1   | 0   | 100.99        | 33.66 | 67.33 |

| 0   | 1   | 1   | 115           | 38.33 | 76.67 |

| 1   | 0   | 0   | 100.7         | 33.57 | 67.13 |

| 1   | 0   | 1   | 103           | 34.33 | 68.67 |

| 1   | 1   | 0   | 105           | 35.00 | 70.00 |

| 1   | 1   | 1   | 110           | 36.67 | 73.33 |

# **Pin Descriptions**

| PIN NUMBER                | PIN NAME      | TYPE | DESCRIPTION                                                                                                    |

|---------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------|

| 2, 1                      | FS (1:0)      | IN   | Frequency Select pins, has pull-up to VDD                                                                      |

| 2, 1                      | REF (1:0)     | OUT  | 14.318MHz clock output                                                                                         |

| 3                         | GNDREF        | PWR  | Ground for REF outputs                                                                                         |

| 4                         | X1            | IN   | XTAL_IN 14.318MHz Crystal input, has internal 33pF load cap and feed back resistor from X2                     |

| 5                         | X2            | OUT  | XTAL_OUT Crystal output, has internal load cap 33pF                                                            |

| 6, 12                     | GNDPCI        | PWR  | Ground for PCI outputs                                                                                         |

| 7                         | PCICLK_F      | OUT  | Free Running PCI output. Not affected by the PCI_STOP# input.                                                  |

| 17, 16, 14, 13, 11, 10, 8 | PCICLK (6:0)  | OUT  | PCI clock outputs. TTL compatible 3.3V                                                                         |

| 9, 15                     | VDDPCI        | PWR  | Power for PCICLK outputs, nominally 3.3V                                                                       |

| 18                        | VDDAGP        | PWR  | Power for AGP outputs, nominally 3.3V                                                                          |

| 20, 19                    | AGP (1:0)     | OUT  | AGP outputs defined as 2X PCI. These may not be stopped.                                                       |

| 21                        | GNDAGP        | PWR  | Ground for AGP clock outputs                                                                                   |

| 34                        | VDD           | PWR  | Isolated power for core, nominally 3.3V                                                                        |

| 33                        | GND           | PWR  | Isolated ground for core                                                                                       |

| 22                        | VDD48         | PWR  | Power for USB, FDC outputs nominally 3.3V                                                                      |

| 23                        | 48MHz         | OUT  | 48MHz output                                                                                                   |

| 24                        | SEL24-48#     | IN   | Selects 24 or 48MHz output for pin 24<br>Low = 48MHz High = 24MHz                                              |

|                           | 24-48MHz      | OUT  | Fixed clock out selectable through SEL24-48#                                                                   |

| 25                        | GND48         | PWR  | Ground for 48MHz outputs                                                                                       |

| 26                        | SCLK          | IN   | Clock input for I <sup>2</sup> C                                                                               |

| 27                        | SDATA         | I/O  | Data pin for I <sup>2</sup> C circuitry 5V tolerant                                                            |

| 28                        | FS2           | IN   | Frequency Select pin, has pull-up to VDD                                                                       |

| 29                        | SPREAD#       | IN   | Enables Spread Spectrum feature when LOW. Down Spread 0.5% modulation frequency =50KHz                         |

| 30                        | PD#           | IN   | Powers down chip, active low. Internal PLL & all outputs are disabled.                                         |

| 31                        | CPU_STOP#     | IN   | Halts CPUCLKs. CPUCLKTs driven LOW wheras CPUCLKC is driven HIGH when this pin is asserted (Active LOW).       |

| 32                        | PCI_STOP#     | IN   | Halts PCI Bus at logic "0" level when driven low. PCICLK_F is not affected by this pin                         |

| 46                        | SDRAM_OUT     | OUT  | Reference clock for SDRAM zero delay buffer                                                                    |

| 34                        | VDD           | PWR  | Isolated power for core                                                                                        |

| 35, 44                    | RESERVED      | N/C  | Furture CPU power rail                                                                                         |

| 42, 39, 36                | CPUCLKT (2:0) | OUT  | "True" clocks of differential pair CPU outputs. These open drain outputs need an external 1.5V pull-up.        |

| 43, 40, 37                | CPUCLKC (2:0) | OUT  | "Complementory" clocks of differental pair CPU output. These open drain outputs need an external 1.5V pull_up. |

| 38, 41                    | GNDCPU        | PWR  | Ground for CPUCLK outputs.                                                                                     |

| 45                        | VDDSD         | PWR  | Power for SDRAM_OUT pin. Nominally 3.3V                                                                        |

| 47                        | GNDSD         | PWR  | Ground for SDRAM_OUT pins                                                                                      |

| 48                        | VDDREF        | PWR  | Power for REF, X1, X2, nominally 3.3V                                                                          |

#### **General Description**

The ICS9248-110 is a main clock synthesizer chip for AMD-K7 based systems. This provides all clocks required for such a system when used with a Zero Delay Buffer Chip such as the ICS9179-06.

Spread spectrum may be enabled through I<sup>2</sup>C programming. Spread spectrum typically reduces system EMI by 8dB to 10dB. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9248-110 employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature variations.

Serial programming I<sup>2</sup>C interface allows changing functions, stop clock programming and frequency selection.

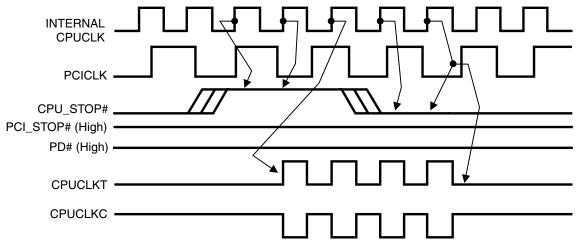

# CPU\_STOP# Timing Diagram

CPU\_STOP# is an asychronous input to the clock synthesizer. It is used to turn off the CPUCLKs for low power operation. CPU\_STOP# is synchronized by the ICS9248-110. All other clocks will continue to run while the CPUCLKs clocks are disabled. The CPUCLKs will always be stopped in a low state and start in such a manner that guarantees the high pulse width is a full pulse. CPUCLK on latency is less than 4 CPUCLKs and CPUCLK off latency is less than 4 CPUCLKs.

- 1. All timing is referenced to the internal CPUCLK.

- CPU\_STOP# is an asynchronous input and metastable conditions may exist. This signal is synchronized to the CPUCLKs inside the ICS9248-110.

- 3. All other clocks continue to run undisturbed.

- 4. PD# and PCI\_STOP# are shown in a high (true) state.

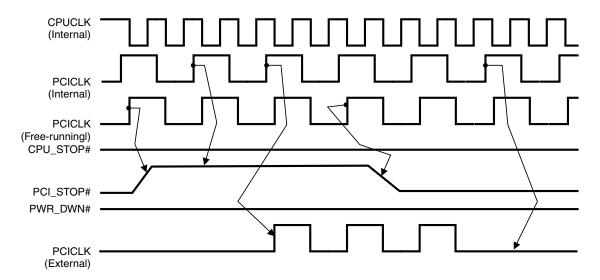

# PCI\_STOP# Timing Diagram

PCI\_STOP# is an asynchronous input to the **ICS9248-110**. It is used to turn off the PCICLK (0:5) clocks for low power operation. PCI\_STOP# is synchronized by the **ICS9248-110** internally. PCICLK (0:5) clocks are stopped in a low state and started with a full high pulse width guaranteed. PCICLK (0:5) clock on latency cycles are only one rising PCICLK clock off latency is one PCICLK clock.

- 1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248 device.)

- 2. PCI\_STOP# is an asynchronous input, and metastable conditions may exist. This signal is required to be synchronized inside the ICS9248.

- 3. All other clocks continue to run undisturbed.

- 4. PD# and CPU\_STOP# are shown in a high (true) state.

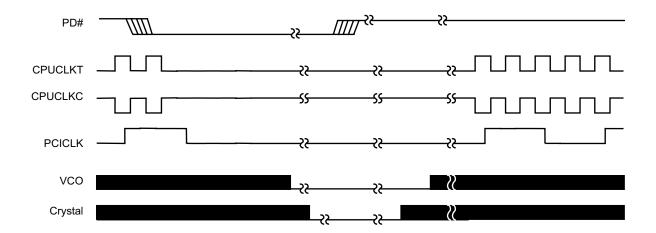

# **PD# Timing Diagram**

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the clock synthesizer.

Internal clocks are not running after the device is put in power down. When PD# is active low all clocks need to be driven to a low value and held prior to turning off the VCOs and crystal. The power up latency needs to be less than 3 mS. The power down latency should be as short as possible but conforming to the sequence requirements shown below. PCI\_STOP# and CPU\_STOP# are considered to be don't cares during the power down operations. The REF and 48MHz clocks are expected to be stopped in the LOW state as soon as possible. Due to the state of the internal logic, stopping and holding the REF clock outputs in the LOW state may require more than one clock cycle to complete.

- 1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248-110 device).

- 2. As shown, the outputs Stop Low on the next falling edge after PD# goes low.

- 3. PD# is an asynchronous input and metastable conditions may exist. This signal is synchronized inside this part.

- 4. The shaded sections on the VCO and the Crystal signals indicate an active clock.

- 5. Diagrams shown with respect to 133MHz. Similar operation when CPU is 100MHz.

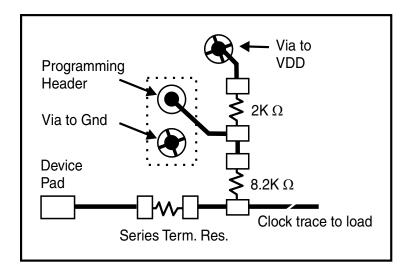

# Shared Pin Operation - Input/Output Pins

The I/O pins designated by (input/output) on the ICS9248-110 serve as dual signal functions to the device. During initial power-up, they act as input pins. The logic level (voltage) that is present on these pins at this time is read and stored into a 5-bit internal data latch. At the end of Power-On reset, (see AC characteristics for timing values), the device changes the mode of operations for these pins to an output function. In this mode the pins produce the specified buffered clocks to external loads.

To program (load) the internal configuration register for these pins, a resistor is connected to either the VDD (logic 1) power supply or the GND (logic 0) voltage potential. A 10 Kilohm (10K) resistor is used to provide both the solid CMOS programming voltage needed during the power-up programming period and to provide an insignificant load on the output clock during the subsequent operating period.

Figure 1 shows a means of implementing this function when a switch or 2 pin header is used. With no jumper is installed the pin will be pulled high. With the jumper in place the pin will be pulled low. If programmability is not necessary, than only a single resistor is necessary. The programming resistors should be located close to the series termination resistor to minimize the current loop area. It is more important to locate the series termination resistor close to the driver than the programming resistor.

Fig. 1

# General I<sup>2</sup>C serial interface information

The information in this section assumes familiarity with I<sup>2</sup>C programming. For more information, contact ICS for an I<sup>2</sup>C programming application note.

#### **How to Write:**

- Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends a dummy command code

- ICS clock will acknowledge

- Controller (host) sends a dummy byte count

- ICS clock will acknowledge

- Controller (host) starts sending first byte (Byte 0) through byte 6

- ICS clock will acknowledge each byte one at a time.

- Controller (host) sends a Stop bit

| How to Write:      |                      |  |  |  |  |  |

|--------------------|----------------------|--|--|--|--|--|

| Controller (Host)  | ICS (Slave/Receiver) |  |  |  |  |  |

| Start Bit          |                      |  |  |  |  |  |

| Address            |                      |  |  |  |  |  |

| D2 <sub>(H)</sub>  |                      |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |

| Dummy Command Code |                      |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |

| Dummy Byte Count   |                      |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |

| Byte 0             |                      |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |

| Byte 1             |                      |  |  |  |  |  |

|                    | ACK                  |  |  |  |  |  |

| Byte 2             | 401/                 |  |  |  |  |  |

| D. ( ) 0           | ACK                  |  |  |  |  |  |

| Byte 3             | ACK                  |  |  |  |  |  |

| Puto 4             | ACK                  |  |  |  |  |  |

| Byte 4             | ACK                  |  |  |  |  |  |

| Byte 5             | AUN                  |  |  |  |  |  |

| byte 3             | ACK                  |  |  |  |  |  |

| Byte 6             | AUN                  |  |  |  |  |  |

| 2,100              | ACK                  |  |  |  |  |  |

| Stop Bit           | 7.5.1                |  |  |  |  |  |

### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the byte count

- · Controller (host) acknowledges

- ICS clock sends first byte (Byte 0) through byte 6

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a stop bit

| How to            | Read:                |

|-------------------|----------------------|

| Controller (Host) | ICS (Slave/Receiver) |

| Start Bit         |                      |

| Address           |                      |

| D3 <sub>(H)</sub> |                      |

|                   | ACK                  |

|                   | Byte Count           |

| ACK               |                      |

|                   | Byte 0               |

| ACK               |                      |

|                   | Byte 1               |

| ACK               |                      |

|                   | Byte 2               |

| ACK               |                      |

|                   | Byte 3               |

| ACK               |                      |

|                   | Byte 4               |

| ACK               |                      |

|                   | Byte 5               |

| ACK               |                      |

|                   | Byte 6               |

| ACK               |                      |

| Stop Bit          |                      |

- 1. The ICS clock generator is a slave/receiver, I<sup>2</sup>C component. It can read back the data stored in the latches for verification. **Read-Back will support Intel PIIX4 "Block-Read" protocol**.

- 2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

- 3. The input is operating at 3.3V logic levels.

- 4. The data byte format is 8 bit bytes.

- 5. To simplify the clock generator I<sup>2</sup>C interface, the protocol is set to use only "**Block-Writes**" from the controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those two bytes. The data is loaded until a Stop sequence is issued.

- 6. At power-on, all registers are set to a default condition, as shown.

# I<sup>2</sup>C Command Bitmaps

Byte 6: SDRAM Clock & Generator Mode Control Register

| Spread Spectrum enable (+/- 0.25% center spread) 1=ON 0=OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit      | Description |            |     |              |             |       |              |       | PWD   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|------------|-----|--------------|-------------|-------|--------------|-------|-------|

| Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7        |             |            |     |              |             |       |              |       | 0     |

| Sit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | Bit 3       | Bit 2      |     |              |             |       |              |       |       |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |            |     |              |             |       |              |       |       |

| 3.2, 6:4    0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |             | Ţ.         |     |              | 0           |       |              |       |       |

| 3.2, 6:4    O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |             | _          |     | 0            |             |       |              |       |       |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |            |     | 1            | 0           |       |              |       |       |

| 3,2,6:4    O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             |            | 0   |              |             |       |              |       |       |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |            | 1   |              | 0           |       |              |       |       |

| 3,2,6:4    O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             | 0          | 1   | 0            | _           |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             | -          | 1   | 1            | 0           |       |              |       |       |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             | 0          |     |              |             |       |              |       |       |

| 3,2,6:4    0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             | 1          |     |              |             |       |              |       |       |

| 3,2,6:4    0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             |            |     |              |             |       |              |       |       |

| 3,2,6:4    0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             | 1          |     | 1            | 0           |       |              |       |       |

| 3,2,6:4    0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             | 1          | 0   |              |             |       |              |       |       |

| 3,2,6:4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |             | 1          | 1   | 0            | 0           |       |              |       |       |

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |             | 1          | 1   | 0            | 1           |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 2 6.4  |             | 1          | 1   | 1            | 0           |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3,2, 0.1 | 0           |            | 1   |              |             |       |              |       | Note1 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           |            | _   |              | 0           | 112   |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           | 0          | _   | 0            | _           |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           | _          |     | 1            | 0           |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           |            | 0   | 1            |             |       |              |       |       |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           |            | 1   |              | 0           |       |              |       |       |

| 1       0       1       1       1       120       30.00       60.00         1       1       0       0       0       121       30.25       60.50         1       1       0       0       1       122       30.50       61.00         1       1       0       1       0       123       30.75       61.50         1       1       0       1       1       124       31.00       62.00         1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00     1  O - Frequency is selected by hardware select, latched input; Spread controlled by pin 29  1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  O - SDRAM_OUT Disable |          |             |            |     | 0            |             |       |              |       |       |

| 1       1       0       0       0       121       30.25       60.50         1       1       0       0       1       122       30.50       61.00         1       1       0       1       0       123       30.75       61.50         1       1       0       1       1       124       31.00       62.00         1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00     1  O - Frequency is selected by hardware select, latched input; Spread controlled by pin 29  1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  O - SDRAM_OUT Disable                                                                             |          | 1           |            | 1   | 1            | 0           |       |              |       |       |

| 1       1       0       0       1       122       30.50       61.00         1       1       1       0       123       30.75       61.50         1       1       0       1       124       31.00       62.00         1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00     1  O - Frequency is selected by hardware select, latched input; Spread controlled by pin 29  1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  O - SDRAM_OUT Disable                                                                                                                                                                         |          | 1           | 0          |     |              | 1           |       |              |       |       |

| 1       1       0       1       0       123       30.75       61.50         1       1       1       0       1       1       124       31.00       62.00         1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00     1  O - Frequency is selected by hardware select, latched input; Spread controlled by pin 29  1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  O - SDRAM_OUT Disable                                                                                                                                                                                                                             |          | 1           | 1          |     |              | 0           |       |              |       | 1     |

| 1       1       0       1       1       124       31.00       62.00         1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00     1  O - Frequency is selected by hardware select, latched input; Spread controlled by pin 29  1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  O - SDRAM_OUT Disable                                                                                                                                                                                                                                                                                                                 |          | 1           | 1          |     | 0            |             |       |              |       | 1     |

| 1       1       1       0       0       125       31.25       62.50         1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       1       150       37.50       75.00         1       0 - Frequency is selected by hardware select, latched input; Spread controlled by pin 29       0         1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7       0                                                                                                                                                                                                                                                                                                                                                                                    |          | 1           | 1          |     | 1            | 0           |       |              |       | 1     |

| 1       1       1       0       1       133.33       33.33       66.67         1       1       1       1       0       140       35.00       70.00         1       1       1       1       150       37.50       75.00         1       0 - Frequency is selected by hardware select, latched input; Spread controlled by pin 29       0         1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7       0         0       0 - SDRAM_OUT Disable       1                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 1           | 1          | 0   |              | 1           |       | 31.00        |       |       |

| 1         1         1         1         0         140         35.00         70.00           1         1         1         1         150         37.50         75.00           1         0 - Frequency is selected by hardware select, latched input; Spread controlled by pin 29         0           1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 1           | 1          | 1   |              | 0           |       |              |       |       |

| 1 1 1 1 1 1 150 37.50 75.00  1 0 - Frequency is selected by hardware select, latched input; Spread controlled by pin 29 1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  0 0 - SDRAM_OUT Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1           | 1          | 1   | 0            | 1           |       |              |       |       |

| 1 0 - Frequency is selected by hardware select, latched input; Spread controlled by pin 29 0 1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7 0 - SDRAM_OUT Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 1           | 1          | 1   | 1            | 0           |       |              |       | 1     |

| 1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7 0 - SDRAM_OUT Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 1           | 1          | -   | -            | -           |       |              |       |       |

| 1 - Frequency is selected by Bit 6:2; Spread controlled by bit 7  0 - SDRAM_OUT Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1        |             |            |     |              |             |       | trolled by p | in 29 | 0     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1        | _           | •          | •   | 2; Spread co | ntrolled by | bit 7 |              |       |       |

| 1 - SDRAM_OUT Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0        |             |            |     |              |             |       |              |       | 1     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 1 - SDRAM   | I_OUT Enab | ole |              |             |       |              |       |       |

- 1. Default at power-up will be latched logic inputs to define frequency, as displayed by Bit 1.

- 2. PWD = Power-Up Default

# I<sup>2</sup>C Command Bitmaps

Byte 4: Clock Control Register

| Bit | Pin#   | Default | Description                                                          |

|-----|--------|---------|----------------------------------------------------------------------|

| 7   | 1      | 1       | REF0 enable                                                          |

| 6   | 23     | 1       | 24MHz/48MHz enable                                                   |

| 5   | 22     | 1       | USB0 enable                                                          |

| 4   | 20     | 1       | AGP1 enable                                                          |

| 3   | 19     | 1       | AGP0 enable                                                          |

| 2   | 42, 43 | 1       | CPUCLK2 enable (both of differential pair, True" and "Complimentary" |

| 1   | 39, 40 | 1       | CPUCLK1 enable (both of differential pair, True" and "Complimentary" |

| 0   | 36, 37 | 1       | CPUCLK0 enable (both of differential pair, True" and "Complimentary" |

**Notes:** A value of '1'b is enable, '0'b is disable

Byte 5: PCI Clock Control Register

| Bit | Pin# | Default | Description    |

|-----|------|---------|----------------|

| 7   | 2    | 1       | REF1 enable    |

| 6   | 17   | 1       | PCICLK6 enable |

| 5   | 16   | 1       | PCICLK5 enable |

| 4   | 14   | 1       | PCICLK4 enable |

| 3   | 13   | 1       | PCICLK3 enable |

| 2   | 11   | 1       | PCICLK2 enable |

| 1   | 10   | 1       | PCICLK1 enable |

| 0   | 8    | 1       | PCICLK0 enable |

**Notes:** A value of '1'b is enable, '0'b is disable

# **Absolute Maximum Ratings**

Ambient Operating Temperature . . . . .  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

# **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70^{\circ}$  C; Supply Voltage  $V_{DD} = 3.3$  V +/-5% (unless otherwise stated)

| PARAMETER                      | SYMBOL                | CONDITIONS                                                | MIN           | TYP    | MAX           | UNITS |

|--------------------------------|-----------------------|-----------------------------------------------------------|---------------|--------|---------------|-------|

| Input High Voltage             | $ m V_{IH}$           |                                                           | 2             |        | $V_{DD}$ +0.3 | V     |

| Input Low Voltage              | $V_{IL}$              |                                                           | $V_{SS}$ -0.3 |        | 0.8           | V     |

| Input High Current             | $I_{IH}$              | $V_{IN} = V_{DD}$                                         |               |        | 5             | uA    |

| Input Low Current              | $I_{IL1}$             | $V_{IN} = 0 \text{ V}$ ; Inputs with no pull-up resistors | -5            |        |               | uA    |

| Input Low Current              | $I_{IL2}$             | $V_{IN} = 0 \text{ V}$ ; Inputs with pull-up resistors    | -200          |        |               | uA    |

|                                |                       | C <sub>L</sub> =20 pF; Select @ 66 MHz                    |               | 87     | 160           | mΑ    |

| Operating Supply Current       | $I_{DD3.3OP}$         | C <sub>L</sub> = 20 pF; Select @ 100 MHz                  |               | 116    | 160           |       |

|                                |                       | $C_L = 20 \text{ pF}$ ; Select @ 133 MHz                  |               | 127    | 160           | mA    |

| Power Down                     | PD                    |                                                           |               |        | 600           | uA    |

| Input frequency                | $F_{i}$               | $V_{DD} = 3.3 \text{ V}$                                  | 12            | 14.318 | 16            | MHz   |

| Input Capacitance <sup>1</sup> | $C_{IN}$              | Logic Inputs                                              |               |        | 5             | pF    |

| Input Capacitance              | $C_{INX}$             | X1 & X2 pins                                              | 27            |        | 45            | pF    |

| Clk Stabilization <sup>1</sup> | $T_{STAB}$            | From $V_{DD} = 3.3 \text{ V}$ to 1% target Freq.          |               |        | 3             | ms    |

|                                | $T_{CPU	ext{-}SDRAM}$ | Vt=50% CPU - 1.5V SDRAM; CPU Leads                        |               | 120    | 400           | ps    |

| Skew <sup>1</sup>              | T <sub>CPU-PCI</sub>  | Vt=50% CPU - 1.5V PCI; CPU Leads                          |               | 160    | 550           | ps    |

|                                | $T_{CPU-AGP}$         | Vt =50% CPU - 1.5V AGP; CPU Leads                         |               | 65     | 250           | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# **Electrical Characteristics - USB, REF**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3V + -5\%$ ;  $C_L = 20 \text{ pF}$  (unless otherwise specified)

| PARAMETER               | SYMBOL                    | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|-------------------------|---------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Output Impedance        | $R_{DSP2B}^{1}$           | $V_0 = V_{DD}^*(0.5)$                            | 20  | 47  | 60  | Ω     |

| Output Impedance        | $R_{\mathrm{DSN2B}}^{}1}$ | $V_0 = V_{DD}^*(0.5)$                            | 20  | 44  | 60  | Ω     |

| Output High Voltage     | $V_{\mathrm{OH5}}$        | $I_{OH} = -12 \text{ mA}$                        | 2.4 |     |     | V     |

| Output Low Voltage      | $V_{OL5}$                 | $I_{OL} = 9 \text{ mA}$                          |     |     | 0.4 | V     |

| Output High Current     | $I_{OH5}$                 | $V_{OH} = 2.0 \text{ V}$                         |     |     | -22 | mA    |

| Output Low Current      | $I_{OL5}$                 | $V_{OL} = 0.8 \text{ V}$                         | 16  |     |     | mA    |

| Rise Time <sup>1</sup>  | $t_{r5}^1$                | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 2.6 | 4.0 | ns    |

| Fall Time <sup>1</sup>  | $t_{f5}^{1}$              | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 2.5 | 4.0 | ns    |

| Duty Cycle <sup>1</sup> | $d_{t5}^{-1}$             | $V_T = 1.5 \text{ V}$                            | 45  | 51  | 55  | %     |

| REF Jitter, Cyl-to-Cyl  | t <sub>jcyc-cyc5</sub> 1  | $V_T = 1.5 \text{ V}$                            |     | 320 | 700 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# **Electrical Characteristics - CPUCLK (Open Drain)**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3V + /-5\%$ ;  $C_L = 20$  pF (unless otherwise specified)

| 1 <sub>A</sub> = 0 700, 1 <sub>DD</sub> =3.31 | 17 370, C <sub>L</sub> - 2           | o pr (unicss otherwise specified) |     |      |           |       |

|-----------------------------------------------|--------------------------------------|-----------------------------------|-----|------|-----------|-------|

| PARAMETER                                     | SYMBOL                               | CONDITIONS                        | MIN | TYP  | MAX       | UNITS |

| Output Impedance                              | $Z_0^{-1}$                           | $V_0 = V_X$                       |     |      | 60        | Ω     |

| Output High Voltage                           | $V_{\mathrm{OH2B}}$                  | Termination to Vpull-up(external) | 1   |      | 1.8       | V     |

| Output Low Voltage                            | $V_{\rm OL2B}$                       | Termination to Vpull-up(external) |     |      | 0.8       | V     |

| Output Low Current                            | $I_{OL2B}$                           | $V_{OL} = 0.3 \text{ V}$          | 18  |      |           | mA    |

| Rise Time <sup>1</sup>                        | $t_{r2B}^{1}$                        | $V_{OL} = 20\%$ , $V_{OH} = 80\%$ |     | 2.4  | 2.6       | ns    |

| Fall Time <sup>1</sup>                        | $t_{f2B}^1$                          | $V_{OH} = 80\%, V_{OL} = 20\%$    |     | 1.2  | 2.6       | ns    |

| Differential voltage-AC <sup>1</sup>          | $V_{ m DIF}$                         | Note 2                            | 0.4 | Vpul | l-up(ext) | V     |

| Differential voltage-DC <sup>1</sup>          | $V_{ m DIF}$                         | Note 2                            | 0.2 | Vpul | l-up(ext) | V     |

| Diff Crossover Voltage <sup>1</sup>           | $V_{X}$                              | Note 3                            | 1.1 | 1.4  | 1.7       | V     |

| Duty Cycle <sup>1</sup>                       | $d_{t2B}^{1}$                        | $V_T = 50\%$                      | 44  | 46   | 54        | %     |

| Skew window <sup>1</sup>                      | $t_{\rm sk2B}^{-1}$                  | $V_T = 50\%$                      |     | 40   | 200       | ps    |

| Jitter, Cycle-to-cycle1                       | tjcyc-cyc <sub>2B</sub> <sup>1</sup> | $V_T = V_X$                       |     | 80   | 250       | ps    |

| Jitter, Absolute1                             | tjabs <sub>2B</sub> <sup>1</sup>     | $V_T = 50\%$                      |     | 120  | 250       | ps    |

- 1 Guaranteed by design, not 100% tested in production.

- 2  $V_{DIF}$  specifies the minimum input differential voltages ( $V_{TR}$ - $V_{CP}$ ) required for switching, where  $V_{TR}$  is the "true" input Level and  $V_{CP}$  is the "complement" input level.

- $3 Vpull-up(external) = 2.7V, \\ Min=Vpull-up(external)/2 150 \\ mV; \\ Max=Vpull-up(external)/2 + 150 \\ mV; \\ Max=Vpull-up(external)$

# **Electrical Characteristics - PCICLK**

$T_A = 0 - 70C$ ;  $V_{DD} = V_{DDL} = 3.3V + /-5\%$ ;  $C_L = 30 pF$  (unless otherwise specified)

|                          |                                 | *                                                |     |      |     |       |

|--------------------------|---------------------------------|--------------------------------------------------|-----|------|-----|-------|

| PARAMETER                | SYMBOL                          | CONDITIONS                                       | MIN | TYP  | MAX | UNITS |

| Output Impedance         | R <sub>DSP2B</sub> <sup>1</sup> | $V_O = V_{DD} * (0.5)$                           | 12  | 24   | 55  | Ω     |

| Output Impedance         | R <sub>DSN2B</sub> <sup>1</sup> | $V_O = V_{DD} * (0.5)$                           | 12  | 23   | 55  | Ω     |

| Output High Voltage      | Voh1                            | Іон = -11 mA                                     | 2.6 |      |     | V     |

| Output Low Voltage       | V <sub>OL1</sub>                | Iol = 9.4  mA                                    |     |      | 0.4 | V     |

| Output High Current      | Іон1                            | V <sub>OH</sub> = 2.0 V                          |     |      | -16 | mA    |

| Output Low Current       | Iol1                            | $V_{OL} = 0.8 \text{ V}$                         | 19  |      |     | mA    |

| Rise Time <sup>1</sup>   | tr1                             | Vol = 0.4 V, Voh = 2.4 V                         |     | 1.65 | 2.5 | ns    |

| Fall Time <sup>1</sup>   | tfi                             | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1.60 | 2.5 | ns    |

| Duty Cycle <sup>1</sup>  | dt1                             | $V_T = 1.5 \text{ V}$                            | 45  | 50   | 55  | %     |

| Skew window <sup>1</sup> | t <sub>sk1</sub>                | $V_T = 1.5 \text{ V}$                            |     | 300  | 400 | ps    |

| Jitter, Cyc-to-Cyc       | tjcyc-cyc1                      | $V_T = 1.5 \text{ V}$                            |     | 70   | 200 | ps    |

Guaranteed by design, not 100% tested in production.

# **Electrical Characteristics - PCICLK\_F**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3V + /-5\%$ ;  $C_L = 20 pF$  (unless otherwise specified)

| PARAMETER                | SYMBOL                          | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|--------------------------|---------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Output Impedance         | R <sub>DSP2B</sub> <sup>1</sup> | $V_O = V_{DD} * (0.5)$                           | 12  | 24  | 55  | Ω     |

| Output Impedance         | Rdsn2b <sup>1</sup>             | Vo=V <sub>DD</sub> *(0.5)                        | 12  | 23  | 55  | Ω     |

| Output High Voltage      | Voh1                            | Іон = -11 mA                                     | 2.6 |     |     | V     |

| Output Low Voltage       | V <sub>OL1</sub>                | IoL = 9.4  mA                                    |     |     | 0.4 | V     |

| Output High Current      | Іон1                            | $V_{OH} = 2.0 \text{ V}$                         |     |     | -12 | mA    |

| Output Low Current       | Iol1                            | $V_{OL} = 0.8 V$                                 | 12  |     |     | mA    |

| Rise Time <sup>1</sup>   | tr1                             | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 1.4 | 2.0 | ns    |

| Fall Time <sup>1</sup>   | tfi                             | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1.3 | 2.0 | ns    |

| Duty Cycle <sup>1</sup>  | dt1                             | $V_T = 1.5 \text{ V}$                            | 45  | 51  | 55  | %     |

| Skew window <sup>1</sup> | t <sub>sk1</sub>                | $V_T = 1.5 \text{ V}$                            |     | 300 | 400 | ps    |

| Jitter, Cyc-to-Cyc       | tjcyc-cyc1                      | $V_T = 1.5 \text{ V}$                            |     | 70  | 200 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - AGP**

$T_A$  = 0 - 70C;  $V_{DD}\!\!=\!\!3.3V$  +/-5%;  $C_L$  = 20 pF (unless otherwise specified)

| PARAMETER               | SYMBOL                 | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|-------------------------|------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Output Impedance        | $R_{DSP4B}^{1}$        | $V_0 = V_{DD}^*(0.5)$                            | 12  |     | 55  | Ω     |

| Output Impedance        | $R_{DSN4B}^{1}$        | $V_0 = V_{DD}^*(0.5)$                            | 12  |     | 55  | Ω     |

| Output High Voltage     | $V_{\mathrm{OH4B}}$    | $I_{OH} = -18 \text{ mA}$                        | 2   |     |     | V     |

| Output Low Voltage      | $V_{OL4B}$             | $I_{OL} = 18 \text{ mA}$                         |     |     | 0.4 | V     |

| Output High Current     | $I_{OH4B}$             | $V_{OH} = 2.0 \text{ V}$                         |     |     | -19 | mA    |

| Output Low Current      | $I_{OL4B}$             | $V_{OL} = 0.8 \text{ V}$                         | 19  |     |     | mA    |

| Rise Time <sup>1</sup>  | $t_{r4B}$              | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 1   | 2   | ns    |

| Fall Time <sup>1</sup>  | $t_{\rm f4B}$          | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1   | 2   | ns    |

| Duty Cycle <sup>1</sup> | $d_{t4B}$              | $V_T = 1.5 \text{ V}$                            | 45  | 50  | 55  | %     |

| Skew window1            | tsk <sup>1</sup>       | $V_T = 1.5 \text{ V}$                            |     | 50  | 200 | ps    |

| Jitter Cyc-Cyc          | tjcyc-cyc <sup>1</sup> | $V_T = 1.5 \text{ V}$                            |     | 288 | 450 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# **Electrical Characteristics - SDRAM\_OUT**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3V + /-5\%$ ;  $C_L = 30 \text{ pF}$  (unless otherwise specified)

| PARAMETER                            | SYMBOL             | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|--------------------------------------|--------------------|--------------------------------------------------|-----|-----|-----|-------|

| Output Impedance                     | Rdsp <sup>1</sup>  | Vo=Vdd*(0.5)                                     | 12  |     | 55  | Ω     |

| Output Impedance                     | $R_{\rm DSN}^{-1}$ | $V_O = V_{DD} * (0.5)$                           | 12  |     | 55  | Ω     |

| Output High Voltage                  | V <sub>OH3</sub>   | I <sub>OH</sub> = -11 mA                         | 2   |     |     | V     |

| Output Low Voltage                   | V <sub>OL3</sub>   | $I_{OL} = 11 \text{ mA}$                         |     |     | 0.4 | V     |

| Output High Current                  | Іоні               | Vон = 2.0 V                                      |     |     | -12 | mA    |

| Output Low Current                   | Iol3               | $V_{OL} = 0.8 \text{ V}$                         | 12  |     |     | mA    |

| SD (0:1,3:12) Rise Time <sup>1</sup> | $t_{r3}^{1}$       | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 1   | 2   | ns    |

| SD(0:1,3:12) Fall Time <sup>1</sup>  | tß <sup>1</sup>    | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1   | 2   | ns    |

| SD(0:1,3:12) Duty Cycle <sup>1</sup> | dt3 <sup>1</sup>   | $V_T = 1.5 \text{ V}$                            | 45  | 50  | 55  | %     |

| Skew window <sup>1</sup>             | $t_{sk}^{1}$       | $V_T = 1.5 \text{ V}$                            |     | 70  | 150 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

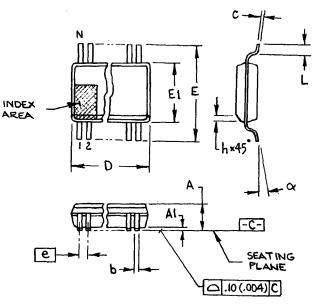

300 mil SSOP

| SYMBOL | In Millimeters COMMON DIMENSIONS |          | In Inches IS COMMON DIMENSION |       |  |

|--------|----------------------------------|----------|-------------------------------|-------|--|

|        | MIN                              | MAX      | MIN                           | MAX   |  |

| Α      | 2.413                            | 2.794    | .095                          | .110  |  |

| A1     | 0.203                            | 0.406    | .008                          | .016  |  |

| b      | 0.203                            | 0.343    | .008                          | .0135 |  |

| С      | 0.127                            | 0.254    | .005                          | .010  |  |

| D      | SEE VAR                          | RIATIONS | SEE VARIATIONS                |       |  |

| Е      | 10.033                           | 10.668   | .395                          | .420  |  |

| E1     | 7.391                            | 7.595    | .291                          | .299  |  |

| е      | 0.635                            | BASIC    | 0.025 BASIC                   |       |  |

| h      | 0.381                            | 0.635    | .015                          | .025  |  |

| L      | 0.508                            | 1.016    | .020                          | .040  |  |

| N      | SEE VAR                          | IATIONS  | SEE VARIATIONS                |       |  |

| α      | 0°                               | 8°       | 0°                            | 8°    |  |

VARIATIONS

| N        | D mm.  |        | D (inch) |        |  |