## STMAV340 evaluation board & PCB layout recommendation

### Introduction

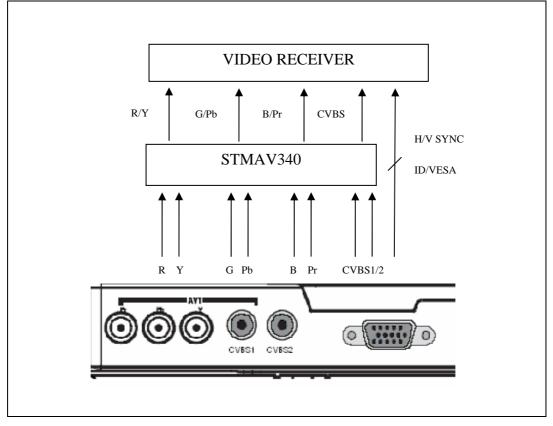

STMAV340 has 4 channels and a 2 to 1 video switch that is well suited for switching analog video signals on a TV or monitor set. Below is a diagram of STMAV340 typical application configuration. As illustrated on the picture below, the 3 channels of the switch can be used to switch two complete sets of RGB and YPbPr to a single RGB/YPbPr output. One additional channel can be used to switch 2 CBVS inputs to a single output that can be directly connected to a single CVBS receiver input.

Without STMAV340 integrated in the system, the video receiver needs to have more input pins to accommodate the many video inputs at the back panel. With the introduction of STMAV340, less IO pins are required at the video receiver. Together with the optimized pin arrangement, the result is a straightforward system design and overall cost reduction.

### STMAV340 in a TV application

## Contents

| 1 | Evaluation board           |

|---|----------------------------|

| 2 | PCB layout recommendation6 |

| 3 | Revision history9          |

### 1 Evaluation board

The evaluation board was designed with trouble-free customer evaluation in mind. Instead of having two sets of RGB (VGA connector) and YPbPr (RCA connector) as inputs and branching the output to the VGA and RCA connectors, two VGA RGB inputs are connected and the outputs go directly to single VGA connector to a display unit.

For the evaluation, the customer can connect the two sets of inputs to two VGA port of PC, while the output can be directly connected to the VGA port of the display unit.

Power supply

The board can be powered either directly from a DC power supply or from a DC adaptor. If it is powered from DC power supply, 5VDC is connected to the power socket labeled  $V_{CC}5V$  and the ground is connected to the power socket labeled GND. The board can also be powered from a DC adaptor having output voltage of 7 V to 15 V. The DC adaptor voltage is regulated to 5 V by the on board regulator. The DC adaptor can be center positive or negative and it should be connected to the DC JACK.

To prevent the digital lines switching from coupling to the analog lines, the power distribution is separated from digital and analog sections. Although STMAV340 has also two digital lines, which are OE and SEL, it should still be powered from the analog supply because its main function is to switch analog signals and those two digital lines are mostly static during operation. Hence the analog lines are not disturbed by the digital part and, as such, there is no need to have a separate analog and digital supply for STMAV340.

The analog and digital sections on the board are isolated by ferrite beads.

| Designator         | Notes                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> 5V | Connect to 5 V of external power supply.                                                             |

| GND                | Connect to ground of external power supply.                                                          |

| DC JACK            | Connect to DC adaptor output if the board is to be powered from DC adaptor. Input voltage: 7 to 15 V |

#### Table 1. STMAV340 Demo board power supply

Note:

External power can be applied to either V<sub>CC</sub>5V/GND or DC JACK, but not to both.

Video input & output ports

There are four video input ports: VGA1, VGA2, CVBS1, and CVBS2. STMAV340 performs the switching of these video inputs. Depending on the SEL control line, either VGA1 or VGA2 input is directed to VGA\_OUT and either CVBS1 or CVBS2 is directed to CVBS\_OUT.

Since STMAV340 does not perform the switching of VGA synchronization signals, two STG719 are incorporated to switch both horizontal and vertical synchronization.

VGA port also has some ID signals. To prevent clashing between ID signals from VGA input 1 and 2, the ID lines are isolated by jumpers. If VGA1 is active and to be directed to VGA\_OUT, JP1 to JP4 should be closed whereas JP5 to JP8 should be opened. If VGA2 is active and to be directed to VGA\_OUT, JP5 to JP8 should be closed whereas JP1 to JP4 should be opened.

| Designator | Notes                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| VGA1       | <ul> <li>Connect to VGA source from PC.</li> <li>When SEL '0' this port is active</li> <li>JP1 to JP4 closed.</li> <li>JP5 to JP8 open.</li> </ul> |

| VGA2       | <ul> <li>Connect to VGA source from PC</li> <li>When SEL '1' this port is active</li> <li>JP1 to JP4 open.</li> <li>JP5 to JP8 closed.</li> </ul>  |

| CVBS1      | <ul> <li>Connect to CVBS source</li> <li>When SEL '0' this port is active</li> </ul>                                                               |

| CVBS2      | <ul> <li>Connect to CVBS source</li> <li>When SEL '1' this port is active</li> </ul>                                                               |

| VGA_OUT    | Active VGA input is directed to this port. Connect to a display unit.                                                                              |

| CVBS_OUT   | Active CVBS input is directed to this port. Connect to a display unit.                                                                             |

Table 2. Video ports on the STMAV340 Demo board

#### • Video inputs conditioning

The blanking level might vary between different video transmitters. This STMAV340 evaluation board can handle video signals with blanking level of 0 V to 2.5 V.

If video signals blanking level at outside the above range, some input conditioning should be done to translate the blanking level to the range specified.

• Digital control signals

Table 3.

Control signals on the STMAV340 Demo board

| Signal | Function                          | Notes                                                               |

|--------|-----------------------------------|---------------------------------------------------------------------|

| OE     | Enable or disable the output.     | JP9 close = LOW (enable)<br>JP9 open = HIGH (disable)               |

| SEL    | Select which switch is activated. | JP10 close = LOW (VGA1, CVBA1)<br>JP10 open = HIGH<br>(VGA2, CVBS2) |

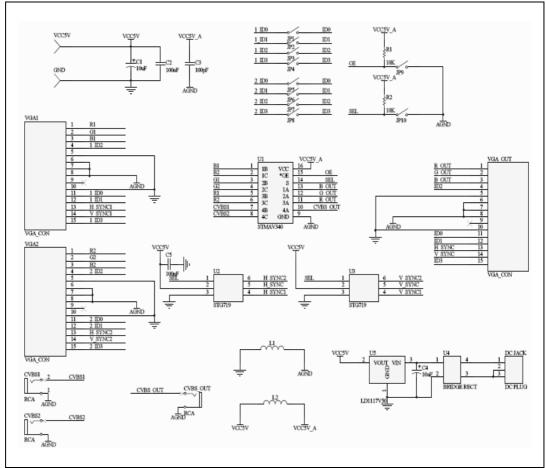

Figure 1. STMAV340 Evaluation board schematic

| Table 4. | Bill of materials (BOM) | ) |

|----------|-------------------------|---|

|----------|-------------------------|---|

| No | Component              | Designator              | Package    | Manufacturer       |

|----|------------------------|-------------------------|------------|--------------------|

| 1  | STMAV340               | U1                      | TSSOP16    | STMicroelectronics |

| 2  | STG719STR              | U2, U3                  | SOT23-6L   | STMicroelectronics |

| 3  | VGA FEMALE CON         | VGA1, VGA2, VGA_OUT     |            |                    |

| 4  | RCA CON                | CVBS1, CVBS2, CVBS_OUT  |            |                    |

| 5  | LD1117V50              | U5                      | TO-220     | STMicroelectronics |

| 6  | DF04M RECTIFIER        | U4                      | DFM        | GENERAL SEMI       |

| 7  | DC JACK                | DC JACK                 |            |                    |

| 8  | POWER SOCKET           | V <sub>CC</sub> 5V, GND |            |                    |

| 9  | FERRITE BEAD           | L1, L2                  | 1206       |                    |

| 10 | 100 nF Cap             | C2,C3, C5               | 0603       |                    |

| 11 | 10 µF Electrolytic Cap | C1, C4                  | Cap7.62 mm |                    |

|    |                        |                         |            |                    |

| No | Component    | Designator                                            | Package | Manufacturer |

|----|--------------|-------------------------------------------------------|---------|--------------|

| 12 | Jumper       | JP1, JP2, JP3, JP4, JP5, JP6,<br>JP7, JP8, JP9, JP10. | HDR 2X1 |              |

| 13 | 10k Resistor | R1, R2                                                | 0603    |              |

Table 4. Bill of materials (BOM) (continued)

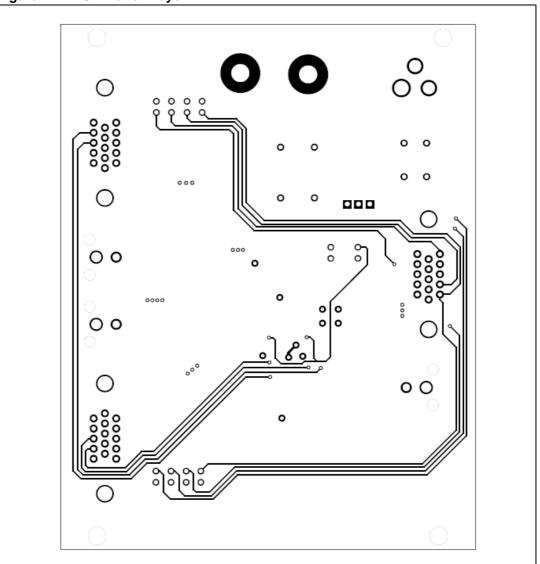

### 2 PCB layout recommendation

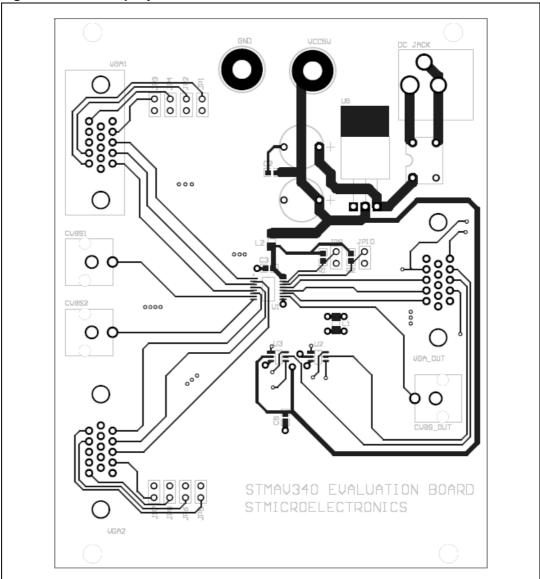

For the purpose of maintaining 75  $\Omega$  track for all the analog lines, a 4-layer structure is recommended. All the analog tracks are routed on the top layer of the board. The middle two layers are used for both analog and digital ground.

The middle two layers are identical and separated into two sections, analog and digital grounds. They are separated by a slot area and are only connected at the top layer through ferrite bead. This ensures that the digital switching noise does not get coupled to the analog portion.

All the analog tracks are routed on top of the analog ground and all the digital tracks are routed on top of digital ground. There is one signal, the SEL line, which needs to cross from analog to the digital portion. The crossing is done at the bottom layer exactly below where the ferrite bead is used to bridge the analog and digital ground. Since the SEL digital line is mostly static during operation, it does not cause any disruption to the analog portion.

STMAV340 supply is connected to V<sub>CC</sub>5V analog and GND analog. To further guarantee the stability of STMAV340 supply, a 100 nF capacitor is used to decouple the V<sub>CC</sub> pin. The stability of the analog supply lines is of significant importance since the bias level of STMAV340 is referenced to it. Any instability on the analog supply affects the switch characteristics.

Each set of video signals, RGB1, RGB2, and RGB\_OUT are routed with the same track length. This guarantees minimum channel-to-channel delay. To guarantee the impedance match on the analog lines, no via is used for routing these signals.

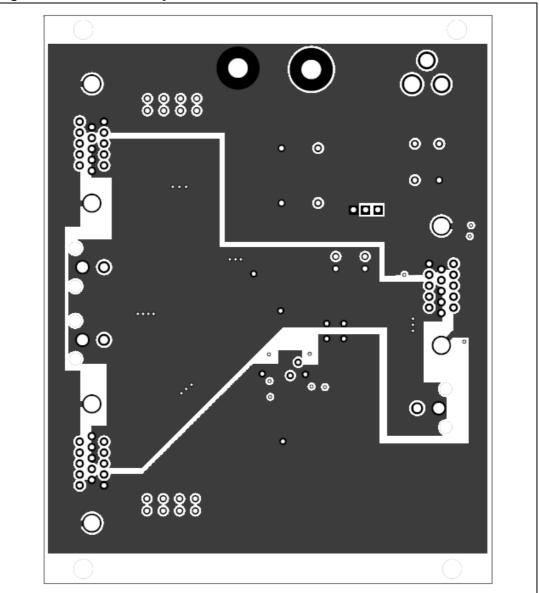

Figure 3. PCB Middle layer

Figure 4. PCB Bottom layer

# 3 Revision history

| Table 5. Revision histor | Table 5. | Revision history | 1 |

|--------------------------|----------|------------------|---|

|--------------------------|----------|------------------|---|

| Date        | Revision | Changes     |

|-------------|----------|-------------|

| 30-Apr-2007 | 1        | First issue |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com