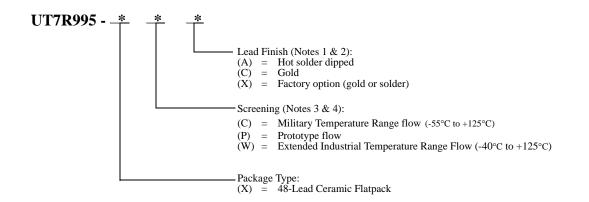

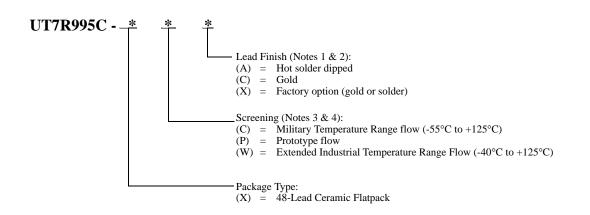

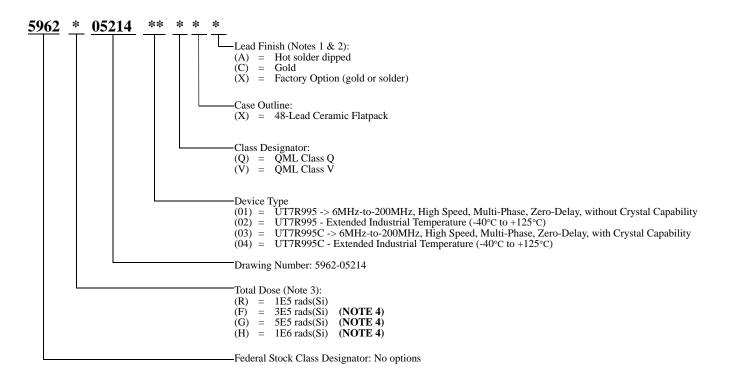

# Standard Products UT7R995 & UT7R995C RadClock<sup>TM</sup> RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer

Datasheet February, 2007

### FEATURES:

- □ +3.3V Core Power Supply

- +2.5V or +3.3V Clock Output Power Supply

Independent Clock Output Bank Power Supplies

- Output frequency range: 6 MHz to 200 MHz

- Bank pair output-output skew < 100 ps

- **Cycle-cycle** jitter < 50 ps

- $\Box$  50% ± 2% maximum output duty cycle at 100MHz

- □ Eight LVTTL outputs with selectable drive strength

- □ Selectable positive- or negative-edge synchronization

- □ Selectable phase-locked loop (PLL) frequency range and lock indicator

- $\Box$  Phase adjustments in 625 to 1300 ps steps up to  $\pm$  7.8 ns

- $\Box$  (1-6,8,10,12) x multiply and (1/2,1/4) x divide ratios

- Compatible with Spread-Spectrum reference clocks

- Power-down mode

- □ Selectable reference input divider

- **D** Radiation performance

- Total-dose tolerance: 100 krad (Si)

- SEL Immune to a LET of 109 MeV-cm<sup>2</sup>/mg

- SEU Immune to a LET of 109 MeV-cm<sup>2</sup>/mg

- $\Box$  Military temperature range: -55°C to +125°C

- $\Box$  Extended industrial temp: -40°C to +125°C

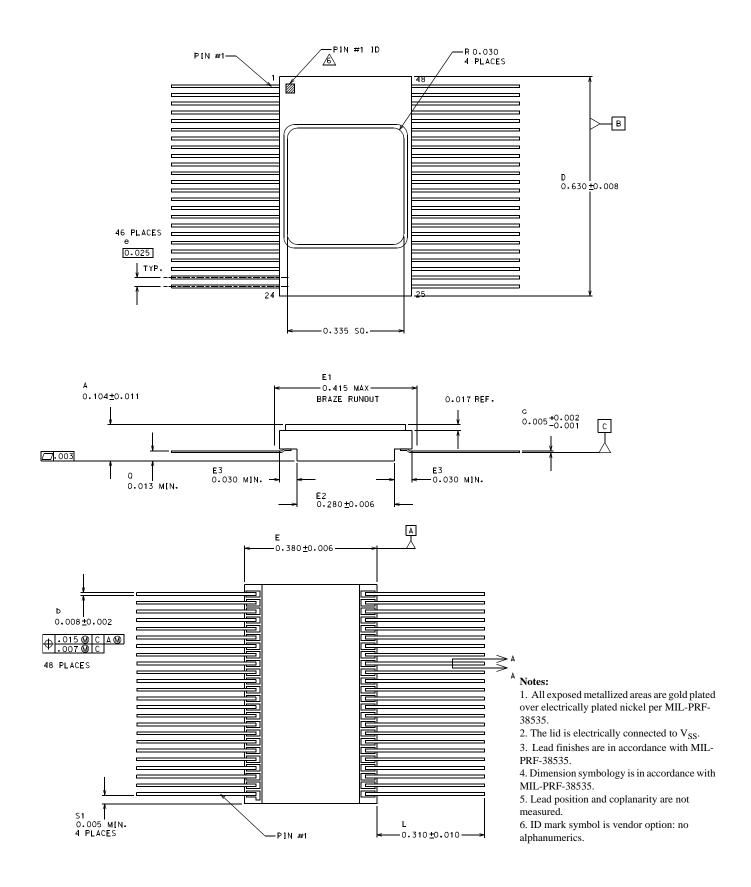

- □ Packaging options:

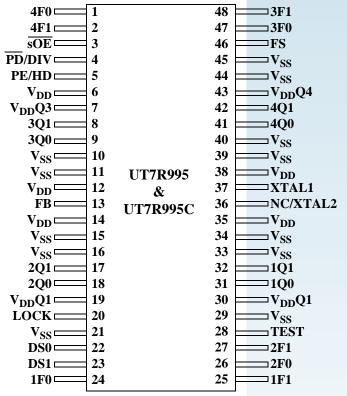

- 48-Lead Ceramic Flatpack

- Standard Microcircuit Drawing: 5962-05214

QML-Q and QML-V compliant part

### **INTRODUCTION:**

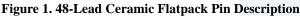

The UT7R995/UT7R995C is a low-voltage, low-power, eightoutput, 6-to-200 MHz clock driver. It features output phase programmability which is necessary to optimize the timing of high-performance microprocessor and communication systems.

The user programs both the frequency and the phase of the output banks through nF[1:0] and DS[1:0] pins. The adjustable phase feature allows the user to skew the outputs to lead or lag the reference clock. Connect any one of the outputs to the feedback input to achieve different reference frequency multiplication and division ratios.

A passion for performance. The devices also feature split output bank power supplies that

enable banks 1 & 2, bank 3, and bank 4 to operate at a different power supply levels. The ternary PE/HD pin controls the synchronization of output signals to either the rising or the falling edge of the reference clock and selects the drive strength of the output buffers. The UT7R995 and UT7R995C both interface to a digital clock while the UT7R995C will also interface to a quartz crystal.

Figure 2. UT7R995 & UT7R995C Block Diagram

### **1.0 DEVICE CONFIGURATION:**

The outputs of the UT7R995/C can be configured to run at frequencies ranging from 6 MHz to 200 MHz. Each output bank has the ability to run at separate frequencies and with various phase skews. Furthermore, numerous clock division and multiplication options exist.

The following discussion and list of tables will summarize the available configuration options for the UT7R995/C. Tables 1 through 12, are relevant to the following configuration discussions.

Table 1. Feedback Divider Settings (N-factor) Table 2. Reference Divider Settings (R-Factor) Table 3. Output Divider Settings - Bank 3 (K-factor) Table 4. Output Divider Settings - Bank 4 (M-Factor) Table 5. Frequency Divider Summary Table 6. Calculating Output Frequency Settings Table 7. Frequency Range Select Table 8. Multiplication Factor (MF) Calculation Table 9. Signal Propagation Delays in Various Media Table 10: Output Skew Settings Table 11. PE/HD Settings Table 12. Power Supply Constraints

### 1.1 Divider Configuration Settings:

The feedback input divider is controlled by the 3-level DS[1:0] pins as indicated in Table 1 and the reference input divider is controlled by the 3-level  $\overline{PD}/DIV$  pin as indicated in Table 2. Although the Reference divider will continue to operate when the UT7R995/C is in the standard TEST mode of operation, the Feedback Divider will not be available.

### Table 1: Feedback Divider Settings (N-factor)

| DS[1:0] | Feedback Input<br>Divider - (N) | Permitted Output<br>Divider (K or M)<br>Connected to FB |

|---------|---------------------------------|---------------------------------------------------------|

| LL      | 2                               | 1 or 2                                                  |

| LM      | 3                               | 1                                                       |

| LH      | 4                               | 1, 2, or 4                                              |

| ML      | 5                               | 1 or 2                                                  |

| MM      | 1                               | 1, 2, or 4                                              |

| MH      | 6                               | 1 or 2                                                  |

| HL      | 8                               | 1 or 2                                                  |

| HM      | 10                              | 1                                                       |

| HH      | 12                              | 1                                                       |

| Table 2: Reference | e Divider | Settings | ( <i>R-factor</i> ) |

|--------------------|-----------|----------|---------------------|

|--------------------|-----------|----------|---------------------|

| PD/DIV           | Operating Mode   | Reference Input<br>Divider - ( <i>R</i> ) |

|------------------|------------------|-------------------------------------------|

| LOW <sup>1</sup> | Powered Down     | Not Applicable                            |

| MID              | Normal Operation | 2                                         |

| HIGH             | Normal Operation | 1                                         |

Notes:

1. When  $\overline{PD}/DIV = LOW$ , the device enters power-down mode.

In addition to the reference and feedback dividers, the UT7R995/C includes output dividers on Bank 3 and Bank 4, which are controlled by 3F[1:0] and 4F[1:0] as indicated in Tables 3 and 4, respectively.

Table 3: Output Divider Settings - Bank 3 (K-factor)

| <b>3F(1:0)</b>     | Bank 3 Output Divider - (K) |

|--------------------|-----------------------------|

| LL                 | 2                           |

| HH                 | 4                           |

| Other <sup>1</sup> | 1                           |

Notes:

1. These states are used to program the phase of the respective banks. Please see Equation 1 along with Tables 8 and 10.

| Table 4: Output Divider Settings - Bank 4 | ( <i>M</i> -factor) |

|-------------------------------------------|---------------------|

|-------------------------------------------|---------------------|

| 4F[1:0]            | Bank 4 Output Divider (M) |

|--------------------|---------------------------|

| LL                 | 2                         |

| Other <sup>1</sup> | 1                         |

### Notes:

1. These states are used to program the phase of the respective banks. Please see Equation 1 along with Tables 8 and 10.

Each of the four divider options and their respective settings are summarized in Table 5. By applying the divider options in Table 5 to the calculations shown in Table 6, the user determines the proper clock frequency for every output bank.

**Table 5: Frequency Divider Summary**

| Division<br>Factors | Available Divider Settings  |  |

|---------------------|-----------------------------|--|

| Ν                   | 1, 2, 3, 4, 5, 6, 8, 10, 12 |  |

| R                   | 1, 2                        |  |

| K                   | 1, 2, 4                     |  |

| М                   | 1, 2                        |  |

| Configuration                   | Output Frequency                                    |                                   |                                   |  |

|---------------------------------|-----------------------------------------------------|-----------------------------------|-----------------------------------|--|

| Clock Output<br>Connected to FB | 1Q[1:0] <sup>1</sup><br>and<br>2Q[1:0] <sup>1</sup> | 3Q[1:0]                           | 4Q[1:0]                           |  |

| 1Qn or 2Qn                      | (N/R) * f <sub>XTAL</sub>                           | (N/R) * (1/K) * f <sub>XTAL</sub> | (N/R) * (1/M) * f <sub>XTAL</sub> |  |

| 3Qn                             | (N/R) * K * f <sub>XTAL</sub>                       | (N/R) * f <sub>XTAL</sub>         | (N/R) * (K/M) * f <sub>XTAL</sub> |  |

| 4Qn                             | (N/R) * M * f <sub>XTAL</sub>                       | $(N/R) * (M/K) * f_{XTAL}$        | (N/R) * f <sub>XTAL</sub>         |  |

**Table 6: Calculating Output Frequency Settings**

Notes:

1. These outputs are undivided copies of the VCO clock. Therefore, the formulas in this column can be used to calculate the nominal VCO operating frequency ( $f_{NOM}$ ) at a given reference frequency ( $f_{XTAL}$ ) and the divider and feedback configuration. The user must select a configuration and a reference frequency that will generate a VCO frequency that is within the range specified by FS pin. Please see Table 7.

### 1.2 Frequency Range and Skew Selection:

The PLL in the UT7R995/C operates within three nominal frequency ranges. Depending upon the desired PLL operating frequency, the user must define the state of the ternary FS control pin. Table 7 defines the required FS selections based upon the nominal PLL operating frequency ranges. Because the clock outputs on Bank 1 and Bank 2 do not include a divider option, they will always reflect the current frequency of the PLL. Reference the first column of equations in Table 6 to calculate the value of f<sub>NOM</sub> for any given feedback clock.

| FS | Nominal PLL Frequency Range (f <sub>NOM</sub> ) |  |  |

|----|-------------------------------------------------|--|--|

| L  | 24 to 50 MHz                                    |  |  |

| М  | 48 to 100MHz                                    |  |  |

| Н  | 96 to 200 MHz                                   |  |  |

**Table 7: Frequency Range Select**

Selectable output skew is in discrete increments of time unit  $(t_U)$ . The value of  $t_U$  is determined by the FS setting and the PLL's operating frequency  $(f_{NOM})$ . Use the following equation to calculate the time unit  $(t_U)$ :

Equation 1.

$$t_{u} = \frac{1}{(f_{NOM} * MF)}$$

The  $f_{NOM}$  term, which is calculated with the help of Table 6, must be compatible with the nominal frequency range selected by the FS signal as defined in Table 7. The multiplication factor (MF), also determined by FS, is shown in Table 8. The UT7R995/C output skew steps have a typical accuracy of +/-15% of the calculated time unit ( $t_{II}$ ).

After calculating the time unit  $(t_U)$  based on the nominal PLL frequency  $(f_{NOM})$  and multiplication factor (MF), the circuit designer plans routing requirements of each clock output and its respective destination receiver. With an understanding of signal propagation delays through a conductive medium (see Table 9), the designer specifies trace lengths which ensure a signal propagation delay that is equal to one of the  $t_U$  multiples show in Table 10. For each output bank, the  $t_U$  skew factors are selected with the tri-level, bank-specific, nF[1:0] pins.

**Table 8: MF Calculation**

| FS | MF | $f_{NOM}$ examples that result in a $t_U$ of 1.0ns |

|----|----|----------------------------------------------------|

| L  | 32 | 31.25 MHz                                          |

| М  | 16 | 62.5 MHz                                           |

| Н  | 8  | 125 MHz                                            |

| Table 9: | Signal | <b>Propagation</b> | <b>Delays</b> in | Various Media |

|----------|--------|--------------------|------------------|---------------|

|          |        |                    |                  |               |

| Medium                     | Propagation<br>Delay (ps/inch) | Dielectric<br>Constant |

|----------------------------|--------------------------------|------------------------|

| Air (Radio Waves)          | 85                             | 1.0                    |

| Coax. Cable (75% Velocity) | 113                            | 1.8                    |

| Coax. Cable (66% Velocity) | 129                            | 2.3                    |

| FR4 PCB, Outer Trace       | 140 - 180                      | 2.8 - 4.5              |

| FR4 PCB, Inner Trace       | 180                            | 4.5                    |

| Alumina PCB, Inner Trace   | 240 - 270                      | 8 - 10                 |

| nF[1:0]            | Skew<br>1Q[1:0], 2Q[1:0] | Skew<br>3Q[1:0]  | Skew<br>4Q[1:0]       |

|--------------------|--------------------------|------------------|-----------------------|

| LL <sup>1, 2</sup> | -4t <sub>U</sub>         | Divide by 2      | Divide by 2           |

| LM                 | -3t <sub>U</sub>         | -6t <sub>U</sub> | -6t <sub>U</sub>      |

| LH                 | -2t <sub>U</sub>         | -4t <sub>U</sub> | -4t <sub>U</sub>      |

| ML                 | -1t <sub>U</sub>         | -2t <sub>U</sub> | -2t <sub>U</sub>      |

| MM                 | Zero Skew                | Zero Skew        | Zero Skew             |

| MH                 | $+1t_{U}$                | $+2t_U$          | $+2t_{U}$             |

| HL                 | $+2t_{U}$                | +4t <sub>U</sub> | $+4t_U$               |

| HM                 | $+3t_{U}$                | +6t <sub>U</sub> | $+6t_{U}$             |

| HH <sup>2</sup>    | $+4t_{U}$                | Divide by 4      | Inverted <sup>3</sup> |

### Table 10: Output Skew Settings<sup>4</sup>

#### Notes:

1. nF[1:0] = LL disables bank specific outputs if TEST=MID and  $\overline{sOE}$  = HIGH. 2. When TEST=MID or HIGH, the Divide-by-2, Divide-by-4, and Inversionoptions function as defined in Table 9.

3. When 4Q[1:0] are set to run inverted (4F[1:0] = HH),  $\overline{\text{sOE}}$  disables these outputs HIGH when PE/HD = HIGH or MID,  $\overline{sOE}$  disables them LOW when PE/HD = LOW.

4. Skew accuracy is within +/-15% of  $n*t_{II}$  where "n" is the selected number of skew steps. Supplied as a design limit, but not tested or guaranteed.

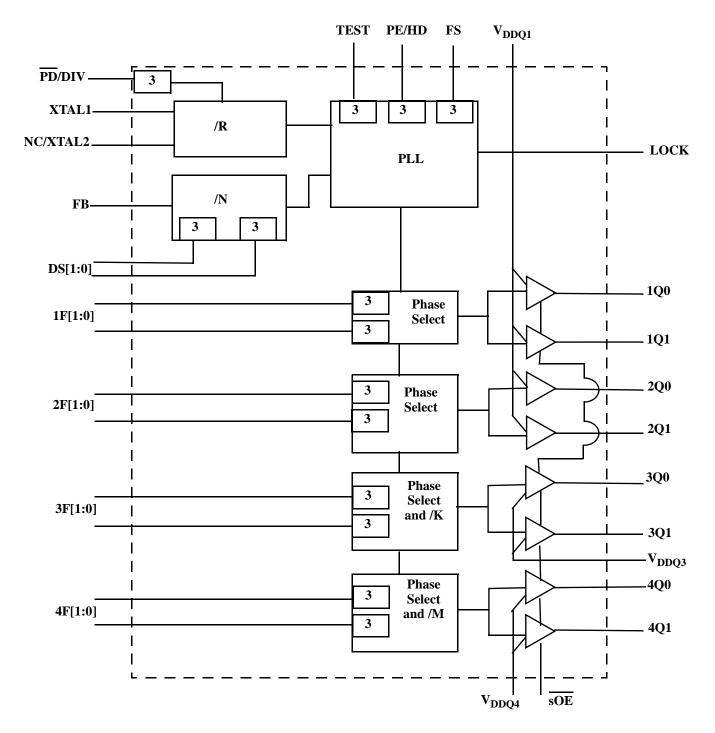

A graphical summary of Table 10 is shown in Figure 3. The drawing assumes that the FB input is driven by a clock output programmed with zero skew. Depending upon the state of the nF[1:0] pins the respective clocks will be skewed, divided, or inverted relative to the fedback output as shown in Figure 3.

### 1.3 Output Drive, Synchronization, and Power Supplies:

The UT7R995/C employs flexible output buffers providing the user with selectable drive strengths, independent power supplies, and synchronization to either edge of the reference input. Using the 3-level PE/HD pin, the user selects the reference edge synchronization and the output drive strength for all clock outputs. The options for edge synchronization and output drive strength selected by the PE/HD pin are listed in Table 11.

| Table 11 | l: PE/HD | Settings |

|----------|----------|----------|

|----------|----------|----------|

| PE/HD | Synchronization | Output Drive<br>Strength <sup>1</sup> |

|-------|-----------------|---------------------------------------|

| L     | Negative        | Low Drive                             |

| М     | Positive        | High Drive                            |

| Н     | Positive        | Low Drive                             |

5t<sub>U</sub> 6t<sub>U</sub>

Notes:

1. Please refer to "DC Parameters" section for I<sub>OH</sub>/I<sub>OL</sub> specifications.

Figure 3. Typical Outputs with FB Connected to a Zero-Skewed Output

When the outputs are configured for low drive operation, they will provide a minimum 12mA of drive current regardless of the selected output power supply. If the outputs are configured for high drive operation, they will provide a minimum 24mA of drive current under a 3.3V power supply and 20mA when powered from a 2.5V supply.

The UT7R995/C features split power supply buses for Banks 1 and 2, Bank 3, and Bank 4. These independent power supplies enable the user to obtain both 3.3V and 2.5V output signals from one UT7R995/C device. The core power supply ( $V_{DD}$ ) must run from a 3.3V power supply. Table 12 summarizes the various power supply options available with the UT7R995/C.

Table 12: Power Supply Constraints<sup>1</sup>

| V <sub>DD</sub> | V <sub>DD</sub> Q1 | V <sub>DD</sub> Q3 | V <sub>DD</sub> Q4 |  |

|-----------------|--------------------|--------------------|--------------------|--|

| 3.3V            | 3.3V or 2.5V       | 3.3V or 2.5V       | 3.3V or 2.5V       |  |

Notes:

1.  $V_{DD}Q1/3/4$  must not be set at a level higher than that of  $V_{DD}$ .

### 1.4 Reference Clock Interfaces

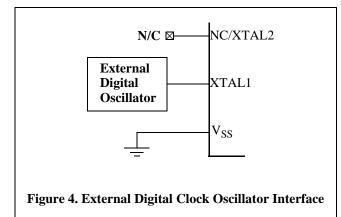

When an external, LVCMOS/LVTTL, digital clock is used to drive the UT7R995 and UT7R995C, the reference clock signal should drive the XTAL1 input of the RadClock, while the XTAL2 output should be left unconnected (see Figure 4). Note, for the UT7R995 only, the XTAL2 pin is defined as a noconnect.

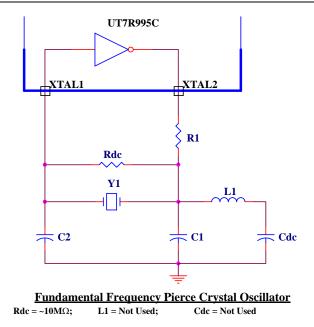

In addition to a digital clock reference, the UT7R995C can interface to a quartz crystal. When interfacing to a quartz crystal, XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier within the RadClock. This inverting amplifier provides the initial 180° phase shift of the reference clock whose frequency, and subsequent 180° phase shift, is set by the quartz crystal and its surrounding RLC network. Figure 5 shows a typical pierce-oscillator with tank-circuit that will support reliable startup of fundamental and odd-harmonic, ATcut, quartz crystals.

C2 is used to tune the circuit for stable oscillation. Typical values for C2 range from 30pF to 50pF.

R1 and C1 are selected to create a time constant that facilitates the fundamental frequency  $(f_F)$  of the quartz crystal as defined in equation 2.

Equation 2.

$$f_F = \frac{1}{(2\pi * RI * CI)}$$

As an example, selecting a value of  $100\Omega$  for R1 and 80pF for C1 would facilitate the reliable operation of a 20MHz, AT-cut, quartz crystal.

### Higher Frequency Pierce Crystal Oscillator

Rdc =  $\sim 10M\Omega$ ; Cdc =  $\sim 1.5nF$ ; C2 = Tuning capacitor similar to prior example

R1 and C1 are selected to create a time constant that facilitates the overtone frequency ( $f_{OT}$ ) of the quartz crystal as shown in equation 3.

Equation 3.

$$f_{OT} = \frac{1}{(2\pi * R1 * C1)}$$

Additionally, L1 is selected such that its relationship with C1 facilitates a frequency falling between the fundamental frequency ( $f_{\rm F}$ ) and the specified overtone frequency ( $f_{\rm OT}$ ) of the quartz crystal as shown in equation 4.

Equation 4.

$$f_M = \frac{1}{\left(2\pi * \sqrt{L1 * C1}\right)}$$

As an example, selecting the following component values will result in a 50MHz Pierce Crystal Oscillator based upon an 3rd overtone, AT-cut, quartz crystal having a fundamental frequency of 16.6666MHz.

| $\mathbf{Rdc} = 10\mathbf{M}\Omega;$ | Cdc = 1.5nF;     | C2 = 30pF;  |

|--------------------------------------|------------------|-------------|

| $\mathbf{R1} = 50\Omega;$            | C1 = 55pF;       | L1 = 300 nH |

| f <sub>F</sub> = 16.6666MHz;         | $f_{OT} = 50MHz$ |             |

F

Figure 5. Pierce Crystal Oscillator with Tank Circuit

## 2.0 RADIATION HARDNESS

| Parameter                                                                     | Limit  | Units                   |

|-------------------------------------------------------------------------------|--------|-------------------------|

| Total Ionizing Dose (TID)                                                     | >1E6   | rads(Si)                |

| Single Event Latchup (SEL) <sup>1, 2</sup>                                    | >109   | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Upset (SEU) LET Threshold <sup>3, 4</sup>                  | >109   | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Transient (SET) LET Threshold (@ 50MHz; FS=L) <sup>5</sup> | >74    | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence                                                               | 1.0E14 | n/cm <sup>2</sup>       |

## **Table 13: Radiation Hardness Design Specifications**

Notes:

1. The UT7R995/C are latchup immune to particle LETs >109 MeV-cm<sup>2</sup>/mg. 2. Worst case temperature and voltage of  $T_C = +125^{\circ}C$ ,  $V_{DD} = 3.6V$ ,  $V_{DD}Q1/Q3/Q4 = 3.6V$  for SEL. 3. Worst case temperature and voltage of  $T_C = +25^{\circ}C$ ,  $V_{DD} = 3.0V$ ,  $V_{DD}Q1/Q3/Q4 = 3.0V$  for SEU. 4. All SEU data specified in this datasheet is based on the storage elements used in the UT7R995/C. 5. For characterization data on the UT7R995/C SET performance over allowable operating ranges, please contact the factory.

### **3.0 PIN DESCRIPTION**

| Flatpack<br>Pin No. | Name              | I/O | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|-------------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37                  | XTAL1             | Ι   | LVTTL   | <b>Primary reference clock input.</b> When interfacing a single-ended reference clock to the UT7R995 or UT7R995C, this input must be driven by an LVTTL/LVCMOS clock source.<br>If a quartz crystal is used as the reference clock source (UT7R995C only), the second pin on the crystal must be connected to XTAL2. If a singled ended reference clock is supplied to this pin, then XTAL2 should be left unconnected. |

|                     | N/C               |     |         | No Connect. UT7R995 Only.                                                                                                                                                                                                                                                                                                                                                                                               |

| 36                  | XTAL2             | 0   | N/A     | <b>Feedback output from the on-board crystal oscillator.</b> When a crystal is used to supply the reference clock for the UT7R995C, this pin must be connected to the second terminal of the quartz crystal. If a single-ended reference clock is supplied to XTAL1, then this output should be left unconnected.                                                                                                       |

| 13                  | FB                | Ι   | LVTTL   | <b>Feedback input for the PLL.</b> When FB is not driven by an active clock output the PLL will run to its maximum frequency, unless the device is placed in power-down.                                                                                                                                                                                                                                                |

| 28                  | TEST <sup>1</sup> | Ι   | 3-Level | <b>Built-in test control signal.</b> When Test is set to the <b>MID</b> or <b>HIGH</b> level, it disables the PLL and the XTAL1 reference frequency is driven to all outputs (except for the conditions described in note 1). Set Test <b>LOW</b> for normal operation.                                                                                                                                                 |

| Flatpack<br>Pin No.                | Name    | I/O | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------------------|---------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3                                  | SOE     | Ι   | LVTTL   | Synchronous Output Enable. The sOE input is used to synchronously enable/<br>disable the output clocks. Each clock output that is controlled by the sOE pin is<br>synchronously enabled/disabled by the individual output clock. When HIGH, sOE<br>disables all clocks except 2Q0 and 2Q1. When disabled, 1Q0, 1Q1, 3Q0, and 3Q1<br>will always enter a LOW state when PE/HD is MID or HIGH, and they will disable<br>into a HIGH state when PE/HD is LOW.         The disabled state of 4Q0 and 4Q1 is dependent upon the state of PE/HD and 4F[1:0].<br>The following table illustrates the disabled state of bank 4 outputs as they are<br>controlled by the state of PE/HD and 4F[1:0]. <u>PE/HD</u> <u>4F[1:0]*</u> <u>4Q0</u> <u>4Q1</u> LOW       HH       LOW       LOW         MID       HH       HIGH       HIGH         +IIGH       HIGH       HIGH       *All other combinations of 4F[1:0] will result in 4Q0 and 4Q1 disabling into<br>a LOW state when PE/HD is MID or HIGH, and they will disable into a<br>HIGH state when PE/HD is LOW.         When TEST is held at the MID level and sOE is HIGH, the nF[1:0] pins act as<br>individual output enable/disable controls for each output bank, excluding bank 2.<br>Setting both nF[1:0] signals LOW disables the corresponding output bank.         Set sOE LOW to place the UT7R995/C RadClock <sup>TM</sup> outputs into their normal<br>operating modes. |  |  |  |

| 1, 2, 24,<br>25, 26, 27,<br>47, 48 | nF[1:0] | Ι   | 3-Level | <b>Output divider and phase skew selection for each output bank.</b><br>Please see Tables 3, 4, 5, 6, and 9 for a complete explanation of the nF[1:0] control functions and their effects on output frequency and skew.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 46                                 | FS      | Ι   | 3-Level | VCO operating frequency range selection.<br>Please see Tables 7 and 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 8, 9, 17,<br>18, 31, 32,<br>41, 42 | nQ[1:0] | 0   | LVTTL   | <b>Four clock banks of two outputs each.</b><br>Please see Table 6 for frequency settings and Table 9 for skew settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 22, 23                             | DS[1:0] | Ι   | 3-Level | <b>Feedback input divider selection.</b><br>Please see Table 1 for a summary of the feedback input divider settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 5                                  | PE/HD   | Ι   | 3-Level | Positive/negative edge control and high/low output drive strength selection. The PE portion of this pin controls which edge of the reference input synchronizes the clock outputs. The HD portion of this pin controls the drive strength of the output clock buffers. The following table summarizes the effects of the PE/HD pin during normal operation.         PE/HD       Synchronization       Output Drive Strength         LOW       Negative Edge       Low Drive         MID       Positive Edge       High Drive         HIGH       Positive Edge       Low Drive         Low drive strength outputs provide 12mA of drive strength while the high drive condition results in 24mA of current drive. Output banks operating from a 2.5V power supply guarantee a high drive of 20mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Flatpack<br>Pin No.                                               | Name                            | I/O | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------------|---------------------------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4                                                                 | PD/DIV                          | I   | 3-Level | <b>Power down and reference divider control.</b> This dual function pin controls the power down operation and selects the input reference divider. Holding the pin low during power up ensures clean RadClock startup that is independent of the behavior of the reference clock. The pin may also be driven low at any time to force a reset to the PLL. The following table summarizes the operating states controlled by the PD/DIV pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                                   |                                 |     |         | PD/DIV         Operating Mode         Input Reference Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                                   |                                 |     |         | LOW Powered Down N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                   |                                 |     |         | MID     Normal Operation     ÷ 2       MICH     Normal Operation     ÷ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                   |                                 |     |         | HIGH Normal Operation ÷ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 20                                                                | LOCK                            | 0   | LVTTL   | PLL lock indication signal. A HIGH state indicates that the PLL is in a locked condition. A LOW state indicates that the PLL is not locked and the outputs may not be synchronized to the input. As the following table indicates, the level of phase alignment between XTAL1 and FB that will cause the LOCK pin to change states is dependent upon the frequency range selected by the FS input.         FS       LOCK Resolution         L       1.6ns typical         M       1.6ns typical         H       800ps typical         *** Note: The LOCK pin can only be considered as a valid output when the RadClock is in a normal mode of operation (e.g. PD/DIV != LOW, TEST = LOW, and a valid reference clock is supplied to the XTAL1 input). Until these conditions are met, RadClock is not in a normal operating mode and the LOCK pin may be HIGH or LOW and therefore should not be used in making any logical decisions until the device is in a normal operating mode. Reference the t <sub>LOCK</sub> parameter in the AC timing specification to determine the delay for the LOCK pin to become valid HIGH following a stable input reference clock and the application of a clock to the FB input. |  |  |

| 43                                                                | V <sub>DD</sub> Q4 <sup>2</sup> | PWR | Power   | Power supply for Bank 4 output buffers.<br>Please see Table 12 for supply level constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 7                                                                 | V <sub>DD</sub> Q3 <sup>2</sup> | PWR | Power   | <b>Power supply for Bank 3 output buffers.</b><br>Please see Table 12 for supply level constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 19, 30                                                            | V <sub>DD</sub> Q1 <sup>2</sup> | PWR | Power   | <b>Power supply for Bank 1 and Bank 2 output buffers.</b><br>Please see Table 12 for supply level constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 6, 12, 14,<br>35, 38                                              | V <sub>DD</sub> <sup>2</sup>    | PWR | Power   | <b>Power supply for internal circuitry.</b><br>Please see Table 12 for supply level constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 10, 11, 15,<br>16, 21, 29,<br>33, 34, 39,<br>40, 44, 45<br>Notes: | V <sub>SS</sub>                 | PWR | Power   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

### Notes:

1. When TEST = MID and  $\overline{OE}$  = HIGH, the PLL remains active with nF[1:0] = LL functioning as an output disable control for individual output banks. Skew selections remain in effect unless nF[1:0] = LL.

<sup>2.</sup> A bypass capacitor  $(0.1\mu F)$  should be placed as close as possible to each positive power pin (<0.2"). An additional 1 $\mu$ F capacitor should be located within 0.2" of the output bank power supplies ( $V_{DD}Q1$ ,  $V_{DD}Q3$ , and  $V_{DD}Q4$ ). If these bypass capacitors are not close to the pins, their high frequency filtering characteristics will be cancelled by the parasitic inductance of the traces. Additionally, it is recommend that wide traces (0.025" or wider) be used when connecting the decoupling capacitors to their respective power pins on the RadClock.

## 4.0 ABSOLUTE MAXIMUM RATINGS:<sup>1</sup>

## (Referenced to V<sub>SS</sub>)

| Symbol                                   | Description                                  | Limits                        | Units |

|------------------------------------------|----------------------------------------------|-------------------------------|-------|

| V <sub>DD</sub>                          | Core Power Supply Voltage                    | -0.3 to 4.0                   | V     |

| $V_{DD}Q1$ , $V_{DD}Q3$ , and $V_{DD}Q4$ | Output Bank Power Supply Voltage             | -0.3 to 4.0                   | V     |

| V <sub>IN</sub>                          | Voltage Any Input Pin                        | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| V <sub>OUT</sub>                         | Voltage Any Clock Bank Output                | -0.3 to $V_{DD}Qn + 0.3$      | V     |

| V <sub>O</sub>                           | Voltage on XTAL2 and LOCK Outputs            | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| II                                       | DC Input Current                             | <u>+</u> 10                   | mA    |

| P <sub>D</sub>                           | Maximum Power Dissipation                    | 1.5                           | W     |

| T <sub>STG</sub>                         | Storage Temperature                          | -65 to +150                   | °C    |

| TJ                                       | Maximum Junction Temperature <sup>2</sup>    | +150                          | °C    |

| $\Theta_{ m JC}$                         | Thermal Resistance, Junction to Case         | 15                            | °C/W  |

| ESD <sub>HBM</sub>                       | ESD Protection (Human Body Model) - Class II | 3000                          | V     |

### Notes:

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating 2. Maximum junction temperature may be increased to +175°C during burn-in and steady-static life.

## 5.0 RECOMMENDED OPERATING CONDITIONS:

| Symbol                                   | Description                                 | Limits                  | Units |

|------------------------------------------|---------------------------------------------|-------------------------|-------|

| V <sub>DD</sub>                          | Core Operating Voltage                      | 3.0 to 3.6              | V     |

| $V_{DD}Q1$ , $V_{DD}Q3$ , and $V_{DD}Q4$ | Output Bank Operating Voltage               | 2.25 to 3.6             | V     |

| V <sub>IN</sub>                          | Voltage Any Configuration and Control Input | 0 to V <sub>DD</sub>    | V     |

| V <sub>OUT</sub>                         | Voltage Any Bank Output                     | 0 to V <sub>DD</sub> Qn | V     |

| T <sub>C</sub>                           | Case Operating Temperature                  | -55 to +125             | °C    |

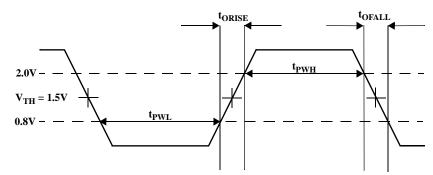

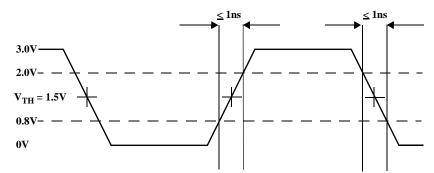

### 6.0 DC INPUT ELECTRICAL CHARACTERISTICS (Pre- and Post-Radiation)\*

| Symbol                           | Description                                            | Conditio                                                                                                 | ns                    | Min.                     | Max.                  | Units |

|----------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|-----------------------|-------|

| $V_{IH}^{4}$                     | High-level input voltage<br>(XTAL1, FB and sOE inputs) |                                                                                                          |                       | 2.0                      |                       | V     |

| $V_{IL}^{4}$                     | Low-level input voltage<br>(XTAL1, FB and sOE inputs)  |                                                                                                          |                       |                          | 0.8                   | V     |

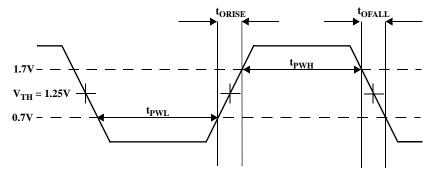

| V <sub>IHH</sub> <sup>1,3</sup>  | High-level input voltage                               |                                                                                                          |                       | V <sub>DD</sub> - 0.6    |                       | v     |

| V <sub>IMM</sub> <sup>1, 3</sup> | Mid-level input voltage                                |                                                                                                          |                       | V <sub>DD</sub> ÷2 - 0.3 | $V_{DD} \div 2 + 0.3$ | v     |

| V <sub>ILL</sub> <sup>1, 3</sup> | Low-level input voltage                                |                                                                                                          |                       |                          | 0.6                   | v     |

| I <sub>IL</sub>                  | Input leakage current<br>(XTAL1, FB and sOE inputs)    | $V_{IN} = V_{DD}$ or $V_{SS}$ ; $V_{DD} = Max$                                                           | -5                    | 5                        | μΑ                    |       |

|                                  |                                                        | HIGH, $V_{IN} = V_{DD}$                                                                                  |                       |                          | 200                   | μΑ    |

| $I_{3L}^{1}$                     | 3-Level input DC current                               | MID, $V_{IN} = V_{DD}/2$                                                                                 |                       | -50                      | 50                    | μΑ    |

|                                  |                                                        | LOW, $V_{IN} = V_{SS}$                                                                                   |                       | -200                     |                       | μΑ    |

|                                  |                                                        | $V_{DD} = V_{DD}Qn = +3.0V;$                                                                             | $T_C = +25^{\circ}C$  |                          | 100                   | μΑ    |

| I <sub>DDPD</sub>                | Power-down current                                     | TEST & $\overline{\text{sOE}}$ = HIGH;<br>XTAL1, $\overline{\text{PD}}$ /DIV, FB, FS, & PE/<br>HD = LOW; | $T_C = +125^{\circ}C$ |                          | 150                   | μΑ    |

|                                  |                                                        | All other inputs are floated;<br>Outputs are not loaded                                                  | $T_C = -55^{\circ}C$  |                          | 4.5                   | mA    |

| C <sub>IN-2L</sub> <sup>2</sup>  | Input pin capacitance<br>2-level inputs                | f = 1MHz @ 0V; V <sub>DD</sub> = Max                                                                     |                       | 8                        | .5                    | pF    |

| C <sub>IN-3L</sub> <sup>2</sup>  | Input pin capacitance<br>3-level inputs                | f = 1MHz @ 0V; V <sub>DD</sub> = Max                                                                     |                       | 15                       |                       | pF    |

$(V_{DD} = +3.3V \pm 0.3V; T_C = -55^{\circ}C \text{ to } +125^{\circ}C)$  (For "W" screening,  $T_C = -40^{\circ}C \text{ to } +125^{\circ}C$ )

Notes:

\* Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to a TID level of 1.0E6 rad(Si).

1. These inputs are normally wired to V<sub>DD</sub>, V<sub>SS</sub>, or left unconnected. Internal termination resistors bias unconnected inputs to V<sub>DD</sub>/2 ± 0.3V. The 3-level inputs include: TEST, PD/DIV, PE/HD, FS, nF[1:0], DS[1:0].

Capacitance is measured for initial qualification and when design changes may affect the input/output capacitance. Capacitance is measured between the designated terminal and V<sub>SS</sub> at a frequency of 1MHz and a signal amplitude of 50mV rms maximum.

3. Pin FS is guaranteed by functional testing.

4. For pin FB, this specification is supplied as a design limit, but is neither guaranteed nor tested.

### 7.0 DC OUTPUT ELECTRICAL CHARACTERISTICS (Pre- and Post-Radiation)\*

| Symbol                                   | Description                  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min.                                        | Max.    | Units |     |    |

|------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------|-------|-----|----|

|                                          | Output low voltage           | $I_{OL} = 12mA$ (PE/HD = LOW or HIGH);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             | 0.4     | v     |     |    |

| V <sub>OL</sub>                          |                              | I <sub>OL</sub> = 20mA (PE/HD = MID); (Pins: nQ[1:0])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |         | 0.4   | v   |    |

|                                          |                              | $I_{OL} = 2mA$ (Pins: LOCK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |         | 0.4   | v   |    |

|                                          |                              | $I_{OH}$ = -6mA (PE/HD=LOWorHIGH); (Pins: nQ[1:0]; $V_{DD}Qn$ = +2.25V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             | 2.0     |       | v   |    |

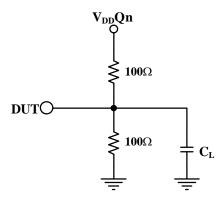

| V <sub>OH</sub> High-level ou<br>voltage |                              | $I_{OH} = -10$ mA (PE/HD=LOWor HIGH); (I<br>= +2.375V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pins: nQ[1:0]; V <sub>DD</sub> Qn           | 2.0     |       | V   |    |