# MSTM-S3-T2 Stratum 3 Timing Module

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040 www.conwin.com

### **Application**

The Connor-Winfield MSTM-S3-T2 Simplified Control Timing Module acts as a complete system clock module for Stratum 3 timing applications in accordance with GR-1244, Issue 2 and GR-253, Issue 3.

Connor Winfield's Stratum 3 timing modules helps reduce the cost of your design by minimizing your development time and maximizing your control of the system clock with our simplified design.

#### **Features**

- 5V Miniature Timing Module

- Redundant 8kHz References

- 40 sec., Filtered, Hold Over History

- .37 ppm Hold Over During Initial 24 Hours

- 4.6 ppm Free Run Accuracy

- Hitless Reference Switching

| Bulletin  | TM053     |

|-----------|-----------|

| Page      | 1 of 20   |

| Revision  | 00        |

| Date      | 14 MAY 03 |

| Issued By | MBatts    |

### **General Description**

The Connor-Winfield Stratum 3 Simplified Control Timing Module acts as a complete system clock module for general Stratum 3 timing applications.

Full external control input allows for selection and monitoring of any of four possible operating states: 1) Holdover, 2) External Reference #1, 3) External Reference #2, and 4) Free Run. Table #1 illustrates the control signal inputs and corresponding operational states.

In the absence of External Control Inputs (A,B), the MSTM enters the Free Run mode and signals an External Alarm. The MSTM will enter other operating modes upon application of a proper control signal. Mode 1 operation (A=1, B=0) results in an output signal that is phase locked to the External Reference Input #1. Mode 2 operation (A=0, B=1) results in an output signal that is phase locked to External Reference Input #2. Holdover mode operation (A=1, B=1) results in an output signal at or near the frequency as determined by the latest (last) locked-signal input values and the holdover performance of the MSTM. Free Run mode operation (A=0, B=0) is a guaranteed output of 4.6 ppm of the nominal frequency.

Alarm signals are generated at the Alarm Output during Holdover and Free Run operation. Alarm Signals are also generated by loss-of-lock, loss of Reference, and by a Tune-Limit indication from the PLL. A Tune-Limit alarm signal indicates that the OCXO tuning voltage is approaching within 10% the limits of its lock capability and that the External Reference Input may be erroneous. A high level indicates an alarm condition. Real-time indication of the operational mode is available at unique operating mode outputs on pins 1-4.

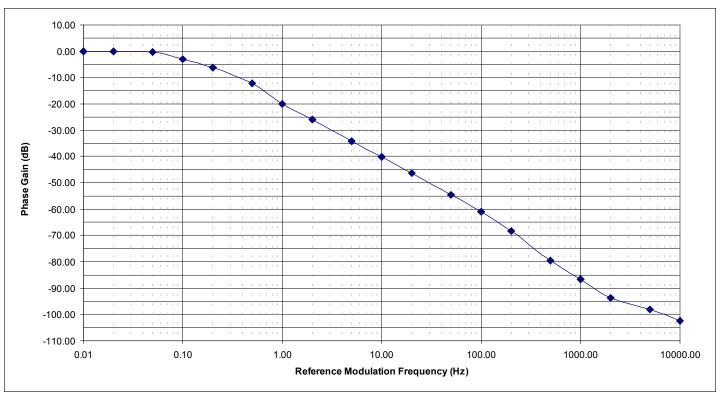

Control loop 0.1 Hz filters effectively attenuate any reference jitter, smooth out phase transients, comply with wander transfer and jitter tolerances.

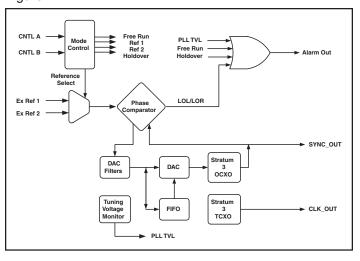

#### **Functional Block Diagram**

#### Figure 1

#### **Function Control Table**

Table 1

| CNTL<br>A | CNTL<br>B | Operation Mode |                | Ref 1 | Ref 2 | Hold Over | Free Run | PLL_TVL | Alarm Out |

|-----------|-----------|----------------|----------------|-------|-------|-----------|----------|---------|-----------|

| 0         | 0         | Free Run       | (Default Mode) | 0     | 0     | 0         | 1        | 0       | 1         |

|           |           | External       | Normal         | 1     | 0     | 0         | 0        | 0       | 0         |

| 1         | 0         | Reference      | Tune Limit     | 1     | 0     | 0         | 0        | 1       | 1         |

|           |           | #1             | LOR + LOL      | 1     | 0     | 0         | 0        | 0       | 1         |

|           |           | External       | Normal         | 0     | 1     | 0         | 0        | 0       | 0         |

| 0         | 1         | Reference      | Tune Limit     | 0     | 1     | 0         | 0        | 1       | 1         |

|           |           | #2             | LOR + LOL      | 0     | 1     | 0         | 0        | 0       | 1         |

| 1         | 1         | Hold           | Over           | 0     | 0     | 1         | 0        | 0       | 1         |

#### **Absolute Maximum Rating**

Table 2

| Symbol          | Parameter            | Minimum | Nominal | Maximum               | Units  | Notes |

|-----------------|----------------------|---------|---------|-----------------------|--------|-------|

| V <sub>cc</sub> | Power Supply Voltage | -0.5    |         | 7.0                   | Volts  | 1.0   |

| V <sub>I</sub>  | Input Voltage        | -0.5    |         | V <sub>cc</sub> + 0.5 | Volts  | 1.0   |

| T <sub>s</sub>  | Storage Temperature  | -55     |         | 100                   | deg. C | 1.0   |

Data Sheet #: TM053 Page 2 of 20 Rev: 00 Date: 5 / 14 / 03

# **Recommended Operating Conditions**

#### Table 3

| Symbol             | Parameter                                                                  | Minimum | Nominal | Maximum         | Units | Notes |

|--------------------|----------------------------------------------------------------------------|---------|---------|-----------------|-------|-------|

| V <sub>cc</sub>    | Power supply voltage                                                       | 4.75    | 5.00    | 5.25            | Volts |       |

| V <sub>IH</sub>    | High level input voltage - TTL                                             | 2.0     |         | V <sub>cc</sub> | Volts |       |

| V <sub>IL</sub>    | Low level input voltage - TTL                                              | 0       |         | 0.8             | Volts |       |

| t <sub>in</sub>    | Input signal transition - TTL                                              |         |         | 250             | ns    |       |

| C <sub>IN</sub>    | Input capacitance                                                          |         |         | 15              | pF    |       |

| V <sub>OH</sub>    | High level output voltage, $I_{OH} = -4.0 \text{mA}, V_{CC} = \text{min}.$ | 2.4     |         | 5.25            | Volts | 2.0   |

| V <sub>OL</sub>    | Low level output voltage, $I_{OL} = 12.0 \text{ mA}, V_{CC} = \text{min}.$ |         |         | 0.4             | Volts |       |

| t <sub>TRANS</sub> | Clock out transition time                                                  |         | 4.0     |                 | ns    |       |

| t <sub>PULSE</sub> | 8kHz input reference pulse width( positive or negative)                    | 30      |         |                 | ns    |       |

| T <sub>OP</sub>    | Operating temperature                                                      | 0       |         | 70              | °C    |       |

## **Specifications**

#### Table 4

| Parameter                                     | Specifications                                  | Notes |

|-----------------------------------------------|-------------------------------------------------|-------|

| Frequency Range (SYNC_OUT)                    | 8 kHz to 125 MHz                                |       |

| Frequency Range (CLK_OUT)                     | 8 kHz to 51.84 MHz                              |       |

| Supply Current                                | 250 mA typical, 400 mA during warm-up (Maximum) |       |

| Timing Reference Inputs                       | Dual 8 kHz references                           | 3.0   |

| Jitter, Wander and Phase Transient Tolerances | GR-1244-CORE 4.2-4.4, GR-253-CORE 5.4.4.3.6     |       |

| Wander Generation                             | GR-1244-CORE 5.3, GR-253-CORE 5.4.4.3.2         |       |

| Wander Transfer                               | GR-1244-CORE 5.4                                |       |

| Jitter Generation                             | GR-1244-CORE 5.5, GR-253-CORE 5.6.2.3           |       |

| Jitter Transfer                               | GR-1244-CORE 5.5, GR-253-CORE 5.6.2.1           |       |

| Phase Transients                              | GR-1244-CORE 5.6, GR-253-CORE 5.4.4.3.3         |       |

| Free Run Accuracy                             | 4.6 ppm over T <sub>OP</sub>                    |       |

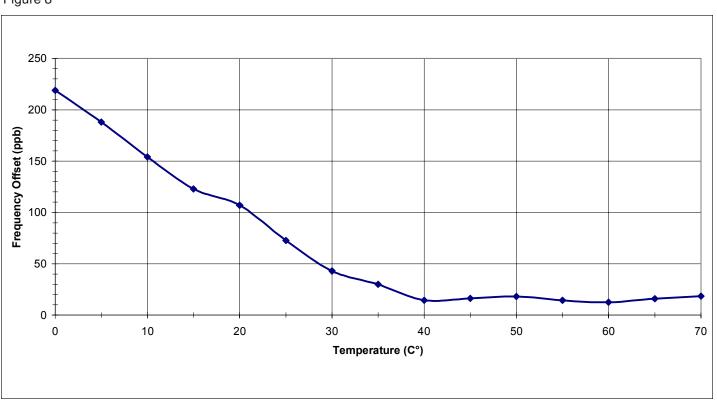

| Hold Over Stability                           | ±0.37 ppm for initial 24 hrs                    |       |

| Initial Offset                                | ±0.05 ppm                                       |       |

| Temperature                                   | ±0.28 ppm                                       |       |

| Drift                                         | ±0.04 ppm                                       |       |

| Maximum Hold Over History                     | 40 seconds                                      |       |

| Pull-in/ Hold-in Range                        | ±4.6 ppm minimum 5.0                            |       |

| Lock Time                                     | <100 sec.                                       |       |

| PLL_TVL Alarm Limit                           | Extreme 10% ranges of Pull-in/Hold-in Range     |       |

|                                               |                                                 |       |

#### NOTES:

- Stresses beyond those listed under Absolute Maximum Rating may cause damage to the device. Operation beyond Recommended Conditions is not implied.

- 2.0: Logic is 3.3V CMOS

- 3.0 GR-1244-CORE 3.2.1

- 4.0: Hold Over stability is the cumulative fractional frequency offset as described by GR-1244-CORE, 5.2

- 5.0: Pull-in Range is the maximum frequency deviation from nominal clock rate on the reference inputs to the timing module that can be overcome to pull into synchronization with the reference

Data Sheet #: TM053 Page 3 of 20 Rev: 00 Date: 5 / 14 / 03

### **Pin Description**

#### Table 5

| Pin # | Connection      | Description                                                                                                               |  |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------|--|

| 1     | HOLD OVER       | Indicator output. High output when Hold Over mode is selected by control pins.                                            |  |

| 2     | REF 1           | Indicator output. High output when Ref 1 mode is selected by control pins.                                                |  |

| 3     | REF 2           | Indicator output. High output when Ref 2 mode is selected by control pins.                                                |  |

| 4     | FREE RUN        | Indicator output. High output when Free Run mode is selected by control pins.                                             |  |

| 5     | GND             | Ground                                                                                                                    |  |

| 6     | ALARM _OUT      | Alarm output. High output if module is in Free Run, or Hold Over, or LOR, or PLL_TVL mode.                                |  |

| 7     | CNTL A          | Mode control input                                                                                                        |  |

| 8     | CNTL B          | Mode control input                                                                                                        |  |

| 9     | PLL_TVL         | Tuning Voltage Limit alarm output. High output when Sync_Out is near the extreme 10% ranges of the Pull-in/Hold-in range. |  |

| 10    | GND             | Ground                                                                                                                    |  |

| 11    | SYNC_OUT        | Primary timing output signal. Signal is synchronized to reference.                                                        |  |

| 12    | GND             | Ground                                                                                                                    |  |

| 13    | CLK_OUT         | Stratum 3 TCXO output (non-synchronized output, Frequency = SYNC_OUT)                                                     |  |

| 14    | GND             | Ground                                                                                                                    |  |

| 15    | EX_REF_2        | External Input Reference #2                                                                                               |  |

| 16    | GND             | Ground                                                                                                                    |  |

| 17    | EX_REF_1        | External Input Reference #1                                                                                               |  |

| 18    | V <sub>cc</sub> | +5V dc supply                                                                                                             |  |

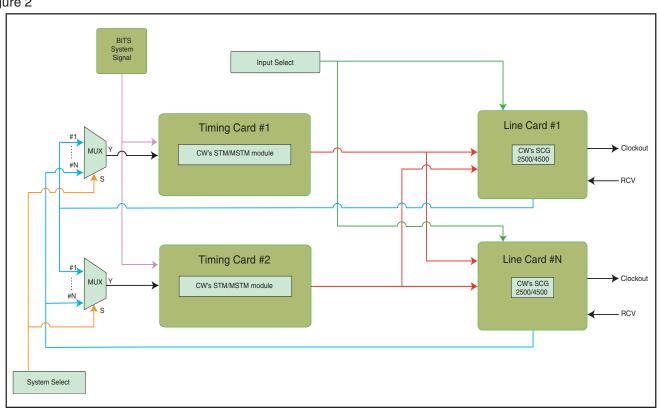

### **Typical Application**

Figure 2

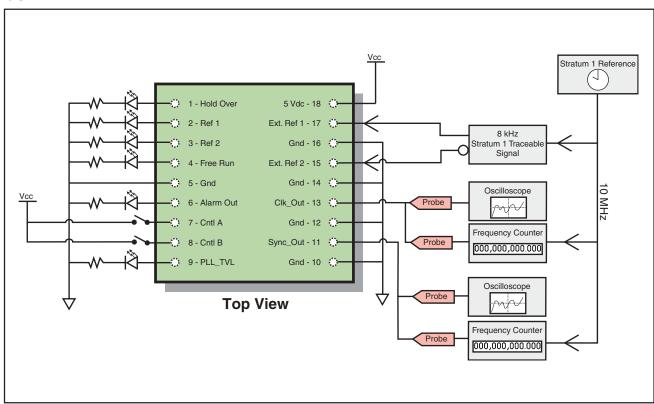

### **Typical Module Test Setup**

Figure 3

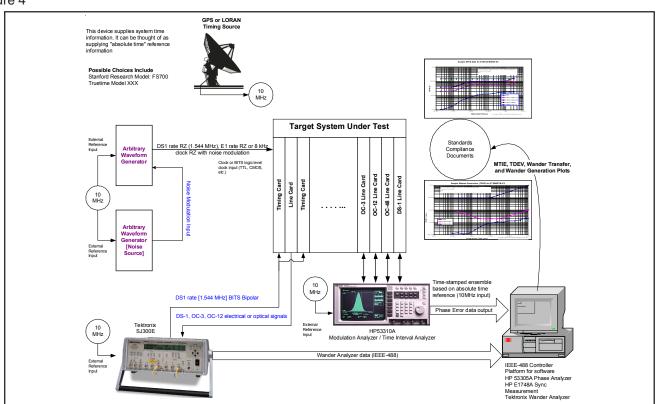

### **Typical System Test Setup**

Figure 4

Data Sheet #: TM053 Page 5 of 20 Rev: 00 Date: 5 / 14 / 03

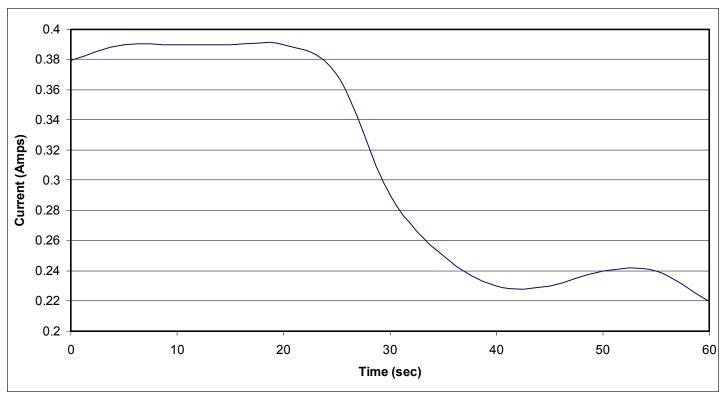

### **MSTM-S3-T2 Typical Current Draw**

Figure 5

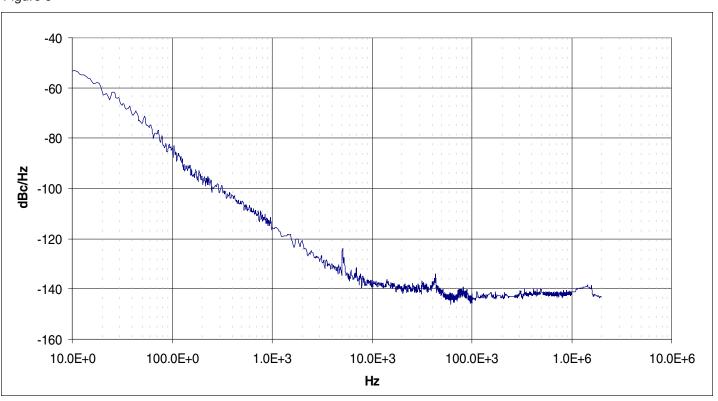

### **MSTM-S3-T2 Typical Phase Noise Plot**

Figure 6

### MSTM-S3-T2 Typical Phase Gain

Figure 7

### MSTM-S3-T2 Typical Hold Over Stability over Temperature

Figure 8

Data Sheet #: TM053 Page 7 of 20 Rev: 00 Date: 5 / 14 / 03

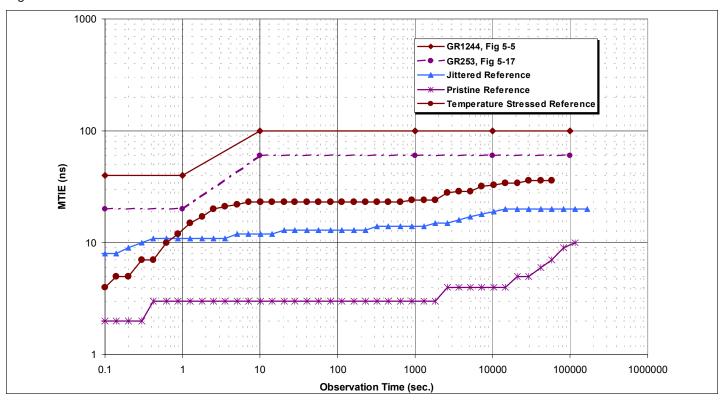

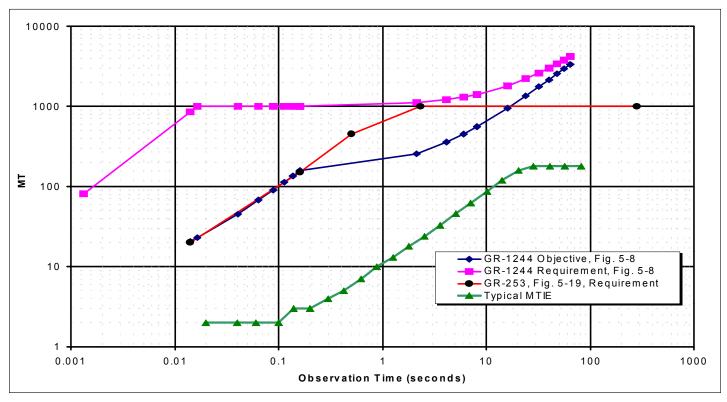

### **Typical Wander Generation MTIE**

Figure 9

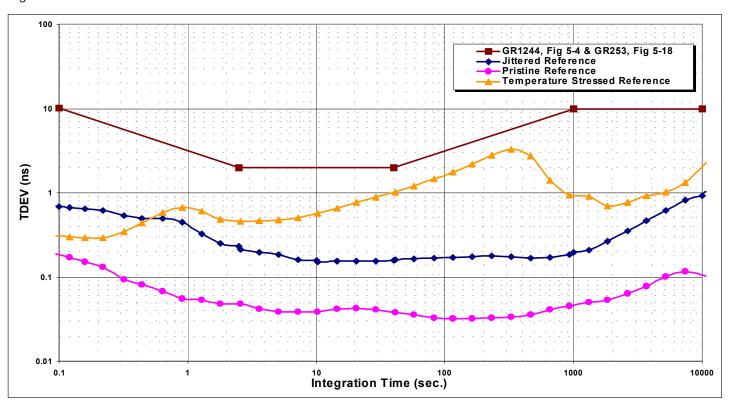

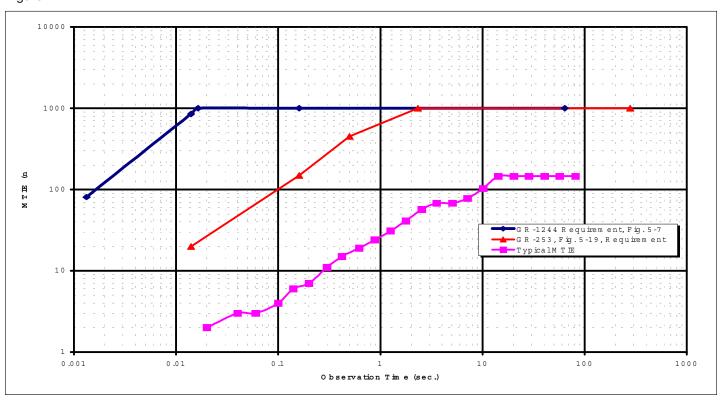

### **Typical Wander Generation TDEV**

Figure 10

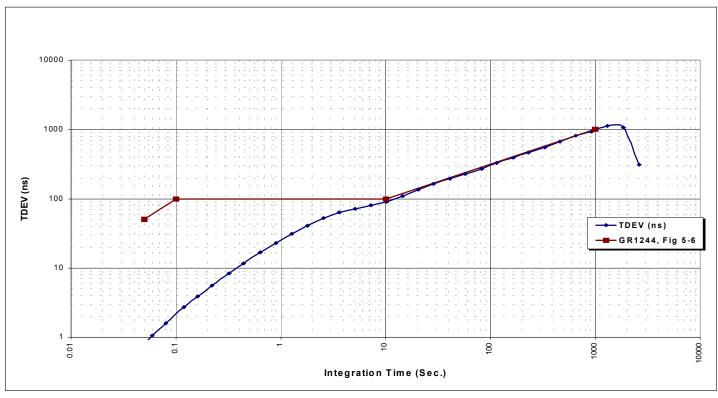

### **Typical Calibrated Wander Transfer TDEV**

Figure 11

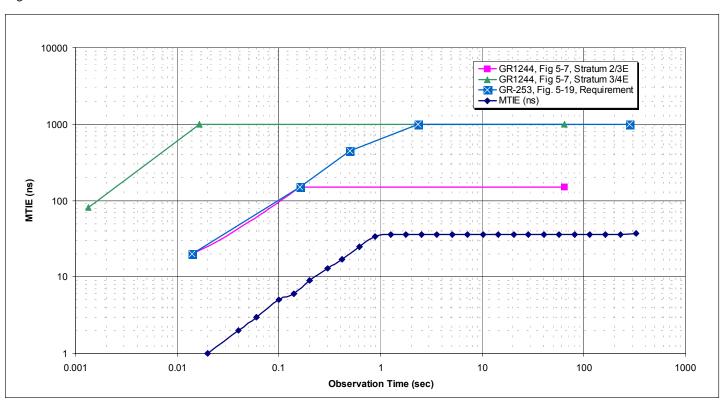

### **Typical Reference Switch MTIE**

Figure 12

Data Sheet #: TM053 Page 9 of 20 Rev: 00 Date: 5 / 14 / 03

### **Typical Entry Into Hold Over MTIE**

Figure 13

### **Typical Return from Hold Over MTIE**

Figure 14

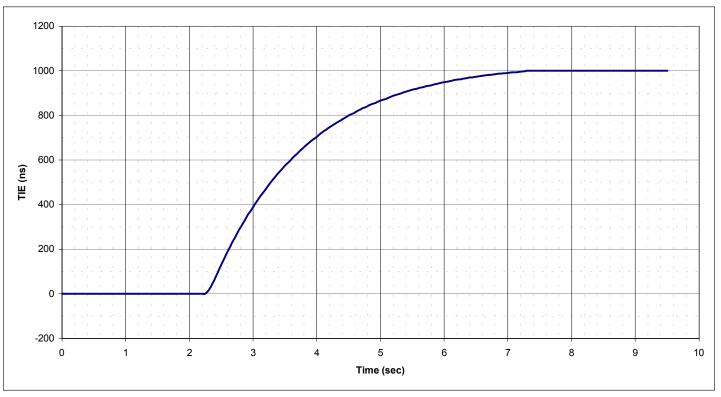

### **Typical 1us Phase Transient TIE**

Figure 15

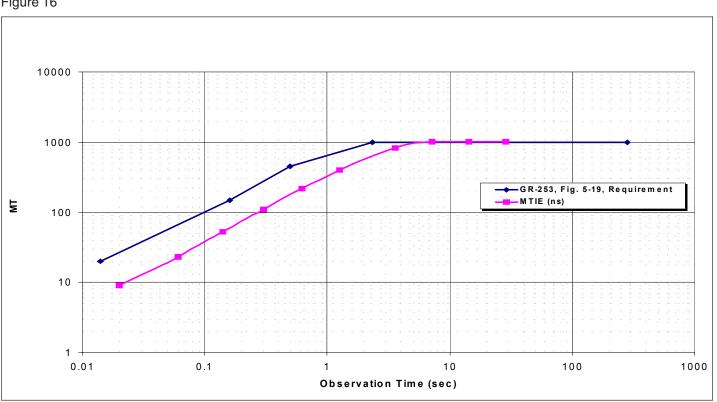

### **Typical Phase Transient MTIE**

Figure 16

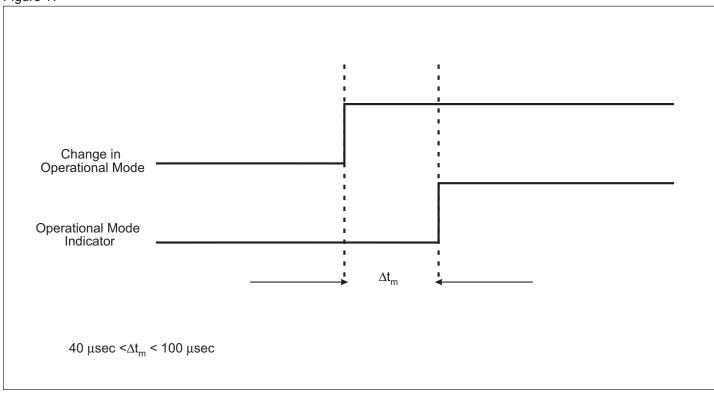

### **MSTM-S3-T2 Mode Indicator Delay**

Figure 17

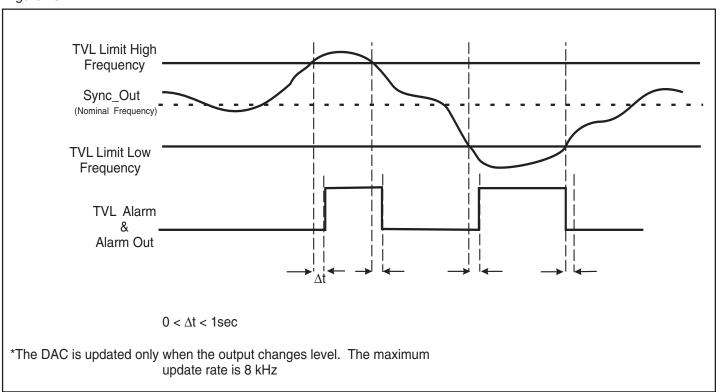

### **Tuning Voltage Limit Alarm Timing Diagram**

Figure 18

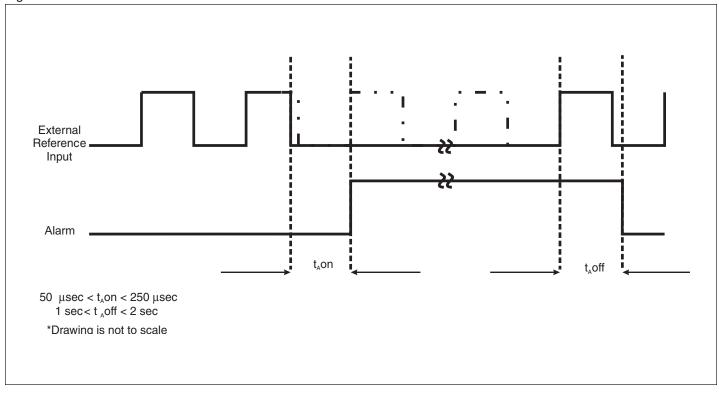

### **Loss of Reference Timing Diagram**

#### Figure 19

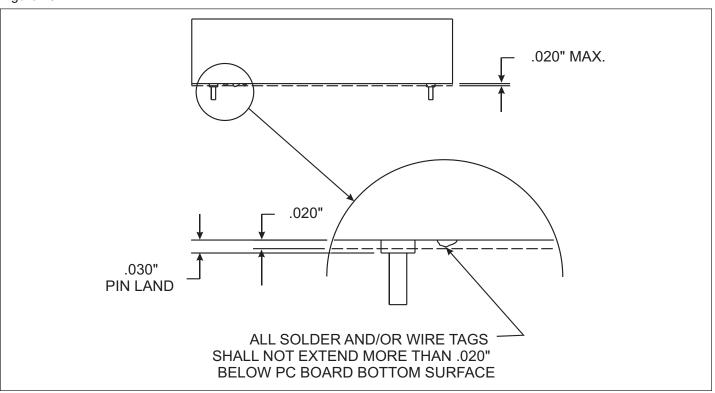

#### **Solder Clearance**

Figure 20

Date: 5 / 14 / 03

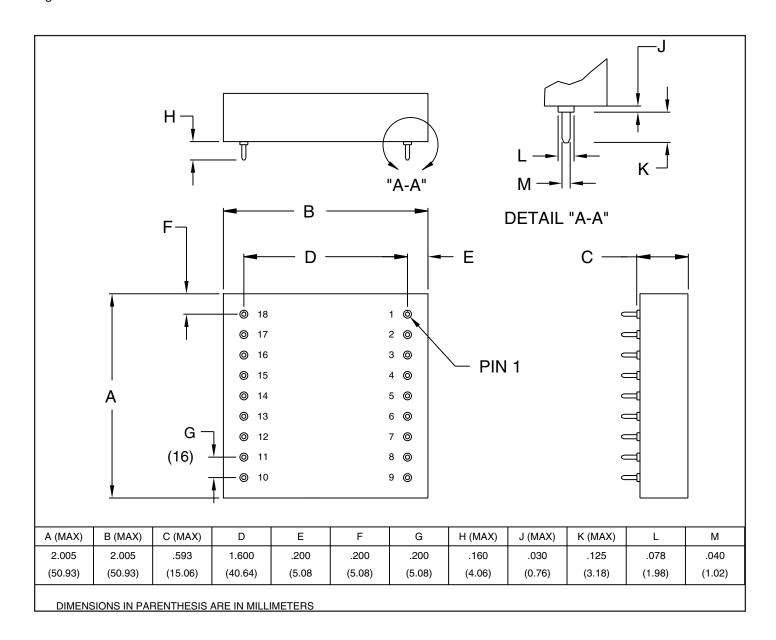

#### **MECHANICAL OUTLINE:**

The mechanical outline of the MSTM-S3-IP is shown in Figure 23. The board space required is 2.005" x 2.005" (max). The pins are .040" in diameter and are .160" (max) in length. The unit is spaced off the PCB by .035"(max) shoulders on the pins. Due to the height of the device it is recommended to have heat sensitive devices away where the air flow might not be blocked.

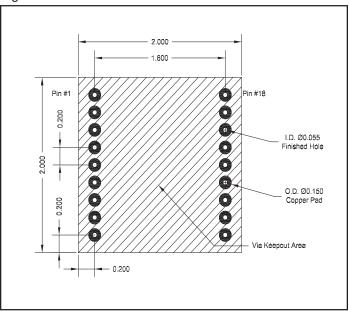

#### PAD ARRAY AND PAD SPACING:

The pins are arranged in a dual-in-line configuration as shown in Figure 16. There is .2" space between the pins in-line and each line is separated by 1.6". See Figures 21 & 23 and Table 6.

#### **PAD CONSTRUCTION:**

The recommended pad construction is shown in Figure 21. For the pin diameter of .040" a hole diameter of .055" is suggested for ease of insertion and rework. A pad diameter of .150" is also suggested for support. This leaves a spacing of .050" between the pads which is sufficient for most signal lines to pass through.

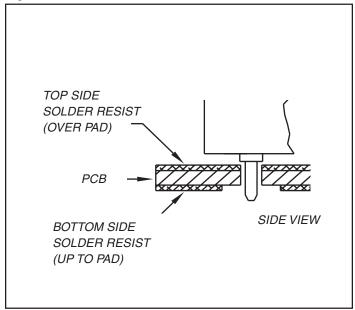

#### **SOLDER MASK:**

A solder mask is recommended to cover most the top pad to avoid excessive solder underneath the shoulder of the pin to avoid rework damage. See Table 6 and Figure 22.

#### **VIA KEEP OUT AREA:**

It is recommended that there be no vias or feed throughs underneath the main body of the module between the pins. It is suggested that the traces in this area be kept to a minimum and protected by a layer of solder mask. See Figure 21.

#### **GROUND AND POWER SUPPLY LINES:**

Power specifications will vary depending primarily on the temperature range. At wider temperature ranges starting at 0 to 70 deg. C., an ovenized oscillator, OCXO, will be incorporated. The turn-on current for an OCXO requires a peak current of about .4A for about a minute. The steady state current will the vary from 50-150 mA depending on the temperature. It is suggested to plan for the peak current in the power and ground traces pin 18 and pin 5. The other four ground pins 10, 12, 14, and 16 are intended for signal grounds.

#### **POWER SUPPLY REGULATION:**

Good power supply regulation is recommended for the MSTM-S3-T2 The internal oscillators are regulated to operate from 4.75 - 5.25 volts. Large jumps within this range may still produce varying degrees of wander. If the host system is subject to large voltage jumps due to hot-swapping and the like, it is suggested that there be some form of external regulation such as a DC/DC converter.

#### **SOLDERING RECOMMENDATIONS:**

Due to the sensitive nature of this part, hand soldering of the pins is recommended after reflow processes.

#### **WASHING RECOMMENDATIONS:**

The MSTM-S3-T2 is not in a hermetic enclosure. It is recommended that the leads be hand cleaned after soldering. Do not completely immerse the module.

#### **MODULE BAKEOUT:**

Do not bakeout the MSTM-S3-T2

Data Sheet #: TM053 Page 15 of 20 Rev: 00 Date: 5 / 14 / 03

### **Recommended Footprint Dimensions**

Figure 21

# **Characteristic Measurements**

Table 6

| Characteristic Item     | Measurement (inches) |  |

|-------------------------|----------------------|--|

| Pad to Pad Spacing      | 0.200                |  |

| Solder pad top O.D.     | 0.150                |  |

| Solder pad top I.D.     | 0.055                |  |

| Solder pad bottom O.D.  | 0.150                |  |

| Solder pad bottom I.D.  | 0.055                |  |

| Solder mask top dia.    | 0.070                |  |

| Solder mask bottom dia. | 0.155                |  |

| Pin row to row spacing  | 1.600                |  |

### **Side Assembly View**

Figure 22

Figure 23

Data Sheet #: TM053 Page 18 of 20 Rev: 00 Date: 5 / 14 / 03

2111 Comprehensive Drive

Aurora, Illinois 60505

Phone: 630-851-4722

Fax: 630-851-5040

www.conwin.com

| Revision | Revision Date | Note          |

|----------|---------------|---------------|

| 00       | 5/14/03       | Final Release |