# ML9078-002

LSI for power-saving solar power supply control

#### Outline

ML9078-002 is power supply control LSI which performs selection control for a solar cell power supply and a primary battery. This LSI consists of a direct switch circuit and a regulator circuit, and each circuit performs the following operations.

- Direct switch circuit

- Primary battery side direct switch circuit (BAT DIRECT)

- This always compare the primary battery side voltage (V<sub>BAT</sub>) with the output voltage (VDO) of ML9078-002. In case V<sub>BAT</sub>>VDO, a primary battery side direct switch will be set to ON and the primary battery side voltage (V<sub>BAT</sub>) is supplied to the output voltage (VDO).

- Solar cell side direct switch circuit (SC DIRECT)

- This always compare the solar cell side voltage (V<sub>SC</sub>) with the output voltage (VDO) of ML9078-002. In case V<sub>SC</sub>>VDO, a solar cell side direct switch will be set to ON and the primary battery side voltage (V<sub>SC</sub>) is supplied to the output voltage (VDO).

- Regulator circuit

- The solar cell side voltage (Vsc) will be limited to be 1.5V(typ) or 3.0V(typ).

#### Feature

- Comparison of primary battery power supply voltage (V<sub>BAT</sub>) and solar cell power supply voltage (V<sub>SC</sub>) is performed, and the power supply source is selected automatically.

- When primary battery voltage ( $V_{BAT}$ ) is higher than solar cell voltage ( $V_{SC}$ ), it outputs primary battery voltage ( $V_{BAT}$ ) to the output terminal (VDO) of ML9078-002.

- When solar cell voltage (V<sub>SC</sub>) is higher than primary battery voltage (V<sub>BAT</sub>), it outputs solar cell voltage (V<sub>SC</sub>) to the output terminal (VDO) of ML9078-002.

- The adverse current from a solar cell to a primary battery is prevented.

- When primary battery voltage is low, the direct switch by the side of a primary battery turns off. The adverse current to a primary battery from a solar cell is prevented, and the primary battery destruction by the adverse current from a solar cell to a primary battery can be prevented.

- Direct power supply from whether a solar cell output or a primary battery output to the external LSI is available. (at the time of SCREG=L)

- The regulator output voltage is selectable by the external input. (at the time of SCREG=H)

- In case SCLV=L: regulator output voltage(V<sub>LD</sub>) will be limited to be 1.5V(typ) (V<sub>SC</sub>>=2V, I<sub>SC</sub><=0.1mA, 25 °C conditions)</li>

- In case SCLV=H: regulator output voltage(V<sub>LD</sub>) will be limited to be 3.0V(typ) (V<sub>SC</sub>>=3.6V, I<sub>SC</sub><=0.8mA, 25 °C conditions)</li>

- Low power operation

- Primary-battery side consumption current: Max 80nA at 25° C

- SCREG=L,SCLV=X,Solar-cell side consumption current: Max 80nA at 25°C

- SCREG=H,SCLV=L,Solar-cell side consumption current: Max 250nA at 25°C

- SCREG=H,SCLV=H,Solar-cell side consumption current: Max 1200 nA at 25°C

- A monitor of the use situation of a solar panel is possible.

- In case DI\_MONI=L, current is supplied from solar cell to external circuit.

- In case DI\_MONI=H, current is supplied from primary battery to external circuit.

## LAPIS Semiconductor Co., Ltd.

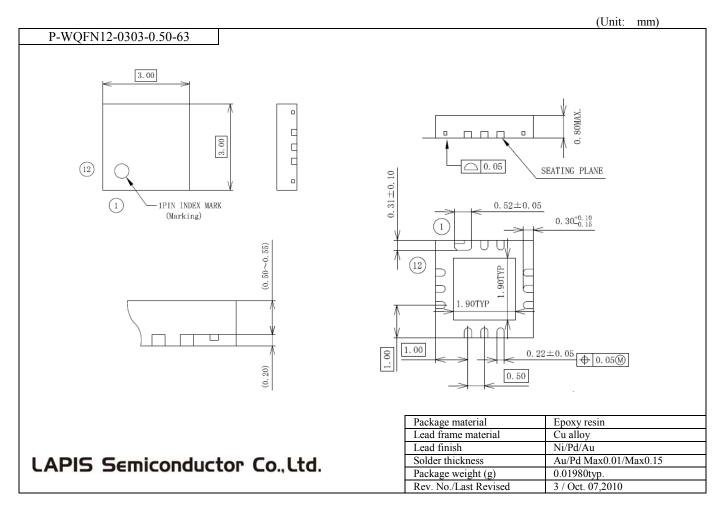

- Shipment form

- 12-pin plastic WQFN

· Part number : ML9078-002GDZ05B

- Chip

- · Part number : ML9078-002WA

- Guaranteed operation range

- Operating temperature : -20 to +70°C

- Operating voltage :  $V_{SC} = 0.0$  to 4V,  $V_{BAT} = 1.1$  to 3.6V

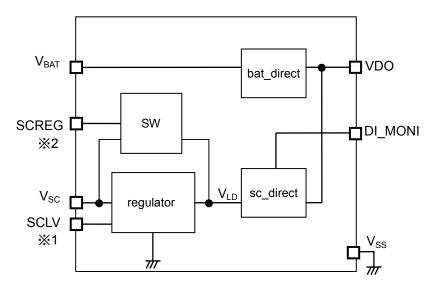

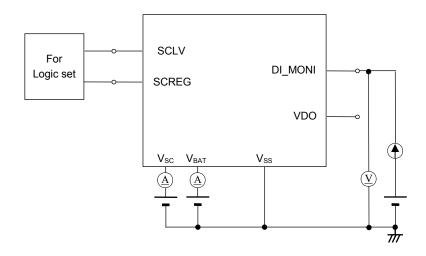

#### Block diagram

#### ML9078-002 block diagram

- The block diagram of ML9078-002 is shown in Fig. 1.

- ※1 Regulator voltage is chosen to 3.0V or 1.5V by SCLV.

- ※2 Regulator can be disabled by SCREG through SW.

Fig 1 ML9078-002 block diagram

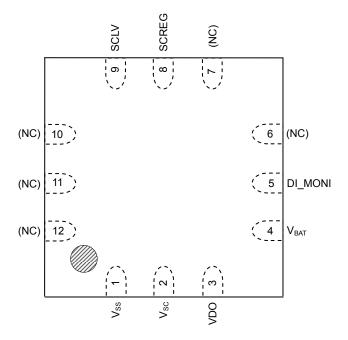

## Pin Configuration

ML9078-002GDZ05B terminal arrangement

(NC): No Connection

Fig. 2 ML9078-002 package article terminal arrangement plan

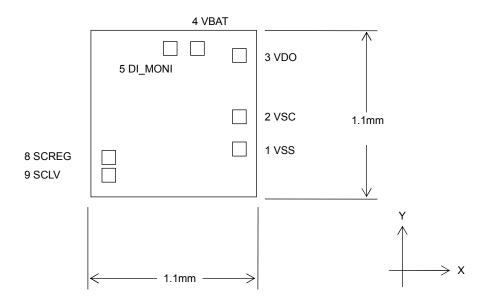

ML9078-002WA terminal arrangement and outline drawing

Chip size :  $1.1 \text{mm} \times 1.1 \text{mm}$ The number of pads : 7 pinsMinimum pad pitch :  $120 \text{ } \mu\text{m}$ Pad opening :  $90 \text{ } \mu\text{m} \times 90 \text{ } \mu\text{m}$ Chip thickness :  $350 \text{ } \mu\text{m}$

The voltage on the back of a chip is  $V_{SS}$  level.

Fig. 3 ML9078-002 chip outline drawing

ML9078-002 chip article pad coordinates

Table 1 ML9078-002 pad coordinates table

|     |         | 1 doic | I WILDONG GO | 2 pad coord | mates table |          |              |

|-----|---------|--------|--------------|-------------|-------------|----------|--------------|

|     |         |        |              |             |             | Chip Cen | ter: X=0,Y=0 |

| PAD | Pad     | ML90   | 78-002       | PAD         | Pad         | ML90     | 78-002       |

| No. | Name    | X (µm) | Υ (μm)       | No.         | Name        | X (μm)   | Y (µm)       |

| 1   | VSS     | 432.0  | -228.0       | 7           | -           | -        | -            |

| 2   | VSC     | 432.0  | -21.0        | 8           | SCREG       | -432.0   | -287.0       |

| 3   | VDO     | 432.0  | 385.0        | 9           | SCLV        | -432.0   | -407.0       |

| 4   | VBAT    | 156.0  | 432.0        | 10          | -           | -        | -            |

| 5   | DI_MONI | -27.0  | 432.0        | 11          | -           | -        | -            |

| 6   | -       | -      | -            | 12          | -           | -        | -            |

## Terminal explanation

Table 2 Explanation of terminal

| Terminal name                    | I/O     | Explanation Logic                                                                                                    |          |  |  |  |  |  |

|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| Power supply terminal            |         |                                                                                                                      |          |  |  |  |  |  |

| $V_{SS}$                         | -       | he minus side power supply terminal.                                                                                 |          |  |  |  |  |  |

| $V_{BAT}$                        | -       | It is the primary battery plus side power supply terminal.                                                           | -        |  |  |  |  |  |

| $V_{SC}$                         | -       | s the plus side power supply terminal of a solar power supply. It connects with the plus side of a solar ver supply. |          |  |  |  |  |  |

| Regulator setting input terminal |         |                                                                                                                      |          |  |  |  |  |  |

| SCLV                             | I       | It is an input port for a regulator voltage setup.                                                                   |          |  |  |  |  |  |

|                                  |         | In case SCLV=L, regulator output voltage will be limited to be 1.5V(typ)                                             | Positive |  |  |  |  |  |

|                                  |         | In case SCLV=H, regulator output voltage will be limited to be 3.0V(typ)                                             |          |  |  |  |  |  |

| SCREG                            | I       | It is an input port for an enabling setup of a regulator.                                                            | Positive |  |  |  |  |  |

| The output term                  | ninal c | of a primary battery and a solar power supply                                                                        |          |  |  |  |  |  |

| VDO                              | О       | It is an output terminal of a primary battery and a solar power supply.                                              |          |  |  |  |  |  |

| The output term                  | ninal v | which displays power supply source                                                                                   |          |  |  |  |  |  |

| DI_MONI                          | О       | It is an output terminal for displaying power supply source.                                                         |          |  |  |  |  |  |

|                                  |         | In case DI_MONI=L, current is supplied from solar cell to external ciruit.                                           | Negative |  |  |  |  |  |

|                                  |         | In case DI_MONI=H, current is supplied from primary battery to external ciruit.                                      |          |  |  |  |  |  |

Termination of unused pins

Table 3 shows methods of terminating the unused pins.

Table 3 Termination of unused pins

| Terminal                                        | Recommendation terminal processing |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| output                                          |                                    |  |  |  |  |  |  |

| VDO                                             | Open                               |  |  |  |  |  |  |

| DI_MONI                                         | Open                               |  |  |  |  |  |  |

| input                                           |                                    |  |  |  |  |  |  |

| SCLV <sup>(*1)</sup>                            | $ m V_{SC}$ or $ m V_{SS}$         |  |  |  |  |  |  |

| SCREG <sup>(*1)</sup>                           | $ m V_{SC}$ or $ m V_{SS}$         |  |  |  |  |  |  |

| * Note                                          |                                    |  |  |  |  |  |  |

| Consider input to fix to $V_{SC}$ or $V_{SS}$ . |                                    |  |  |  |  |  |  |

## Electrical property

## Absolute maximum rating

$(V_{SS}=0V)$

| Item                     | Sign             | Conditions            | Rated value                   | Unit |

|--------------------------|------------------|-----------------------|-------------------------------|------|

| Power supply voltage 1   | $V_{BAT}$        | $Top = 25  ^{\circ}C$ | -0.3 to +4.2                  | V    |

| Power supply voltage 2   | $V_{SC}$         | $Top = 25  ^{\circ}C$ | -0.3 to +5.6                  | V    |

| Power supply voltage 3   | VDO              | Top = 25 °C           | -0.3 to +5.6                  | V    |

| Input voltage            | $V_{IN}$         | $Top = 25  ^{\circ}C$ | - 0.3 to V <sub>SC</sub> +0.3 | V    |

| Output voltage           | V <sub>OUT</sub> | Top = 25 °C           | -0.3 to VDO+0.3               | V    |

| Output current 1         | $I_{OUT1}$       | VDO, Top = $25$ °C    | 10                            | mA   |

| Permissible loss         | PD               | $Top = 25  ^{\circ}C$ | 0.88                          | W    |

| Preservation temperature | $T_{STG}$        | -                     | -40 to +125                   | °C   |

## Recommendation operation conditions

$(V_{SS}=0V)$

| Item                                              | Sign              | Condi                                                               | tions             | Range       | Unit |   |  |   |  |            |    |

|---------------------------------------------------|-------------------|---------------------------------------------------------------------|-------------------|-------------|------|---|--|---|--|------------|----|

| Temperature of operation                          | $T_{OP}$          | -                                                                   |                   | -           |      | - |  | - |  | -20 to +70 | °C |

| Voltage of operation                              | V <sub>SC</sub> * | Top=-20 to 70                                                       |                   | 0.0 to 4.0  | V    |   |  |   |  |            |    |

| voltage of operation                              | $V_{BAT}$         | Top=-20 to 70                                                       |                   | 1.1 to 3.6  | •    |   |  |   |  |            |    |

| External capacitance for regulator output voltage | Cdo               | Top=-20°C to 70°C                                                   | SCREG=H<br>SCLV=L | 0.01 to 0.1 | μF   |   |  |   |  |            |    |

| stabilization                                     | Cuo               | Cdo $V_{SC}=0V \text{ to } 4.0V$<br>$V_{BAT}=1.1V \text{ to } 3.6V$ |                   | 0.1 to 1    | μF   |   |  |   |  |            |    |

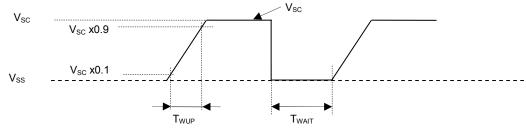

VSC power rise time is required to be more than TWUP=125 us/V.

Please start after stand-by-time TWAIT=10msec when a VSC power supply is less than 0.5V.

## Notice of starting speed and stand-by-time for $\ensuremath{V_{\text{SC}}}$

#### Direct-current characteristic (Input)

(V\_BAT=1.1V to 3.6V, V\_SC=0.0V to 4.0V, V\_SS=0V, and Top=-20 to +70 °C, unless otherwise specified)

| Item                        | Sign | Sign Conditions              |                         | Rating |                 |       | Unit    | Measuring |

|-----------------------------|------|------------------------------|-------------------------|--------|-----------------|-------|---------|-----------|

| Hem                         | Sign | Conditions                   | Min.                    | Тур.   | Max.            | Omt   | circuit |           |

|                             | VIH  | V <sub>SC</sub> =1.1 to 4.0V | 0.7<br>xV <sub>SC</sub> | -      | $V_{SC}$        |       |         |           |

| Input voltage (SCLV, SCREG) | VIL  | $V_{SC}$ =1.3 to 4.0V        | 0                       | 1      | $0.3$ $xV_{SC}$ | V     |         |           |

|                             |      | $V_{SC}$ =1.1 to 4.0V        | 0                       | -      | $0.2$ $xV_{SC}$ |       | 1       |           |

| Input (SCLV, SCREG)         | IIH  | $V_{SC}$ =1.1 to 4.0V        | ı                       | ı      | 10              | nA    |         |           |

|                             | IIL  | $V_{SC}$ =1.1 to 4.0V        | -10                     | ı      | ı               | 117 1 |         |           |

## Direct-current characteristic (power supply control)

$(V_{BAT}=1.1 \text{V to } 3.6 \text{V}, V_{SC}=0.0 \text{V to } 4.0 \text{V}, V_{SS}=0 \text{V}, \text{ and Top=-20 to } +70 ^{\circ}\text{C}, \text{ unless otherwise specified})$

| Item                                          | Item Sign Condition                                                  |                               | Conditions        |   | Standard value |      | Unit | Measuring |

|-----------------------------------------------|----------------------------------------------------------------------|-------------------------------|-------------------|---|----------------|------|------|-----------|

| Item                                          | Sign                                                                 | Collations                    | Conditions        |   | Тур.           | Max. | Ont  | Circuit   |

| Primary battery side<br>Consumption current   | IDD <sub>BAT</sub> (*1)                                              | $V_{BAT}=3.6V$<br>Top = 25 °C |                   | - | -              | 80   |      |           |

| Solar power supply side IDD <sub>SC</sub> (*2 |                                                                      | $V_{SC}=4V$<br>Top = 25 °C    | SCREG=L           | - | ı              | 80   | 4    | 2         |

|                                               | $\begin{array}{c c} IDD_{SC}(*2) & Top \\ \hline V_{SC} \end{array}$ | $V_{SC}=4V$<br>Top = 25 °C    | SCREG=H<br>SCLV=L | - | ı              | 250  | nA   | _         |

|                                               |                                                                      | $V_{SC}=4V$<br>Top = 25 °C    | SCREG=H<br>SCLV=H | - | -              | 1200 |      |           |

<sup>\*1 :</sup> IDD<sub>BAT</sub> is consumption current to the current consumed by the primary battery side.

7/19

<sup>\*2 :</sup> IDD<sub>SC</sub> is consumption current to the current consumed by the solar power supply side.

( $V_{BAT}$ =1.1V to 3.6V,  $V_{SC}$ =0.0V to 4.0V,  $V_{SS}$ =0V, and Top=-20 to +70 °C, unless otherwise specified)

| Τ.                                                                    | a:                     | $(V_{BAT}=1.1V \text{ to } 3.6V, V_{SC})$                                                                                                         | 0.01 10 1.01, 133 |                         | tandard val |      |      | Measuring |

|-----------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|-------------|------|------|-----------|

| Item                                                                  | Sign                   | Conditions                                                                                                                                        |                   | Min.                    | Тур.        | Max. | Unit | Circuit   |

| VDO voltage                                                           |                        | $V_{SC} < V_{BAT}$ - 50mV<br>$0V <= V_{BAT} <= 1.1V$<br>$I_{BAT} <= 2mA$                                                                          |                   | 0                       | -           | -    |      |           |

| V <sub>BAT</sub> ->VDO<br>(VDO is supplied<br>from V <sub>BAT</sub> ) | $VDO_{BAT}$            | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                            |                   | V <sub>BAT</sub> - 0.3  | -           | -    |      |           |

| HOIII V <sub>BAT</sub> )                                              |                        | $ \begin{array}{c c} V_{SC}\!\!<\!\!V_{BAT} & \text{-} 50mV \\ V_{BAT}\!\!>\!\!2.0V \\ I_{BAT}\!\!<\!\!=\!\!2mA \end{array} $                     |                   | V <sub>BAT</sub> - 0.15 | -           | -    |      |           |

| VDO voltage<br>V <sub>SC</sub> (VDO)                                  |                        | $V_{SC} > V_{BAT} - 50 \text{mV}$<br>$0V <= V_{SC} <= 1.1 \text{V}$<br>$I_{SC} <= 2 \text{mA}$                                                    |                   | 0                       | -           | -    |      |           |

| (VDO is supplied from $V_{SC}$ )                                      | VDO <sub>SC</sub>      | $V_{SC} > V_{BAT}$ - 50mV<br>1.1V<= $V_{SC} <= 2V$<br>$I_{SC} <= 2mA$                                                                             | SCREG=L           | V <sub>SC</sub> - 0.3   | -           | -    |      |           |

| Regulator through mode                                                |                        | $V_{SC} > V_{BAT}$ - 50mV $V_{SC} > 2.0$ V $I_{SC} < 2mA$                                                                                         |                   | V <sub>SC</sub> - 0.13  | -           | -    |      |           |

|                                                                       | VDO <sub>REG(L1)</sub> | $ \begin{array}{lll} V_{SC}{>}V_{BAT} & -50mV \\ 0V{<=}V_{SC}{<=}1.1V \\ I_{SC}{<=}0.1mA \\ Cdo{=}0.1uF \\ Top = 25 \ ^{\circ}C \end{array} $     |                   | 0                       | -           | -    |      |           |

|                                                                       |                        | $ \begin{aligned} &V_{SC}{>}V_{BAT} &- 50mV \\ &1.1V{<=}V_{SC}{<=}2V \\ &I_{SC}{<=}0.1mA \\ &Cdo{=}0.1uF \\ &Top = 25 \ ^{\circ}C \end{aligned} $ | SCREG=H<br>SCLV=L | 0.8                     | -           | 1.6  | V    | 3,4       |

| VDO voltage $V_{SC}$ (VDO) (VDO is supplied                           | VDO <sub>REG(L2)</sub> | $\begin{array}{ll} V_{SC}{>}V_{BAT} & -50mV \\ V_{SC}{>}2V \\ I_{SC}{<=}0.1mA \\ Cdo{=}0.1uF \\ Top = 25~^{\circ}C \end{array}$                   |                   | 1.35                    | 1.5         | 1.6  |      |           |

| from V <sub>Sc</sub> ) Regulator operational mode                     | VDO <sub>REG(H1)</sub> | $\begin{split} &V_{SC}{>}V_{BAT} - 50mV \\ &0V{<=}V_{SC}{<=}1.1V \\ &I_{SC}{<=}0.8mA \\ &Cdo{=}0.1uF \\ &Top = 25 \ ^{\circ}C \end{split}$        |                   | 0                       | -           | -    |      |           |

|                                                                       |                        | $\begin{array}{c} V_{SC}{>}V_{BAT} - 50mV \\ 1.1V{<=}V_{SC}{<=}3.6V \\ I_{SC}{<=}0.8mA \\ Cdo{=}0.1uF \\ Top = 25\ ^{\circ}C \end{array}$         | SCREG=H<br>SCLV=H | 0.8                     | -           | 3.1  |      |           |

|                                                                       | VDO <sub>REG(H2)</sub> | $V_{SC} > V_{BAT} - 50 \text{mV}$<br>$V_{SC} > 3.6 \text{V}$<br>$I_{SC} < = 0.8 \text{mA}$<br>C = 0.1 uF<br>$V_{SC} = 0.2 \text{mA}$              |                   | 2.9                     | 3           | 3.1  |      |           |

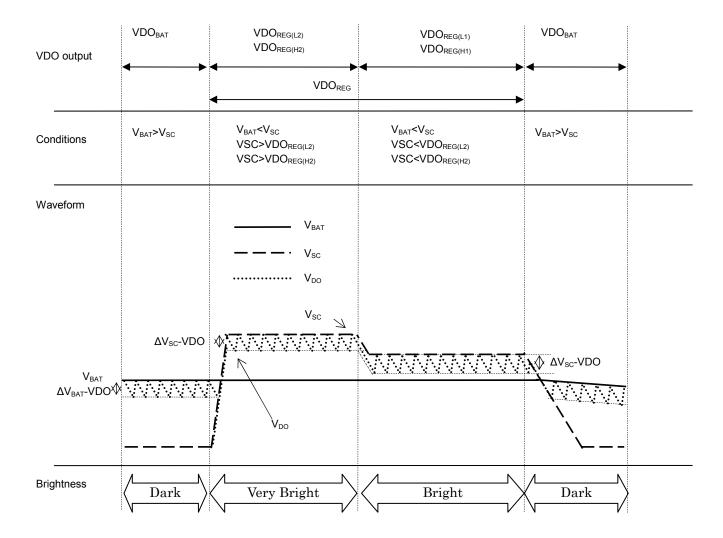

• ML9078-002 operation in regulator through mode

• ML9078-002 operation in regulator mode

## Direct-current characteristic (DI\_MONI)

$(V_{BAT}=1.1V \text{ to } 3.6V, V_{SC}=0.0V \text{ to } 4V, V_{SS}=0V, \text{ and Top=-20 to } +70 \,^{\circ}\text{C}, \text{ unless otherwise specified})$

| T.               | a:    | G. Fri                                      | Standard value  |      | ue   | TT 1. | Measuring |

|------------------|-------|---------------------------------------------|-----------------|------|------|-------|-----------|

| Item             | Sign  | Conditions                                  |                 | Typ. | Max. | Unit  | Circuit   |

|                  |       | IOH1=-0.5mA                                 | $V_{SC}$        | _    | _    |       |           |

|                  |       | $V_{DO}=1.8V\sim4.0V$                       | 0.7             |      |      |       |           |

|                  | VOH1  | IOH1=-0.1mA                                 | $V_{SC}$        |      |      | V     | 5         |

|                  | VOIII | $V_{DO} = 1.3 \text{ V} \sim 4.0 \text{ V}$ | 0.5             |      | -    | ·     |           |

|                  |       | IOH1=-0.03mA                                | V <sub>SC</sub> |      |      |       |           |

| Output voltage 1 |       | $V_{DO} = 1.1 V \sim 4.0 V$                 | 0.5             | -    | -    |       |           |

| (DI_MONI)        |       | IOL1=+0.5mA                                 |                 |      | 0.7  |       |           |

|                  |       | $V_{DO} = 1.8 V \sim 3.6 V$                 | 0.7             |      | 0.7  |       |           |

|                  | VOL1  | IOL1=+0.1mA                                 |                 | _    | 0.7  | V     | 6         |

|                  | VOLI  | $V_{DO} = 1.3 \text{V} \sim 3.6 \text{V}$   | -               |      | 0.7  | V     | · ·       |

|                  |       | IOL1=+0.03mA                                |                 |      | 0.5  |       |           |

|                  |       | $V_{DO} = 1.1 V \sim 3.6 V$                 | -               | -    | 0.5  |       |           |

## Alternating-current characteristic (DI\_MONI)

( $V_{BAT}$ =1.1V to 3.6V,  $V_{SC}$ =0.0V to 4V,  $V_{SS}$ =0V, and Top=-20 to +70 °C, unless otherwise specified)

| Τ.                           | a:   | Q IV        | Standard value        |           |                          | TT '4 | Measuring |

|------------------------------|------|-------------|-----------------------|-----------|--------------------------|-------|-----------|

| Item                         | Sign | Conditions  | Min.                  | Тур.      | Max.                     | Unit  | Circuit   |

| DI_MONI<br>Detection voltage | VDM  | Top = 25 °C | V <sub>BAT</sub> -0.1 | $V_{BAT}$ | V <sub>BAT</sub><br>+0.1 | V     | 5         |

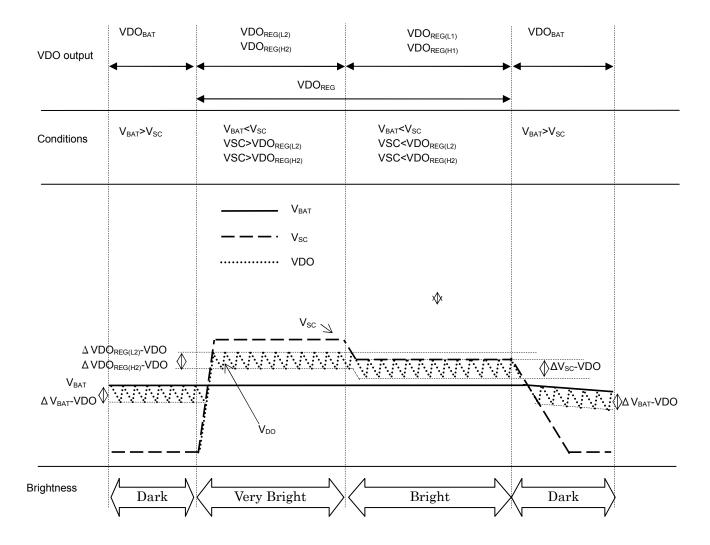

## Operation of DI\_MONI

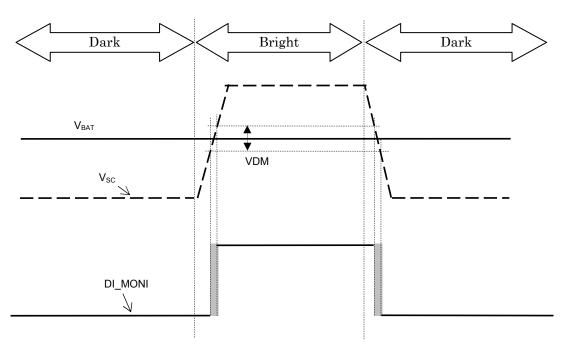

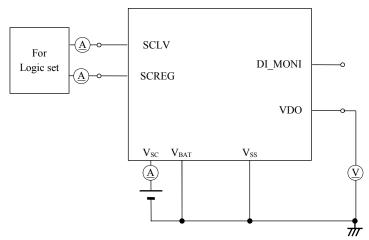

## Measuring circuit

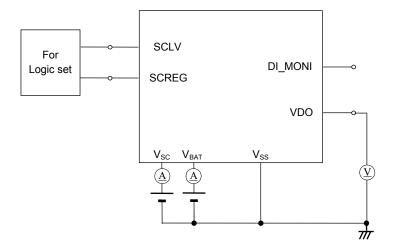

Measuring circuit 1

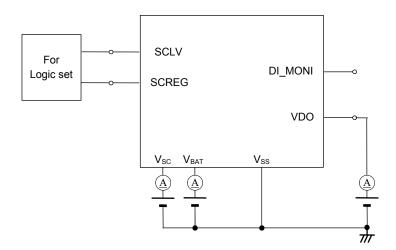

Measuring circuit 2

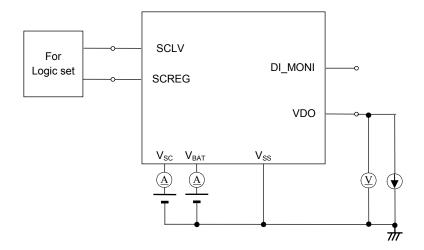

Measuring circuit 3

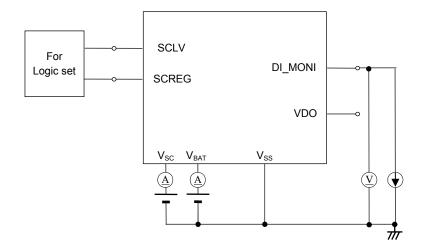

## Measuring circuit 4

## Measuring circuit 5

## Measuring circuit 6

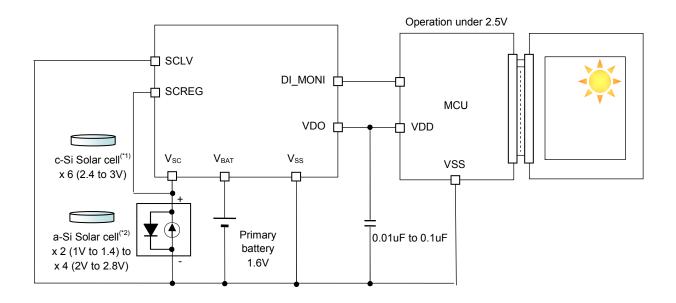

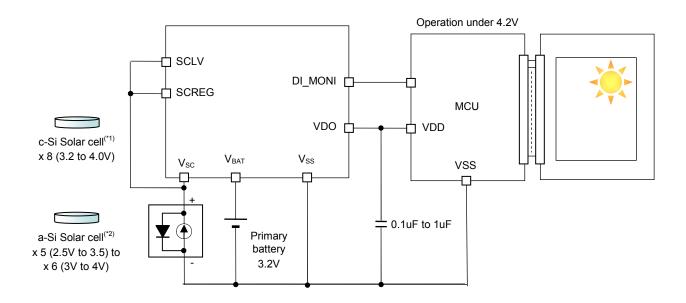

## Appllileation circuit

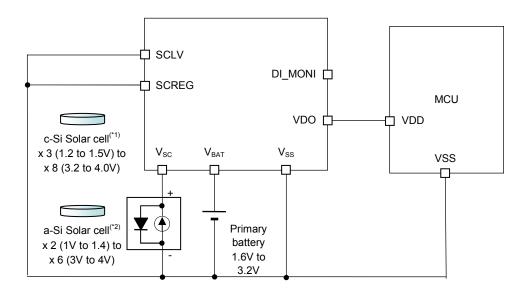

- Simple application

- SCLV=L, SCREG=L

- When DI\_MONI is used (1.5V battery)

- SCLV=L, SCREG=L

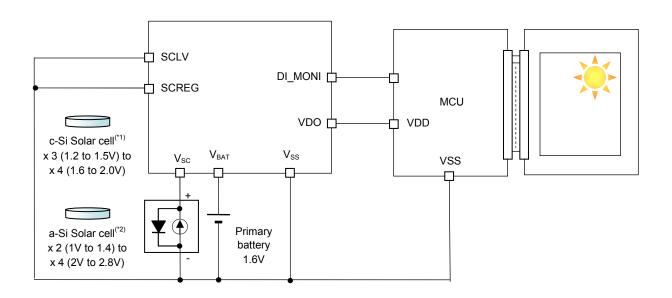

- When DI\_MONI is used (3V battery)

- SCLV=L, SCREG=L

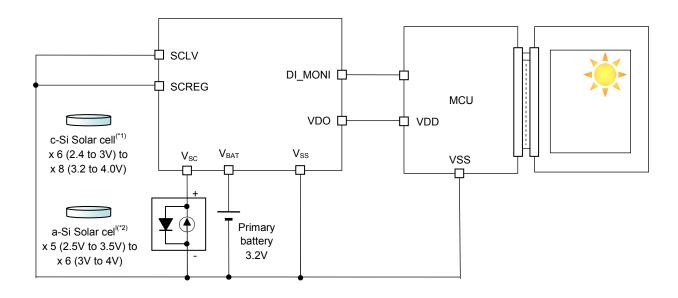

- When a regulator is used (regulator voltage will be at 1.65 V)

- SCLV=L, SCREG=H

- When using a regulator by SCLV=L, please insert the external capacitance Cdo = 0.01uF to 0.1uF between VDO and V<sub>SS</sub> for regulator output voltage stabilization.

- When a regulator is used (regulator voltage will be at 3.3 V

- SCLV=H, SCREG=H

- When using a regulator by SCLV=H, please insert the external capacitance Cdo = 0.1uF to 1uF between VDO and  $V_{SS}$  for regulator output voltage stbirization.

\*1 : c-Si Solar cell is a Crystal Si type solar cell. (The single crystal Si, the many crystals Si)

\*2 : a-Si Solar cell is an amorphous Si type solar cell. (Amorphous silicon)

## Package dimensions

Attention on surface mount type package mounting

A surface mount type package is a package which is very much easy to receive influence in the heat at the time of reflow mounting, the amount of moisture absorption of the package at the time of storage, etc.

Therefore, when inquired by implementation of reflow mounting, please be sure to ask the product name, a package name, the number of pins, a package code and the mounting conditions (the reflow method, temperature, number of times) for which it wishes, storage conditions, etc. to the business assigned to our company.

ML9078-002

## ■ Revision history

|                 |               | Pa              | ige            |                        |

|-----------------|---------------|-----------------|----------------|------------------------|

| Document No.    | Date of issue | Before revision | After revision | The contents of change |

| FEDL9078-002-01 | Jan.30,2012   | -               | -              | First edition issue    |

#### **NOTES**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production. Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such

damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2012 LAPIS Semiconductor Co., Ltd.