### ULC0544P10

#### Description

The ULC0544P10 is ultra low capacitance TVS arrays designed to protect high speed data interfaces. This series has been specifically designed to protect sensitive components which are connected to high-speed data and transmission lines from over-voltage caused by ESD (electrostatic discharge), CDE (Cable Discharge Events), and EFT (electrical fast transients).

### Feature

- ♦ 50 Watts Peak Pulse Power per Line (tp=8/20µs)

- Protects Four High Speed Lines

- Low Clamping Voltage

- RoHS Compliant

- ♦ IEC61000-4-2(ESD):±15kV (air discharge) ±10kV (contact discharge);

- IEC61000-4-4 (EFT) 40A (5/50 η s)

- IEC61000-4-5 (LIGHTING) 2A (8/20 μ s)

#### Applications

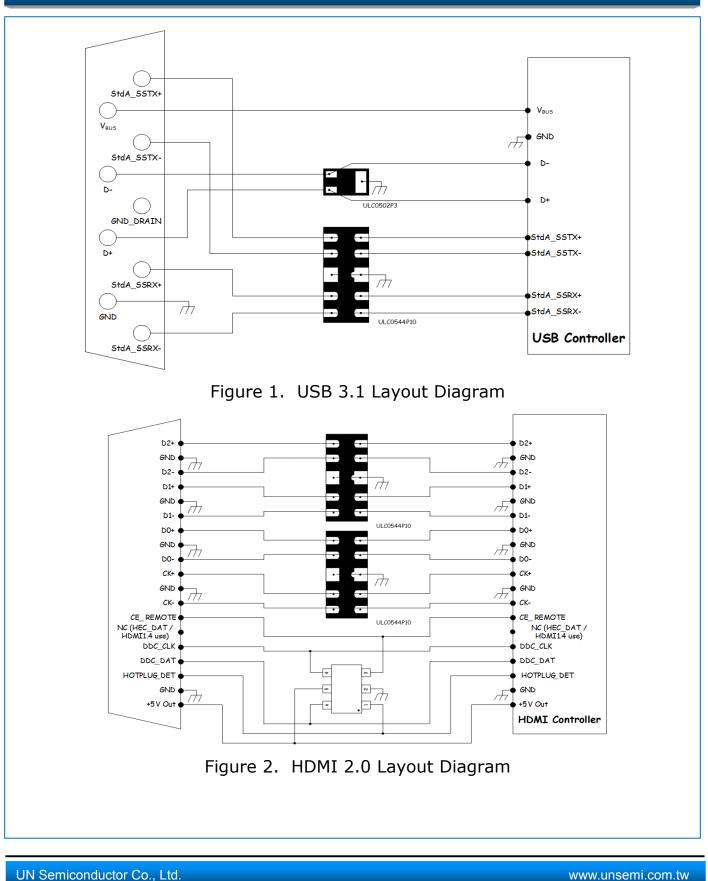

- USB 3.0 / USB 3.1 Interfaces

- HDMI 1.4 / HDMI 2.0 Interfaces

- Video Graphics Cards

- Notebooks, Desktops, and Servers

- Portable Instrumentation

- Industrial Controls

- Peripherals

#### Mechanical Data

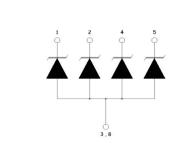

**Functional Diagram**

- DFN2510P10 (2.5x1.0mm) Package

- Molding Compound Flammability Rating : UL 94V-O

- Weight 5.0 Millgrams (Approximate)

- Quantity Per Reel : 3,000pcs

- Reel Size : 7 inch

- Lead Finish : Lead Free

- Device Marking: UL4L

#### **Mechanical Characteristics**

| Symbol | Parameter                             | Value       | Units |

|--------|---------------------------------------|-------------|-------|

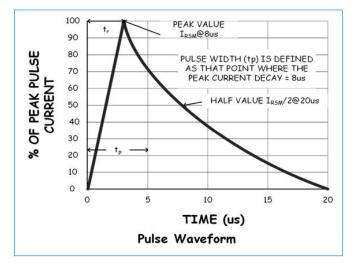

| Ррр    | Peak Pulse Power (tp=8/20µs waveform) | 50          | Watts |

| TJ     | Operating Junction Temperature Range  | -55 to +150 | °C    |

| Тѕтс   | Storage Temperature Range             | -55 to +150 | °C    |

| ΤL     | Soldering Temperature, T max = 10s    | 260         | °C    |

UN Semiconductor Co., Ltd.

#### www.unsemi.com.tw

### ULC0544P10

| Electrical Characteristics (@ 25°C Unless Otherwise Specified ) |                  |                                             |      |      |      |      |  |  |

|-----------------------------------------------------------------|------------------|---------------------------------------------|------|------|------|------|--|--|

| Characteristics                                                 | Symbol           | Test Conditions                             | Min. | Тур. | Max. | Unit |  |  |

| Reverse Working<br>Voltage                                      | V <sub>RWM</sub> |                                             |      | -    | 5    | V    |  |  |

| Reverse Breakdown<br>Voltage                                    | V <sub>BR</sub>  | I <sub>T</sub> =1mA                         | 6    |      |      | V    |  |  |

| Reverse Leakage                                                 |                  | V <sub>RWM</sub> =5V ; T=25°C               |      |      | 1    | μA   |  |  |

| Junction capacitance                                            | CJ               | I/O To GND; $V_R = 0V$ , f=1MHz ;           |      | 0.35 |      | pF   |  |  |

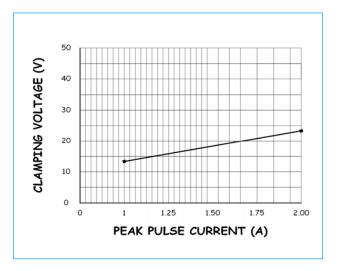

| Positive Clamping                                               |                  | I <sub>PP</sub> =1A,T <sub>P</sub> =8/20μS; |      |      | 14   |      |  |  |

| Voltage                                                         | Vc               | I <sub>PP</sub> =2A,T <sub>P</sub> =8/20μS; |      |      | 25   | V    |  |  |

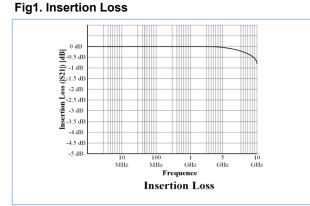

### **Characteristic Curves**

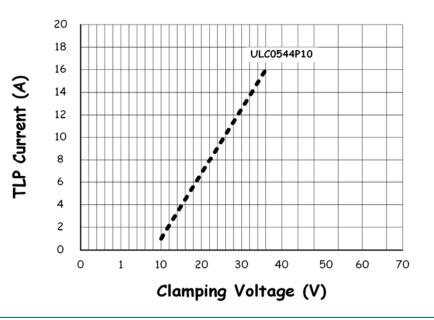

### Fig3. ESD Clamping Volatge & Peak Pulse Curerent

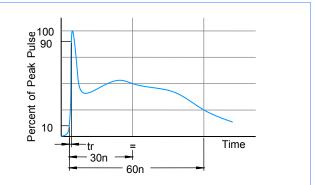

#### Fig2. ESD Pulse Waveform (according to IEC 61000-4-2)

#### Fig4. Pulse Waveform

#### UN Semiconductor Co., Ltd.

#### www.unsemi.com.tw

### ULC0544P10

#### **Transmission Line Pulse (TLP)**

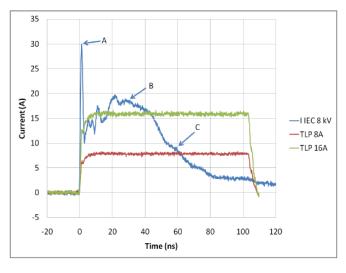

Transmission Line Pulse (TLP) is a measurement technique used in the Electrostatic Discharge (ESD) arena to characterize performance attributes of devices under ESD stresses. TLP is able to obtain current versus voltage (I–V) curves in which each data point is obtained with a 100 ns long pulse, with currents up to 40 A. TLP was first used in the ESD field to study human body model (HBM) in integrated circuits, but it is an equally valid tool in the field of system level ESD. The applicability of TLP to system level ESD is illustrated in Figure 1, which compares an 8 kV IEC 61000–4–2 current waveform with TLP current pulses of 8 and 16 A. The current levels and time duration for the pulses are similar and the initial rise time for the TLP pulse is comparable to the rise time of the IEC 61000–4–2's initial current spike. This application note will give a basic introduction to TLP measurements and explain the datasheet parameters extracted from TLP for Yeashin Technology's protection products.

Comparison of a Current Waveform of IEC 61000-4-2 with TLP Pulses at 8 and 16 A.

The IEC 61000-4-2 ESD waveforms is true to the Standard and is shown here as captured on an oscilloscope. The points A, B, and C show the points on the waveforms specified in IEC 61000-4-2.

#### **TLP Characteristic**

UN Semiconductor Co., Ltd.

#### www.unsemi.com.tw

## ULC0544P10

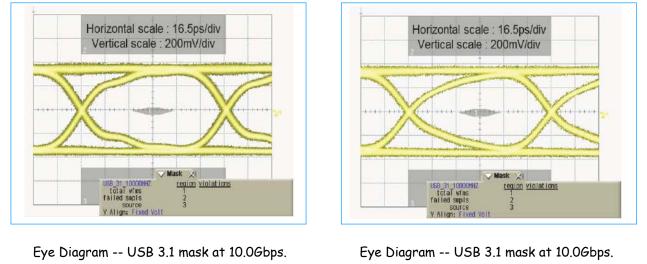

### Eye Diagram

| 1        | Zero Level : measure of the mean value of the logical O. |  |  |  |

|----------|----------------------------------------------------------|--|--|--|

| 2        | One Level : measure of the mean value of the logical 1.  |  |  |  |

| 3        | Rise Time : measure of the transition time of the        |  |  |  |

|          | data from the 10% level to the 90% level on the          |  |  |  |

|          | upward slope.                                            |  |  |  |

| 4        | Fall Time : measure of the transition time of the        |  |  |  |

|          | data from the 90% level to the 10% level on the          |  |  |  |

|          | downward slope.                                          |  |  |  |

| 5        | Eye Height : measure of the vertical opening.            |  |  |  |

| 0        | Determine eye closure due to noise.                      |  |  |  |

| 6        | Eye Width : measure of the horizontal opening.           |  |  |  |

| U        | Determine influence of jitter on the eye opening.        |  |  |  |

| 7        | Deterministic Jitter : deviation of a transition         |  |  |  |

| ,        | from its ideal time caused by reflections relative       |  |  |  |

|          | to other transitions.                                    |  |  |  |

| 8        | Eye Amplitude : difference between the logic 0           |  |  |  |

| 0        | level and the logic 1 level histogram mean value.        |  |  |  |

| 9        | Bit Rate : inverse of the bit period.                    |  |  |  |

|          |                                                          |  |  |  |

|          | (7)                                                      |  |  |  |

|          |                                                          |  |  |  |

|          |                                                          |  |  |  |

|          |                                                          |  |  |  |

| -        | ↑                                                        |  |  |  |

|          |                                                          |  |  |  |

|          |                                                          |  |  |  |

|          | 5                                                        |  |  |  |

|          |                                                          |  |  |  |

| (8)      |                                                          |  |  |  |

| <u> </u> |                                                          |  |  |  |

|          |                                                          |  |  |  |

|          |                                                          |  |  |  |

|          |                                                          |  |  |  |

| -        | <b>★</b>                                                 |  |  |  |

2

1

9

4

### ULC0544P10

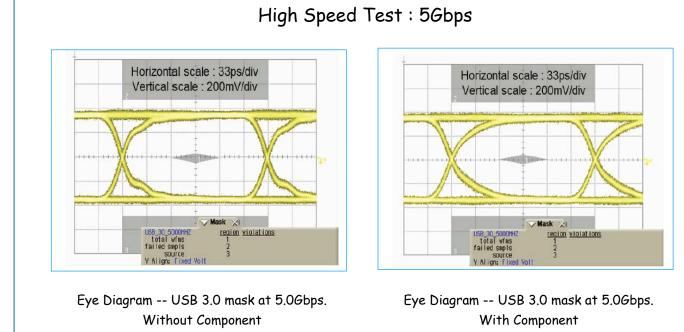

#### Eye Diagram at 5Gbps and 10Gbps

## High Speed Test : 10Gbps

Without Component

UN Semiconductor Co., Ltd.

www.unsemi.com.tw

## ULC0544P10

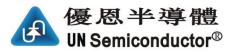

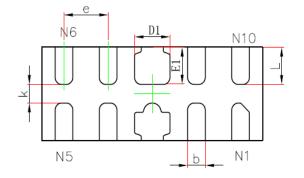

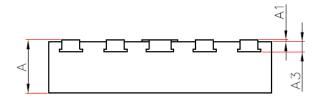

### DFN2510P10 Package Outline & Dimensions

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|--------|---------------------------|-------|----------------------|-------|--|

| Symbol | Min.                      | Max.  | Min.                 | Max.  |  |

| А      | 0.500                     | 0.600 | 0.020                | 0.024 |  |

| A1     | 0.000                     | 0.050 | 0.000                | 0.002 |  |

| A3     | 0.110REF.                 |       | 0.004REF.            |       |  |

| D      | 2.450                     | 2.550 | 0.096                | 0.100 |  |

| E      | 0.950                     | 1.050 | 0.037                | 0.041 |  |

| D1     | 0.350                     | 0.450 | 0.014                | 0.018 |  |

| E1     | 0.350                     | 0.450 | 0.014                | 0.018 |  |

| k      | 0.150MIN.                 |       | 0.006MIN.            |       |  |

| b      | 0.150                     | 0.250 | 0.006                | 0.010 |  |

| e      | 0.500TYP.                 |       | 0.020TYP.            |       |  |

| L      | 0.350                     | 0.450 | 0.014                | 0.018 |  |

UN Semiconductor Co., Ltd.

www.unsemi.com.tw

Revision December 18, 2013

## ULC0544P10

#### LAYOUT DIAGRAM INFORMATION

Revision December 18, 2013