# UT54ACS165/UT54ACTS165

# 8-Bit Parallel Shift Registers

Datasheet November 2010 www.aeroflex.com/logic

### FEATURES

- □ Complementary outputs

- □ Direct overriding load (data) inputs

- Gated clock inputs

- Parallel-to-serial data conversions

- $\Box$  1.2 $\mu$  CMOS

- Latchup immune

- $\hfill \Box$  High speed

- □ Low power consumption

- □ Single 5 volt supply

- □ Available QML Q or V processes

- □ Flexible package

- 16-pin DIP

- 16-lead flatpack

- UT54ACS165 SMD 5962-96558

- UT54ACTS165 SMD 5962-96559

### DESCRIPTION

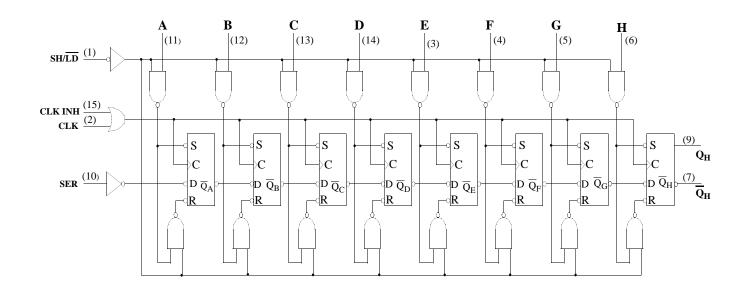

The UT54ACS165 and the UT54ACTS165 are 8-bit serial shift registers that, when clocked, shift the data toward serial output  $Q_{\rm H}.$  Parallel-in access to each stage is provided by eight individual data inputs that are enabled by a low level at the SH/LD input. The devices feature a clock inhibit function and a complemented serial output  $\overline{Q}_{\rm H}$ .

Clocking is accomplished by a low-to-high transition of the CLK input while SH/LD is held high and CLK INH is held low. The functions of the CLK and CLK INH (clock inhibit) inputs are interchangeable. Since a low CLK input and a low-to-high transition of CLK INH will also accomplish clocking, CLK INH should be changed to the high level only while the CLK input is high. Parallel loading is disabled when SH/LD is held high. Parallel inputs to the registers are enabled while SH/LD is low independently of the levels of CLK, CLK INH or SER inputs.

The devices are characterized over full military temperature range of -55°C to +125°C.

### FUNCTION TABLE

| INPUTS            |            |            |     | RNAL<br>PUTS    | OUTI               | PUTS                      |                  |                    |

|-------------------|------------|------------|-----|-----------------|--------------------|---------------------------|------------------|--------------------|

| <u>SH</u> /<br>LD | CLK<br>INH | CLK        | SER | PARALLEL<br>A H | $\overline{Q}_{A}$ | $\overline{Q}_B$          | Q <sub>H</sub>   | $\overline{Q}_{H}$ |

| L                 | Х          | Х          | Х   | a h             | а                  | b                         | h                | h                  |

| Н                 | L          | L          | Х   | Х               | QA                 | $Q_{\rm B}$               | $Q_{\mathrm{H}}$ | $\overline{Q}_{H}$ |

| Н                 | L          | $\uparrow$ | Н   | Х               | Н                  | $\mathbf{Q}_{\mathbf{A}}$ | $Q_{G}$          | $\overline{Q}_G$   |

| Н                 | L          | $\uparrow$ | L   | Х               | L                  | $\mathbf{Q}_{\mathbf{A}}$ | $Q_{G}$          | $\overline{Q}_G$   |

| Η                 | Н          | Х          | Х   | Х               | QA                 | $Q_{\rm B}$               | $Q_{\mathrm{H}}$ | $\overline{Q}_{H}$ |

### Note:

1.  $Q_n$  = The state of the referenced output one setup time prior to the Low-to-High clock transition.PINOUTS

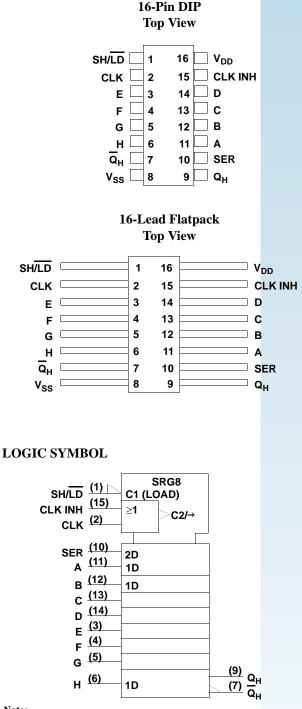

PINOUTS

Note:

1. Logic symbol in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## LOGIC DIAGRAM

# **OPERATIONAL ENVIRONMENT<sup>1</sup>**

| PARAMETER                  | LIMIT  | UNITS                   |

|----------------------------|--------|-------------------------|

| Total Dose                 | 1.0E6  | rads(Si)                |

| SEU Threshold <sup>2</sup> | 80     | MeV-cm <sup>2</sup> /mg |

| SEL Threshold              | 120    | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence            | 1.0E14 | n/cm <sup>2</sup>       |

Notes:

Logic will not latchup during radiation exposure within the limits defined in the table.

Device storage elements are immune to SEU affects.

### ABSOLUTE MAXIMUM RATINGS

| SYMBOL            | PARAMETER                              | LIMIT                    | UNITS |

|-------------------|----------------------------------------|--------------------------|-------|

| V <sub>DD</sub>   | Supply voltage                         | -0.3 to 7.0              | V     |

| V <sub>I/O</sub>  | Voltage any pin                        | 3 to V <sub>DD</sub> +.3 | V     |

| T <sub>STG</sub>  | Storage Temperature range              | -65 to +150              | °C    |

| T <sub>J</sub>    | Maximum junction temperature           | +175                     | °C    |

| T <sub>LS</sub>   | Lead temperature (soldering 5 seconds) | +300                     | °C    |

| $\Theta_{\rm JC}$ | Thermal resistance junction to case    | 20                       | °C/W  |

| II                | DC input current                       | ±10                      | mA    |

| P <sub>D</sub>    | Maximum power dissipation              | 1                        | W     |

Note:

1. Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL          | PARAMETER             | LIMIT                | UNITS |

|-----------------|-----------------------|----------------------|-------|

| V <sub>DD</sub> | Supply voltage        | 4.5 to 5.5           | V     |

| V <sub>IN</sub> | Input voltage any pin | 0 to V <sub>DD</sub> | V     |

| T <sub>C</sub>  | Temperature range     | -55 to + 125         | °C    |

# DC ELECTRICAL CHARACTERISTICS 7

$(V_{DD} = 5.0V \pm 10\%; V_{SS} = 0V^6, -55^{\circ}C < T_C < +125^{\circ}C);$  Unless otherwise noted, Tc is per the temperature range ordered.

| SYMBOL             | PARAMETER                                                            | CONDITION                                                                                                                    | MIN                                         | MAX                      | UNIT       |

|--------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------|------------|

| V <sub>IL</sub>    | Low-level input voltage <sup>1</sup><br>ACTS<br>ACS                  |                                                                                                                              |                                             | 0.8<br>.3V <sub>DD</sub> | v          |

| V <sub>IH</sub>    | High-level input voltage <sup>1</sup><br>ACTS<br>ACS                 |                                                                                                                              | .5V <sub>DD</sub><br>.7V <sub>DD</sub>      |                          | v          |

| I <sub>IN</sub>    | Input leakage current<br>ACTS/ACS                                    | $V_{IN} = V_{DD} \text{ or } V_{SS}$                                                                                         | -1                                          | 1                        | μΑ         |

| V <sub>OL</sub>    | Low-level output voltage <sup>3</sup><br>ACTS<br>ACS                 | $I_{OL} = 8.0 \text{mA}$ $I_{OL} = 100 \mu \text{A}$                                                                         |                                             | 0.40<br>0.25             | v          |

| V <sub>OH</sub>    | High-level output voltage <sup>3</sup><br>ACTS<br>ACS                | $I_{OH} = -8.0 \text{mA}$ $I_{OH} = -100 \mu \text{A}$                                                                       | .7V <sub>DD</sub><br>V <sub>DD</sub> - 0.25 |                          | v          |

| I <sub>OS</sub>    | Short-circuit output current <sup>2</sup> , <sup>4</sup><br>ACTS/ACS | $V_{O} = V_{DD}$ and $V_{SS}$                                                                                                | -200                                        | 200                      | mA         |

| I <sub>OL</sub>    | Output current <sup>10</sup><br>(Sink)                               | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{OL} = 0.4V$                                                                             | 8                                           |                          | mA         |

| I <sub>OH</sub>    | Output current <sup>10</sup><br>(Source)                             | $V_{IN} = V_{DD} \text{ or } V_{SS}$ $V_{OH} = V_{DD} - 0.4V$                                                                | -8                                          |                          | mA         |

| P <sub>total</sub> | Power dissipation <sup>2, 8, 9</sup>                                 | $C_L = 50 pF$                                                                                                                |                                             | 2.9                      | mW/<br>MHz |

| I <sub>DDQ</sub>   | Quiescent Supply Current                                             | V <sub>DD</sub> = 5.5V                                                                                                       |                                             | 10                       | μΑ         |

| ΔI <sub>DDQ</sub>  | Quiescent Supply Current Delta<br>ACTS                               | For input under test<br>$V_{IN} = V_{DD} - 2.1V$<br>For all other inputs<br>$V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{DD} = 5.5V$ |                                             | 1.6                      | mA         |

| C <sub>IN</sub>    | Input capacitance <sup>5</sup>                                       | f = 1MHz @ 0V                                                                                                                |                                             | 15                       | pF         |

| C <sub>OUT</sub>   | Output capacitance <sup>5</sup>                                      | f = 1MHz @ 0V                                                                                                                |                                             | 15                       | pF         |

#### Notes:

- 1. Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions:  $V_{IH} = V_{IH}(min) + 20\%$ , 0%;  $V_{IL} = V_{IL}(max) + 0\%$ , 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to  $V_{IH}(min)$  and  $V_{IL}(max)$ .

- 2. Supplied as a design limit but not guaranteed or tested.

- 3. Per MIL-PRF-38535, for current density  $\leq$  5.0E5 amps/cm<sup>2</sup>, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765 pF/MHz.

- 4. Not more than one output may be shorted at a time for maximum duration of one second.

- 5. Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and V<sub>SS</sub> at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

- 6. Maximum allowable relative shift equals 50mV.

- 7. All specifications valid for radiation dose  $\leq$  1E6 rads(Si).

- 8. Power does not include power contribution of any TTL output sink current.

- 9. Power dissipation specified per switching output.

- 10. This value is guaranteed based on characterization data, but not tested.

# AC ELECTRICAL CHARACTERISTICS <sup>2</sup>

| SYMBOL                       | PARAMETER                                                                 | MINIMUM | MAXIMUM | UNIT |

|------------------------------|---------------------------------------------------------------------------|---------|---------|------|

| t <sub>PHL</sub>             | CLK or CLK INH to $Q_H$ or $\overline{Q}_H$                               | 2       | 21      | ns   |

| t <sub>PLH</sub>             | CLK or CLK INH to $Q_H$ or $\overline{Q}_H$                               | 2       | 18      | ns   |

| t <sub>PHL</sub>             | SH/ $\overline{\text{LD}}$ to $Q_{\text{H}}$ or $\overline{Q}_{\text{H}}$ | 2       | 21      | ns   |

| t <sub>PLH</sub>             | $SH/\overline{LD}$ to $Q_H$ or $\overline{Q}_H$                           | 2       | 18      | ns   |

| t <sub>PHL</sub>             | H to Q <sub>H</sub>                                                       | 2       | 21      | ns   |

| t <sub>PLH</sub>             | H to Q <sub>H</sub>                                                       | 2       | 17      | ns   |

| t <sub>PHL</sub>             | H to $\overline{Q}_{H}$                                                   | 2       | 20      | ns   |

| t <sub>PLH</sub>             | H to $\overline{Q}_{H}$                                                   | 2       | 18      | ns   |

| f <sub>MAX</sub>             | Maximum clock frequency                                                   |         | 71      | MHz  |

| t <sub>SU1</sub>             | SER, SH/LD, CLKINH or CLK<br>Setup time before CLK ↑ or CLK INH ↑         | 7       |         | ns   |

| t <sub>SU2</sub>             | Data setup time before SH/LD                                              | 7       |         | ns   |

| t <sub>H1</sub>              | SER hold time after CLK or CLK INH $\uparrow$                             | 2       |         | ns   |

| t <sub>H2</sub>              | CLK INH hold time after CLK ↑                                             | 2       |         | ns   |

| t <sub>H3</sub> <sup>3</sup> | Hold time for any input after SH/LD                                       | 2       |         | ns   |

| t <sub>W</sub>               | Minimum pulse width<br>CLK or CLK INH high<br>CLK or CLK INH low<br>SH/LD | 7       |         | ns   |

$(V_{DD} = 5.0V \pm 10\%; V_{SS} = 0V^{-1}, -55^{\circ}C < T_C < +125^{\circ}C);$  Unless otherwise noted, Tc is per the temperature range ordered.

Notes:

Notes: 1. Maximum allowable relative shift equals 50mV. 2. All specifications valid for radiation dose  $\leq 1E6$  rads(Si). 3. Based on characterization, hold time (t<sub>H3</sub>) of 0ns for data pins A-H, can be assumed if data setup time (t<sub>SU2</sub>) is  $\geq 10$ ns. This is guaranteed, but not tested.

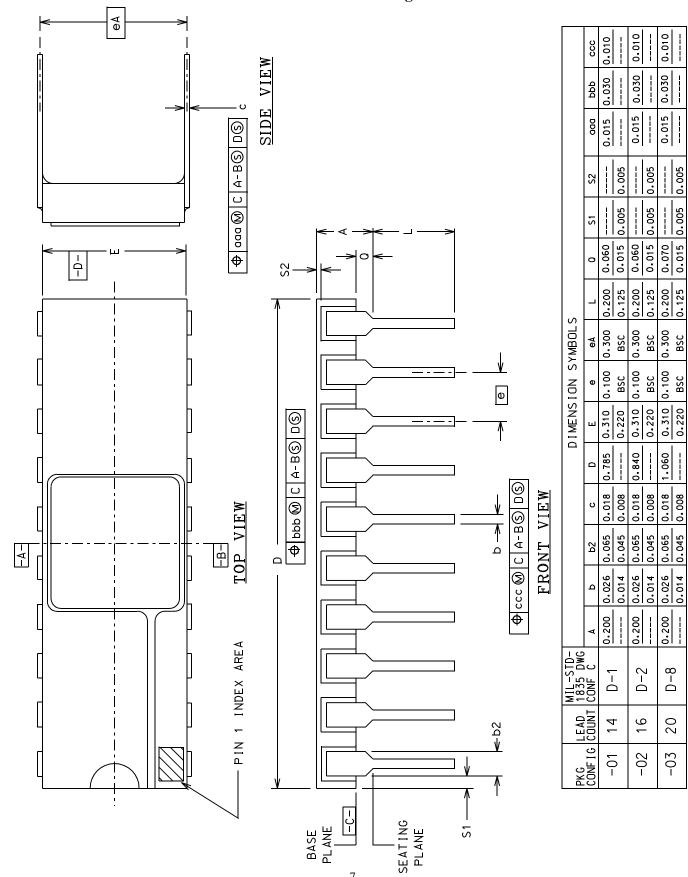

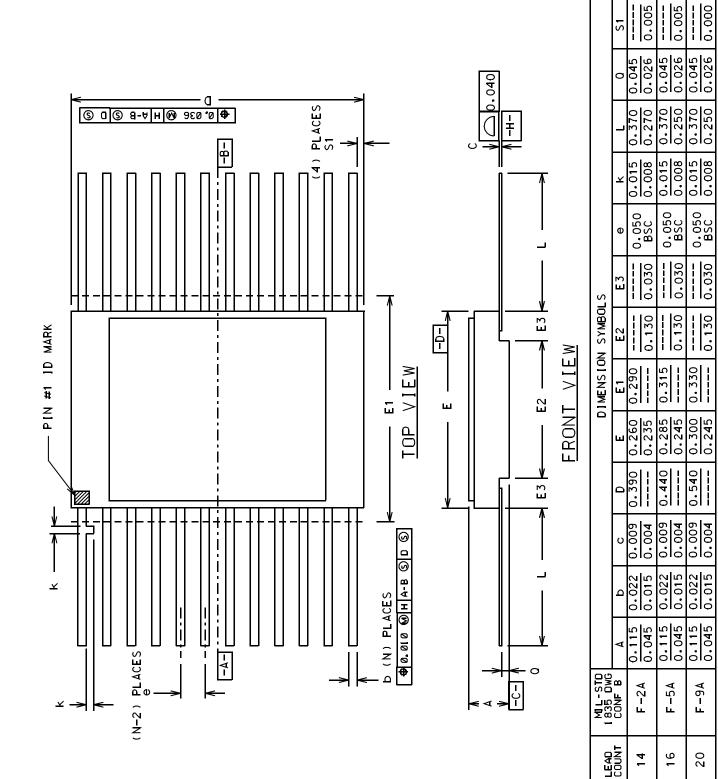

# PACKAGING

# **Side-Brazed Packages**

# FLATPACK PACKAGES

PKG CONFI G

-03

-05

-04

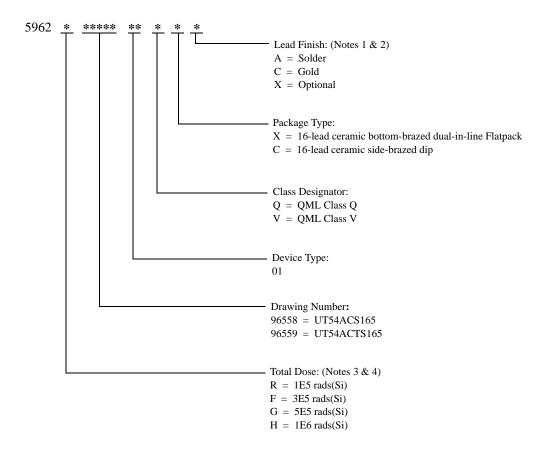

### UT54ACS165/UT54ACTS165: SMD

#### Notes:

- 1. Lead finish (A,C, or X) must be specified.

- 2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3. Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening. For prototype inquiries, contact factory.

- 4. Device type 02 is only offered with a TID tolerance guarantee of 3E5 rads(Si) or 1E6 rads(Si) and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A and section 3.11.2. Device type 03 is only offered with a TID tolerance guarantee of 1E5 rads(Si), 3E5 rads(Si), and 5E5 rads(Si), and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A.

# Aeroflex Colorado Springs - Datasheet Definition

Advanced Datasheet - Product In Development Preliminary Datasheet - Shipping Prototype Datasheet - Shipping QML & Reduced Hi-Rel

**COLORADO** Toll Free: 800-645-8862 Fax: 719-594-8468 **INTERNATIONAL** Tel: 805-778-9229 Fax: 805-778-1980

**SE AND MID-ATLANTIC** Tel: 321-951-4164 Fax: 321-951-4254 **WEST COAST** Tel: 949-362-2260 Fax: 949-362-2266 Fax: 603-888-4585 CENTRAL Tel: 719-594-8017

Fax: 719-594-8468

Tel: 603-888-3975

NORTHEAST

www.aeroflex.com info-ams@aeroflex.com

Aeroflex UTMC Microelectronic Systems Inc. (Aeroflex) reserves the right to make changes to any products and services herein at any time without notice. Consult Aeroflex or an authorized sales representative to verify that the information in this data sheet is current before using this product. Aeroflex does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by Aeroflex; nor does the purchase, lease, or use of a product or service from Aeroflex convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of Aeroflex or of third parties.

Our passion for performance is defined by three attributes represented by these three icons: solution-minded, performance-driven and customer-focused