73S8014BN

DS 8014BN 057

#### DESCRIPTION

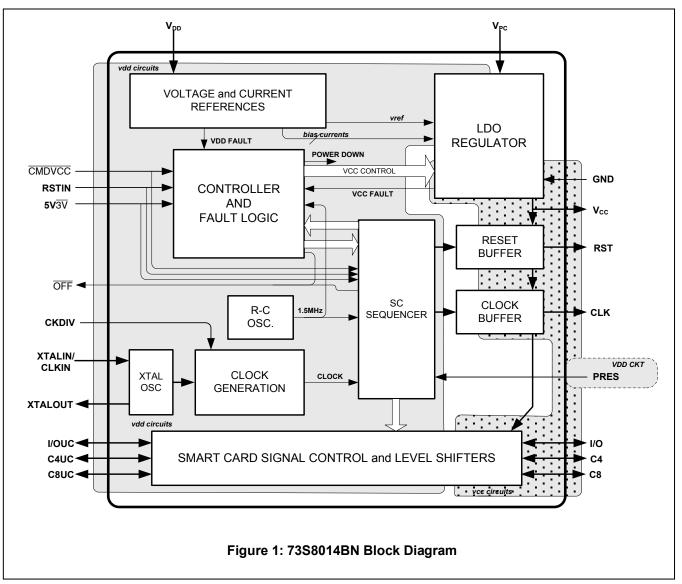

The 73S8014BN is a single smart card (ICC) interface circuit designed to provide full electrical compliance with ISO 7816-3, EMV® 4.2, and NDS specifications. It is derived from the 73S8024RN industry-standard electrical interface, but adds support for 1.8V smart card applications. The 73S8014BN has been optimized to match set-top box/A/V conditional access applications. The optimization adds functionality while creating a device with a smaller pin count. For NDS applications requiring an on-chip adjustable POR, see the Maxim 73S8024RN series of interface ICs.

The 73S8014BN interfaces with the host processor through the same bus (digital I/Os) as the 73S8024RN and most other 8024 type devices. As a result, the 73S8014BN is a very attractive cost-reduction path from traditional 8024 ICs.

Interfacing with the system controller is done through a control bus, composed of digital inputs to control the 73S8014BN, and one interrupt output to inform the system controller of the card presence, device readiness and faults.

The card clock can be generated by an on-chip oscillator using an external crystal or by connection to an externally supplied clock signal. In addition, the clock divider provides divisor values of divide by 1, 2, 4, and 8 that are controlled through a single pin.

The 73S8014BN incorporates an ISO 7816-3 activation/deactivation sequencer that controls the card signals. Level-shifters drive the card signals with the selected card voltage (1.8V, 3V, or 5V), coming from an internal low dropout (LDO) voltage regulator. This LDO regulator is powered by a dedicated power-supply input,  $V_{PC}$ . Digital circuitry is powered separately by a digital power supply,  $V_{DD}$ . With its embedded LDO regulator, the 73S8014BN is a cost-effective solution for any application where a 5V (typically -5% +10%) power supply is available.

Emergency card deactivation is initiated upon card extraction or upon any fault detected by the protection circuitry. The fault can be a card overcurrent, V<sub>CC</sub> undervoltage, or power-supply fault (V<sub>DD</sub>). The card overcurrent circuitry is a true current-detection function, as opposed to V<sub>CC</sub> voltage drop detection, as usually implemented in non-Maxim 8024 interface ICs.

The 73S8014BN contains a power-down mode with typical power consumption of  $1\mu A$  on each of the  $V_{DD}$  and  $V_{PC}$  supplies. The power-down mode is controlled through existing control pins without the need for a dedicated control pin.

Set-Top Box Conditional Access and Pay-per-View

Smart Card Interface

General-Purpose Smart Card Readers

#### **ADVANTAGES**

•

- NDS Compliant

- Same Advantages as the Maxim 73S80xxR Family:

- Card V<sub>CC</sub> Generated by an LDO Regulator

- Very Low Power Dissipation (Saves Up to 1/2W)

- Fewer External Components Are Required

- Better Noise Performance

- True Card Overcurrent Detection

- Firmware Compatibility with 8024 ICs

- Small-Format 20-Pin SO Package Capable of Fully

Supporting NDS Applications

- Power-Down Mode

#### FEATURES

- Card Interface

- Complies with ISO 7816-3, EMV 4.2, and NDS

- Supports 3V/5V Cards Up to 65mA and 1.8V Cards Up to 40mA

- ISO 7816-3 Activation/Deactivation Sequencer

- Automated Deactivation Upon Hardware Fault (i.e., Upon Drop on V<sub>DD</sub> Power Supply or Card Overcurrent)

- Overcurrent Detection 145mA max

- Card CLK Clock Frequency Up to 20MHz

#### System Controller Interface

- Three Digital Inputs Control the Card Activation/Deactivation, Card Reset, Power-Down, and Card Voltage

- One Digital Input Controls the Card Clock Frequency

- One Digital Output, Interrupt to the System Controller, Reports to the Host the Card Presence, Device Readiness, and Faults

- Crystal Oscillator or Host Clock, Up to 27MHz

- Regulator Power Supply

- 4.75V to 5.5V (EMV 4.2)

- 4.85V to 5.5V (NDS)

- Digital Interfacing: 2.7V to 3.6V

- ±6kV ESD Protection on the Card Interface

- 20-Pin SO Package

- RoHS-Compliant (6/6)/Lead(Pb)-Free Package

EMV is a registered trademark of EMVCo LLC.

Downloaded from: http://www.datasheetcatalog.com/

## FUNCTIONAL DIAGRAM

# **Table of Contents**

| 1    | Pine  | out                                  | 5  |

|------|-------|--------------------------------------|----|

| 2    | Elec  | ctrical Specifications               | 8  |

| 2.1  |       | Absolute Maximum Ratings             |    |

| 2.2  | 2     | Recommended Operating Conditions     | 8  |

| 2.3  | 3     | Smart Card Interface Requirements    | 9  |

| 2.4  | 4     | Digital Signals Characteristics      |    |

| 2.5  | 5     | DC Characteristics                   | 12 |

| 2.6  | 6     | Voltage Fault-Detection Circuits     | 12 |

| 3    | Арр   | plications Information               | 13 |

| 3.1  | 1     | Example 73S8014BN Schematics         |    |

| 3.2  | 2     | System Controller Interface          |    |

| 3.3  | 3     | Power-Down Mode                      |    |

| 3.4  | 4     | Power Supply and Voltage Supervision |    |

| 3.5  | 5     | Card Power Supply                    |    |

| 3.6  | -     | On-Chip Oscillator and Card Clock    |    |

| 3.   | -     | Activation Sequence                  |    |

| 3.8  | -     | Deactivation Sequence                |    |

| 3.9  |       | Fault Detection and OFF              | 20 |

|      | 10    | I/O, C4, and C8 Circuitry and Timing |    |

| 4    | Equ   | uivalent Circuits                    | 22 |

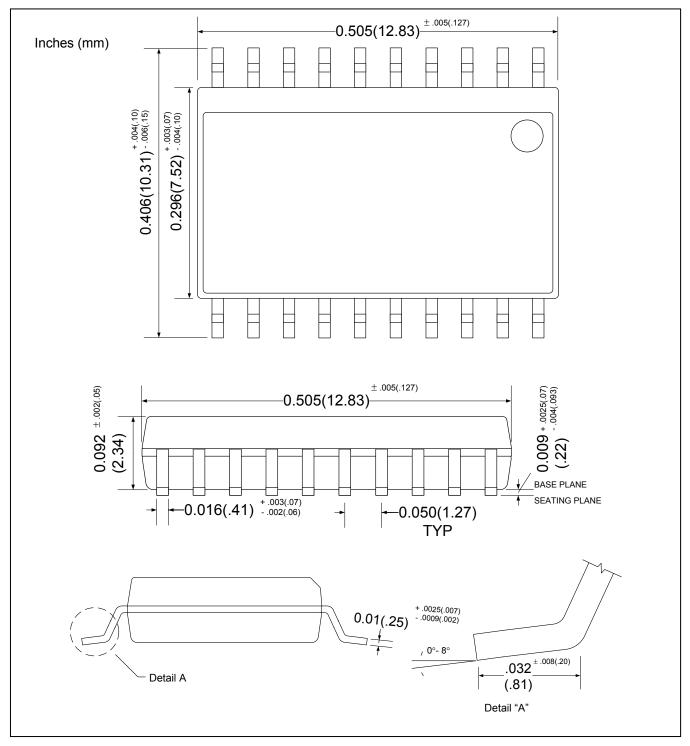

| 5    | Mec   | chanical Drawing                     | 27 |

| 6    | Ord   | lering Information                   |    |

|      |       | ntact Information                    |    |

| Revi | isioı | n History                            | 29 |

# Figures

| Figure 1: 73S8014BN Block Diagram                                                         | 2  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2: 73S8014BN 20-SO Pinout                                                          |    |

| Figure 3: 73S8014BN—Typical Application Schematic                                         | 14 |

| Figure 4: Power-Down Mode and PRES Debounce                                               |    |

| Figure 5: CLKDIV Usage                                                                    |    |

| Figure 6: Activation Sequence—RSTIN Low When CMDVCC Goes Low                              |    |

| Figure 7: Activation Sequence-RSTIN High When CMDVCC Goes Low                             |    |

| Figure 8: Deactivation Sequence                                                           | 19 |

| Figure 9: Timing Diagram—Management of the Interrupt Line OFF                             | 20 |

| Figure 10: I/O and I/OUC State Diagram                                                    | 21 |

| Figure 11: Timing Diagram—I/O to I/OUC Delays                                             | 21 |

| Figure 12: Open-Drain Type—OFF                                                            |    |

| Figure 13: Power Input/Output Circuit—V <sub>DD</sub> , V <sub>PC</sub> , V <sub>CC</sub> | 22 |

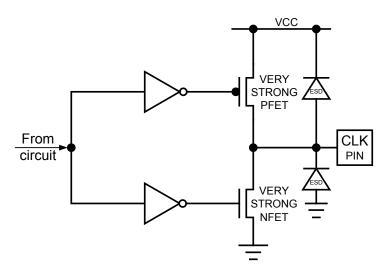

| Figure 14: Smart Card CLK Driver Circuit                                                  | 23 |

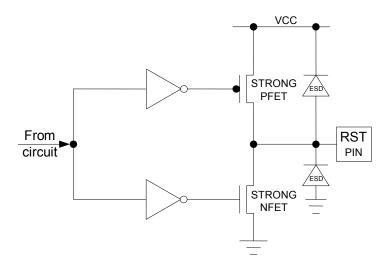

| Figure 15: Smart Card RST Driver Circuit                                                  | 23 |

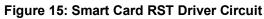

| Figure 16: Smart Card I/O, C4, and C8 Interface Circuit                                   | 24 |

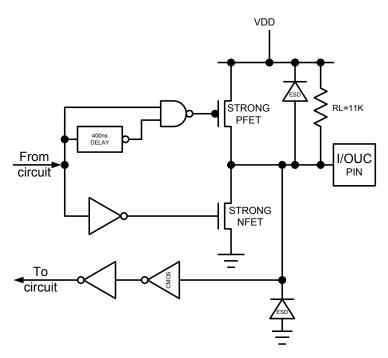

| Figure 17: Smart Card I/OUC Interface Circuit                                             | 24 |

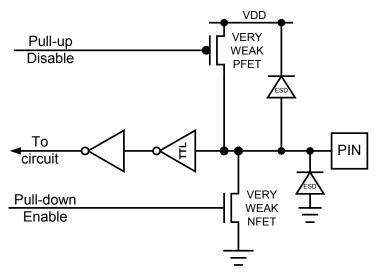

| Figure 18: General Input Circuit                                                          |    |

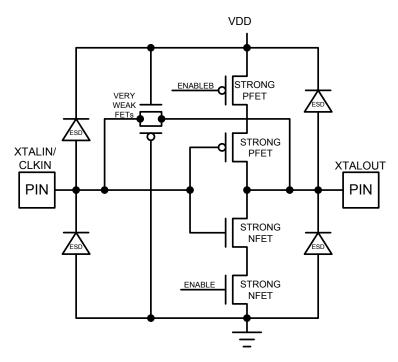

| Figure 19: Oscillator Circuit                                                             |    |

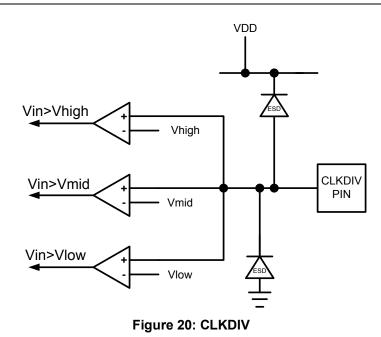

| Figure 20: CLKDIV                                                                         |    |

| Figure 21: Mechanical Drawing 20-Pin SO Package                                           |    |

|                                                                                           |    |

## Tables

| Table 1: 73S8014BN 20-Pin SO Pin Definitions          | 6  |

|-------------------------------------------------------|----|

| Table 2: Absolute Maximum Device Ratings              | 8  |

| Table 3: Recommended Operating Conditions             |    |

| Table 4: DC Smart Card Interface Requirements         | 9  |

| Table 5: Digital Signals Characteristics              | 11 |

| Table 6: DC Characteristics                           | 12 |

| Table 7: Voltage and Current Fault-Detection Circuits | 12 |

| Table 8: V <sub>CC</sub> Voltage Logic Table          | 15 |

| Table 9: Order Numbers and Packaging Marks            |    |

| Table 9: Order Numbers and Packaging Marks            | 28 |

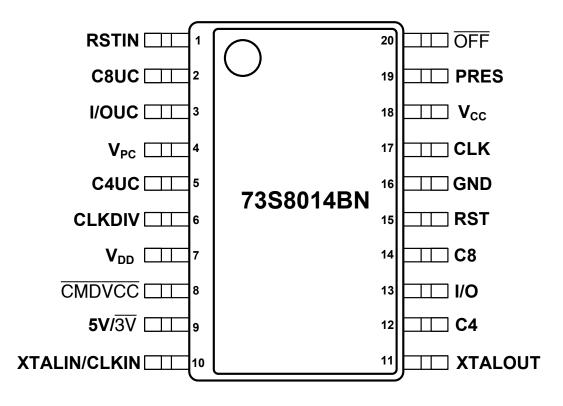

# 1 Pinout

The 73S8014BN is offered in a 20-pin SO package.

Figure 2: 73S8014BN 20-SO Pinout

Table 1 provides the 73S8014BN pin names, pin numbers, type, equivalent circuits, and descriptions.

| NAME                                 | PIN    | ТҮРЕ | EQUIVALENT<br>CIRCUIT<br>FIGURE # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------------------------------------|--------|------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CARD INTE                            | RFACE  |      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| I/O                                  | 13     | ю    | Figure 16                         | Card I/O: Data Signal to/from Card. Includes an 11k $\Omega$ pullup resistor to $V_{\text{CC.}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| C4                                   | 12     | ю    | Figure 16                         | Card C4: Data Signal to/from Card. Includes an 11k $\Omega$ pullup resistor to $V_{\text{CC.}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| C8                                   | 14     | ю    | Figure 16                         | Card C8: Data Signal to/from Card. Includes an 11k $\Omega$ pullup resistor to $V_{\text{CC.}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RST                                  | 15     | 0    | Figure 15                         | Card Reset. Provides reset (RST) signal to card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| CLK                                  | 17     | 0    | Figure 14                         | Card Clock: Provides clock signal (CLK) to card. The rate of this clock is determined by the external crystal frequency or frequency of the external clock signal applied on XTALIN and CLKDIV selections.                                                                                                                                                                                                                                                                                                                                                |  |  |

| PRES                                 | 19     | I    | Figure 18                         | Card Presence Switch. Active high indicates the card is present.<br>Includes a high-impedance pulldown current source. The PRES<br>input includes a 5ms debounce for card insertion.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| V <sub>cc</sub>                      | 18     | PSO  | Figure 13                         | Card Power Supply. Logically controlled by sequencer, output of LDO regulator. Requires an external filter capacitor to the card GND.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GND 16 GND — Card and Digital Ground |        |      |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| HOST PRO                             | CESSOF |      | FACE                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CMDVCC                               | 8      | I    | Figure 18                         | Command $V_{CC}$ (Negative Assertion). Logic-low on this pin causes the LDO regulator to ramp the $V_{CC}$ supply to the card and initiates a card activation sequence, only when a card is present.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 5V/3V                                | 9      | I    | Figure 18                         | 5V/3V/1.8V Card Selection. Logic-high selects 5V for V <sub>CC</sub> and card interface. Logic-low selects 3V operation. Logic going from high to low within ±400ns of $\overline{CMDVCC}$ falling selects 1.8V. When the device is to be used with a single card voltage (3V or 5V only), this pin should be connected to either GND or V <sub>DD</sub> . However, it includes a high-impedance pullup resistor to default this pin high (selection of 5V card) when not connected. Do not change the level of this pin when $\overline{CMDVCC}$ is low. |  |  |

| CLKDIV                               | 6      | I    | Figure 20                         | Sets the Divide Ratio from the XTAL Oscillator (or External Clock Input) to Card Clock. This is a multilevel input that uses a ratio of the $V_{DD}$ voltage to select the clock divider as shown:<br>$\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                              |  |  |

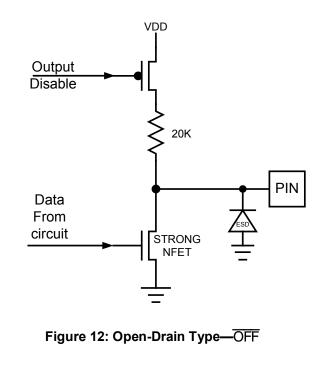

| OFF                                  | 20     | 0    | Figure 12                         | Active-Low Interrupt Signal to the Processor. Active-low multifunction indicating fault conditions, device readiness, and card presence. Open-drain output configuration. It includes an internal $20k\Omega$ pullup to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                 |  |  |

#### Table 1: 73S8014BN 20-Pin SO Pin Definitions

| NAME                                                                               | PIN                                                                                                                                 | ТҮРЕ  | EQUIVALENT<br>CIRCUIT<br>FIGURE # | DESCRIPTION                                                                                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RSTIN                                                                              | 1                                                                                                                                   | I     | Figure 18                         | Reset Input. Within a card session, this signal is the reset command to the card. Outside a card session, this signal is used to place the device in power-down. |  |  |  |  |

| C8UC                                                                               | 2                                                                                                                                   | ю     | Figure 17                         | System Controller Data C8 to/from the Card. Includes an $11 k\Omega$ pullup resistor to $V_{\text{DD.}}$                                                         |  |  |  |  |

| I/OUC 3 IO Figure 17 System Controller Data I/O to/from the Card. Includes an 11kg |                                                                                                                                     |       |                                   |                                                                                                                                                                  |  |  |  |  |

| C4UC                                                                               | 5                                                                                                                                   | Ю     | Figure 17                         | System Controller Data C4 to/from the Card. Includes an $11 k\Omega$ pullup resistor to $V_{\text{DD.}}$                                                         |  |  |  |  |

| MISCELLA                                                                           | NEOUS                                                                                                                               | NPUTS | AND OUTPUTS                       |                                                                                                                                                                  |  |  |  |  |

| XTALIN/<br>CLKIN                                                                   | 10                                                                                                                                  | I     | Figure 19                         | Crystal Oscillator Input. This pin can either be connected to crystal or driven as a source for the card clock.                                                  |  |  |  |  |

| XTALOUT                                                                            | 11                                                                                                                                  | 0     | Figure 19                         | Crystal Oscillator Output. Connected to crystal. This pin can be left open if XTALIN is being used as external clock input.                                      |  |  |  |  |

| POWER SUPPLY AND GROUND                                                            |                                                                                                                                     |       |                                   |                                                                                                                                                                  |  |  |  |  |

| V <sub>DD</sub>                                                                    | V <sub>DD</sub> 7         PSO         Figure 13         System Interface Supply Voltage and Supply Voltage for Interna<br>Circuitry |       |                                   |                                                                                                                                                                  |  |  |  |  |

| V <sub>PC</sub>                                                                    | 4                                                                                                                                   | PSO   | Figure 13                         | LDO Regulator Power Supply Source                                                                                                                                |  |  |  |  |

## 2 Electrical Specifications

This section provides the following:

- Absolute Maximum Ratings

- Recommended Operating Conditions

- Smart Card Interface Requirements

- Digital Signals Characteristics

- DC Characteristics

- Voltage Fault-Detection Circuits

### 2.1 Absolute Maximum Ratings

Table 2 lists the maximum operating conditions for the 73S8014BN. Permanent device damage can occur if absolute maximum ratings are exceeded. Exposure to the extremes of the absolute maximum rating for extended periods may affect device reliability. The smart card interface pins are protected against short circuits to  $V_{CC}$ , ground, and each other.

| PARAMETER                                 | RATING                               |

|-------------------------------------------|--------------------------------------|

| Supply Voltage Range, V <sub>DD</sub>     | -0.5V to 4.0V DC                     |

| Supply Voltage Range, V <sub>PC</sub>     | -0.5V to 6.0V DC                     |

| Input Voltage for Digital Inputs          | -0.3V to (V <sub>DD</sub> + 0.5V) DC |

| Storage Temperature Range                 | -60°C to +150°C                      |

| Pin Voltage Range (except Card Interface) | -0.3V to (V <sub>DD</sub> + 0.5V) DC |

| Pin Voltage Range (Card Interface)        | -0.3V to (V <sub>CC</sub> + 0.5V) DC |

| ESD Tolerance (Card Interface Pins)*      | ±6kV                                 |

| ESD Tolerance (Other Pins)                | ±2kV                                 |

#### **Table 2: Absolute Maximum Device Ratings**

\*ESD testing on smart card pins is Human Body Model (HBM) condition, three pulses, each polarity referenced to ground.

Note: Smart card pins are protected against shorts between any combinations of smart card pins.

### 2.2 Recommended Operating Conditions

Function operation should be restricted to the recommended operating conditions specified in Table 3.

#### **Table 3: Recommended Operating Conditions**

| PARAMETER                             | RATING                        |

|---------------------------------------|-------------------------------|

| Supply Voltage Range, V <sub>DD</sub> | 2.7V to 3.6V DC               |

| Supply Voltage Range, V <sub>PC</sub> | 4.75V to 5.5V DC              |

| Ambient Operating Temperature Range   | -40°C to +85°C                |

| Input Voltage for Digital Inputs      | 0 to (V <sub>DD</sub> + 0.3V) |

## 2.3 Smart Card Interface Requirements

Table 4 lists the 73S8014BN smart card interface requirements.

| PARAMETER                                      | SYMBOL                    | CONDITIONS                                                                                                               | MIN           | TYP            | MAX  | UNITS |

|------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|----------------|------|-------|

|                                                | / < V <sub>PC</sub> < 5.5 | V, 2.7V < V <sub>DD</sub> < 5.5V; -40°C < T <sub>A</sub> < +8                                                            | 5°C, unless c | otherwise note | ed.) | 1     |

| (NDS conditions: 4.85V <                       | V <sub>PC</sub> < 5.5V, 1 | Inactive mode                                                                                                            | +0.1          |                |      |       |

|                                                |                           | Inactive mode, I <sub>CC</sub> = 1mA                                                                                     | -0.1          |                | +0.4 | -     |

|                                                |                           | Active mode; $I_{CC} < 65mA$ ; 5V                                                                                        | 4.65          |                | 5.25 | -     |

|                                                |                           | Active mode; I <sub>CC</sub> < 65mA; 5V, NDS condition                                                                   | 4.75          |                | 5.25 | -     |

|                                                |                           | Active mode; I <sub>CC</sub> < 65mA; 3V                                                                                  | 2.85          |                | 3.15 | -     |

|                                                |                           | Active mode; single pulse of 100mA<br>for 2µs; 5V, fixed load = 25mA<br>(Note 1)                                         | 4.6           |                | 5.25 |       |

|                                                |                           | Active mode; I <sub>CC</sub> < 40mA; 1.8V                                                                                | 1.68          |                | 1.92 |       |

| Card Supply Voltage<br>ncluding Ripple and     | V <sub>cc</sub>           | Active mode; single pulse of 100mA<br>for 2µs; 3V, fixed load = 25mA<br>(Note 1)                                         | 2.76          |                | 3.15 |       |

| Voise                                          |                           | Active mode; current pulses of<br>40nAs with peak  I <sub>CC</sub>   < 200mA,<br>t < 400ns; 5V (Note 1)                  | 4.6           |                | 5.25 |       |

|                                                |                           | Active mode; current pulses of<br>40nAs with peak  I <sub>CC</sub>   <200mA,<br>t < 400ns; 5V, NDS condition<br>(Note 1) | 4.65          |                | 5.25 |       |

|                                                |                           | Active mode; current pulses of<br>40nAs with peak  I <sub>CC</sub>   <200mA,<br>t < 400ns; 3V (Note 1)                   | 2.7           |                | 3.15 | -     |

|                                                |                           | Active mode; current pulses of<br>20nAs with peak  I <sub>CC</sub>   <100mA,<br>t < 400ns; 1.8V (Note 1)                 | 1.62          |                | 1.92 | 1     |

| / <sub>cc</sub> Ripple                         | V <sub>CCRIP</sub>        | f <sub>RIPPLE</sub> = 20kHz – 200MHz<br>(Note 1)                                                                         |               |                | 350  | mV    |

| Card Supply Output                             | ICCMAX                    | Static load current, $V_{CC} > 4.6V$ or 2.7V as selected                                                                 |               |                | 65   | mA    |

| Current                                        | -000                      | Static load current, V <sub>CC</sub> >1.65                                                                               |               |                | 40   |       |

|                                                |                           | V <sub>CC</sub> = 3V or 5V                                                                                               | 70            |                | 145  | mA    |

| cc Fault Current                               | I <sub>CCF</sub>          | V <sub>CC</sub> = 1.8V                                                                                                   | 50            |                | 110  | mA    |

| CC Slew Rate, Rise                             | V <sub>SR</sub>           | $C_F = 1.0 \mu F$ on $V_{CC}$                                                                                            | 0.06          | 0.150          | 0.30 | V/µs  |

| / <sub>CC</sub> Slew Rate, Fall                | V <sub>SF</sub>           | $C_F = 1.0 \mu F$ on $V_{CC}$                                                                                            | 0.075         | 0.150          | 0.60 | V/µs  |

| External Filter Cap (V <sub>CC</sub><br>o GND) | C <sub>FNDS</sub>         | NDS applications, $C_F$ should be<br>ceramic with low ESR (< 100m $\Omega$ )<br>(Note 1)                                 | 0.5           | 1.0            | 1.5  | μF    |

| PARAMETER                                                                                          | SYMBOL                            | CONDITIONS                                                            | MIN                    | TYP | MAX                       | UNITS |

|----------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|------------------------|-----|---------------------------|-------|

| INTERFACE REQUIREN<br>DATA SIGNALS: I/O, C4<br>HOST INTERFACES: I/O<br>(ISHORTL, ISHORTH, and VIN/ | I, C8<br>DUC, C4UC,               | <b>C8UC</b><br>ents do not pertain to I/OUC, C4UC, a                  | nd C8UC.)              |     |                           |       |

| Output Level High                                                                                  |                                   | I <sub>OH</sub> = -40μA                                               | 0.9 x V <sub>DD</sub>  |     | V <sub>DD</sub> + 0.1     |       |

| (I/OUC, C4UC, C8UC)                                                                                |                                   | I <sub>OH</sub> = 0mA                                                 | 0.75 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.1     |       |

| Output Level High                                                                                  | Vон                               | $I_{OH} = -40 \mu A (V_{CC} = 3V/5V),$<br>-20 $\mu A (V_{CC} = 1.8V)$ | 0.9 x V <sub>CC</sub>  |     | V <sub>CC</sub> + 0.1     | V     |

| (I/O, C4, C8)                                                                                      |                                   | I <sub>OL</sub> = 1mA                                                 | $0.75 V_{CC}$          |     | V <sub>CC</sub> +0.1      |       |

| Output Level Low<br>(I/OUC, C4UC, C8UC)                                                            | - V <sub>OL</sub>                 | I <sub>OL</sub> = 1mA                                                 |                        |     | 0.15 x<br>V <sub>DD</sub> | V     |

| Output Level Low<br>(I/O, C4, C8)                                                                  | VOL                               |                                                                       |                        |     | 0.15 x<br>V <sub>CC</sub> | v     |

| Input Level High<br>(I/OUC, C4UC, C8UC)                                                            | - V <sub>IH</sub>                 |                                                                       | 0.6 x V <sub>DD</sub>  |     | V <sub>DD</sub> +<br>0.30 | V     |

| Input Level High<br>(I/O, C4, C8)                                                                  | VН                                |                                                                       | 0.6 x V <sub>CC</sub>  |     | V <sub>CC</sub> + 0.30    | v     |

| Input Level Low<br>(I/OUC, C4UC, C8UC)                                                             | - V <sub>IL</sub>                 |                                                                       | -0.15                  |     | 0.20 x<br>V <sub>DD</sub> | V     |

| Input Level Low<br>(I/O, C4, C8)                                                                   | VL                                | I <sub>OL</sub> = 0mA                                                 | -0.15                  |     | 0.20 x<br>V <sub>CC</sub> | v     |

| Output Voltage When                                                                                | VINACT                            | I <sub>OL</sub> = 1mA                                                 |                        |     | 0.1                       | V     |

| Outside of Session                                                                                 |                                   | V <sub>IH</sub> = V <sub>CC</sub>                                     |                        |     | 0.3                       |       |

| Input Leakage                                                                                      | I <sub>LEAK</sub>                 | V <sub>IL</sub> = 0V                                                  |                        |     | 10                        | μA    |

| Input Current Low                                                                                  | IIL                               | For output low, shorted to $V_{\text{CC}}$ through 33 $\Omega$        |                        |     | 0.65                      | mA    |

| Short-Circuit Output<br>Current                                                                    | I <sub>SHORTL</sub>               | For output high, shorted to ground through $33\Omega$                 |                        |     | 15                        | mA    |

| Short-Circuit Output<br>Current                                                                    | I <sub>SHORTH</sub>               | C <sub>L</sub> = 80pF, 10% to 90%                                     |                        |     | 15                        | mA    |

| Output Rise Time, Fall<br>Times                                                                    | t <sub>R</sub> , t <sub>F</sub>   |                                                                       |                        |     | 100                       | ns    |

| Input Rise, Fall Times                                                                             | t <sub>IR</sub> , t <sub>IF</sub> | Output stable for > 400ns (Note 1)                                    |                        |     | 1                         | μS    |

| Internal Pullup Resistor                                                                           | R <sub>PU</sub>                   |                                                                       | 8                      | 11  | 15                        | kΩ    |

| Maximum Data Rate                                                                                  | FD <sub>MAX</sub>                 | Edge from master to slave, measured at 50%                            |                        |     | 1                         | MHz   |

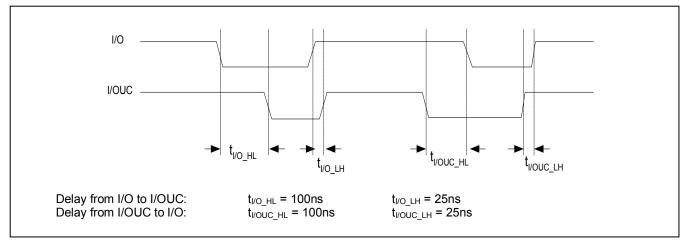

| Delay, I/O to I/OUC,<br>I/OUC to I/O, C4 to<br>C4UC, C4UC to C4, C8<br>to C8UC, C8UC to C8         | t <sub>FDIO</sub>                 |                                                                       | 60                     | 100 | 200                       | ns    |

| (Respectively Falling<br>Edge to Falling Edge<br>and Rising Edge to<br>Rising Edge)                | t <sub>RDIO</sub>                 |                                                                       |                        | 15  |                           |       |

| Input Capacitance                                                                                  | CIN                               | (Note 1)                                                              |                        |     | 10                        | pF    |

| PARAMETER                                    | SYMBOL                          | CONDITIONS                                     | MIN                   | TYP | MAX                       | UNITS |  |  |  |

|----------------------------------------------|---------------------------------|------------------------------------------------|-----------------------|-----|---------------------------|-------|--|--|--|

| RESET AND CLOCK FOR CARD INTERFACE: RST, CLK |                                 |                                                |                       |     |                           |       |  |  |  |

| Output Level High                            | V <sub>OH</sub>                 | I <sub>OH</sub> =-200μA                        | 0.9 x V <sub>CC</sub> |     | V <sub>CC</sub>           | V     |  |  |  |

| Output Level Low                             | Vol                             | I <sub>OL</sub> =200μA                         | 0                     |     | 0.15 x<br>V <sub>CC</sub> | V     |  |  |  |

| Output Voltage When                          | VINACT                          | I <sub>OL</sub> = 0mA                          |                       |     | 0.1                       | v     |  |  |  |

| Outside of Session                           |                                 | I <sub>OL</sub> = 1mA                          |                       |     | 0.3                       |       |  |  |  |

| Output Current Limit,<br>RST                 | I <sub>RST_LIM</sub>            |                                                |                       |     | 30                        | mA    |  |  |  |

| Output Current Limit,<br>CLK                 | I <sub>CLK_LIM</sub>            |                                                |                       |     | 70                        | mA    |  |  |  |

| Output Rise Time, Fall                       |                                 | $C_L$ = 35pF for CLK, 10% to 90%               |                       |     | 8                         |       |  |  |  |

| Time                                         | t <sub>R</sub> , t <sub>F</sub> | $C_L$ = 200pF for RST, 10% to 90%              |                       |     | 100                       | ns    |  |  |  |

| Duty Cycle for CLK                           | δ                               | C <sub>L</sub> =35pF, f <sub>CLK</sub> ≤ 20MHz | 45                    |     | 55                        | %     |  |  |  |

Note 1: Guaranteed by design; not production tested.

## 2.4 Digital Signals Characteristics

Table 5 lists the 73S8014BN digital signals characteristics.

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                         | MIN                     | TYP | MAX                    | UNITS |

|--------------------------------------------------|---------------------|------------------------------------------------------------------------------------|-------------------------|-----|------------------------|-------|

| Input Low Voltage                                | VIL                 |                                                                                    | -0.3                    |     | +0.8                   | V     |

| Input High Voltage                               | V <sub>IH</sub>     |                                                                                    | 1.8                     |     | V <sub>DD</sub> + 0.3  | V     |

| Output Low Voltage                               | V <sub>OL</sub>     | I <sub>OL</sub> = 2mA                                                              |                         |     | 0.45                   | V     |

| Output High Voltage                              | V <sub>OH</sub>     | I <sub>OH</sub> = -1mA                                                             | V <sub>DD</sub> - 0.45  |     |                        | V     |

| Pullup Resistor, OFF                             | R <sub>OUT</sub>    |                                                                                    | 13.5                    | 20  | 26.5                   | kΩ    |

| Input Leakage Current                            | I <sub>⊫1</sub>     | $V_{GND} < V_{IN} < V_{DD}$                                                        | -5                      |     | +5                     | μA    |

|                                                  | V <sub>INCD1</sub>  | Level Range 1                                                                      | -0.3                    |     | +0.400                 | V     |

| Input Loval CLKDIV                               | V <sub>INCD2</sub>  | Level Range 2                                                                      | 0.26 x V <sub>DD</sub>  |     | 0.40 x V <sub>DD</sub> |       |

| Input Level, CLKDIV                              | V <sub>INCD3</sub>  | Level Range 3                                                                      | 0.6 x V <sub>DD</sub>   |     | 0.80 x V <sub>DD</sub> |       |

|                                                  | V <sub>INCD4</sub>  | Level Range 4                                                                      | V <sub>DD</sub> - 0.400 |     | V <sub>DD</sub> + 0.3  |       |

| Input Low Voltage,<br>XTALIN                     | VILXTAL             |                                                                                    | -0.3                    |     | 0.3 x V <sub>DD</sub>  | V     |

| Input High Voltage,<br>XTALIN                    | VIHXTAL             |                                                                                    | 0.7 x V <sub>DD</sub>   |     | V <sub>DD</sub> + 0.3  | V     |

| Input Current, XTALIN                            | I <sub>ILXTAL</sub> | $V_{GND} < V_{IN} < V_{DD}$                                                        | -30                     |     | +30                    | μA    |

| Max Frequency<br>Oscillator or External<br>Clock | f <sub>MAX</sub>    |                                                                                    |                         |     | 27                     | MHz   |

| External Input Duty-<br>Cycle Limit              | δin                 | $t_{\rm R}/t_{\rm F}$ < 10% $f_{\rm IN}$ , 45% < $\delta_{\rm CLK}$ < 55% (Note 1) | 48                      |     | 52                     | %     |

## **Table 5: Digital Signals Characteristics**

Note 1: Guaranteed by design; not production tested.

## 2.5 DC Characteristics

Table 6 lists the 73S8014BN DC characteristics.

Table 6: DC Characteristics

| PARAMETER                      | SYMBOL            | CONDITIONS MIN TYP                                                                          |  | TYP | MAX | UNITS |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------------|--|-----|-----|-------|

| V <sub>DD</sub> Supply Current | I <sub>DD</sub>   | V <sub>DD</sub> = 2.7V to 3.6V                                                              |  | 2.0 | 4   | mA    |

| V <sub>DD</sub> Supply Current | I <sub>PD</sub>   | Power-down                                                                                  |  | 1   | 5   | μA    |

| V <sub>PC</sub> Supply Current | I <sub>PC</sub>   | $V_{\rm CC}$ on, $I_{\rm CC}$ = 0mA, CLK = 2.0MHz, external load < 10pF, I/O, C4, C8 = high |  | 1   | 2   | mA    |

| V <sub>PC</sub> Supply Current | I <sub>PCPD</sub> | CMDVCC = 1                                                                                  |  | 1   | 2   | μA    |

### 2.6 Voltage Fault-Detection Circuits

Table 7 lists the 73S8014BN voltage and current fault-detection circuits.

| PARAMETER                                                               | SYMBOL           | CONDITIONS                      | MIN | ТҮР | MAX  | UNITS |

|-------------------------------------------------------------------------|------------------|---------------------------------|-----|-----|------|-------|

| V <sub>DD</sub> Fault                                                   | V <sub>DDF</sub> | V <sub>DD</sub> falling 2.15    |     | 2.4 | V    |       |

| I <sub>CC</sub> Fault Current                                           | I <sub>CCF</sub> | V <sub>CC</sub> = 3V or 5V      | 70  |     | 145  | mA    |

|                                                                         |                  | V <sub>CC</sub> = 1.8V          | 50  |     | 110  |       |

| V <sub>CC</sub> Fault (V <sub>CC</sub> Voltage<br>Supervisor Threshold) | V <sub>CCF</sub> | V <sub>CC</sub> = 5V            |     |     | 4.6  | V     |

|                                                                         |                  | V <sub>CC</sub> = 3V            |     |     | 2.7  |       |

|                                                                         |                  | V <sub>CC</sub> = 1.8V (Note 1) |     |     | 1.65 |       |

Note 1: Guaranteed by design; not production tested.

# **3** Applications Information

This section provides general usage information for the design and implementation of the 73S8014BN.

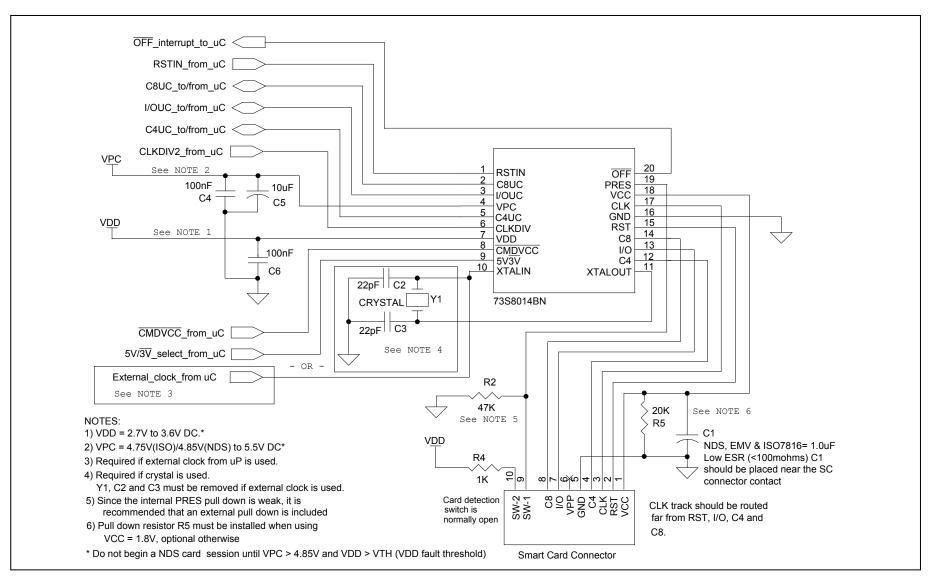

### 3.1 Example 73S8014BN Schematics

Figure 3 shows a typical application schematic for the implementation of the 73S8014BN.

Note that minor changes can occur to the reference material from time to time and the reader is encouraged to contact Maxim for the latest information.

Figure 3: 73S8014BN—Typical Application Schematic

# 3.2 System Controller Interface

Three digital inputs allow direct control of the card interface by the host. The 73S8014BN is controlled as follows:

- Pin CMDVCC: When asserted low, starts an activation sequence. When deasserted high, starts deactivation sequence.

- Pin RSTIN: Controls the card RST signal (when enabled by the sequencer) while the card is activated and the power-down mode when the card is not activated.

- Pin 5V/3V: Defines the card V<sub>DD</sub> voltage according to Table 8.

| CONTROL PINS |              | V <sub>cc</sub> |                                                                                                                                                     |  |

|--------------|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CMDVCC       | 5V/3V        | VOLTAGE<br>(V)  | NOTES                                                                                                                                               |  |

| 1            | х            | 0               | Off                                                                                                                                                 |  |

| <b>_</b>     | 1            | 5               | $5V/\overline{3V}$ must be stable for at least 1µs before assertion of $\overline{CMDVCC}$ and held high until deassertion of $\overline{CMDVCC}$ . |  |

| T.           | 0            | 3               | $5V/\overline{3V}$ must be stable for at least 1µs before assertion of CMDVCC and held low until deassertion of CMDVCC.                             |  |

| T            | _ <b>t</b> _ | 1.8             | Must be asserted low within 400ns of each other to generate $1.8V$ and held low until assertion of $\overline{CMDVCC}$ .                            |  |

Table 8: V<sub>cc</sub> Voltage Logic Table

The  $\overline{OFF}$  digital output reports status back to the host. See the Fault Detection and  $\overline{OFF}$  section for details on the operation of the  $\overline{OFF}$  output.

Note:  $5V/\overline{3V}$  should not change during a card session. Doing so does not change the voltage on V<sub>cc</sub> during that session, but if it is changed, the  $5V/\overline{3V}$  must be taken high outside the current card session and before beginning the next card session. Otherwise, the next card session may not power up to the selected V<sub>cc</sub> voltage.

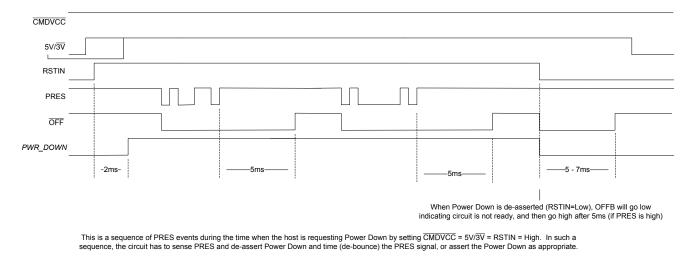

## 3.3 Power-Down Mode

The 73S8014BN includes a power-down mode to greatly reduce the power consumption on the  $V_{DD}$  and  $V_{PC}$  supplies when the smart card interface is deactivated. The power-down mode shuts down the crystal oscillator and other internal circuits to save power. When the power-down mode is released, the oscillator is restarted. It requires some time to start up and stabilize. During this time, the  $\overline{OFF}$  output goes low (if a card is inserted) and is held low until the oscillator stabilizes, and then the  $\overline{OFF}$  output goes high to indicate that the device is ready to activate the card.

The power-down mode is initiated when RSTIN,  $\overline{CMDVCC}$ , and  $5V/\overline{3V}$  are all logic-high for more than 2ms. The power-down mode is released immediately by bringing RSTIN low. This action forces the  $\overline{OFF}$  output low for approximately 5ms to 7ms to allow the oscillator to start up and stabilize. This action informs the host that the 73S8014BN is busy and should not be activated while the  $\overline{OFF}$  output is low. This ensures a proper activation sequence after coming out of power-down.

The card-detection logic on the PRES input remains active in power-down mode. The card status is reported on OFF.

**Note:** The CMDVCC and 5V/3V inputs have no effect when exiting power-down. Bringing RSTIN low is the only way to exit power-down.

Figure 4 shows the power-down mode control timing with PRES debounce. See Section 3.9 for a full description of the PRES debounce behavior.

### Figure 4: Power-Down Mode and PRES Debounce

### 3.4 **Power Supply and Voltage Supervision**

The 73S8014BN smart card interface IC incorporates a low dropout (LDO) voltage regulator for V<sub>CC</sub>. The voltage output is controlled by the digital input  $5V/\overline{3V}$  of the 73S8014BN. This regulator can provide 1.8V, 3V, or 5V card voltage from the power supply applied on the V<sub>PC</sub> pin. The voltage regulator can provide a current of at least 65mA on V<sub>CC</sub> for both 3V and 5V or 40mA for 1.8V that complies with EMV 4.0 and NDS specifications. An overcurrent supervisor triggers a fault if the current on V<sub>CC</sub> exceeds the threshold at the given V<sub>CC</sub> voltage.

Digital circuitry is powered by the power supply applied on the  $V_{DD}$  pin.  $V_{DD}$  is sourced by 2.7 to 3.6V so the system controller must operate with this supply level. A card deactivation sequence is forced upon fault of any voltage or overcurrent supervisor. One supervisor monitors the  $V_{CC}$  output voltage at the selected  $V_{CC}$  voltage level. The maximum  $V_{CC}$  voltage-fault threshold does not exceed the minimum  $V_{CC}$  voltage spec according to ISO 7816. See  $V_{CCF}$  specification for the  $V_{CC}$  voltage thresholds. Another voltage supervisor constantly monitors the  $V_{DD}$  voltage. This fixed threshold supervisor is used to initialize the ISO 7816-3 sequencer at power-on and to deactivate the card at power-off or upon fault. The voltage threshold of the  $V_{DD}$  voltage supervisor is internally set to 2.26V typical ( $V_{DDF}$ ). If an adjustable  $V_{DD}$  threshold (>2.26V) is required on the device, then the 73S8024RN should be considered or an external circuit configured for the desired  $V_{DD}$  threshold should be added to the circuit to control either the <u>CMDVCC</u> or PRES input for an immediate  $V_{CC}$  deactivation.

**Note:** Since the V<sub>DD</sub> and the V<sub>PC</sub> power supplies are separate, special care must be taken to ensure that the V<sub>PC</sub> voltage is greater than 4.85V before beginning activating the card. In addition, V<sub>DD</sub> must be greater than the threshold for V<sub>DD</sub> fault before card activation. When turning off power to the V<sub>DD</sub> and the V<sub>PC</sub> power supplies, the card should be deactivated before shutdown or the V<sub>PC</sub> power supply must remain higher than 4.85V when the V<sub>DD</sub> fault is detected and the emergency deactivation sequence is completed.

### 3.5 Card Power Supply

The 73S8014BN smart card interface IC incorporates an LDO voltage regulator for V<sub>CC</sub>. The voltage output is controlled by the digital inputs  $5V/\overline{3V}$  and  $\overline{CMDVCC}$  of the 73S8014BN. This regulator can provide 1.8V, 3V, or 5V card voltage from the power supply applied on the V<sub>PC</sub> pin. The voltage regulator can provide a current of at least 65mA on V<sub>CC</sub> for both 3V and 5V and 40mA for 1.8V that complies with EMV 4.2 and NDS specifications.

Note: When using  $V_{cc} = 1.8V$ , a minimum load is required on  $V_{cc}$  to ensure proper output regulator stability. A 20k $\Omega$  resistor is required between  $V_{cc}$  and GND to meet this minimum load requirement. If  $V_{cc} = 1.8V$  is never used in a given application, the resistor is not required.

## 3.6 On-Chip Oscillator and Card Clock

The 73S8014BN device has an on-chip oscillator that can generate the smart card clock using an external crystal (connected between XTALIN and XTALOUT) to set the oscillator frequency. When the clock signal is available from another source it can be connected to XTALIN, and XTALOUT should be left unconnected.

For this device the card clock frequency can be chosen among four different division rates, defined by multiplestate input CLKDIV, as per the following table:

| CLKDIV                | CLK        | MAX<br>XTALIN/CLKIN<br>(MHz) |

|-----------------------|------------|------------------------------|

| GND                   | 1/4 XTALIN | 27                           |

| V <sub>DD</sub> /3    | XTALIN     | 20                           |

| V <sub>DD</sub> x 2/3 | 1/8 XTALIN | 27                           |

| V <sub>DD</sub>       | 1/2 XTALIN | 27                           |

Note: The clock-divider ratio must be configured prior to activation and must not change during the card session.

**Note:** Special care should be taken when configuring the CLKDIV input when using the power-down mode. The CLKDIV input does not contain an internal pullup or pulldown so it must not be allowed to be left unconnected. In addition, the CLKDIV input should be set in such a manner as to set the voltage level to GND or  $V_{DD}$  to keep the current consumption to an absolute minimum.

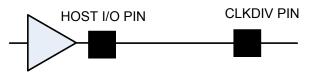

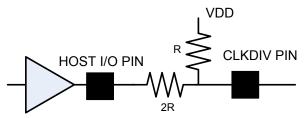

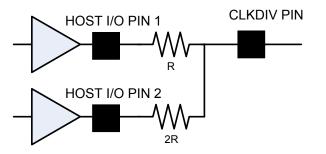

There are numerous simple methods available to control CLKDIV as shown in Figure 5.

1. Selecting between Divide by 2 (I/O HIGH) or divide by 4 (I/O LOW)

2. Selecting between Divide by 2 (IO HIGH) or divide by 8 (IO LOW)

3. Selecting any of the four Divide ratios

Figure 5: CLKDIV Usage

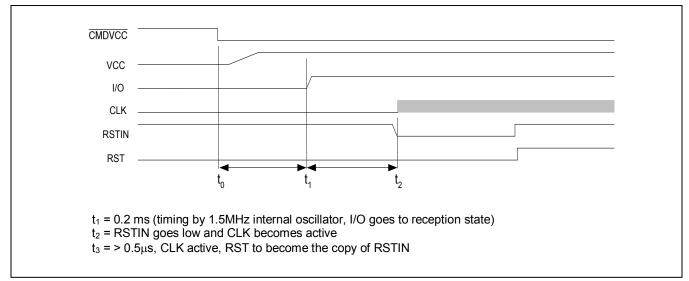

## 3.7 Activation Sequence

The 73S8014BN smart card interface IC has an internal 1ms delay on the application of  $V_{DD}$  where  $V_{DD} > V_{DDF}$ . No activation is allowed during this 1ms period. The  $\overline{CMDVCC}$  (edge triggered) signal must then be set low to activate the card. To initiate activation, the card must be present and there can be no  $V_{DD}$  fault.

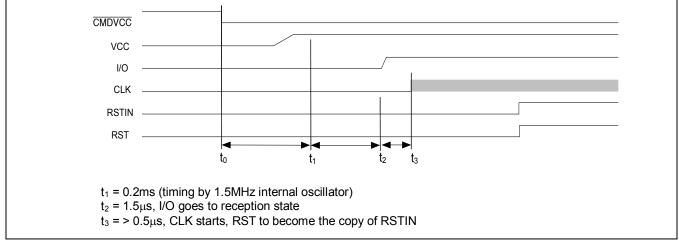

The following steps show the activation sequence and the timing of the card control signals when the system controller sets  $\overline{\text{CMDVCC}}$  low while the RSTIN is low:

- <u>CMDVCC</u> is set low at t<sub>0</sub>.

- $V_{CC}$  rises to the selected level and then the internal  $V_{CC}$  control circuit checks the presence of  $V_{CC}$  at the end of  $t_1$ . In normal operation, the voltage  $V_{CC}$  to the card becomes valid before  $t_1$ . If  $V_{CC}$  is not valid at  $t_1$ ,  $\overrightarrow{OFF}$  goes low to report a fault to the system controller, and  $V_{CC}$  to the card is shut off.

- Turn I/O to reception mode at t<sub>2</sub>.

- CLK is applied to the card at t<sub>3</sub>.

- RST is a copy of RSTIN after t<sub>3</sub>.

#### Figure 6: Activation Sequence—RSTIN Low When CMDVCC Goes Low

The startup of the CLK output can be delayed in the activation sequence by setting the RSTIN input high before beginning activation by bringing  $\overline{CMDVCC}$  low. The CLK output is delayed until RSTIN is taken low. Special care must be taken when performing this type of activation. The power-down mode is initiated by setting the RSTIN and  $5V/\overline{3V}$  inputs high while  $\overline{CMDVCC}$  is high (outside a card session). If this state is held for more than 2ms, the power mode is initiated. As a result, to use this activation mode, the  $\overline{CMDVCC}$  falling edge must occur within 1ms of the RSTIN input being set high. The following steps show the activation sequence and the timing of the card control signals when the system controller pulls the  $\overline{CMDVCC}$  low while the RSTIN is high:

- $\overline{CMDVCC}$  is set low at t<sub>0</sub>.

- V<sub>CC</sub> rises to the selected level and then the internal V<sub>CC</sub> control circuit checks the presence of V<sub>CC</sub> at the end of t<sub>1</sub>. In normal operation, the voltage V<sub>CC</sub> to the card becomes valid before t<sub>1</sub>. If V<sub>CC</sub> is not valid at t<sub>1</sub>, OFF goes low to report a fault to the system controller, and V<sub>CC</sub> to the card is shut off.

- At the fall of RSTIN (under host control) at t<sub>2</sub>, CLK is applied to the card.

- RST is a copy of RSTIN after t<sub>2</sub>.

Figure 7: Activation Sequence—RSTIN High When CMDVCC Goes Low

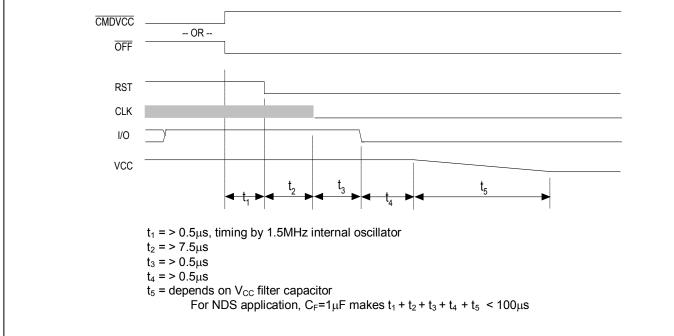

### 3.8 Deactivation Sequence

Deactivation is initiated either by the system controller by setting the  $\overline{CMDVCC}$  high or automatically in the event of hardware faults. Hardware faults are overcurrent, V<sub>DD</sub> fault, V<sub>CC</sub> fault, and card extraction during the session.

The following steps show the deactivation sequence and the timing of the card control signals when the system controller sets the  $\overline{CMDVCC}$  high or  $\overline{OFF}$  goes low due to a fault or card removal:

- RST goes low at the end of t<sub>1</sub>.

- CLK is set low at the end of t<sub>2</sub>.

- I/O goes low at the end of t<sub>3</sub>. Out of reception mode.

- $V_{CC}$  is shut down at the end of time t<sub>4</sub>. After a delay t<sub>5</sub> (discharge of the V<sub>CC</sub> capacitor), V<sub>CC</sub> is low.

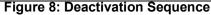

## 3.9 Fault Detection and OFF

There are two different cases that the system controller can monitor the  $\overline{OFF}$  signal: to query regarding the card presence and device readiness outside card sessions, or for fault detection during card sessions. The  $\overline{OFF}$  interrupt output operates as follows:

As long as the card is not activated (CMDVCC is always high), OFF informs the host about the card presence or device readiness. When no card is inserted, the OFF output is low. When a card is inserted, the OFF output is set high after a 5ms debounce period. Upon card removal, there is no debounce on the PRES input as the emergency deactivation must occur as soon as possible to prevent any potential card errors or data corruption. The OFF output goes low immediately upon detection of a logic-low on the PRES input, but the OFF output does not bounce and remains low for at least 5ms.

In addition, when a card is present and the power-down mode is released, the  $\overline{OFF}$  output is taken low for about 5ms to indicate that the device is not ready. This time allows the crystal oscillator to start up and stabilize. When  $\overline{CMDVCC}$  is asserted low (card activation sequence requested from the host), low level on  $\overline{OFF}$  means a fault has been detected (e.g., card removal during card session, voltage fault, or overcurrent fault) that automatically initiates a deactivation sequence.

Figure 9 shows the timing diagram for the signals CMDVCC, PRES, and OFF while the card is activated and deactivated:

Figure 9: Timing Diagram—Management of the Interrupt Line OFF

## 3.10 I/O, C4, and C8 Circuitry and Timing

The I/O, C4, and C8 are smart card data signals that operate identically, and I/OUC, C4UC, and C8UC are the corresponding microcontroller interface signals. The I/O and I/OUC data signals are described henceforth. The state of the I/O and I/OUC pins are low after power-on reset and goes high when the activation sequencer turns on the I/O reception state. See the Activation Sequence section for details on when the I/O reception is enabled. The state of I/OUC is high after power-on reset.

When the card is activated and the I/O reception state is turned on, the first I/O line on which a falling edge is detected becomes the input I/O line and the other becomes the output I/O line. When the input I/O line rising edge is detected, both I/O lines return to their neutral state.

**Note:** In certain situations and conditions, the I/O logic can get confused if the host and the card attempt to drive the I/OUC and the I/O signal low at the same time. It should be noted that this is an illegal condition as all card communication is initiated by the host with a command/response protocol. The next host command should not be sent until a valid response has been completely received from the card. However, if this condition should occur, the 73S8014BN could set both I/OUC and I/O as outputs where they are both driven low at the same time. When either side drives their respective signal high, this mode should be released. However, if there is a series resistance between the host and the 73S8014BN, there may not be enough drive to release this mode. If the series resistance is greater than approximately  $100\Omega$ , this can cause this mode to become locked for the duration of the card session. If the host detects this condition (I/OUC held low for more than 1 byte time), the card session must be terminated and restarted.

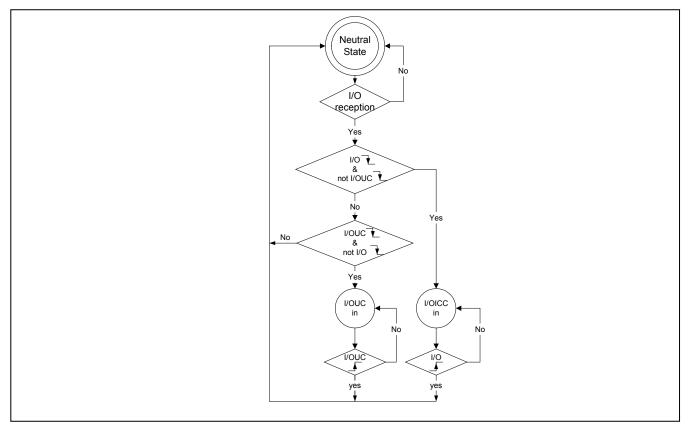

Figure 10 shows the state diagram of how the I/O and I/OUC lines are managed to become input or output. The delay between the I/O signals is shown in Figure 11.

Figure 10: I/O and I/OUC State Diagram

Figure 11: Timing Diagram—I/O to I/OUC Delays

# **4** Equivalent Circuits

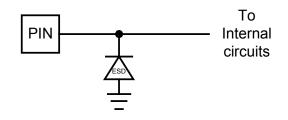

This section provides illustrations of circuits equivalent to those described in the pinout section.

Figure 13: Power Input/Output Circuit— $V_{DD}$ ,  $V_{PC}$ ,  $V_{CC}$

Figure 14: Smart Card CLK Driver Circuit

Figure 16: Smart Card I/O, C4, and C8 Interface Circuit

Figure 17: Smart Card I/OUC Interface Circuit

Note:  $5V/\overline{3V}$  has the pullup enabled. PRES has the pulldown enabled. CMDVCC and RSTIN have pullup and pulldown disabled.

Figure 19: Oscillator Circuit

# 5 Mechanical Drawing

Figure 21: Mechanical Drawing 20-Pin SO Package

# 6 Ordering Information

Table 9 lists the order numbers and packaging marks used to identify 73S8014BN products.

| PART            | PIN-PACKAGE | TOP MARK  |

|-----------------|-------------|-----------|

| 73S8014BN-IL/F  | 20 SO       | 73S8014BN |

| 73S8014BN-ILR/F | 20 SO       | 73S8014BN |

#### Table 9: Order Numbers and Packaging Marks

F = Lead(Pb)-free/RoHS-compliant package.

R = Tape and reel.

# 7 Contact Information

For more information about Maxim products or to check the availability of the 73S8014BN, contact technical support at <u>www.maxim-ic.com/support</u>.

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.0                | 12/10            | Initial release                                                                                                                                                                                                                                                                                                                                 | —                |

| 2                  | 12/11            | Deleted "Certification Pending" from the NDS logo.<br>Added "designed to provide full electrical compliance with ISO<br>7816-3, EMV® 4.2, and NDS specifications" to the first<br>sentence.<br>Added "For NDS applications requiring an on-chip adjustable<br>POR, see the Maxim 73S8024RN series of interface ICs." to<br>the first paragraph. | 1                |

|                    |                  | Provided additional description to Section 3.4.                                                                                                                                                                                                                                                                                                 | 16               |

Rev. 2

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2011 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products.