# **TOSHIBA**

# Considerations for Using Both Mask ROM and Flash Products

#### Flash Memory Control Registers

Mask ROM products do not contain the flash memory control registers shown in the table below. Therefore, a program that accesses these registers operates differently between mask ROM and flash products. If you use a flash product to check the operation of a program written for a mask ROM product, be sure not to write instructions that access these registers in the program.

| Degister Name   | Address | Mask ROM Product | Flash Product  |

|-----------------|---------|------------------|----------------|

| Register Name   | Address | 89CM42, 89CH42 〈 | 89FM42, 89FH42 |

| FLSCR1          | 0x0FD0  |                  |                |

| FLSCR2 / FLSCRM | 0x0FD1  | Niet erreitekte  | A. Della La    |

| FLSSTB          | 0x0FD2  | Not available    | Available      |

| SPCR            | 0x0FD3  |                  |                |

#### Conversion Accuracy of the AD Converter

The conversion accuracy of the AD converter differs between mask ROM and flash products, as shown below. When developing your application system, careful consideration must be given to these accuracy differences.

$(V_{SS} = 0.0 \text{ V}, 4.5 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter           | Condition                             | Min      | Тур.  | / \ M            | ax               | Unit |

|---------------------|---------------------------------------|----------|-------|------------------|------------------|------|

| Non-linearity error |                                       | 1        | 1     | 89CM42<br>89CH42 | 89FM42<br>89FH42 |      |

|                     | $V_{DD} = A_{VDD} / V_{AREF} = 5.0 V$ |          | ( ) ) | ±4               | ±3               |      |

| Zero-point error    | V <sub>SS</sub> = 0.0 V               | -        | \\\   | ±4               | ±3               | LSB  |

| Full-scale error    |                                       | <u> </u> | _     | ±4               | ±3               |      |

| Total error         |                                       | 1-1      | -     | ±4               | ±3               |      |

$(V_{SS} = 0.0 \text{ V}, 2.7 \text{ V} \le V_{DD} < 4.5 \text{ V}, \text{Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter           | Condition                             | Min | Тур. | М                | ax               | Unit |

|---------------------|---------------------------------------|-----|------|------------------|------------------|------|

| Non-linearity error |                                       | _   | -    | 89CM42<br>89CH42 | 89FM42<br>89FH42 |      |

|                     | $V_{DD} = A_{VDD} / V_{AREF} = 2.7 V$ |     |      | ±4               | ±3               |      |

| Zero-point error    | V <sub>SS</sub> = 0.0 V               | -   | -    | ±4               | ±3               | LSB  |

| Full-scale error    |                                       | -   | _    | ±4               | ±3               |      |

| Total error         |                                       | -   | -    | ±4               | ±3               |      |

$(V_{SS} = 0.0 \text{ V}, 2.2 \text{ V} \le V_{DD} < 2.7 \text{ V}, \text{Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter           | Condition                                                      | Min | Тур. | М                | ax               | Unit |

|---------------------|----------------------------------------------------------------|-----|------|------------------|------------------|------|

| Non-linearity error |                                                                | _   | _    | 89CM42<br>89CH42 | 89FM42<br>89FH42 |      |

|                     | V <sub>DD</sub> = A <sub>VDD</sub> / V <sub>AREF</sub> = 2.2 V |     |      | ±5               | ±4               |      |

| Zero-point error    | V <sub>SS</sub> = 0.0 V                                        | -   | -    | ±5               | ±4               | LSB  |

| Full-scale error    |                                                                | -   | -    | ±5               | ±4               |      |

| Total error         |                                                                | -   | -    | ±5               | ±4               |      |

Precaution for Using the Emulation Chip (Development Tool)

· Precaution for debugging the voltage detection circuit

In debug using the RTE870/C1 In-Circuit Emulator (ICE mode) with the TMP89C900 mounted on it, no interrupt is generated when the supply voltage rises to the detection voltage. Since the #!Undefined!# may operate differently, take account of this difference when debugging programs.

# Revision History

| Date      | Revision |                  |

|-----------|----------|------------------|

| 2008/2/16 | 1        | First Release    |

| 2008/9/4  | 2        | Contents Revised |

| 2009/7/16 | 3        | Contents Revised |

# **Table of Contents**

| <b>Considerations for Using Both Mask ROM</b>                                                                                                              | and Flash Products      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                            |                         |

| ТМР89СН42                                                                                                                                                  |                         |

| 11111 07 011 42                                                                                                                                            |                         |

| 1.1 Features                                                                                                                                               |                         |

|                                                                                                                                                            |                         |

| 1.2 Pin Assignment                                                                                                                                         |                         |

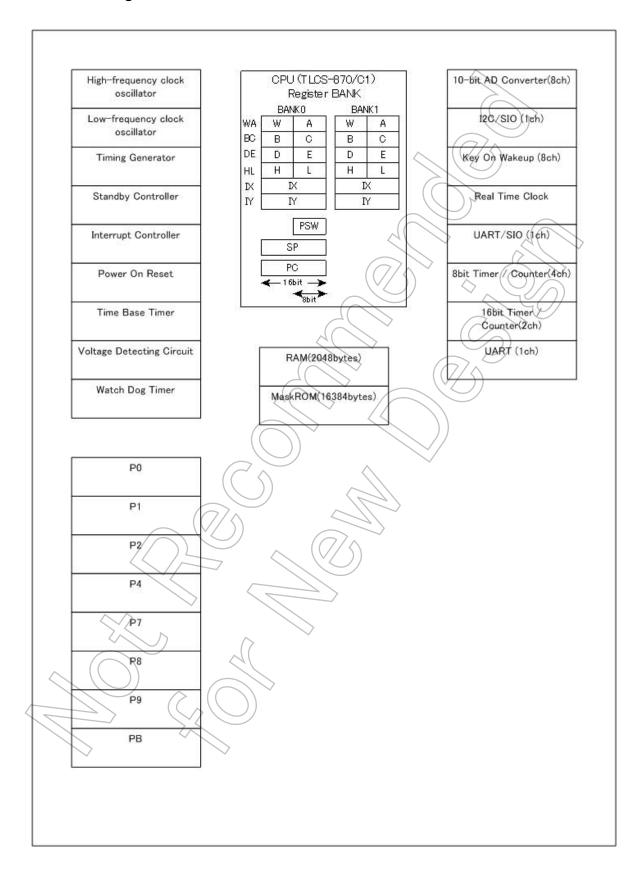

| 1.3 Block Diagram                                                                                                                                          |                         |

| 1.4 Pin Names and Functions                                                                                                                                |                         |

|                                                                                                                                                            |                         |

|                                                                                                                                                            |                         |

| 2. CPU Core                                                                                                                                                |                         |

| a: Cro core                                                                                                                                                |                         |

| 2.1 Configuration                                                                                                                                          | $\rightarrow$ $(\vee/)$ |

| 2.2 Memory space                                                                                                                                           |                         |

|                                                                                                                                                            |                         |

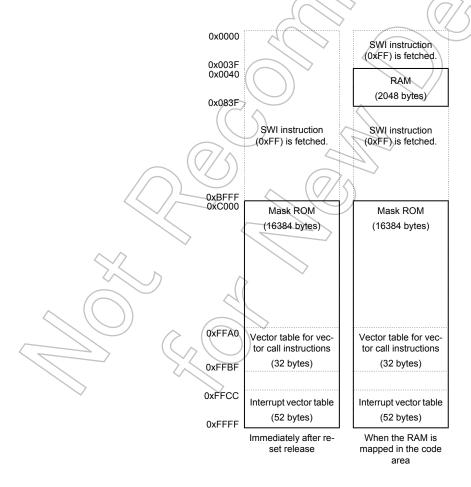

| 2.2.1 Code area                                                                                                                                            | ,9                      |

| 2.2.1.2 MaskROM                                                                                                                                            |                         |

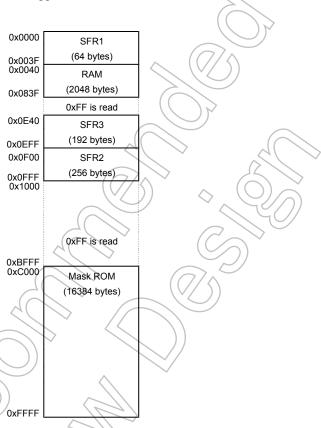

| 2.2.2 Data area                                                                                                                                            | 12                      |

| 2.2.2.1 SFR<br>2.2.2.2 RAM                                                                                                                                 |                         |

| 2.2.2.3 MaskROM                                                                                                                                            |                         |

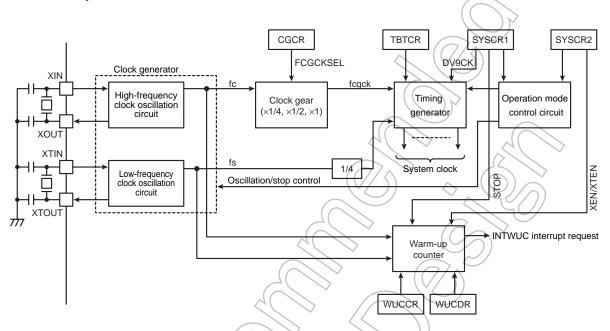

| 2.3 System clock controller                                                                                                                                | 1                       |

|                                                                                                                                                            |                         |

| 2.3.2 Control                                                                                                                                              | 14                      |

| 2.3.3 Functions                                                                                                                                            | (/\)                    |

| 2.3.3.1 Clock generator 2.3.3.2 Clock gear                                                                                                                 | <b>v</b> ())            |

| 2.3.3.3 Timing generator                                                                                                                                   |                         |

|                                                                                                                                                            |                         |

| <ul> <li>2.3.4.1 Warm-up counter operation when the oscillation is enal</li> <li>2.3.4.2 Warm-up counter operation when the oscillation is enal</li> </ul> | oled by the hardware    |

|                                                                                                                                                            | 21                      |

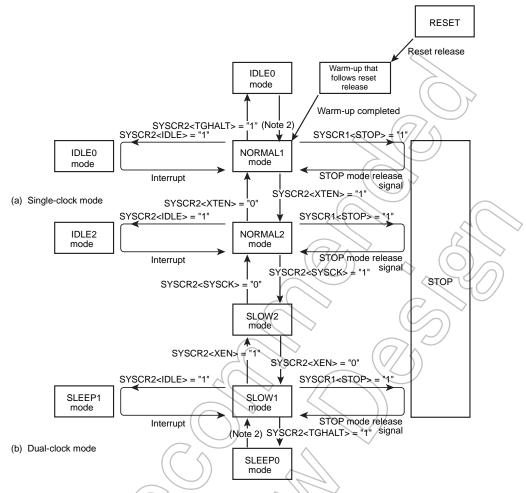

| 2.3.5.1 Single-clock mode                                                                                                                                  |                         |

| 2.3.5.2 Dual-clock mode<br>2.3.5.3 STOP mode                                                                                                               |                         |

| 2.3.5.4 Transition of operation modes                                                                                                                      |                         |

|                                                                                                                                                            |                         |

| 2.3.6.1 STOP mode 2.3.6.2 IDLE1/2 and SLEEP1 modes                                                                                                         |                         |

| 2.3.6.2 IDLE1/2 and SLEEP1 modes 2.3.6.3 IDLE0 and SLEEP0 modes                                                                                            |                         |

| 2.3.6.4 SLOW mode                                                                                                                                          |                         |

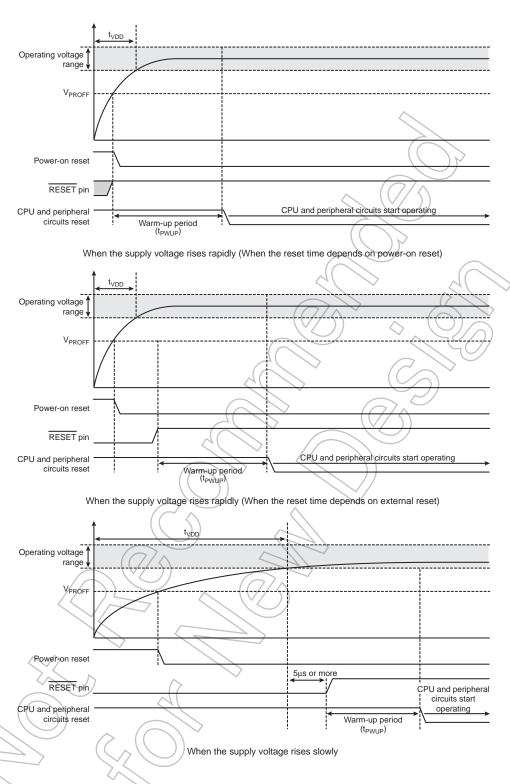

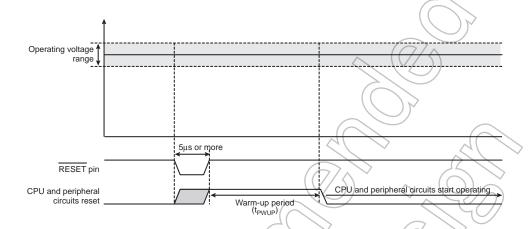

| 2.4 Reset Control Circuit                                                                                                                                  | 3                       |

| •                                                                                                                                                          |                         |

|                                                                                                                                                            | 37                      |

|                                                                                                                                                            |                         |

| 2.4.4 Reset Signal Generating Factors                                                                                                                      | 41                      |

| 2.4.4.2 External reset input (RESET pin input)                                                                                                             |                         |

| 2.4.4.3 Voltage detection reset 2.4.4.4 Watchdog timer reset                                                                                               |                         |

| 2.4.4.4 watchdog timer reset<br>2.4.4.5 System clock reset                                                                                                 |                         |

| 2.4.4.6 Trimming data reset                                                                                                                                |                         |

| 2.4.4.7 Internal factor reset detection status register 2.4.4.8 How to use the external reset input pin as a port                                          |                         |

| 2.7.7.0 How to use the external reset input pin as a port                                                                                                  |                         |

|    | 2.5 Revision History                                                                                                                                                             | 45 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |                                                                                                                                                                                  |    |

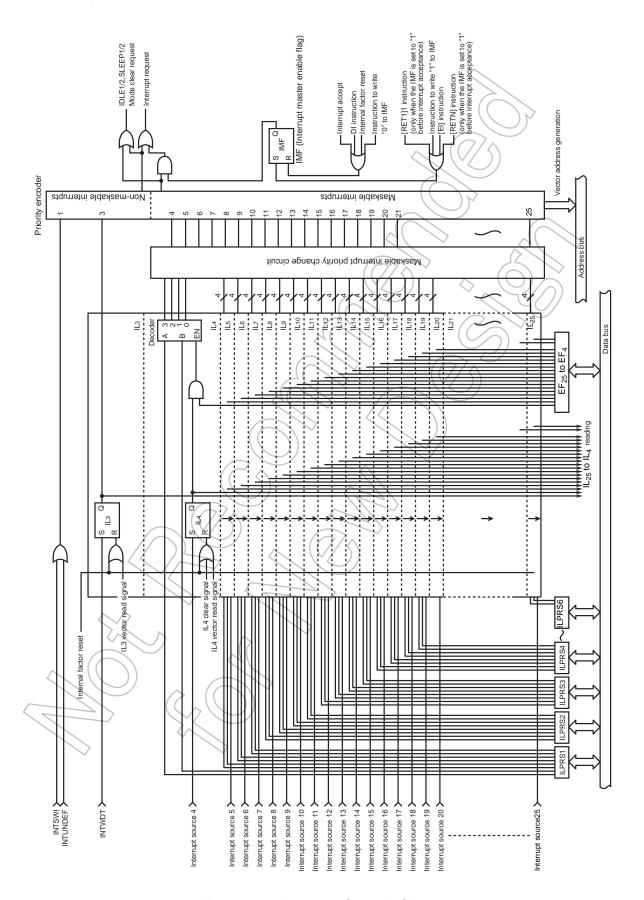

| 3. | Interrupt Control Circuit                                                                                                                                                        |    |

| ٠. | Invertige Control Circuit                                                                                                                                                        |    |

|    | 3.1 Configuration                                                                                                                                                                | 48 |

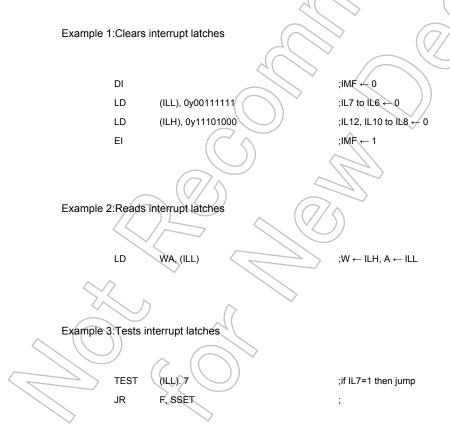

|    | 3.2 Interrupt Latches (IL25 to IL3)                                                                                                                                              | 49 |

|    | 3.3 Interrupt Enable Register (EIR)  3.3.1 Interrupt master enable flag (IMF)                                                                                                    | 50 |

|    | 3.3.1 Interrupt master enable flag (IMF)                                                                                                                                         | 50 |

|    | 5.5.2 Individual interrupt chable riags (El 25 to El 4)                                                                                                                          |    |

|    | 3.4 Maskable Interrupt Priority Change Function                                                                                                                                  | 53 |

|    | 3.5 Interrupt Sequence. 3.5.1 Initial Setting.                                                                                                                                   | 55 |

|    | 3.5.1 Initial Setting                                                                                                                                                            | 55 |

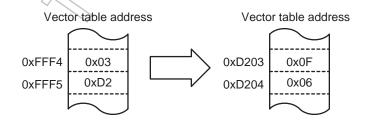

|    | 3.5.2 Interrupt acceptance processing                                                                                                                                            | 56 |

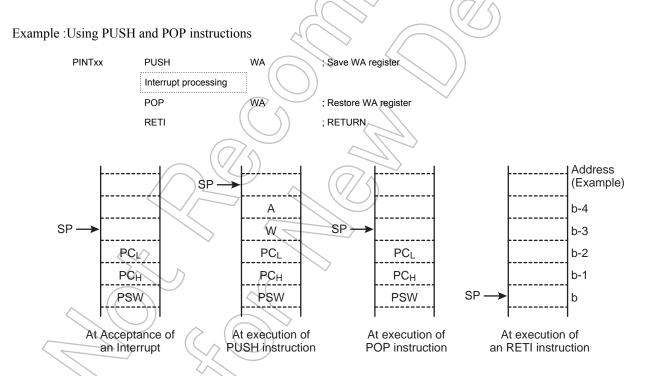

|    | 3.5.3.1 Using PUSH and POP instructions                                                                                                                                          |    |

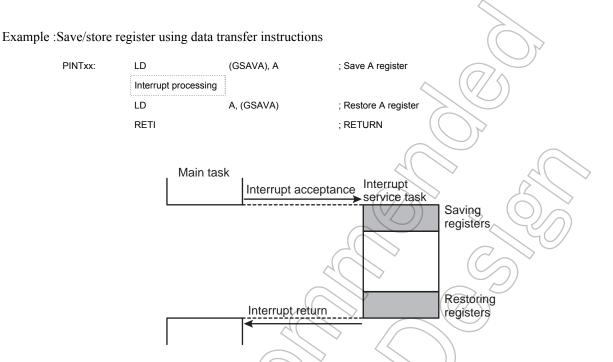

|    | 3.5.3.2 Using data transfer instructions 3.5.3.3 Using a register bank to save/restore general-purpose registers                                                                 |    |

|    | 3.5.4 Interrupt return                                                                                                                                                           | 58 |

|    | 3.6 Software Interrupt (INTSW).  3.6.1 Address error detection.                                                                                                                  | 59 |

|    | 3.6.1 Address error detection.                                                                                                                                                   | 59 |

|    | 3.6.2 Debugging.                                                                                                                                                                 | 59 |

|    | 3.7 Undefined Instruction Interrupt (INTUNDEF)                                                                                                                                   | 59 |

|    | 3.8 Revision History                                                                                                                                                             | 60 |

|    |                                                                                                                                                                                  |    |

|    | 4.1 Configuration 4.2 Control                                                                                                                                                    | 61 |

|    | 4.3 Function                                                                                                                                                                     | 65 |

|    | 4.3.1 Low power consumption function                                                                                                                                             | 66 |

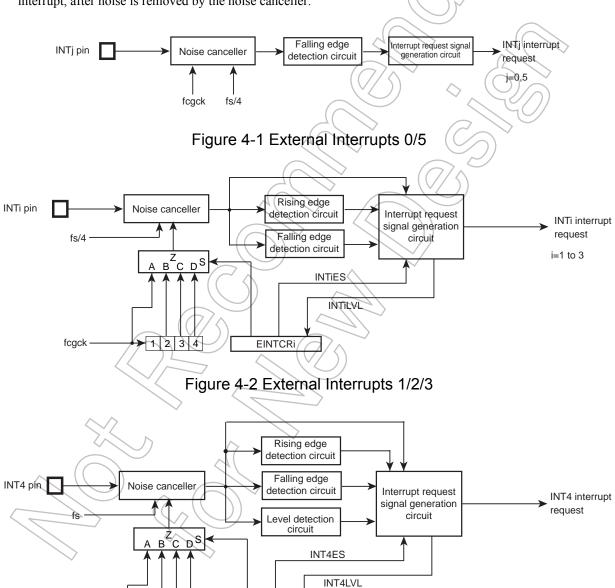

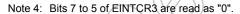

|    | 4.3.2 External interrupt 0. 4.3.3 External interrupts 1/2/3                                                                                                                      | 66 |

|    | 4.3.3.1 Interrupt request signal generating condition detection function                                                                                                         | 07 |

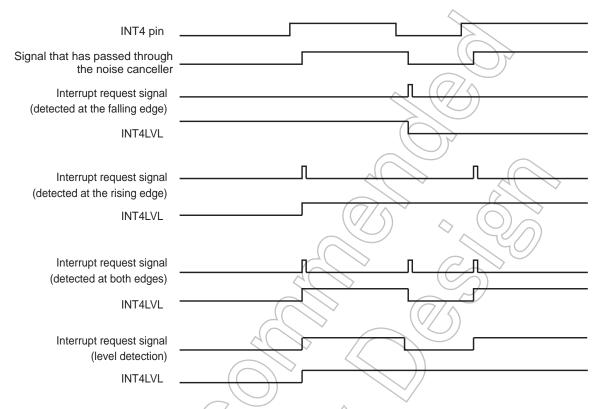

|    | <ul> <li>4.3.3.2 A noise canceller pass signal monitoring function when interrupt request signals are generated</li> <li>4.3.3.3 Noise cancel time selection function</li> </ul> |    |

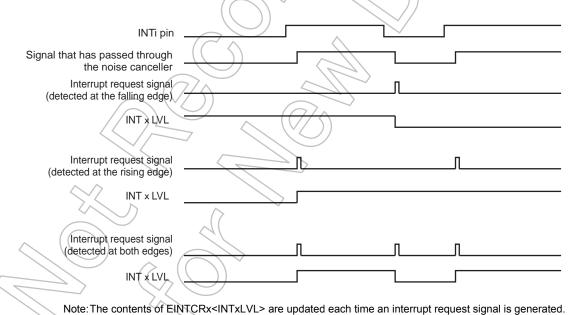

|    | 4.3.3.3 Noise cancel time selection function 4.3.4 External interrupt 4                                                                                                          | 68 |

|    | 4.3.4.1 Interrupt request signal generating condition detection function                                                                                                         |    |

|    | <ul><li>4.3.4.2 A noise canceller pass signal monitoring function when interrupt request signals are generated</li><li>4.3.4.3 Noise cancel time selection function</li></ul>    |    |

|    | 4.3.5 External interrupt 5                                                                                                                                                       | 70 |

|    |                                                                                                                                                                                  |    |

|    |                                                                                                                                                                                  |    |

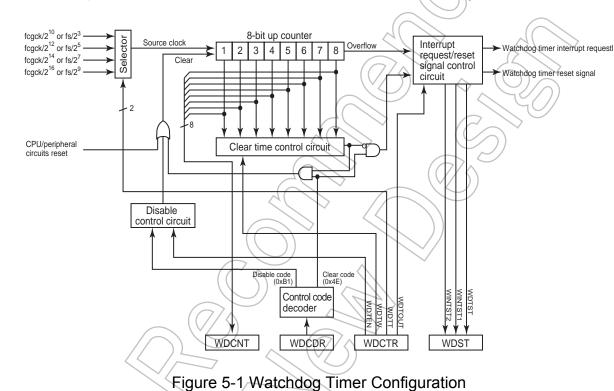

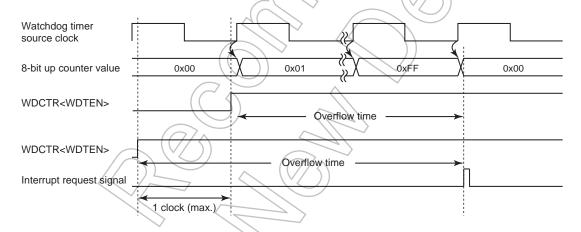

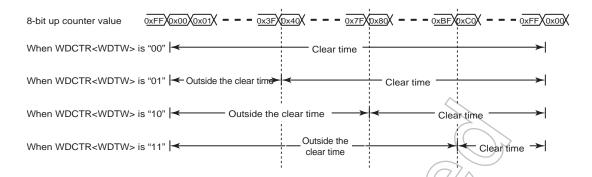

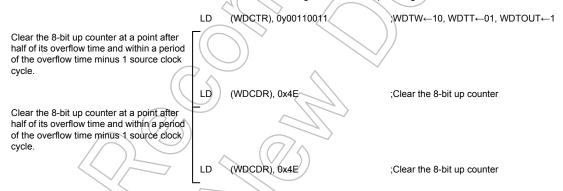

| 5. | Watchdog Timer (WDT)                                                                                                                                                             |    |

|    |                                                                                                                                                                                  |    |

|    | 5.1 Configuration                                                                                                                                                                |    |

|    | 5.2 Control                                                                                                                                                                      | 72 |

|    | 5.3 Functions.                                                                                                                                                                   |    |

|    | 5.3.1 Setting of enabling/disabling the watchdog timer operation                                                                                                                 |    |

|    | 5.3.2 Setting the clear time of the 8-bit up counter                                                                                                                             |    |

|    | 5.3.4 Setting an overflow detection signal of the 8-bit up counter                                                                                                               | 75 |

|    | 5.3.5 Writing the watchdog timer control codes                                                                                                                                   | 76 |

|    | 5.3.6 Reading the 8-bit up counter.                                                                                                                                              |    |

|    | 5.3.7 Reading the watchdog timer status                                                                                                                                          | /6 |

| 6.                 | Pow                      | er-on Reset Circuit                                                                                                                                                                                             |                                                                                                                          |                |

|--------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------|

|                    | 6.1                      | C                                                                                                                                                                                                               |                                                                                                                          | 79             |

|                    | 6.2                      | Function                                                                                                                                                                                                        | ~ (V)                                                                                                                    | 79             |

| 7.                 | Volt                     | age Detection Circuit                                                                                                                                                                                           |                                                                                                                          |                |

|                    | 7.1                      | Configuration                                                                                                                                                                                                   | <u></u>                                                                                                                  | 81             |

|                    | 7.2                      | Control                                                                                                                                                                                                         |                                                                                                                          | 82             |

|                    | 7.3                      | Function                                                                                                                                                                                                        |                                                                                                                          | > 83           |

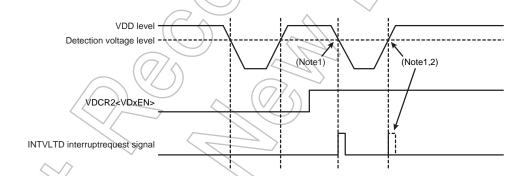

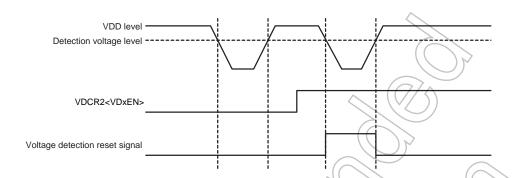

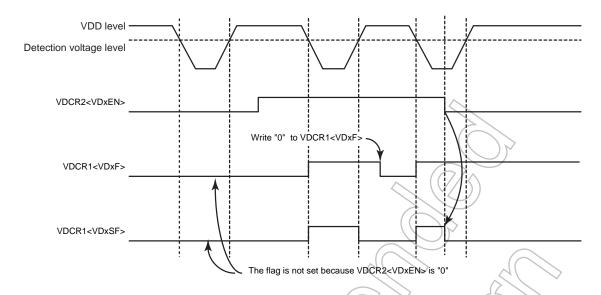

|                    | 7.3<br>7.3<br>7.3<br>7.3 | <ul> <li>1 Enabling/disabling the voltage detection ope</li> <li>2 Selecting the voltage detection ope</li> <li>3 Selecting the detection voltage leve</li> <li>4 Voltage detection flag and voltage</li> </ul> | ection operation peration mode el detection status flag                                                                  | 83<br>83<br>84 |

|                    | 7.4                      | Register Settings                                                                                                                                                                                               |                                                                                                                          | 86             |

|                    | 7.4<br>7.4<br><b>7.5</b> | Setting procedure when the operation 2 Setting procedure when the operation 2.                                                                                                                                  | ion mode is set to generate INTVLTD interrupt request signalsion mode is set to generate voltage detection reset signals | 86<br>86       |

|                    |                          |                                                                                                                                                                                                                 |                                                                                                                          |                |

| 8.                 | I/O                      | Ports                                                                                                                                                                                                           |                                                                                                                          |                |

|                    | 8.1                      | I/O Port Control Registers                                                                                                                                                                                      |                                                                                                                          | 91             |

|                    | 8.2                      | List of I/O Port Settings                                                                                                                                                                                       |                                                                                                                          |                |

|                    |                          | List of I/O Fort Settings                                                                                                                                                                                       |                                                                                                                          | 92             |

|                    | 8.3                      | I/O Port Registers                                                                                                                                                                                              |                                                                                                                          | 95             |

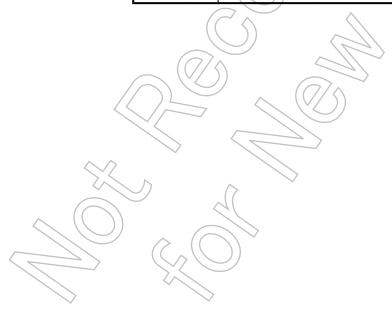

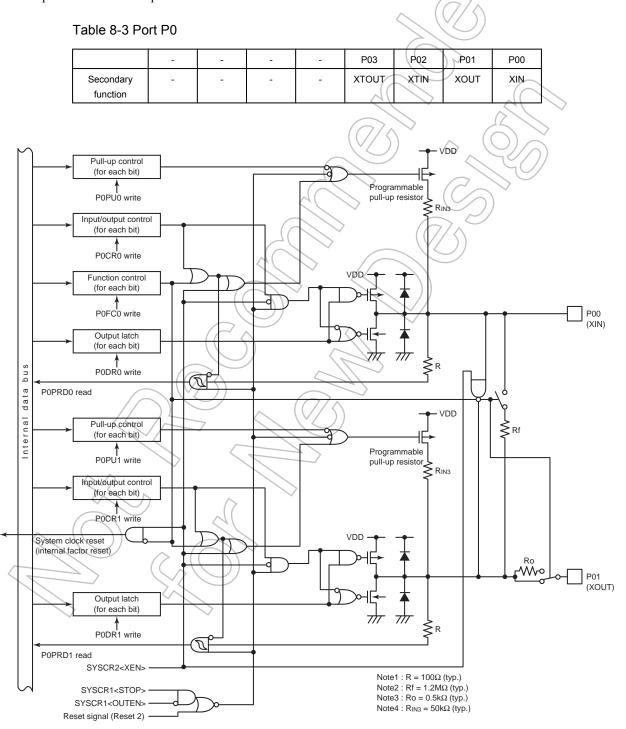

|                    | 8.3<br>8.3               | .1 Port P0 (P03 to P00)                                                                                                                                                                                         |                                                                                                                          | 95             |

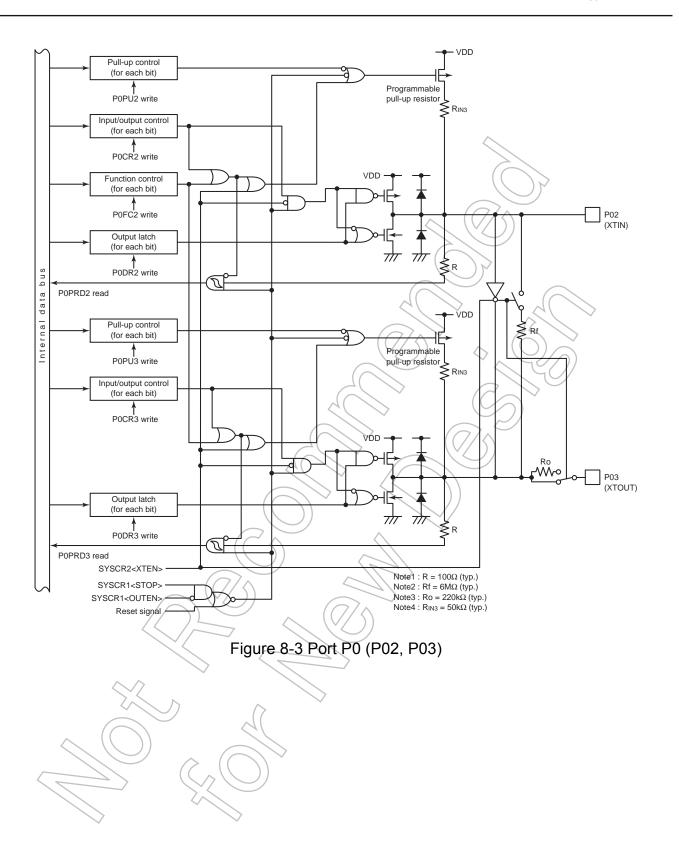

|                    | 8.3                      | 3 Port P2 (P27 to P20)                                                                                                                                                                                          |                                                                                                                          | 103            |

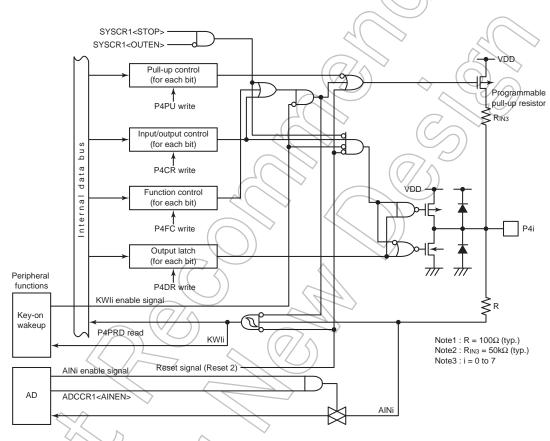

|                    | 8.3                      | .4 Port P4 (P47 to P40)                                                                                                                                                                                         |                                                                                                                          | 107            |

|                    | 8.3                      | .5 Port P7 (P77 to P70)                                                                                                                                                                                         | (0/4                                                                                                                     | 110            |

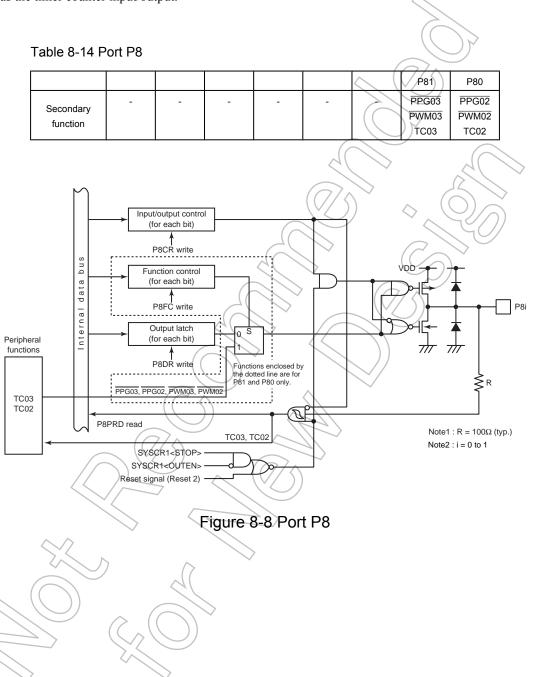

|                    | 8.3                      | .6 Port P8 (P81 to P80)                                                                                                                                                                                         | (\(\vert_{\vert_{\omega}}\))                                                                                             | 112            |

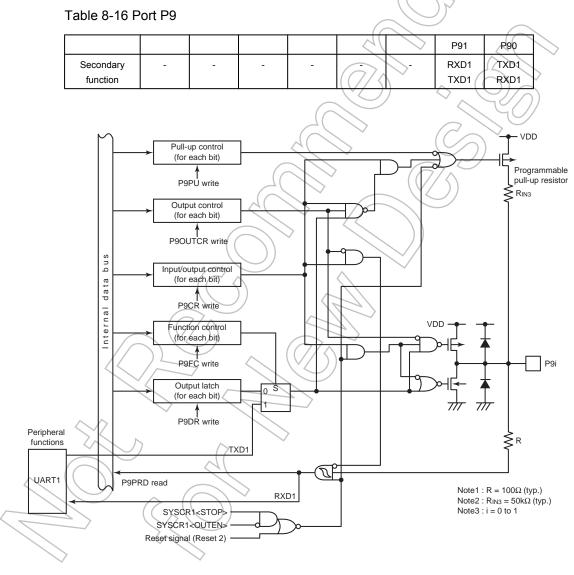

|                    | 8.3                      | ./ Port P9 (P91 to P90)                                                                                                                                                                                         |                                                                                                                          | 115            |

|                    | 8.3                      |                                                                                                                                                                                                                 |                                                                                                                          |                |

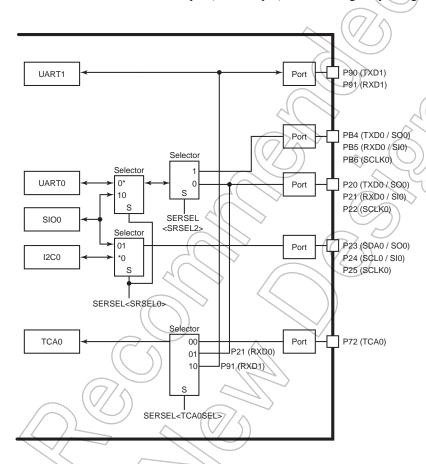

|                    | 8.4                      |                                                                                                                                                                                                                 | inction                                                                                                                  |                |

|                    | 8.5                      | Revision History                                                                                                                                                                                                |                                                                                                                          | 124            |

|                    |                          | 7/\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                                                                                                                         |                                                                                                                          |                |

| <del></del><br>9.  | Spec                     | eial Function Registers                                                                                                                                                                                         |                                                                                                                          |                |

|                    |                          |                                                                                                                                                                                                                 |                                                                                                                          | 105            |

|                    | 9.1                      | SFR1 (0x0000 to 0x003F)                                                                                                                                                                                         | ··)·)                                                                                                                    | 125            |

|                    | 9.2                      | SFR2 (0x0F00 to 0x0FFF)                                                                                                                                                                                         | <u></u>                                                                                                                  | 126            |

|                    | 9.3                      | SFR3 (0x0E40 to 0x0EFF)                                                                                                                                                                                         |                                                                                                                          | 128            |

| 10.                | Lo                       | w Power Consumption Fu                                                                                                                                                                                          | unction for Peripherals                                                                                                  |                |

|                    | 10.1                     | Control                                                                                                                                                                                                         |                                                                                                                          | 132            |

| <del></del><br>11. | Div                      | vider Output (DVO)                                                                                                                                                                                              |                                                                                                                          |                |

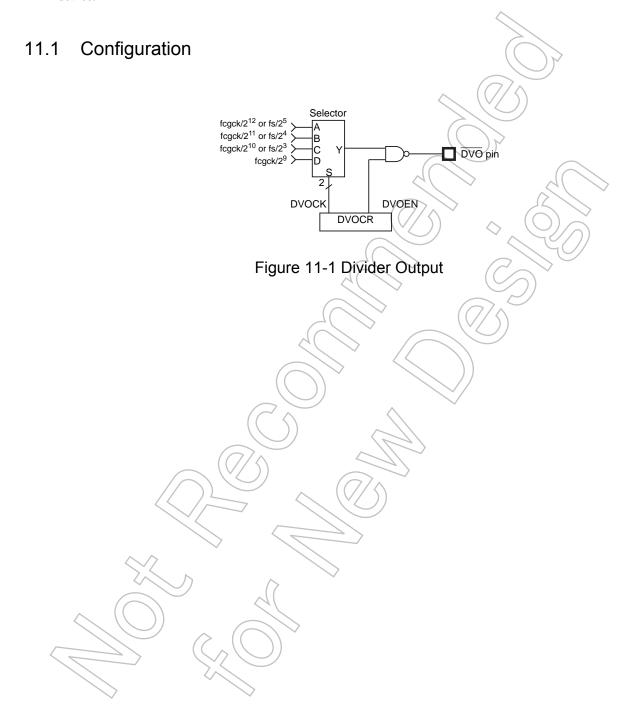

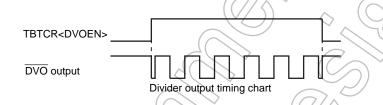

| 11.1 Configuration                                              |                  | 135  |

|-----------------------------------------------------------------|------------------|------|

| 9                                                               |                  |      |

| 11.3 Function                                                   |                  | 137  |

| 11.4 Revision History                                           |                  | 138  |

|                                                                 |                  |      |

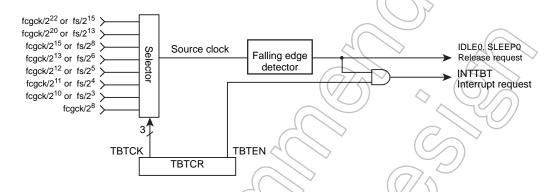

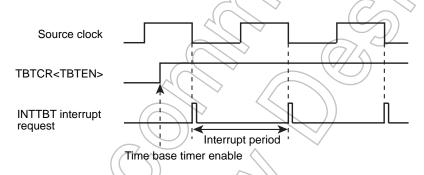

| 2. Time Base Timer (TBT)                                        | ^ (776)          |      |

|                                                                 |                  |      |

|                                                                 |                  |      |

|                                                                 |                  |      |

|                                                                 |                  | 139  |

| 12.2 Revision History                                           |                  | 142  |

|                                                                 |                  | ·    |

|                                                                 |                  |      |

| 13. 16-bit Timer Counter (TCA)                                  |                  |      |

| 13.1 Configuration                                              |                  | 144  |

| 13.2 Control                                                    |                  | 145  |

|                                                                 |                  |      |

| 13.5 Low Fower Consumption Function.                            |                  | 1.51 |

| 13.4 Timer Function                                             |                  |      |

| 13.4.1.1 Setting                                                |                  | 131  |

| 13.4.1.2 Operation                                              | `                |      |

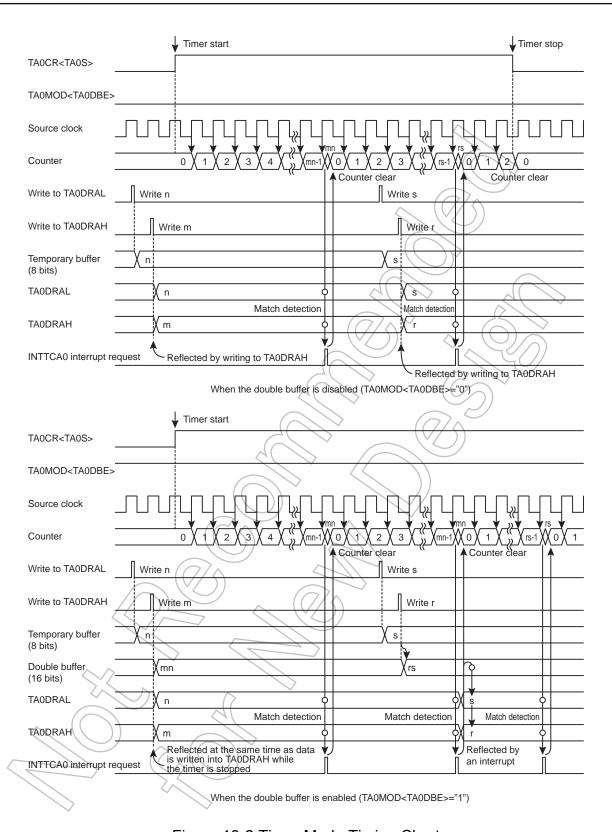

| 13.4.1.3 Auto capture 13.4.1.4 Register buffer configuration    | $\rightarrow$ )) |      |

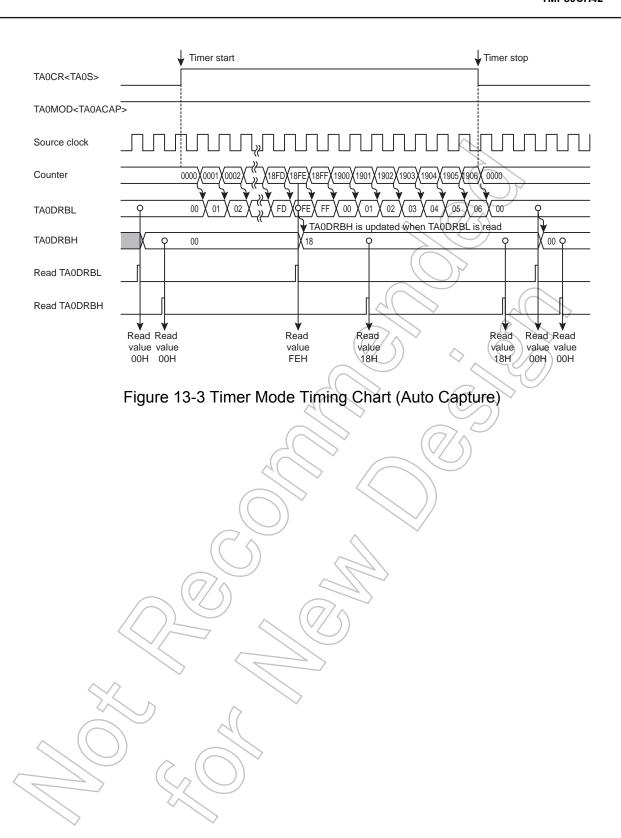

| 13.4.2 External trigger timer mode                              |                  | 155  |

| 13.4.2.1 Setting<br>13.4.2.2 Operation                          | ^                |      |

| 13.4.2.3 Auto capture                                           |                  |      |

| 13.4.2.4 Register buffer configuration                          |                  | 1.57 |

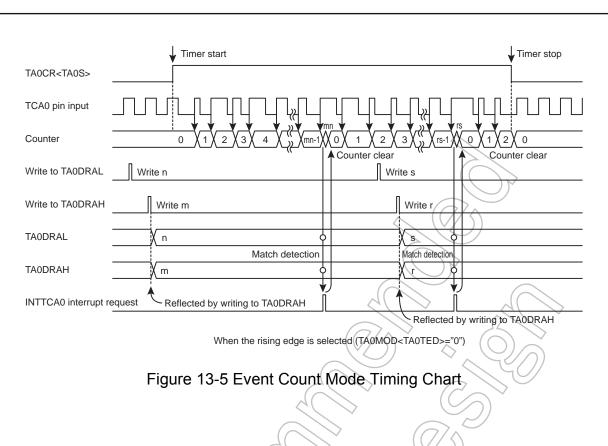

| 13.4.3 Event counter mode                                       |                  | 15/  |

| 13.4.3.2 Operation                                              |                  |      |

| 13.4.3.3 Auto capture<br>13.4.3.4 Register buffer configuration | $(7/\land$       |      |

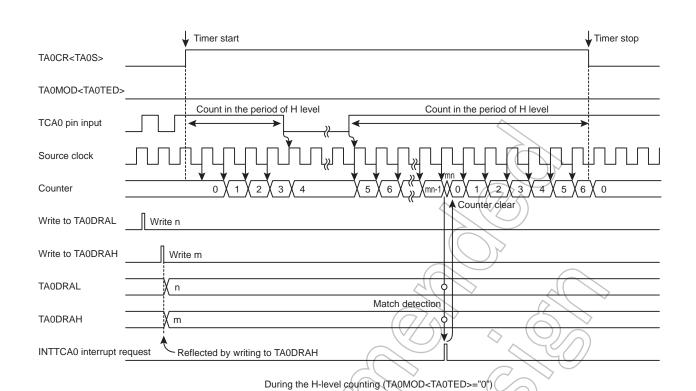

| 13.4.4 Window mode                                              | (V)              | 159  |

| 13.4.4.1 Setting                                                |                  |      |

| 13.4.4.2 Operation<br>13.4.4.3 Auto capture                     |                  |      |

| 13.4.4.4 Register buffer configuration                          |                  | 1.61 |

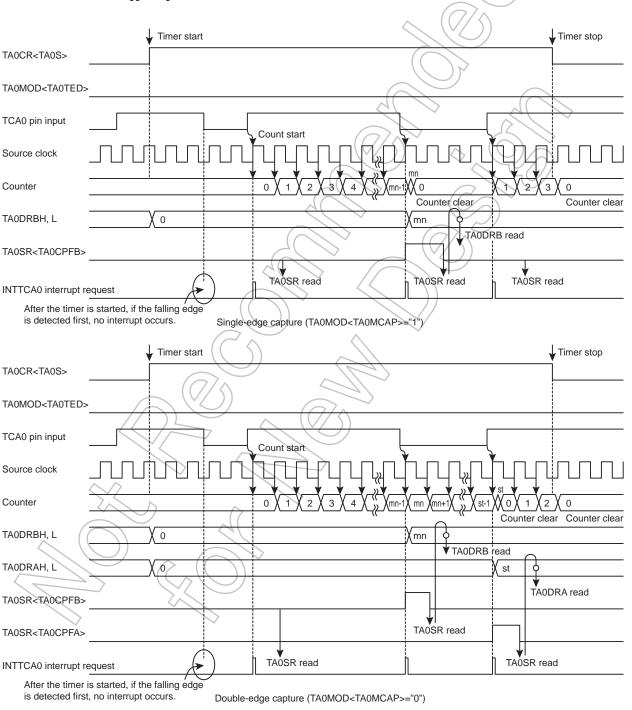

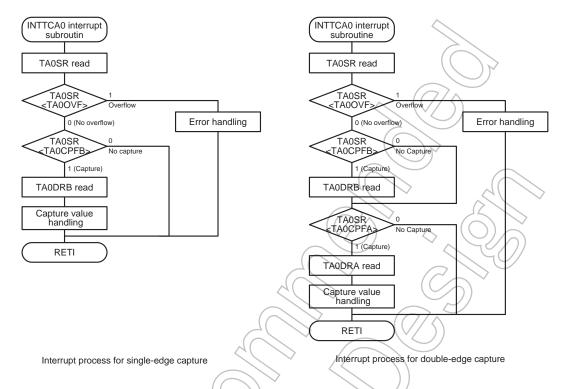

| 13.4.5 Pulse width measurement mode                             | <u>&gt;</u>      | 161  |

| 13.4.5.2 Operation                                              |                  |      |

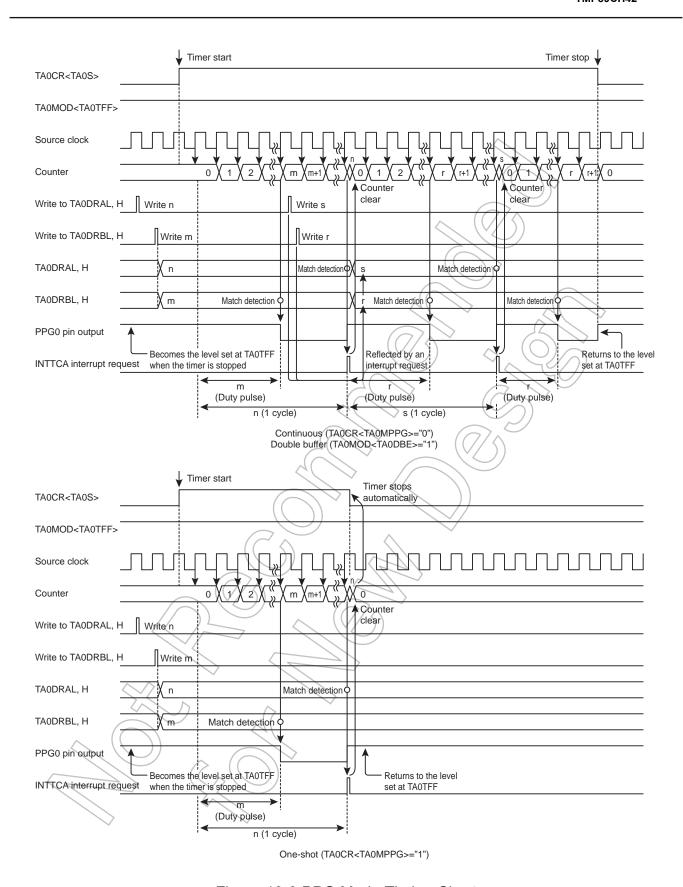

| 13.4.6. Programmable pulse generate (PPG) mode                  |                  | 164  |

| 13.4.6.1 Setting                                                |                  | 104  |

| 13.4.6.2 Operation                                              |                  |      |

| 13.4.6.3 Register buffer configuration  13.5 Noise Canceller    |                  | 167  |

|                                                                 |                  |      |

|                                                                 |                  | 168  |

| 10.00 Ite vision History                                        |                  |      |

|                                                                 |                  |      |

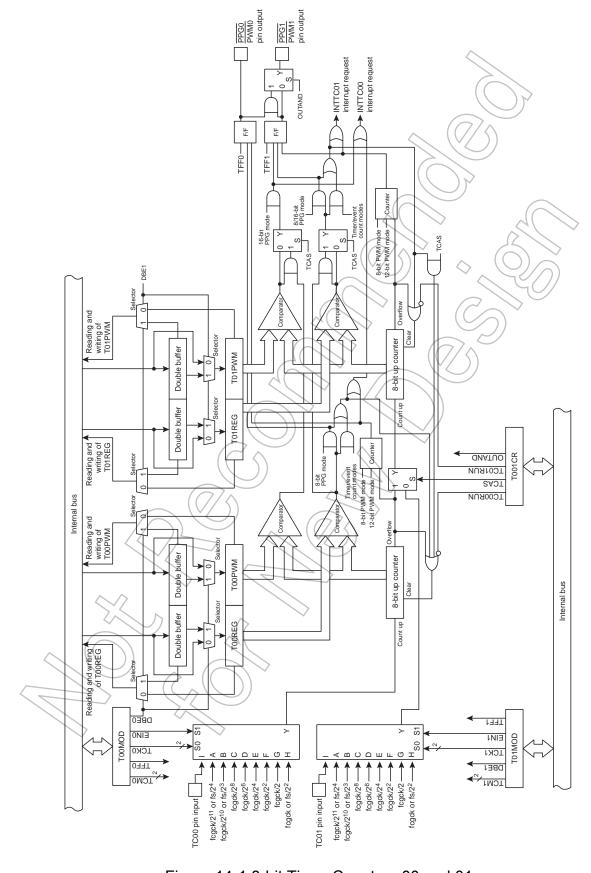

| 4. 8-bit Timer Counter (TC0)                                    |                  |      |

| ,                                                               |                  |      |

| 8                                                               |                  |      |

|                                                                 |                  |      |

|                                                                 |                  |      |

|                                                                 |                  | 173  |

| 14.2.4 Operation modes and usable source clocks                               |      |

|-------------------------------------------------------------------------------|------|

| 14.3 Low Power Consumption Function                                           |      |

|                                                                               |      |

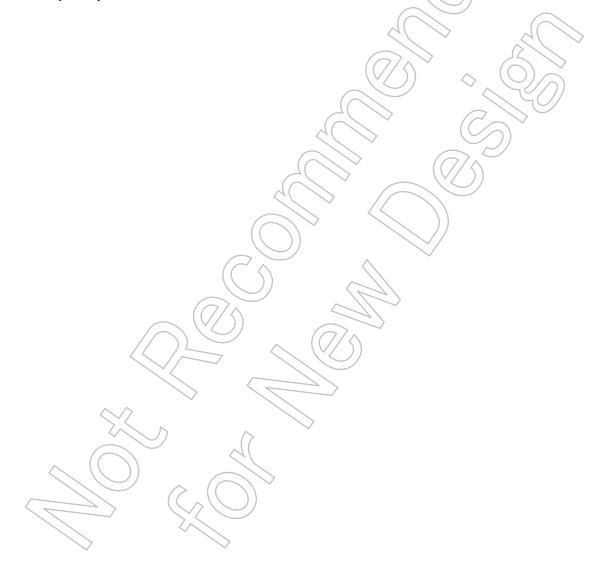

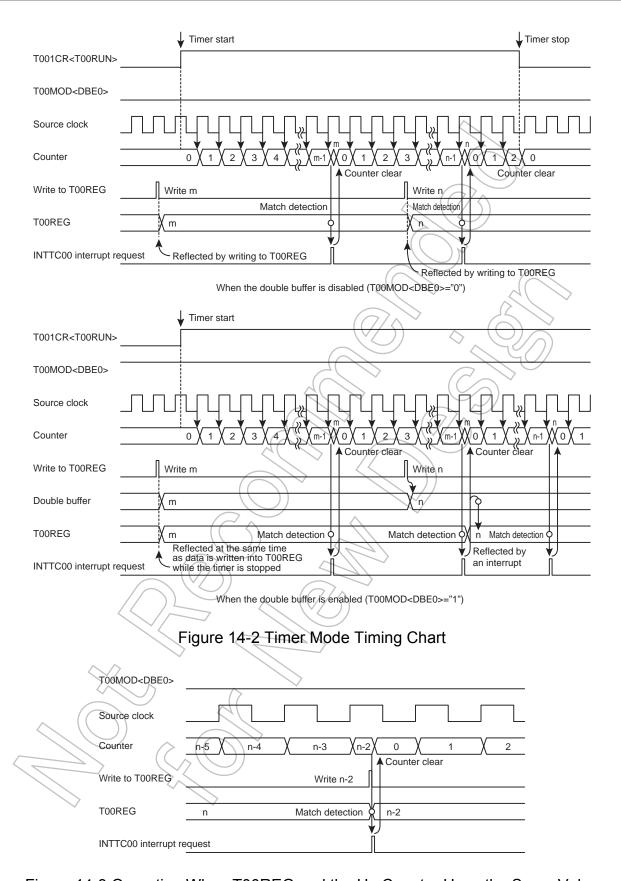

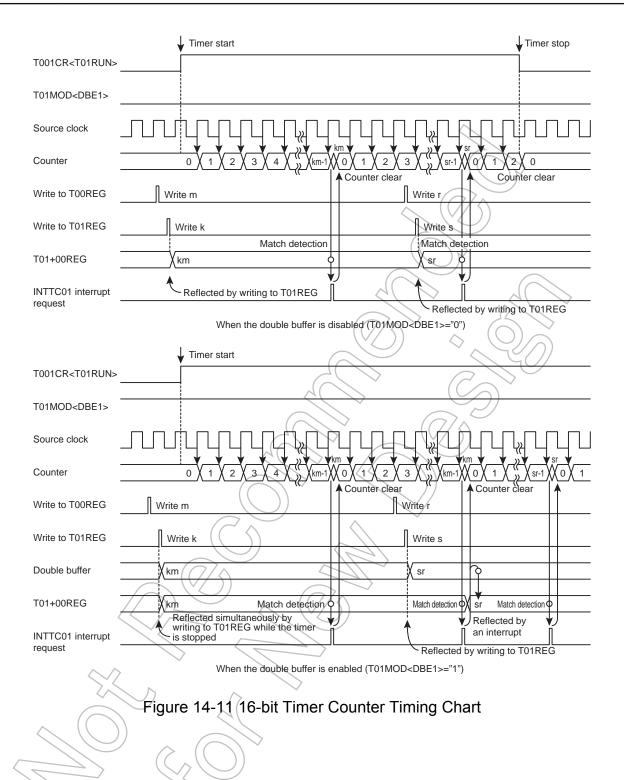

| 14.4.1 8-bit timer mode                                                       | .1/9 |

| 14.4.1.2 Operation                                                            |      |

| 14.4.1.3 Double buffer                                                        |      |

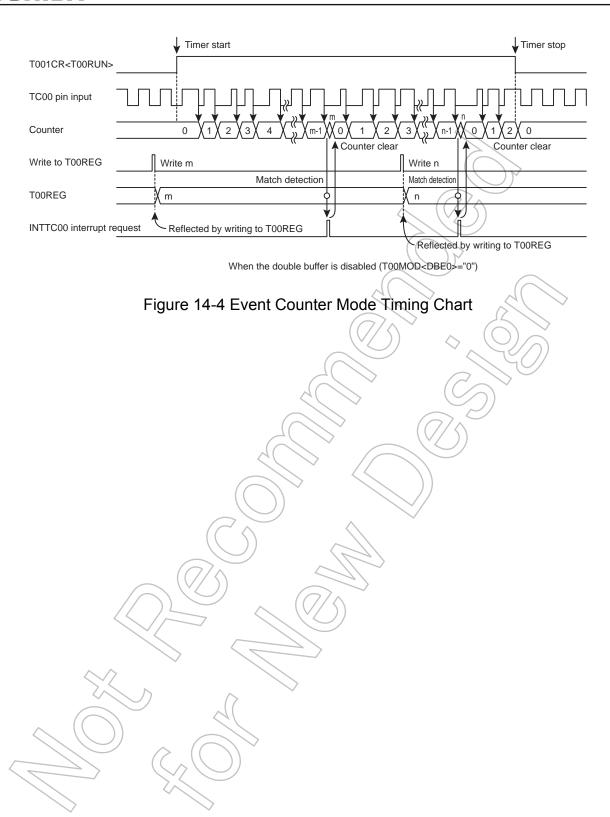

| 14.4.2 8-bit event counter mode                                               | .182 |

| 14.4.2.1 Setting                                                              |      |

| 14.4.2.2 Operation                                                            |      |

| 14.4.2.3 Double buffer                                                        |      |

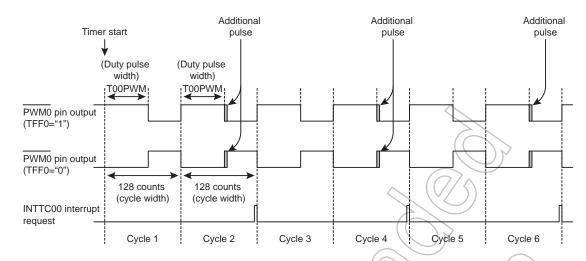

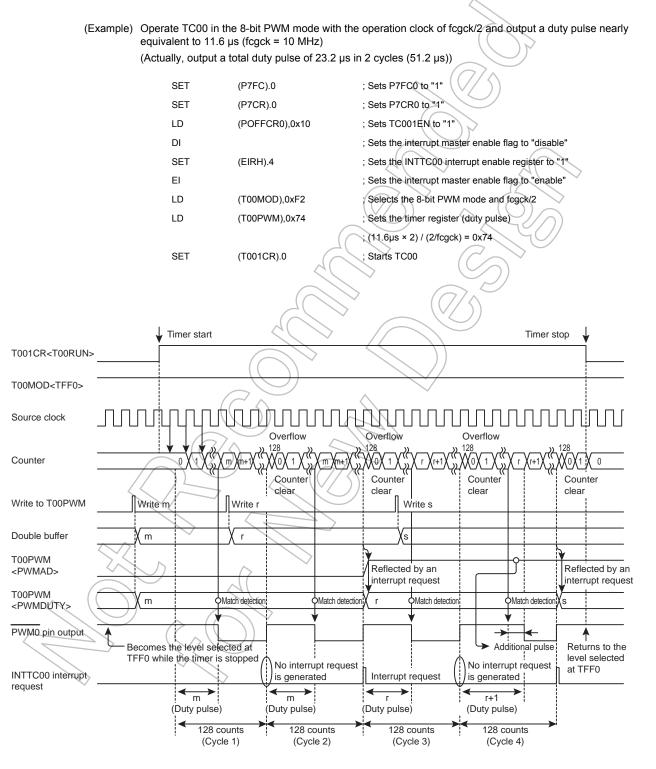

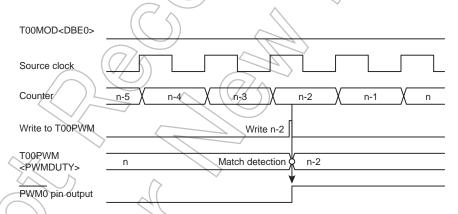

| 14.4.3 8-bit pulse width modulation (PWM) output mode                         | .184 |

| 14.4.3.1 Setting                                                              |      |

| 14.4.3.3 Operations 14.4.3.3 Double buffer                                    |      |

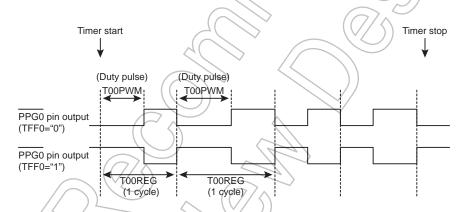

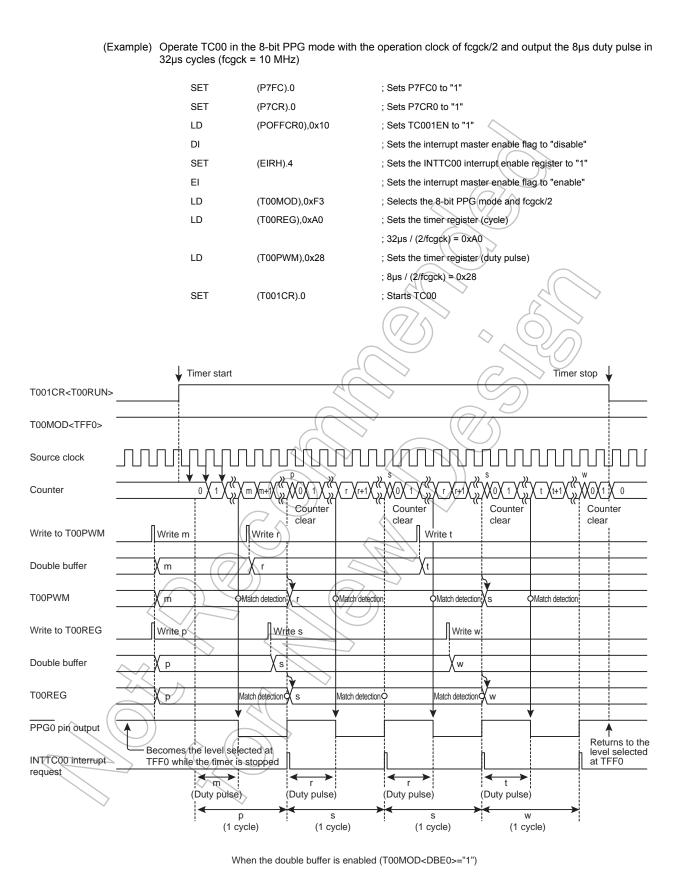

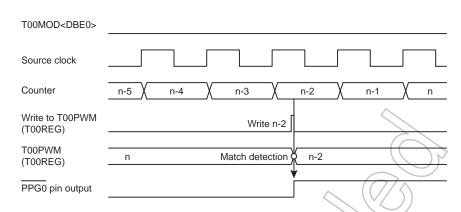

|                                                                               | .189 |

| 14.4.4.1 Setting                                                              | ,    |

| 14.4.4.2 Operation                                                            |      |

| 14.4.4.3 Double buffer                                                        |      |

| 14.4.5 16-bit timer mode                                                      | .193 |

| 14.4.5.1 Setting                                                              |      |

| 14.4.5.2 Operations                                                           |      |

| 14.4.5.3 Double buffer                                                        | 107  |

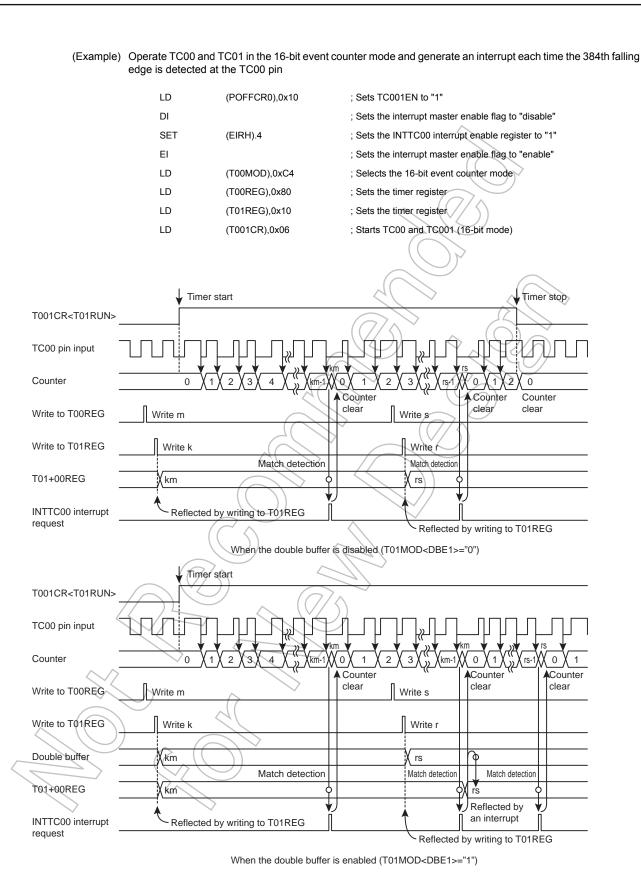

| 14.4.6 1 6-bit event counter mode                                             | .197 |

| 14.4.6.1 Setting 14.4.6.2 Operations                                          |      |

| 14.4.6.3 Double buffer                                                        |      |

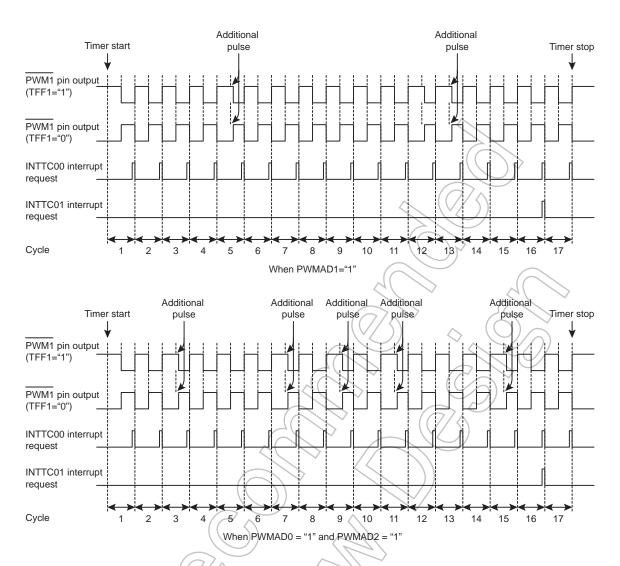

| 14.4.7 12-bit pulse width modulation (PWM) output mode                        | .199 |

| 14.4.7.1 Setting                                                              |      |

| 14.4.7.2 Operations                                                           |      |

| 14.4.7.3 Double buffer                                                        |      |

| 14.4.8 16-bit programmable pulse generate (PPG) output mode                   | .205 |

| 14.4.8.1 Setting                                                              |      |

| 14.4.8.2 Operations 14.4.8.3 Double buffer                                    |      |

|                                                                               | ,    |

| 14.5 Revision History                                                         | 2    |

|                                                                               |      |

|                                                                               |      |

| Real Time Clock (RTC)                                                         |      |

|                                                                               |      |

| 15.1 Configuration                                                            | 2    |

| 15.2 Control                                                                  | 2    |

|                                                                               |      |

| 15.3 Function                                                                 |      |

| 15.3.1 Low Power Consumption Function                                         |      |

| 15.3.2 Enabling/disabling the real time clock operation                       | .212 |

| 15.3.3 Selecting the interrupt generation interval                            |      |

| 15.4 Real Time Clock Operation                                                |      |

| 15.4.1 Enabling the real time clock operation                                 | .213 |

| 15.4.2 Disabling the real time clock operation                                |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Asynchronous Serial Interface (UART)                                          |      |

|                                                                               |      |

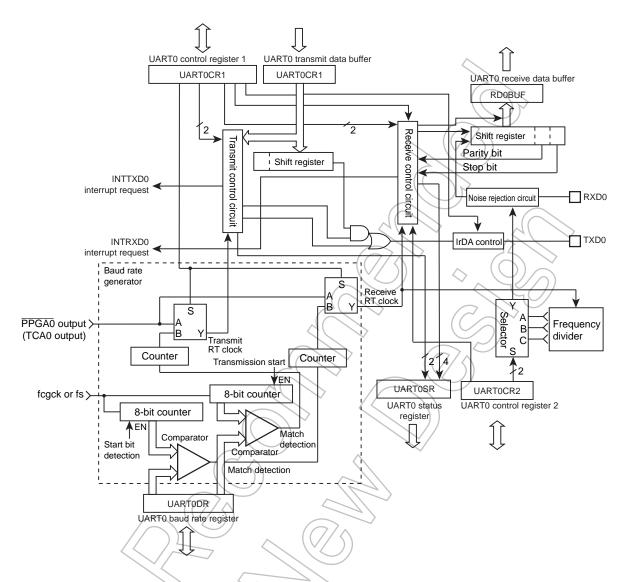

| 16.1 Configuration                                                            | 2    |

| 16.2 Control                                                                  |      |

|                                                                               |      |

| 16.3 Low Power Consumption Function                                           | 2    |

| 16.4 Protection to Prevent UART0CR1 and UART0CR2 Registers from Being Changed |      |

|                                                                               |      |

| 16.5 Activation of STOP, IDLE0 or SLEEP0 Mode                                 | 2    |

| 16.5.1 Transition of register status                                          |      |

| 16.5.2 Transition of TXD pin status                                           | .223 |

| 16.6 Transfer Data Format.                                                    | 2    |

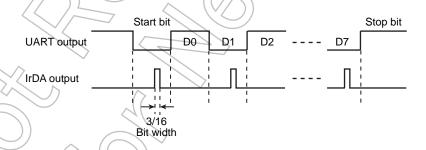

| 16.7 Infrared Data Format Transfer Mode                                       |      |

|                                                                               |      |

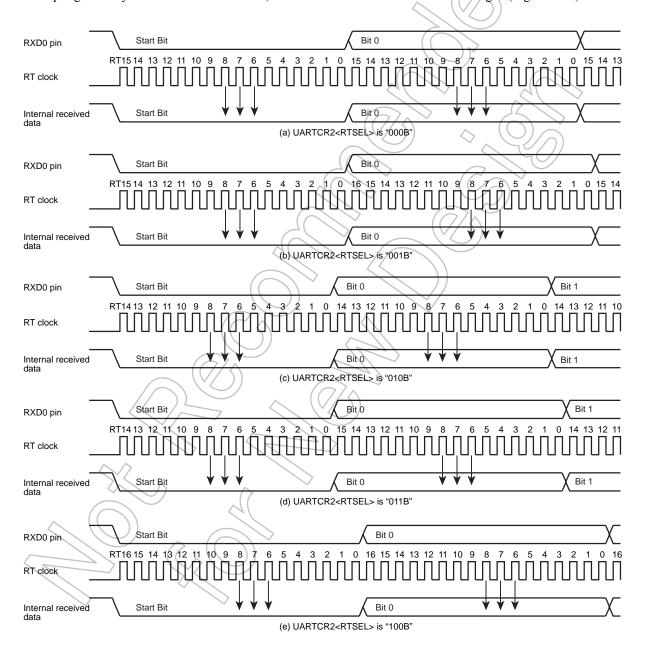

| 16.8 Transfer Baud Rate                                                                                                                             |                                       | 225  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|

|                                                                                                                                                     |                                       | 226  |

| 16.8.1.1 Bit width adjustment using UART0CR2 <rts 16.8.1.2="" calculation="" of="" set="" th="" uart0cr2<rts<="" values=""><th></th><th></th></rts> |                                       |      |

|                                                                                                                                                     | SEL and OAKTODK                       | 229  |

|                                                                                                                                                     |                                       |      |

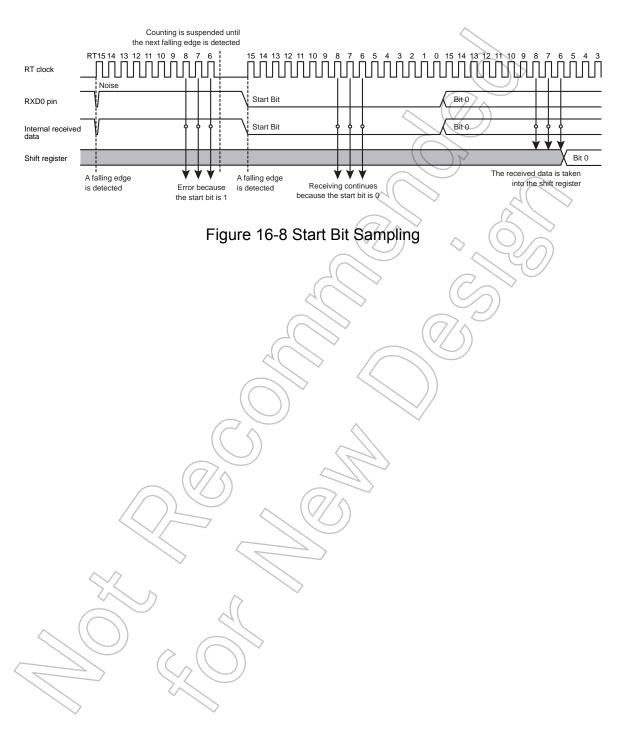

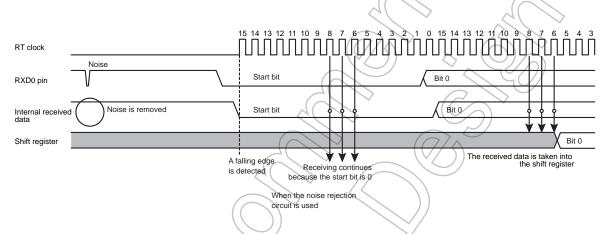

| 16.10 Received Data Noise Rejection                                                                                                                 |                                       | 231  |

| 16.11 Transmit/Receive Operation                                                                                                                    |                                       | 232  |

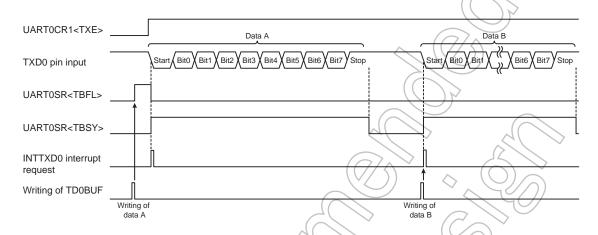

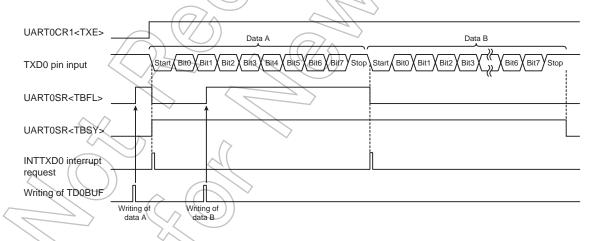

| 16.11.1 Data transmit operation                                                                                                                     |                                       | 232  |

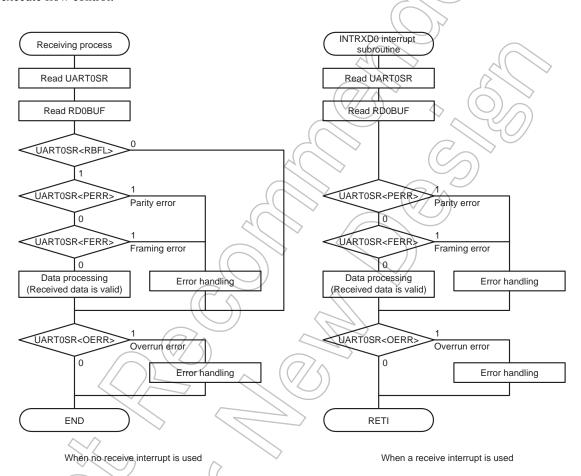

| 16.11.2 Data receive operation                                                                                                                      |                                       | 232  |

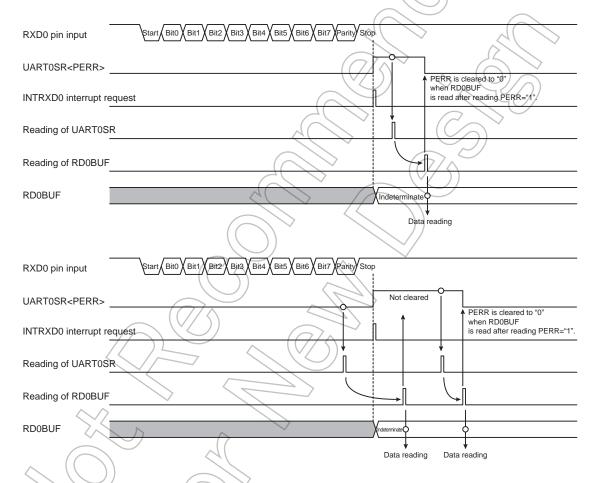

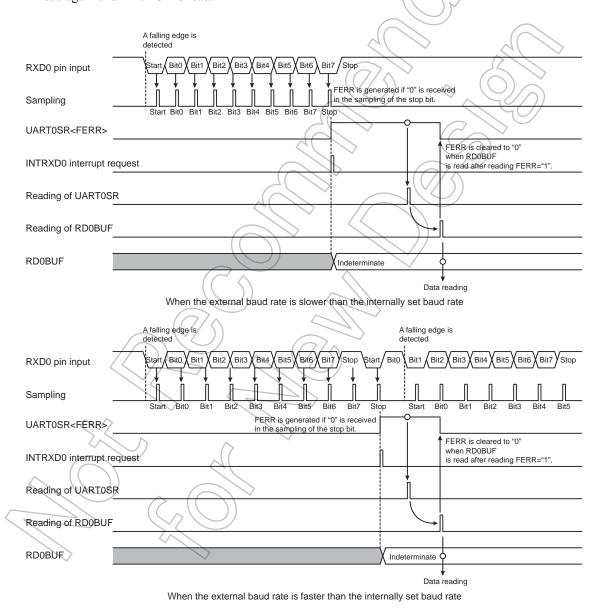

| 16.12 Status Flag                                                                                                                                   |                                       | 233  |

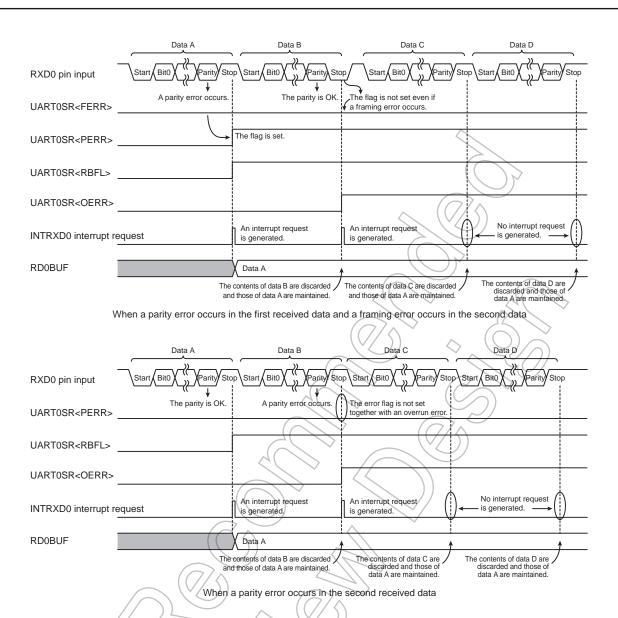

| 16.12.1 Parity error                                                                                                                                |                                       | 234  |

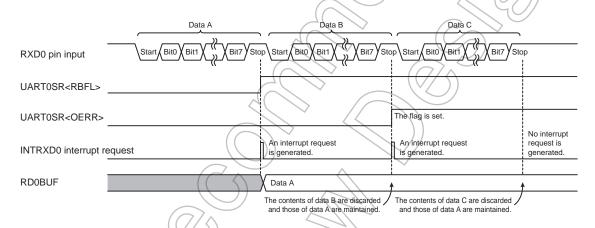

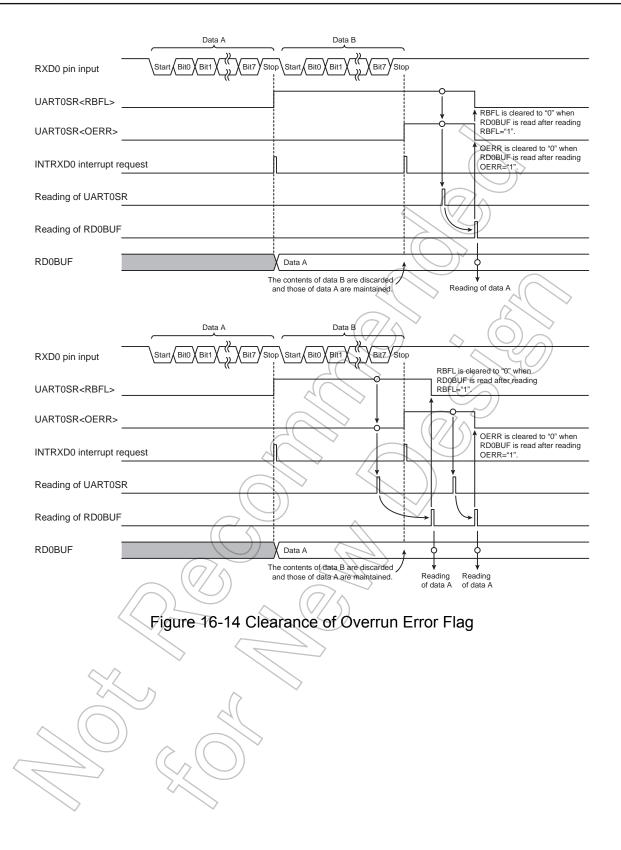

| 16.12.3 Overrun error                                                                                                                               |                                       | 235  |

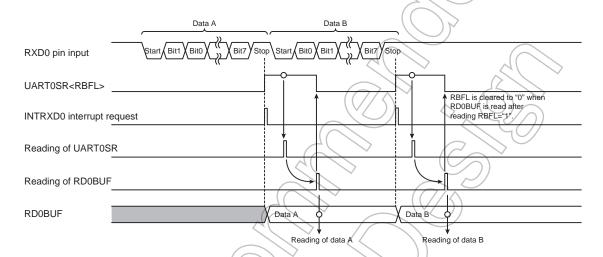

| 16.12.4 Receive Data Buffer Full                                                                                                                    |                                       | 238  |

| 16.12.5 Transmit busy flag                                                                                                                          | al s                                  | 239  |

| 16.12.6 Transmit Buffer Full                                                                                                                        |                                       | 239  |

| 16.13 Receiving Process                                                                                                                             |                                       | ′240 |

| 16.14 AC Properties                                                                                                                                 |                                       | 242  |

| 16.14.1 IrDA properties                                                                                                                             |                                       | 242  |

| 16.15 Revision History                                                                                                                              | 7()                                   | 243  |

|                                                                                                                                                     |                                       |      |

|                                                                                                                                                     |                                       |      |

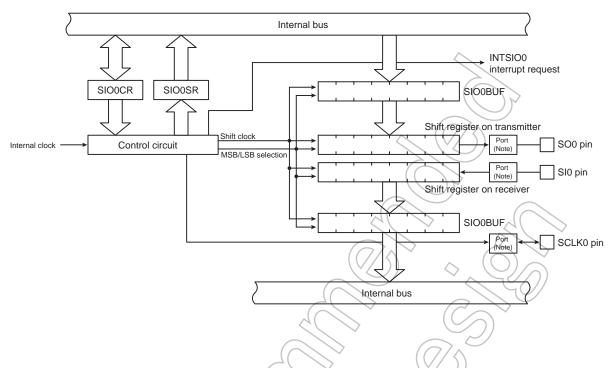

| 17. Synchronous Serial Interface (SIO                                                                                                               |                                       |      |

| 17. Synchronous Serial Interface (SIO                                                                                                               |                                       |      |

| 17.1 Configuration                                                                                                                                  |                                       | 246  |

| 17.1 Configuration                                                                                                                                  |                                       | 247  |

| 17.2 Control                                                                                                                                        | · · · · · · · · · · · · · · · · · · · | 247  |

| 17.3 Low Power Consumption Function                                                                                                                 | n                                     | 250  |

| 17.4 Functions                                                                                                                                      | /                                     | 231  |

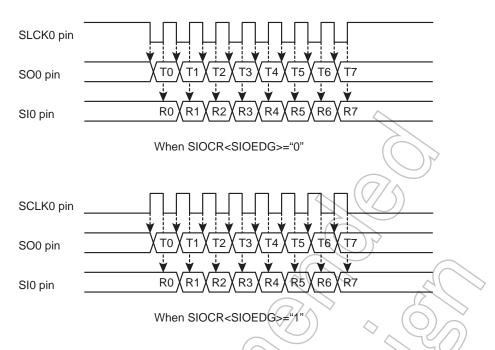

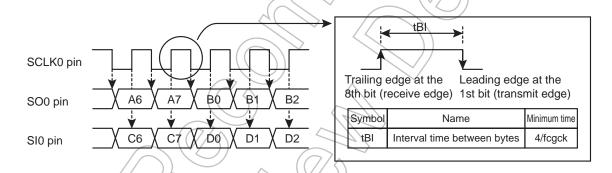

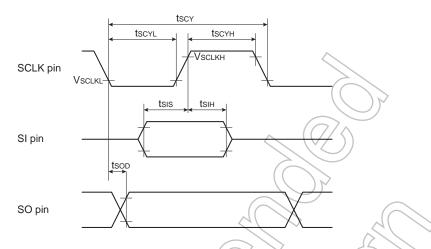

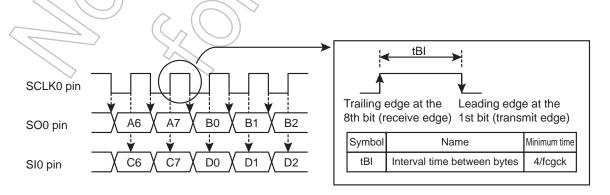

| 17.4.1 Transfer format                                                                                                                              | <u> </u>                              | 251  |

| 17.4.2 Serial clock                                                                                                                                 |                                       | 251  |

| 17.4.3 Transfer edge selection                                                                                                                      |                                       | 231  |

| 17.5 Transfer Modes.                                                                                                                                |                                       | 253  |

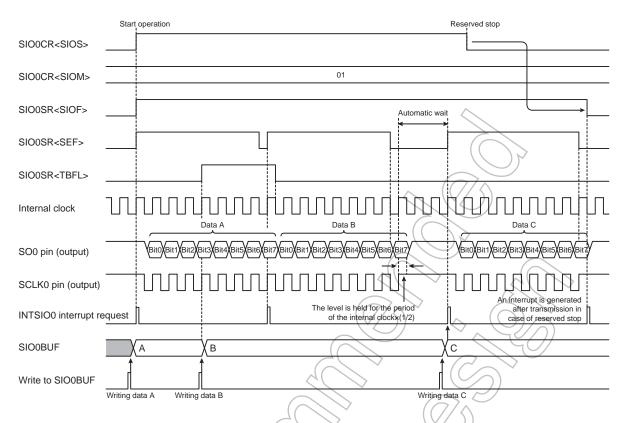

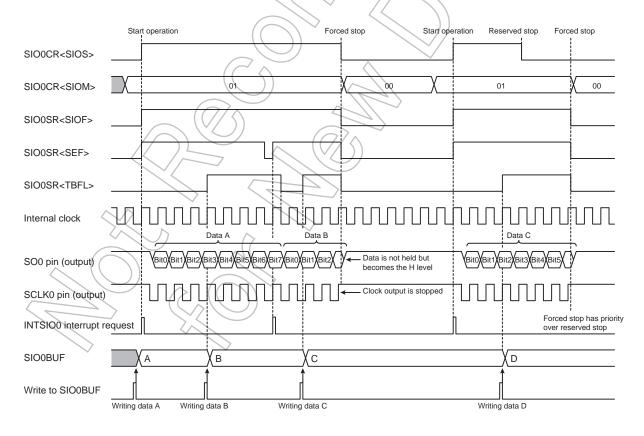

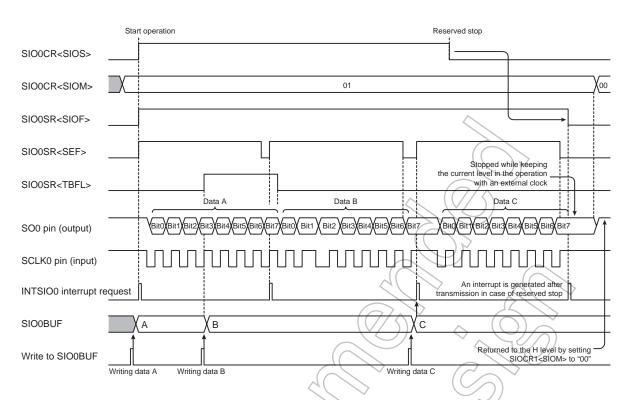

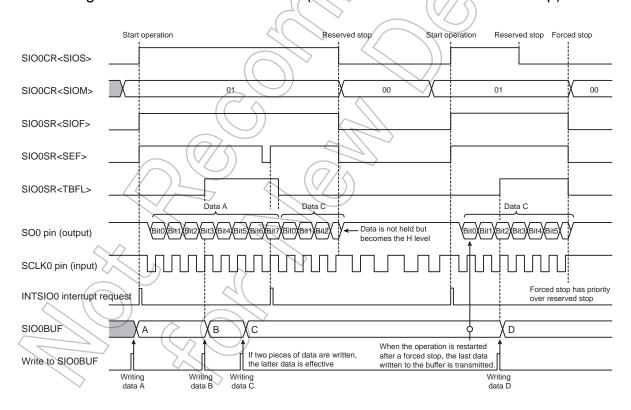

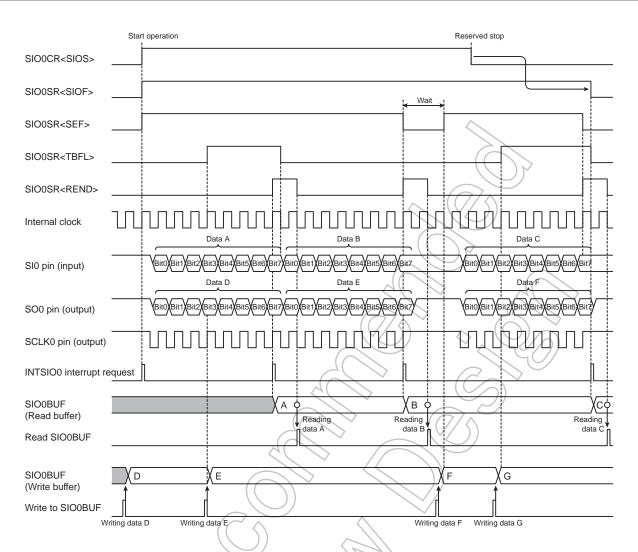

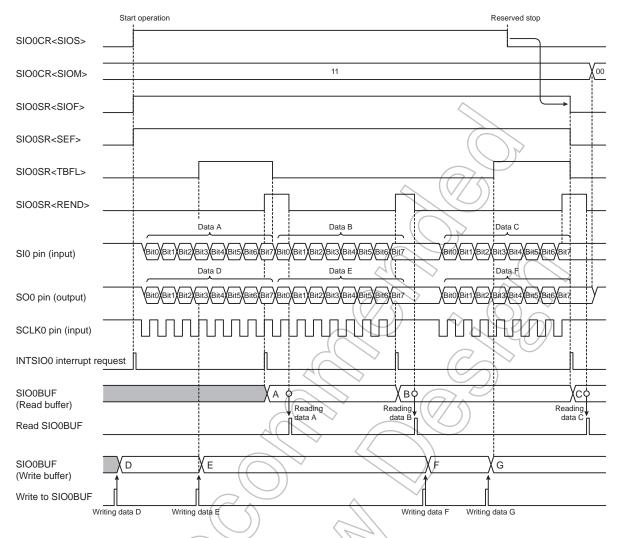

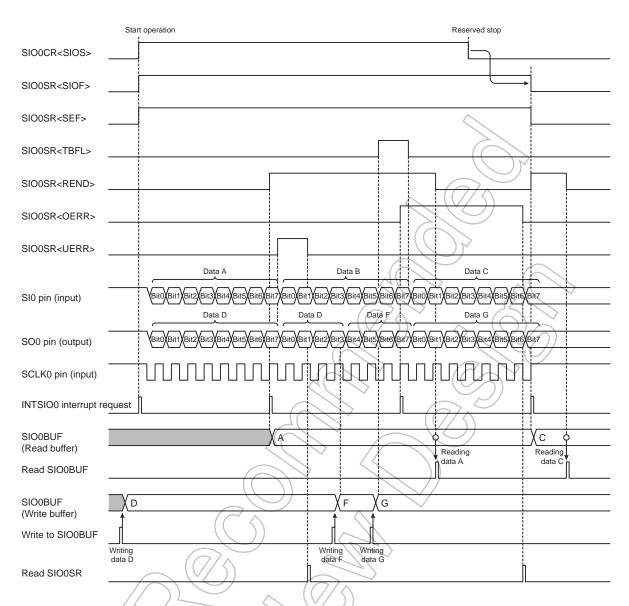

| 17.5.1 8-bit transmit mode                                                                                                                          |                                       | 233  |

| 17.5.1.1 Seating 17.5.1.2 Starting the transmit operation                                                                                           | $((// \land)$                         |      |

| 17.5.1.3 Transmit buffer and shift operation                                                                                                        |                                       |      |

| 17.5.1.4 Operation on completion of transmission 17.5.1.5 Stopping the transmit operation                                                           |                                       |      |

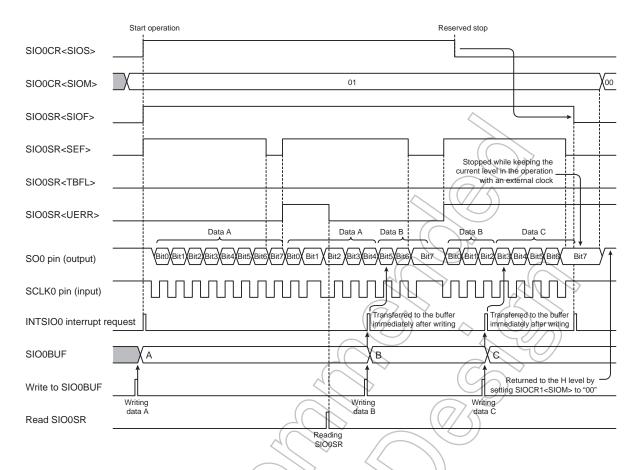

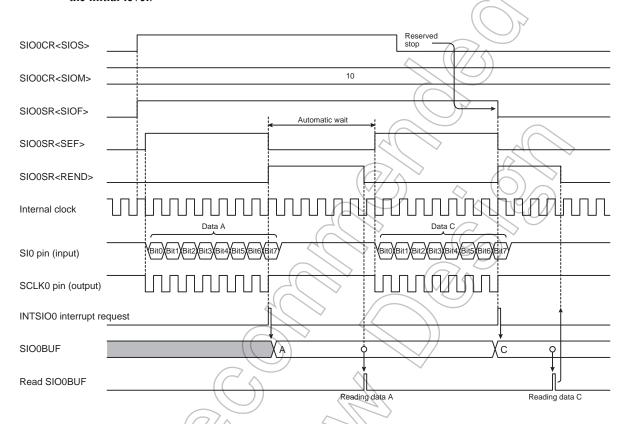

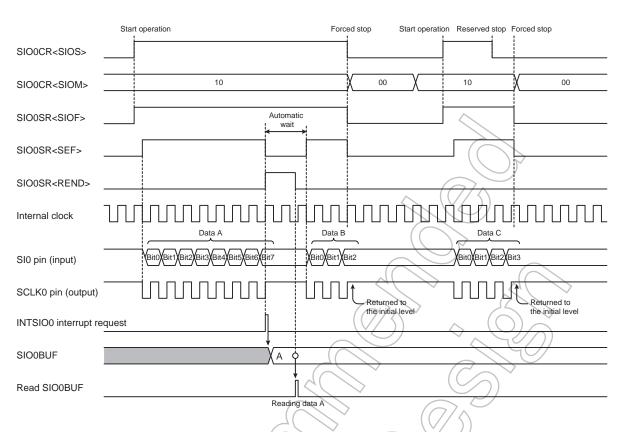

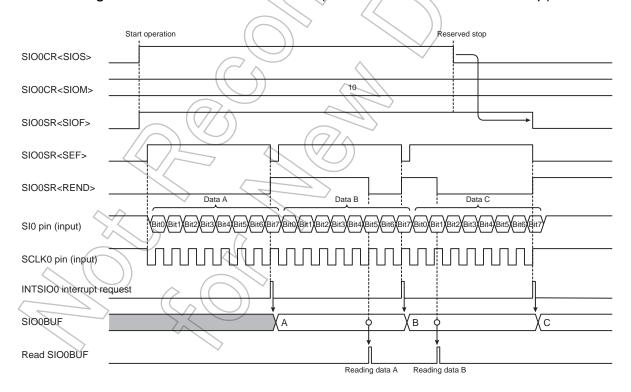

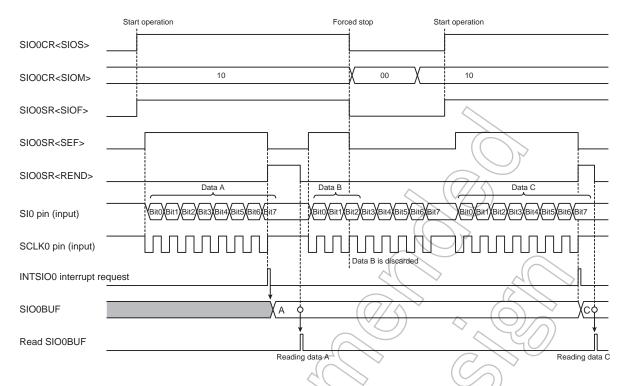

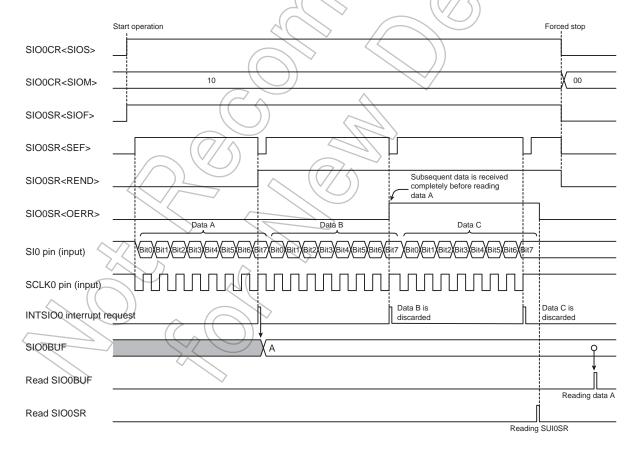

| 17.5.2 8-bit Receive Mode                                                                                                                           |                                       | 258  |

| 17.5.2.1 Setting                                                                                                                                    |                                       |      |

| 17.5.2.2 Starting the receive operation 17.5.2.3 Operation on completion of reception                                                               |                                       |      |

| 17.5.2.4 Stopping the receive operation                                                                                                             | ~                                     |      |

|                                                                                                                                                     |                                       | 262  |

| 17.5.3.1 Setting                                                                                                                                    |                                       |      |

| 17.5.3.2 Starting the transmit/receive operation 17.5.3.3 Transmit buffer and shift operation                                                       |                                       |      |

| 17.5.3.4 Operation on completion of transmission/rece                                                                                               | eption                                |      |

| 17.5.3.5 Stopping the transmit/receive operation                                                                                                    |                                       |      |

|                                                                                                                                                     |                                       |      |

| 17.7 Revision History                                                                                                                               |                                       | 268  |

| ~                                                                                                                                                   |                                       |      |

|                                                                                                                                                     |                                       |      |

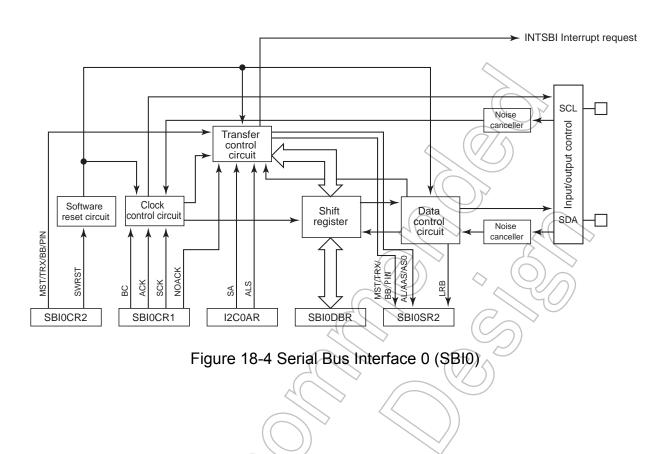

| 18. Serial Bus Interface (SBI)                                                                                                                      |                                       |      |

| io. Scriai dus interface (SDI)                                                                                                                      |                                       |      |

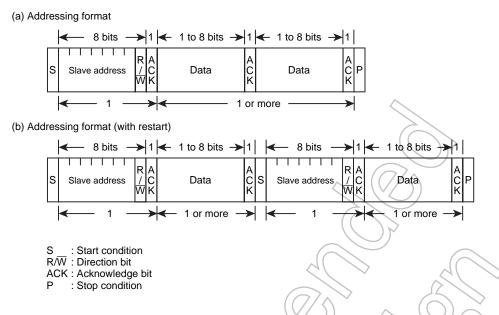

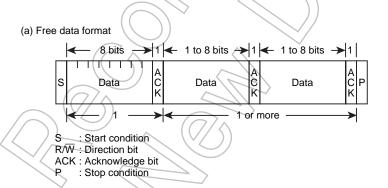

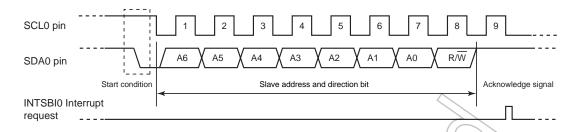

| 18.1 Communication Format                                                                                                                           |                                       | 270  |

|                                                                                                                                                     |                                       |      |

|                                                                                                                                                     |                                       |      |

|                                                                                                                                                     |                                       |      |

| 8                                                                                                                                                   |                                       |      |

| 10.5 COHUTOL                                                                                                                                        |                                       | 2/3  |

| 18.4           | Functions                                                                                               | 276   |

|----------------|---------------------------------------------------------------------------------------------------------|-------|

| 18.4.1         | Low Power Consumption Function.                                                                         | 276   |

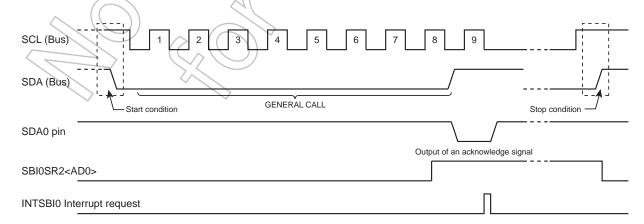

| 18.4.2         | Selecting the slave address match detection and the GENERAL CALL detection                              |       |

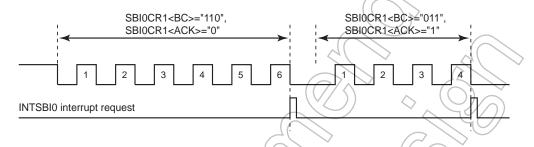

| 18.4.3         | Selecting the number of clocks for data transfer and selecting the acknowledgement or non-acknowledgmen |       |

|                | 276                                                                                                     |       |

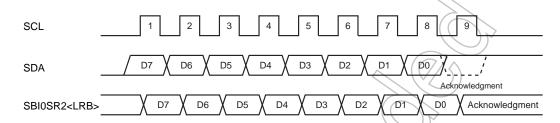

|                | 3.1 Number of clocks for data transfer                                                                  |       |

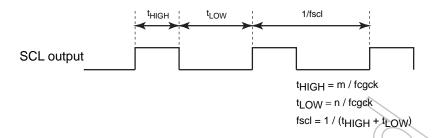

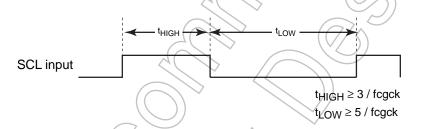

| 18.4<br>18.4.4 | .3.2 Output of an acknowledge signal Serial clock                                                       | 278   |

|                | .4.1 Clock source                                                                                       | 278   |

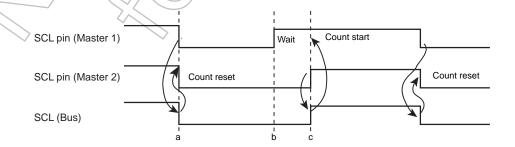

|                | .4.2 Clock synchronization                                                                              |       |

| 18.4.5         | Master/slave selection.                                                                                 | 280   |

| 18.4.6         | Transmitter/receiver selection.                                                                         | 280   |

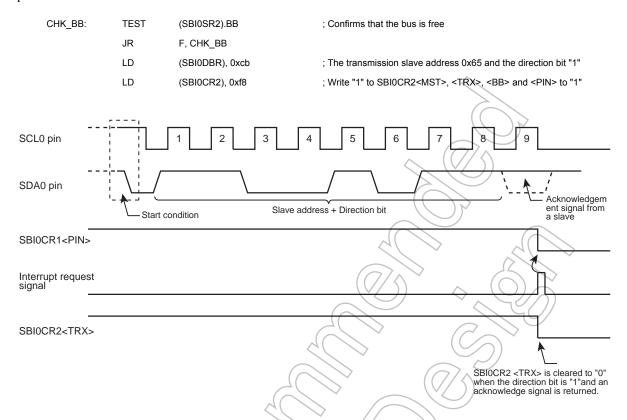

| 18.4.7         | Start/stop condition generation                                                                         | 280   |

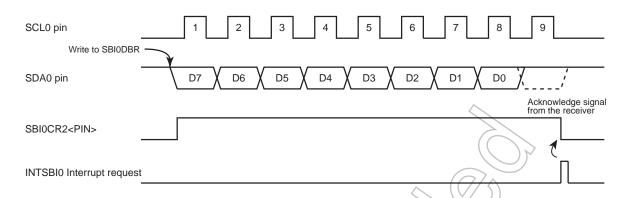

| 18.4.8         | Interrupt service request and release                                                                   | 281   |

| 18.4.9         | Setting of serial bus interface mode                                                                    |       |

| 18.4.10        |                                                                                                         |       |

| 18.4.1         |                                                                                                         | 282   |

| 18.4.12        |                                                                                                         | 284   |

| 18.4.1         |                                                                                                         | ·/284 |

| 18.4.14        |                                                                                                         |       |

| 18.4.1:        |                                                                                                         |       |

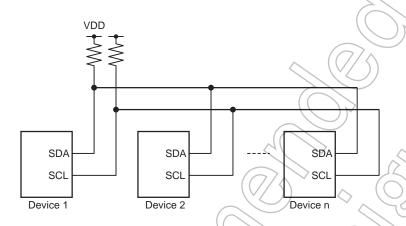

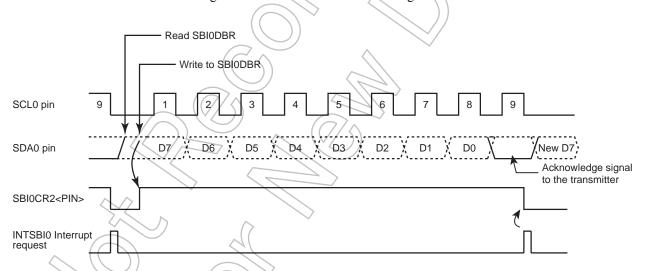

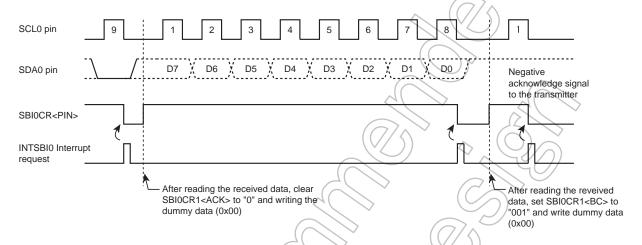

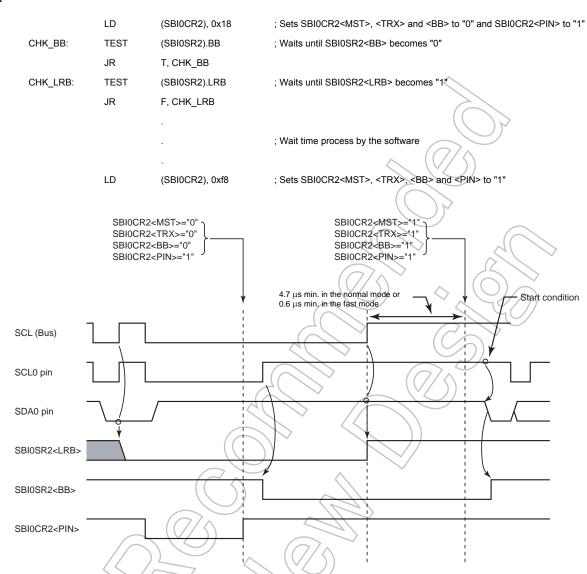

| 18.5           | Data Transfer of I2C Bus                                                                                | 286   |

| 18.5.1         | Device initialization.                                                                                  | 286   |

| 18.5.2         | 8                                                                                                       |       |

| 18.5.3         |                                                                                                         | 287   |

|                | 3.1 When SBIOSR2 <mst> is "1" (Master mode)</mst>                                                       |       |

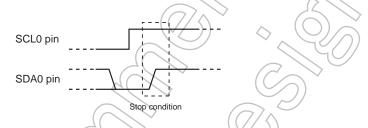

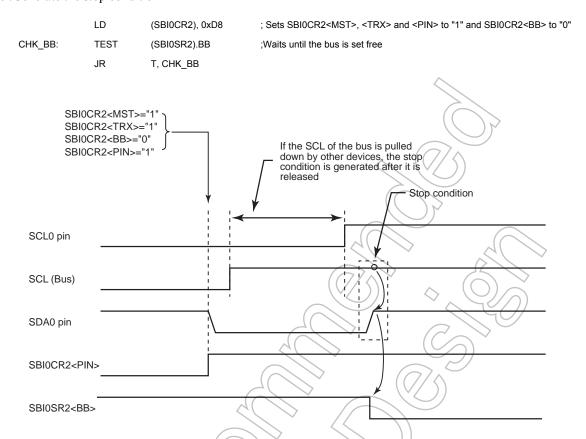

| 18.5.4         | 3.2 When SBI0SR2 <mst> is "0" (Slave mode) Stop condition generation</mst>                              | 290   |

| 18.5.5         | Restart.                                                                                                |       |

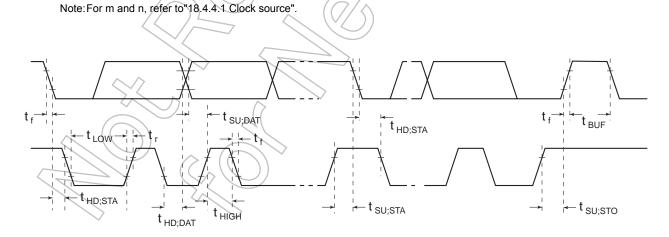

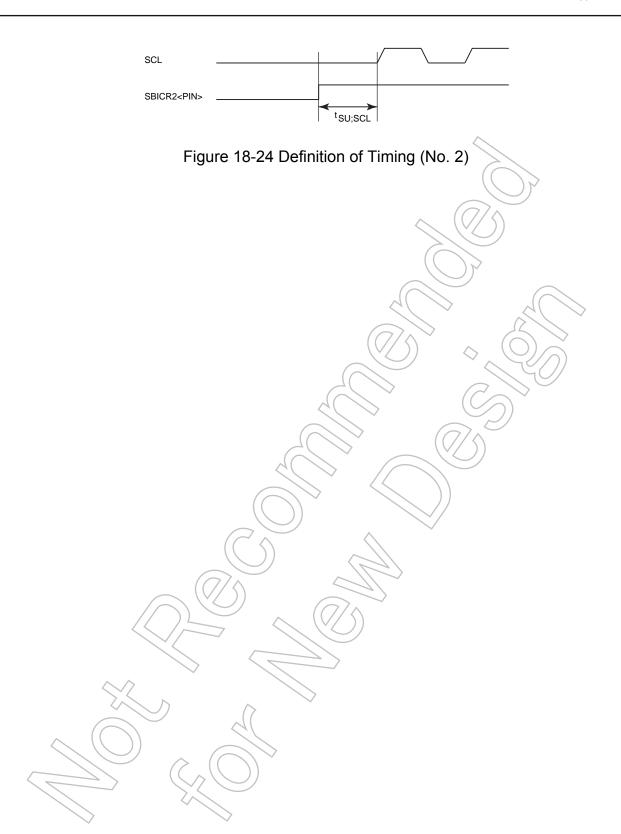

|                | AC Specifications                                                                                       |       |

| 10.0           | AC Specifications                                                                                       |       |

| 18.7           | Revision History                                                                                        | 295   |

|                |                                                                                                         |       |

|                |                                                                                                         |       |

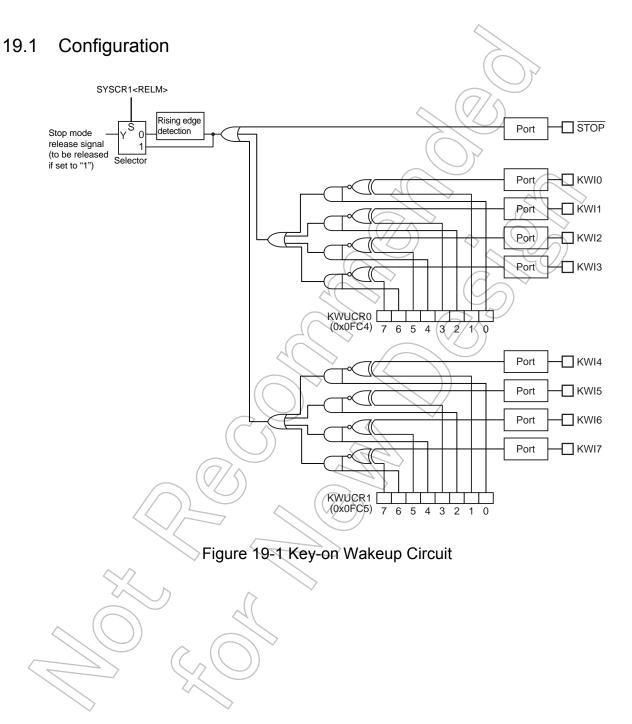

| 19. Key-       | on Walson (ZWII)                                                                                        |       |

| 19. Key-       | on Wakeup (KWU)                                                                                         |       |

| 40.4           |                                                                                                         | 205   |

|                | Configuration                                                                                           |       |

| 19.2           | Control                                                                                                 | 298   |

| 19.3           | Functions/                                                                                              | 299   |

| 17.5           | T UNCHOUS.                                                                                              |       |

|                |                                                                                                         |       |

|                |                                                                                                         |       |

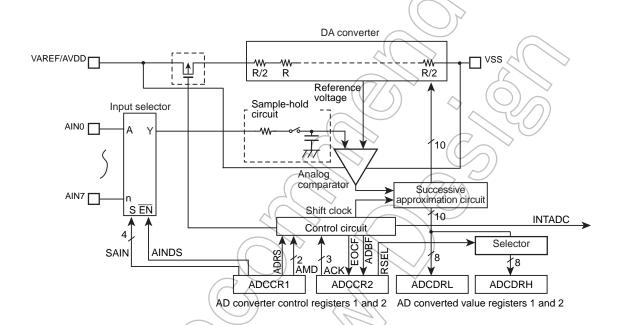

| 20. 10-bi      | t AD Converter (ADC)                                                                                    |       |

| 10 01          | (TID CONVERCE (TIDE)                                                                                    |       |

| 20.1           | Configuration                                                                                           | 301   |

|                | 3 ( ) / / /                                                                                             |       |

| 20.2           | Control                                                                                                 | 302   |

| 20.3           | Functions                                                                                               | 306   |

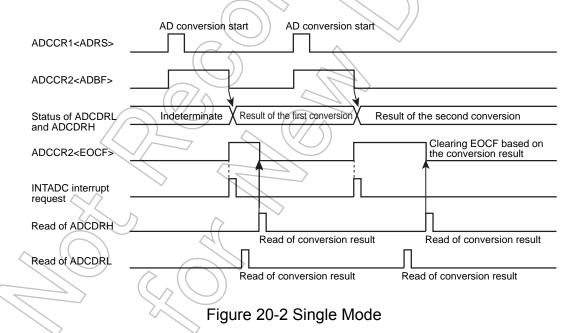

| 20.3.1         |                                                                                                         |       |

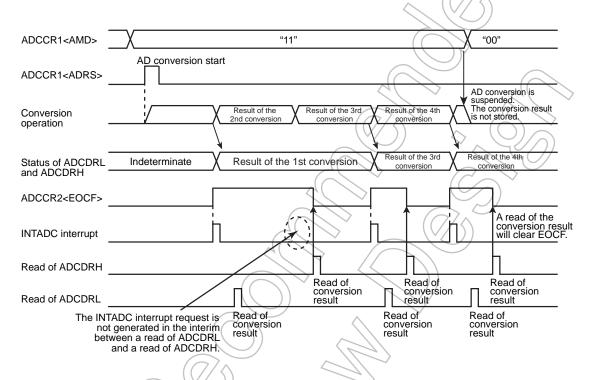

|                | Repeat mode                                                                                             |       |

| 20.3.3         | AD operation disable and forced stop of AD operation.                                                   | 307   |

| 20.4           | Register Setting                                                                                        |       |

|                |                                                                                                         |       |

|                | Starting STOP/IDLE0/SLOW Modes                                                                          |       |

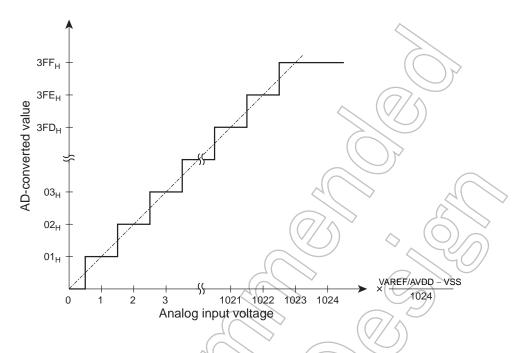

| 20.6           | Analog Input Voltage and AD Conversion Result                                                           | 309   |

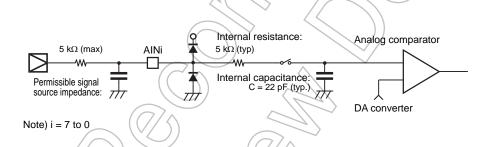

|                | Precautions about the AD Converter                                                                      |       |

| 20.7.1         | Analog input pin voltage range                                                                          |       |

| 20.7.2         | Analog input pin voltage range.  Analog input pins used as input/output ports                           |       |

| 20.7.3         | Noise countermeasure                                                                                    |       |

|                | Revision History                                                                                        |       |

| 40.0           | ICTISIOII IIISIOI y                                                                                     |       |

| 21. | Inpu  | ıt/Output Circuit             |                      |                   |          |                       |     |

|-----|-------|-------------------------------|----------------------|-------------------|----------|-----------------------|-----|

|     | 21.1  | Control Pins                  |                      |                   |          | 3                     | 313 |

|     |       |                               |                      |                   |          |                       |     |

| 22. | Elec  | trical Characteristic         | S                    |                   |          |                       |     |

|     | 22.1  | Absolute Maximum Ra           | atings               | ((                |          | 3                     | 315 |

|     | 22.2  | <b>Operating Conditions</b>   | _                    |                   | / / / .  |                       | 316 |

|     | 22.3  | DC Characteristics            |                      |                   |          |                       | 317 |

|     | 22.4  | <b>AD Conversion Chara</b>    | cteristics           |                   | <u> </u> | ., 3</th <th>318</th> | 318 |

|     | 22.5  | Power-on Reset Circuit        | t Characteristics    |                   | /.       | 3                     | 319 |

|     | 22.6  | <b>Voltage Detecting Circ</b> | uit Characteristics. | (\(\lambda\(/\))) |          | <u></u>               | 320 |

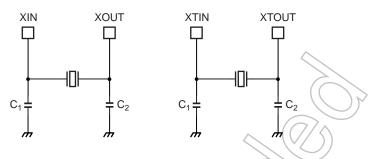

|     | 22.7  | AC Characteristics            |                      |                   |          | 3                     | 321 |

|     | 22.8  | Oscillating Condition         |                      |                   |          | 3                     | 322 |

|     | 22.9  | Handling Precaution           | A(                   |                   | (.(      | }3                    | 323 |

|     | 22.10 | Revision History              |                      | <i></i>           |          | 3                     | 324 |

|     |       |                               |                      | > (               |          |                       |     |

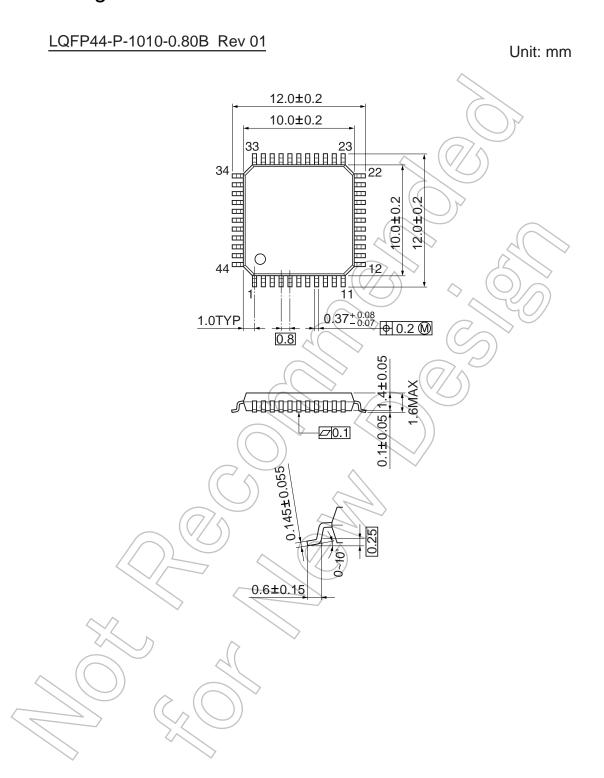

| 23. | Pacl  | kage Dimensions               | 4()                  |                   |          |                       |     |

|     |       |                               |                      |                   |          |                       |     |

#### CMOS 8-Bit Microcontroller

# TMP89CH42

The TMP89CH42 is a single-chip 8-bit high-speed and high-functionality microcomputer incorporating 16384 bytes of Mask ROM.

| Product No. | ROM<br>(Mask ROM) | RAM        | Package             | Flash MCU   | Emulation Chip |

|-------------|-------------------|------------|---------------------|-------------|----------------|

| TMP89CH42UG | 16384 bytes       | 2048 bytes | LQFP44-P-1010-0.80B | TMP89FH42UG | * TMP89C900XBG |

Note: \*; Under development

#### 1.1 Features

- 1. 8-bit single chip microcomputer TLCS-870/C1 series

- Instruction execution time :

100 ns (at 10 MHz)

122 µs (at 32.768 kHz)

- 133 types & 732 basic instructions

- 2. 25 interrupt sources (External: 6 Internal: 19, Except reset)

- 3. Input / Output ports (40 pins)

Note: Two of above pins can not be used for the I/O port, because they should be connected with the high frequency OSC input.

- Large current output: 8 pins (Typ. 20mA)

- 4. Watchdog timer

- Interrupt or reset can be selected by the program

- 5. Power-on reset circuit

- 6. Voltage detection circuit

- 7. Divider output function

- 8. Time base timer

- 9. 16-bit timer counter (TCA): 2 ch

- Timer, External trigger, Event Counter, Window, Pulse width measurement, PPG OUTPUT modes

- 10. 8-bit timer counter (TC0): 4 ch

- Timer, Event Counter, PWM, PPG OUTPUT modes

- Usable as a 16-bit timer, 12-bit PWM output and 16-bit PPG output by the cascade connection of two channels.

- 11. Real time clock

- 12. UART: 1ch

- 13. UART/SIO: 1ch Note: One SIO channel can be used at the same time.

- 14. I2C/SIO: 1ch

- 15. Key-on wake-up: 8 ch

- 16. 10-bit successive approximation type AD converter

- Analog input: 8ch

- 17. Clock operation mode control circuit: 2 circuit

Single clock mode / Dual clock mode

18. Low power consumption operation (8 mode)

1.1 Features TMP89CH42

- STOP mode:

Oscillation stops. (Battery/Capacitor back-up.)

- SLOW1 mode:

Low power consumption operation using low-frequency clock.(High-frequency clock stop.)

- SLOW2 mode:

Low power consumption operation using low-frequency clock.(High-frequency clock oscillate.)

IDLE0 mode:

CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using high frequency clock. Released when the reference time set to TBT has elapsed.

IDLE1 mode:

The CPU stops, and peripherals operate using high frequency clock. Release by interruputs(CPU restarts).

- IDLE2 mode:

CPU stops and peripherals operate using high and low frequency clock. Release by interruputs. (CPU restarts).

- SLEEP0 mode:

CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using low frequency clock. Released when the reference time set to TBT has elapsed.

- SLEEP1 mode:

CPU stops, and peripherals operate using low frequency clock. Release by interruput. (CPU restarts).

19. Wide operation voltage:

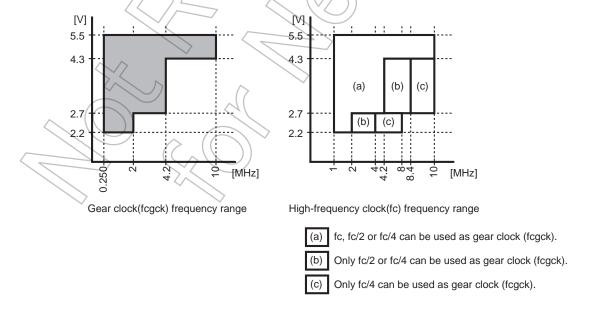

4.3 V to 5.5 V at 10MHz /32.768 kHz 2.7 V to 5.5 V at 4.2 MHz /32,768 kHz 2.2 V to 5.5 V at 2MHz /32.768 kHz

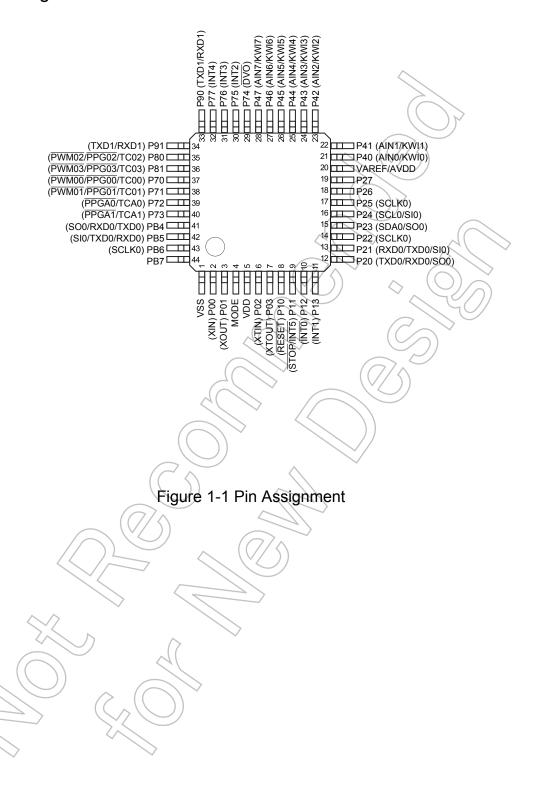

# 1.2 Pin Assignment

1.3 Block Diagram TMP89CH42

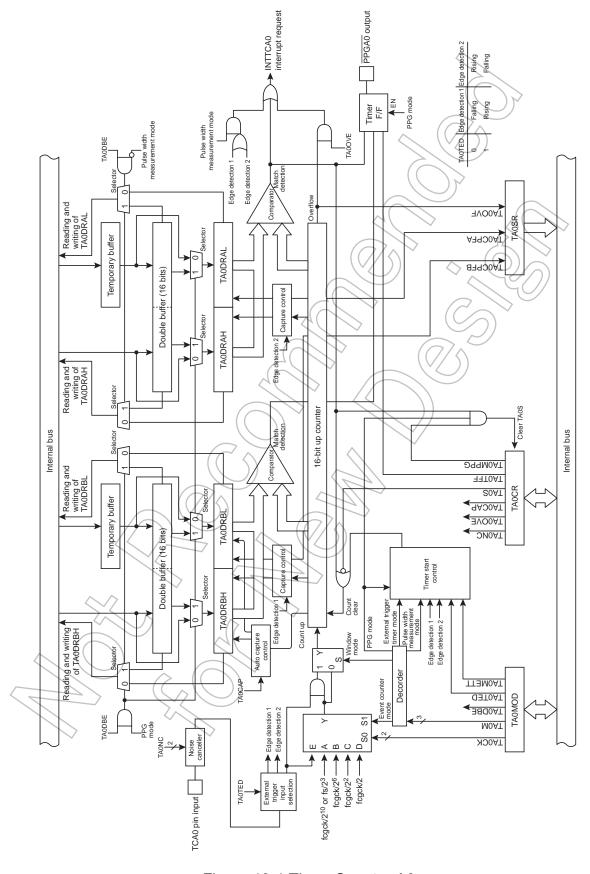

# 1.3 Block Diagram

Figure 1-2 Block Diagram

# 1.4 Pin Names and Functions

Table 1-1 Pin Names and Functions (1/3)

| Pin Name                   | Input/Output  | Functions                                                        |

|----------------------------|---------------|------------------------------------------------------------------|

| P03<br>XTOUT               | 10<br>0       | PORT03<br>Low frequency OSC output                               |

| P02<br>XTIN                | 10<br>1       | PORT02<br>Low frequency OSC input                                |

| P01<br>XOUT                | 10<br>0       | PORT01<br>High frequency OSC output                              |

| P00<br>XIN                 | 10<br>1       | PORT00 High frequency OS& input                                  |

| P13<br>INT1                | 10<br>1       | PORT13 External interrupt 1 input                                |

| P12<br>INTO                | 10<br>1       | PORT12 External interrupt 0 input                                |

| P11<br>INT5<br>STOP        | IO<br>I       | PORT11 External interrupt 5 input STOP mode release input        |

| P10<br>RESET               | 10            | PORT10 Reset signal input                                        |

| P27                        | 10            | PORT27                                                           |

| P26                        | 10            | PORT26                                                           |

| P25<br>SCLK0               | 10            | PORT25<br>Serial clock input/output 0                            |

| P24<br>SCL0<br>SI0         | 10            | PORT24 I2C bus clock input/output 0 Serial data input 0          |

| P23<br>SDA0<br>SO0         | 10<br>10<br>0 | PORT23 12C bus data input/output 0 Serial data output 0          |

| P22<br>SCLK0               | 10            | PORT22<br>Serial clock input/output 0                            |

| P21<br>RXD0<br>TXD0<br>SI0 | 10            | PORT21 UART data input 0 UART data output 0 Serial data input 0  |

| P20<br>TXD0<br>RXD0<br>SO0 | 1000          | PORT20 UART data output 0 UART data input 0 Serial data output 0 |

1.4 Pin Names and Functions TMP89CH42

Table 1-2 Pin Names and Functions (2/3)

| Pin Name                      | Input/Output      | Functions                                    |

|-------------------------------|-------------------|----------------------------------------------|

| P47<br>AIN7<br>KWI7           | 10<br>            | PORT47 Analog input 7 Key-on wake-up input 7 |

| P46<br>AIN6<br>KWI6           | 10<br> <br>       | PORT46 Analog input 6 Key-on wake-up input 6 |

| P45<br>AIN5<br>KWI5           | 10<br> <br>       | PORT45 Analog input 5 Key-on wake-up input 5 |

| P44<br>AIN4<br>KWI4           | 10<br>            | PORT44 Analog input 4 Key-on wake-up input 4 |

| P43<br>AIN3<br>KWI3           | 10<br>            | PORT43 Analog input 3 Key-on wake-up input 3 |

| P42<br>AIN2<br>KWI2           | 10<br>1           | PORT42 Analog input 2 Key-on wake-up input 2 |

| P41<br>AIN1<br>KWI1           | 10                | PORT41 Analog input 1 Key-on wake-up input 1 |

| P40<br>AIN0<br>KWI0           |                   | PORT40 Analog input 0 Key-on wake-up input 0 |

| P77<br>INT4                   | 10                | PORT77 External interrupt 4 input            |

| P76<br>INT3                   | IO I              | PORT76 External interrupt 3 input            |

| P75<br>INT2                   | 10                | PORT75 External interrupt 2 input            |

| P74 DVO                       | 0                 | PÓRT74 Divider output                        |

| P73<br>TCA1<br>PPGA1          | 10                | PORT73 TCA1 input PPGA1 output               |

| P72<br>TCA0<br>PPGA0          |                   | PORT72 TCA0 input PPGA0 output               |

| P71<br>TC01<br>PPG01<br>PWM01 | IO<br>I<br>O<br>O | PORT71 TC01 input PPG01 output PWM01 output  |

Table 1-2 Pin Names and Functions (3/3)

| Pin Name                      | Input/Output      | Functions                                                                         |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------|

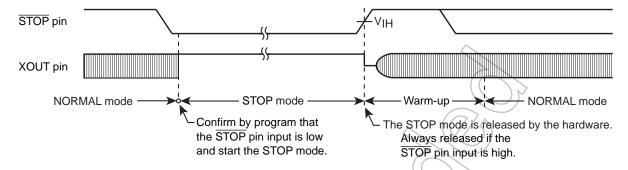

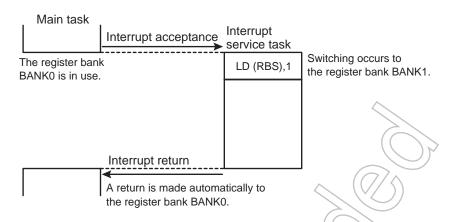

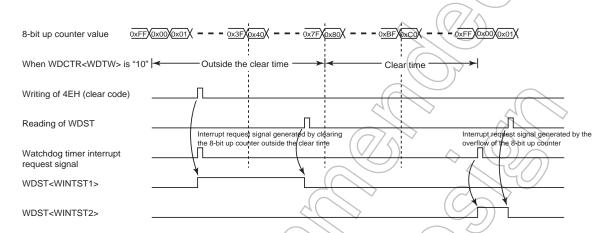

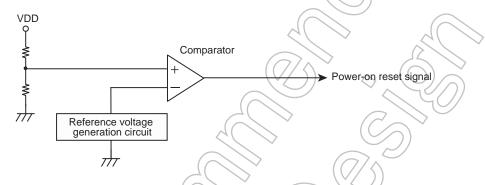

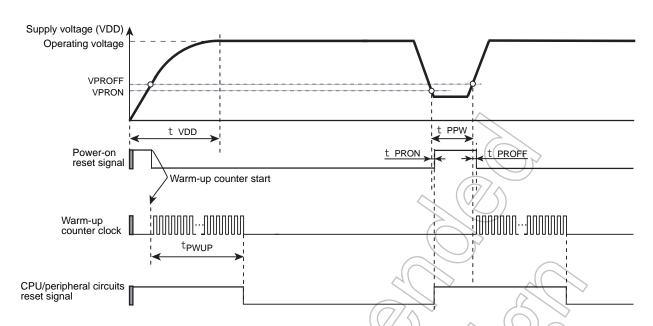

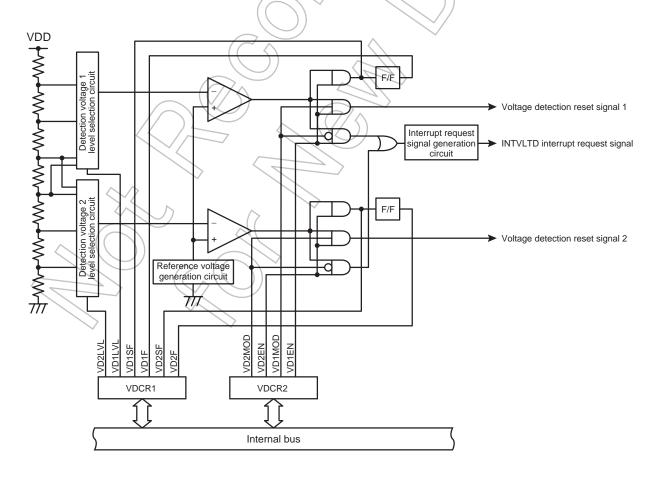

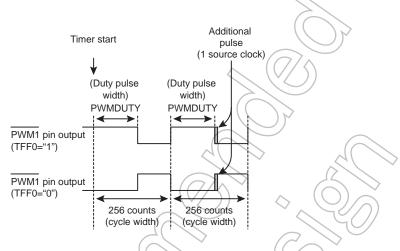

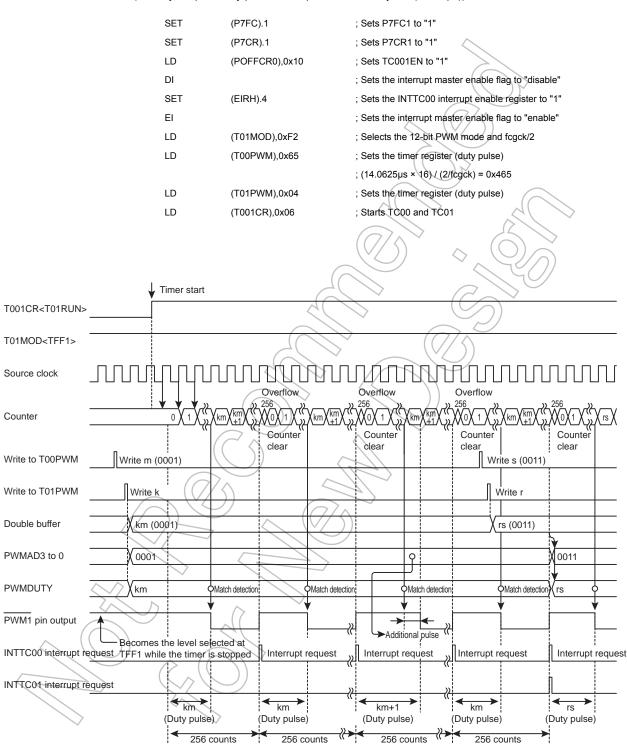

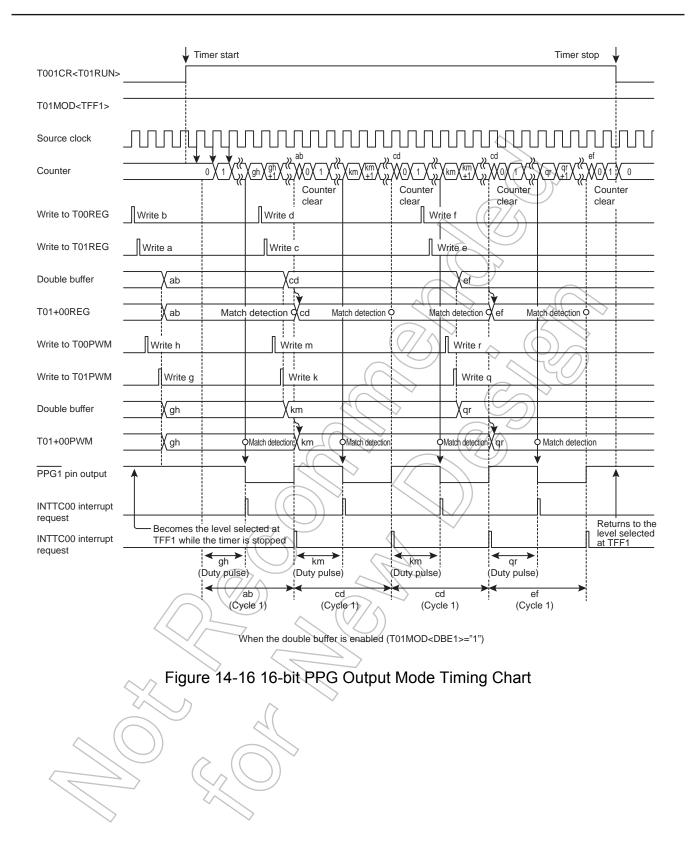

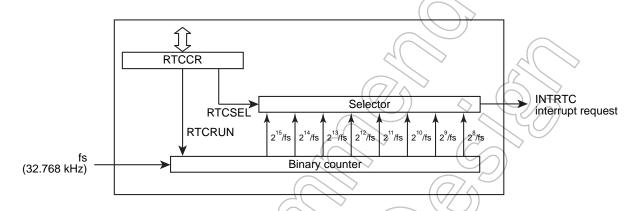

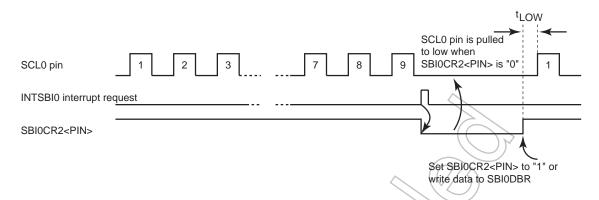

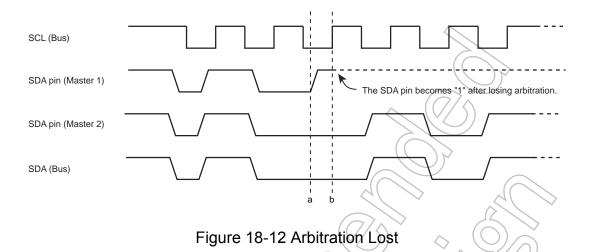

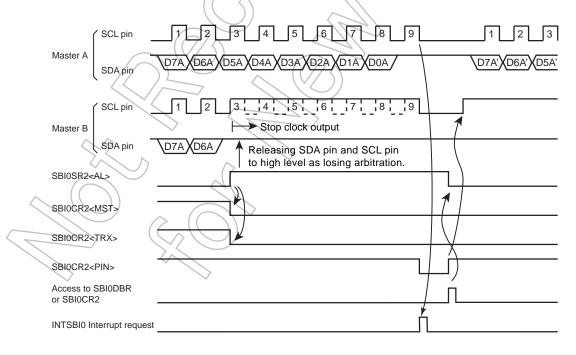

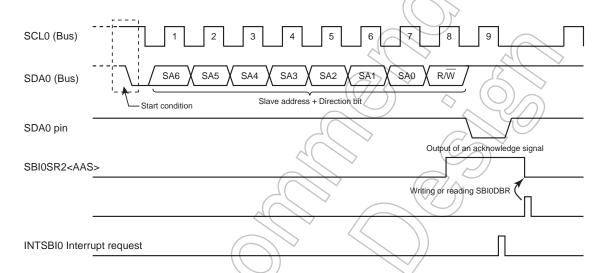

| P70<br>TC00<br>PPG00<br>PWM00 | IO<br>I<br>O<br>O | PORT70 TC00 input PPG00 output PWM00 output                                       |