# **TOSHIBA**

TLCS-900/L1 Series

TMP91CW40FG

# **TOSHIBA CORPORATION**

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

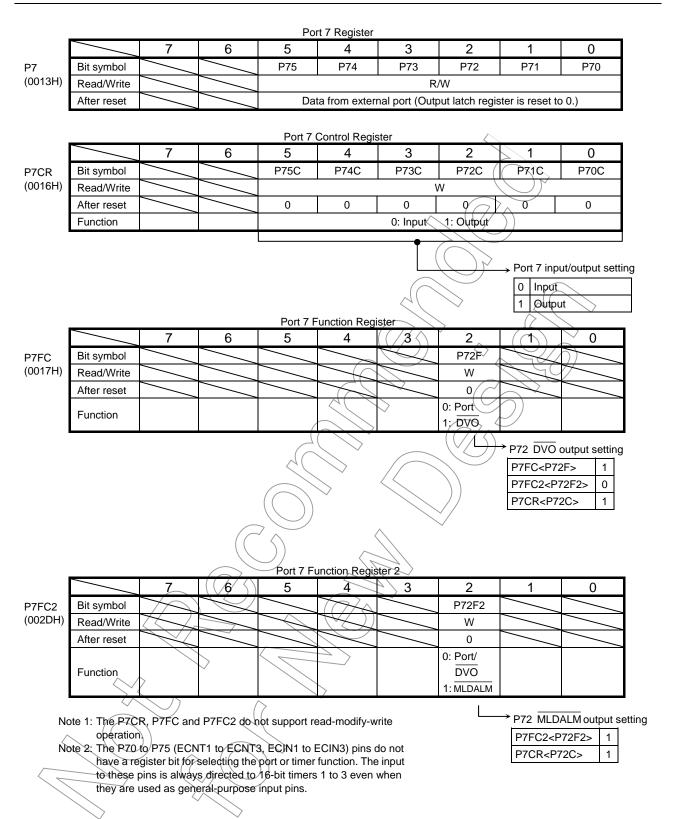

Low Voltage/Low Power Consumption

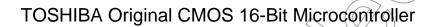

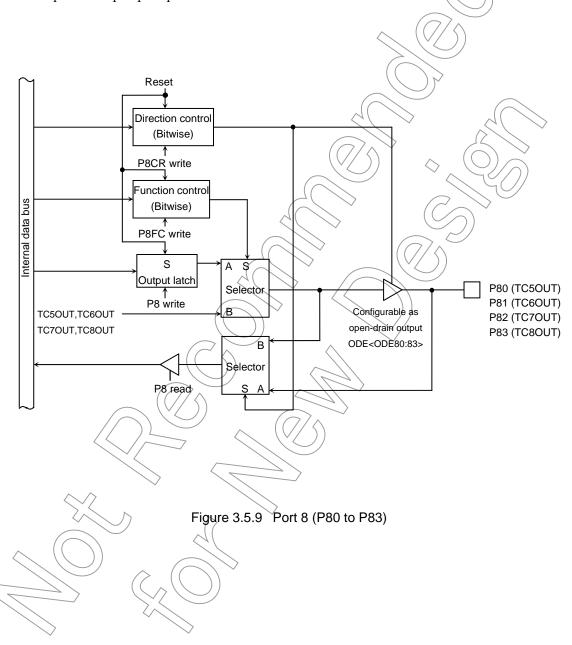

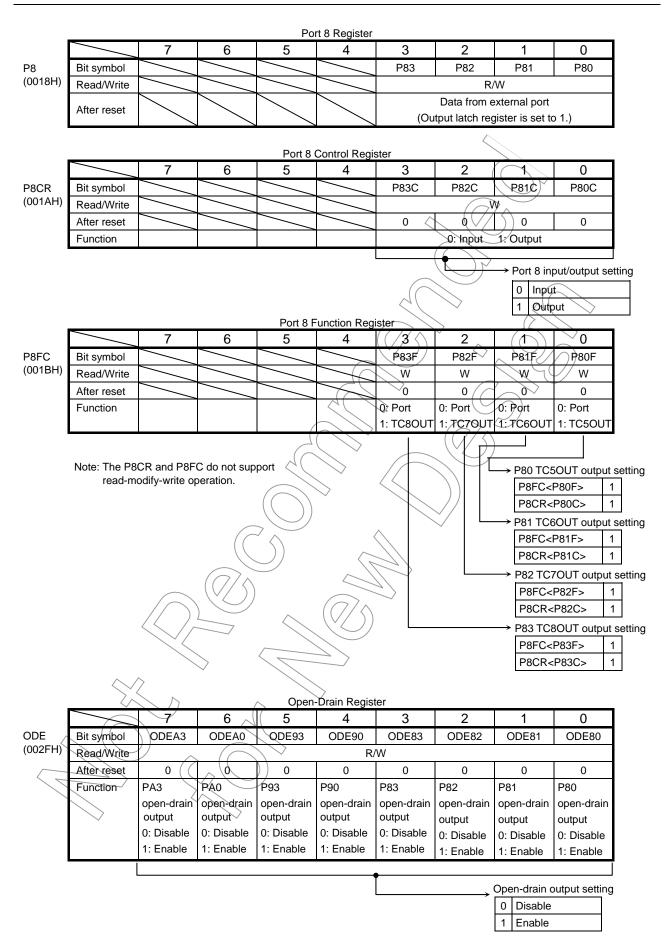

# CMOS 16-Bit Microcontroller TMP91CW40FG

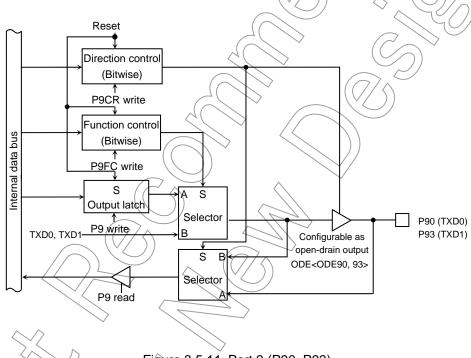

# Outline and Features

The TMP91CW40 is a high-speed, high-performance 16-bit microcontroller capable of low-voltage, low-power-consumption operation.

This microcontroller comes in a 100-pin flat package and has the following features:

- (1) Toshiba proprietary 16-bit CPU (900/L1 CPU)

- Instruction mnemonics are upwardly compatible with the TLCS-90 and TLCS-900.

- 16-Mbyte linear address space

- Architecture based on general-purpose registers and register banks

- 16-bit multiply/divide instructions and bit transfer/arithmetic instructions

- Micro DMA: 4 channels (593 ns/2 bytes at 27 MHz)

- (2) Minimum instruction execution time: 148 ns (at 27 MHz)

- (3) Internal RAM: 4 Kbytes

- (4) Internal ROM: 128 Kbytes

# RESTRICTIONS ON PRODUCT USE

20070701-EN GENERAL

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as controlling the products.

set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- (5) 8-bit timer: 4 channels

- (6) 16-bit timer: 3 channels

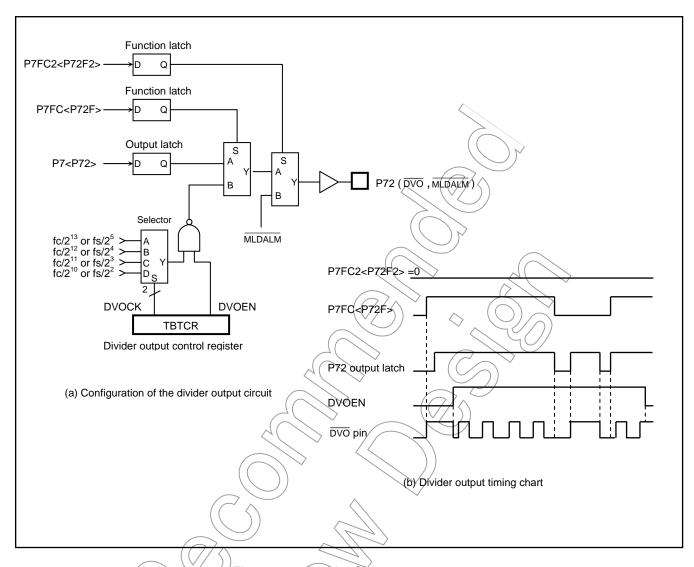

- (7) Divider output

- (8) General-purpose serial interface: 4 channels

- Both UART and synchronous transfer modes are supported.

- (9) 10-bit AD converter (with sample-and-hold): 4 channels

- (10) Watchdog timer

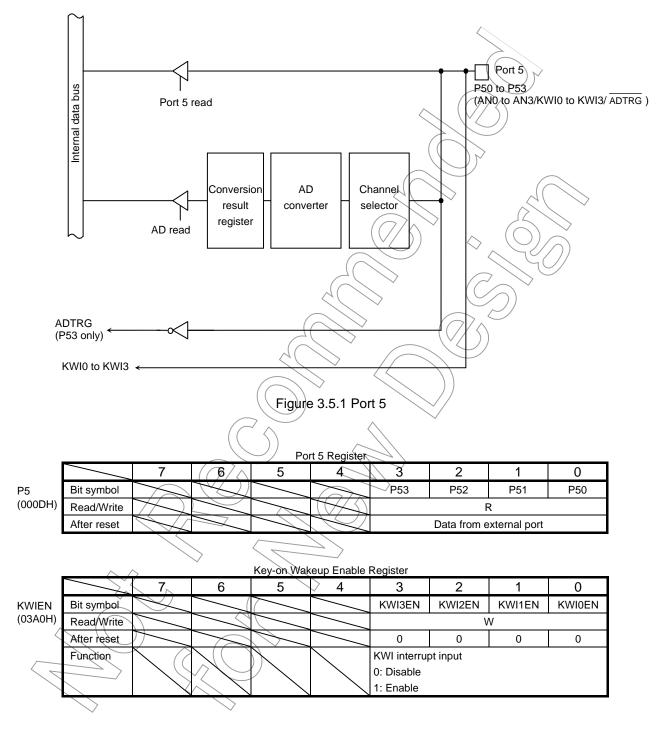

- (11) Key-on wakeup: 4 channels

- (12) Real-time clock (RTC)

- Based on the TC8521A specifications

- (13) Melody/Alarm generator (MLD)

- (14) Program patch logic: 6 banks

- (15) LCD driver/controller (voltage reducer type, reference voltage = VCC)

- LCD direct drive possible (8 to 40 segments x 4 commons)

- 1/4 duty, 1/3 duty, 1/2 duty or static drive selectable

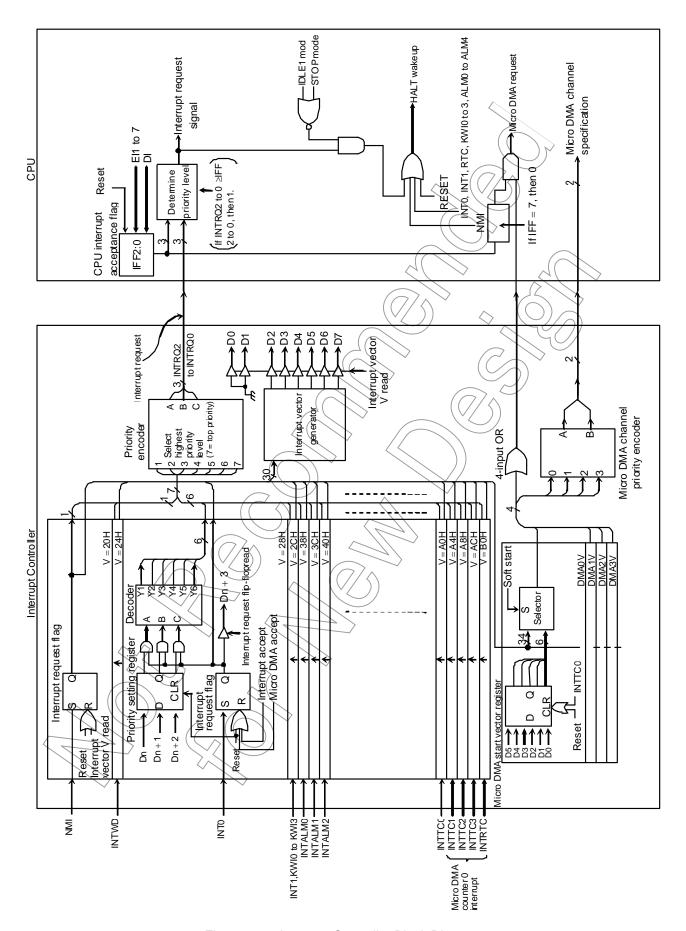

- (16) Interrupts: 43 sources

- 9 CPU interrupts: Triggered by a software interrupt instruction or undefined instruction

- 27 internal interrupts: 7 priority levels

- 7 external interrupts: 7 priority levels

(Two interrupts support selection of triggering edge.)

- (17) Input/output ports: 61 pins

- (18) Standby function

Three HALT modes (programmable IDLE2, IDLE1, STOP)

- (19) Clock control function

- Low-frequency clock (fs = 32.768 kHz)

- (20) Operating voltage range

- $Vec \neq 2.7 \text{ to } 3.6 \text{ V (fc max} = 27 \text{ MHz)}$

- Vcc = 2.2 to 3.6 V (fc max = 16 MHz)

(

m VCC < 2.7V: LCDD disabled.)

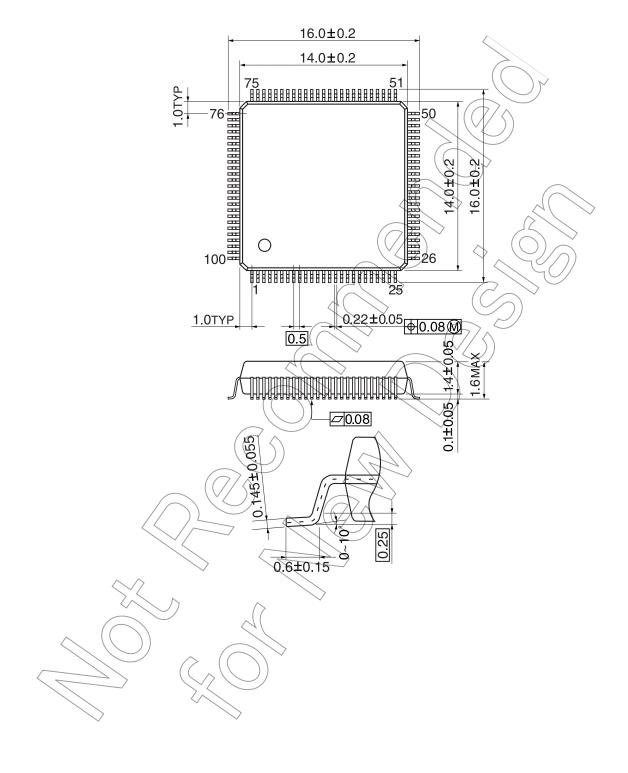

(21) Package: LQFP100-P-1414-0.50F

91CW40-2 2008-09-19

# 2. Pin Assignments and Pin Functions

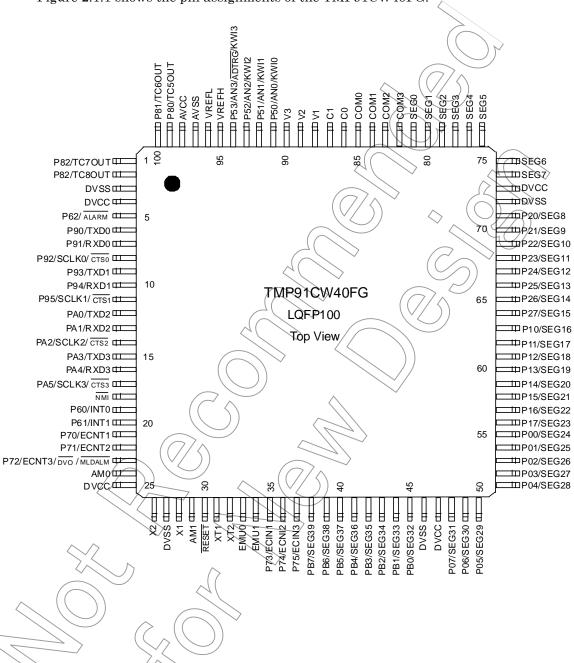

The assignment of input/output pins for the TMP91CW40, their names and functions are follows:

# 2.1 Pin Assignments

Figure 2.1.1 TMP91CW40FG Pin Assignments (100-pin LQFP, top view)

# 2.2 Pin Names and Functions

Table 2.2.1 to Table 2.2.2 list the names and functions of the input and output pins of the TMP91CW40.

Table 2.2.1 Pin Names and Functions (1/2)

|              |                 | ıα       | ble 2.2.1 Pin Names and Functions (1/2)                                                                                             |

|--------------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name     | Number of Pins  | I/O      | Function                                                                                                                            |

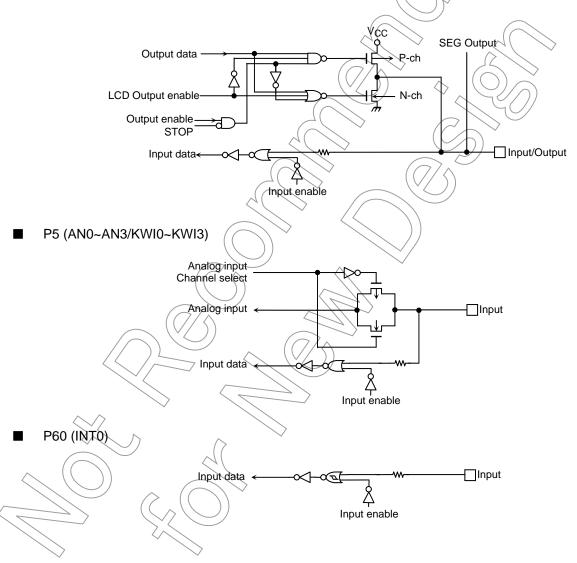

| P50 to P53   | 4               | Input    | Port 5: Input port                                                                                                                  |

| AN0 to AN3   |                 | Input    | Analog input: Input to the AD converter                                                                                             |

| ADTRG        |                 | Input    | AD trigger: External start request pin for the AD converter (multiplexed with P53)                                                  |

| KWI0 to KWI3 |                 | Input    | Key-on wakeup input (multiplexed with P50 to P53)                                                                                   |

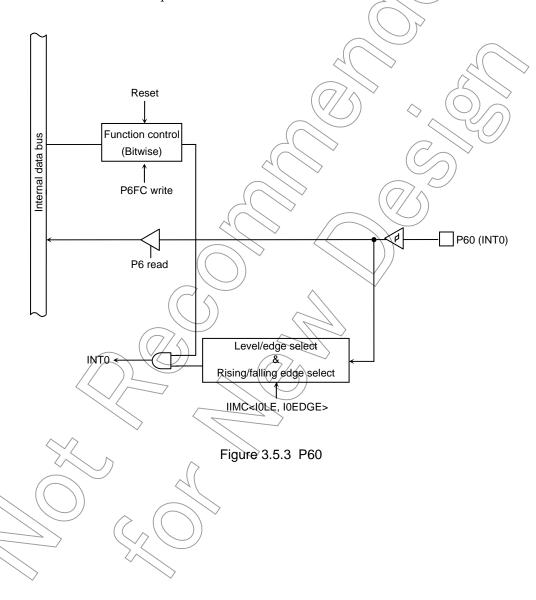

| P60          | 1               | Input    | Port 60: Input port                                                                                                                 |

| INT0         |                 | Input    | Interrupt request pin 0: Programmable as high-level, low-level, rising-edge or falling-edge sensitive                               |

| P61          | 1               | I/O      | Port 61: Input/output port                                                                                                          |

| INT1         |                 | Input    | Interrupt request pin 1: Programmable as high-level, low-level, rising-edge or falling-edge sensitive                               |

| P62          | 1               | Output   | Port 62: Input/output port                                                                                                          |

| ALARM        |                 | Output   | RTC alarm output pin                                                                                                                |

| BOOT         |                 | Input    | Boot mode control pin for flash memory (specifically designed for 91FW40; to be pulled up                                           |

|              |                 | ·        | during the reset period)                                                                                                            |

|              |                 |          | Note: In NORMAL mode, do not input Low level on this pin during the reset period. If Low level is input, boot mode will be entered. |

| P70          | 1               | I/O      | Port 70: Input/output port                                                                                                          |

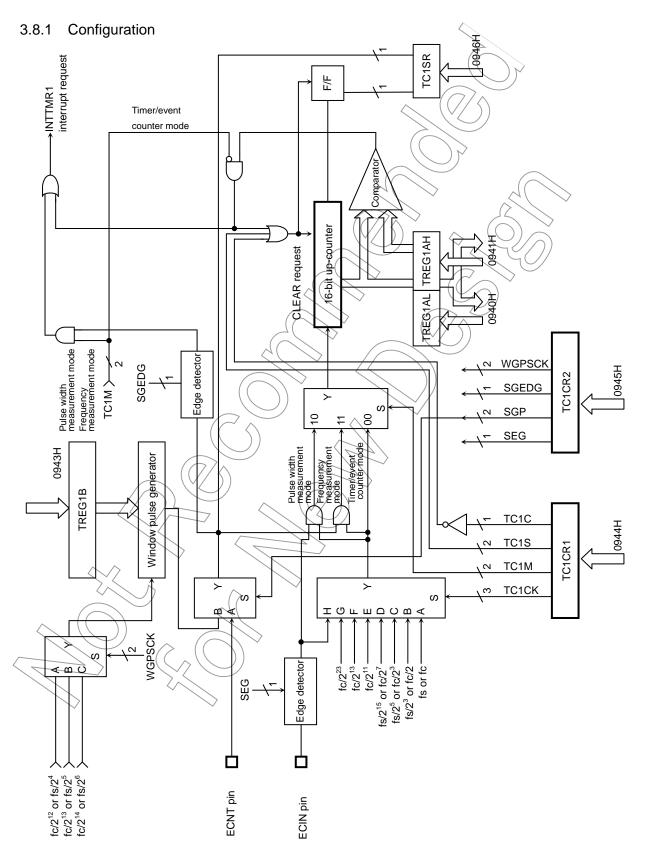

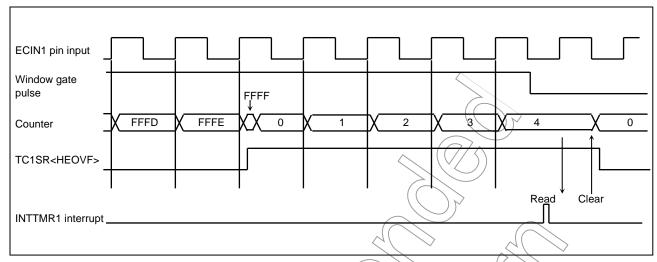

| ECNT1        |                 | Input    | 16-bit timer 1 input: Count control input for 16-bit timer TC1                                                                      |

| P71          | 1               | I/O      | Port 71: Input/output port                                                                                                          |

| ECNT2        |                 | Input    | 16-bit timer 2 input: Count control input for 16-bit timer TC2                                                                      |

| P72          | 1               | I/O      | Port 72: Input/output port                                                                                                          |

| ECNT3        |                 | Input    | 16-bit timer 3 input: Count control input for 16-bit timer TC3                                                                      |

| DVO          |                 | Output   | Divider output pin                                                                                                                  |

| MLDALM       |                 | Output   | Melody/Alarm output pin                                                                                                             |

| P73          | 1               | I/O      | Port 73: (input/output port                                                                                                         |

| ECIN1        | -               | Input    | 16-bit timer 1 input: Count input for 16-bit timer TC1                                                                              |

| P74          | 1               | 1/0/     | Port 74: Input/output port                                                                                                          |

| ECIN2        |                 | _ Input  | 16-bit timer 2 input: Count input for 16-bit timer TC2                                                                              |

| P75          | 1//             | )XO      | Port 75: Input/output port                                                                                                          |

| ECIN3        | //              | Input    | 16-bit timer 3 input: Count input for 16-bit timer TC3                                                                              |

| P80          | 1               | 1/0      | Port 80: Input/output port (large-current port)                                                                                     |

| TC5OUT       |                 | Qutput   | 8-bit timer 5 output: Output pin for 8-bit timer TC5                                                                                |

| . 0000.      |                 | S. Far   | Open-drain output mode by programmable                                                                                              |

| P81          | √/ <sub>1</sub> | I/O      | Port 81: Input/output port (large-current port)                                                                                     |

| TC6OUT       | 7               | Output   | 8-bit timer 6 output: Output pin for 8-bit timer TC6                                                                                |

|              |                 | , Catput | Open-drain output mode by programmable                                                                                              |

| P82          |                 | I/O      | Port 82: Input/output port (large-current port)                                                                                     |

| TC7OUT       | ))              | Output / | 8-bit timer 7 output: Output pin for 8-bit timer TC7                                                                                |

| 10/00/       |                 | Catput ( | Open-drain output mode by programmable                                                                                              |

| P83          | 1               | 1/0      | Port-83: Input/output port (large-current port)                                                                                     |

| TC8OUT       | •               | Output   | 8-bit timer 8 output: Output pin for 8-bit timer TC8                                                                                |

|              |                 | - arpar  | Open-drain output mode by programmable                                                                                              |

| P90          | 1               | I/O      | Port 90: Input/output port                                                                                                          |

| TXD0         | •               | Output   | Serial 0 transmit data                                                                                                              |

|              |                 |          | Open-drain output mode by programmable                                                                                              |

| P91          | 1               | I/O      | Port 91: Input/output port                                                                                                          |

| RXD0         | •               | Input    | Serial 0 receive data                                                                                                               |

| P92          | 1               | I/O      | Port 92: Input/output port                                                                                                          |

| SCLK0        | •               | 1/0      | Serial 0 clock input/output                                                                                                         |

| CTS0         |                 | Input    | Serial 0 data transmit enable (Clear to send)                                                                                       |

| 0100         |                 | iriput   | Ochai o data transmit chable (Olear to Schu)                                                                                        |

Table 2.2.2 Pin Names and Functions (2/2)

| Pin Name       | Number of Pins | I/O           | Function                                                                                                                                  |

|----------------|----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| P93            | 1              | I/O           | Port 93: Input/output port                                                                                                                |

| TXD1           |                | Output        | Serial 1 transmit data                                                                                                                    |

|                |                |               | Open-drain output mode by programmable                                                                                                    |

| P94            | 1              | I/O           | Port 94: Input/output port                                                                                                                |

| RXD1           |                | Input         | Serial 1 receive data                                                                                                                     |

| P95            | 1              | I/O           | Port 95: Input/output port                                                                                                                |

| SCLK1          |                | I/O           | Serial 1 clock input/output                                                                                                               |

| CTS1           |                | Input         | Serial 1 data transmit enable (Clear to send)                                                                                             |

| PA0            | 1              | I/O           | Port A0: Input/output port                                                                                                                |

| TXD2           |                | Output        | Serial 2 transmit data                                                                                                                    |

|                |                |               | Open-drain output mode by programmable                                                                                                    |

| PA1            | 1              | I/O           | Port A1: Input/output port                                                                                                                |

| RXD2           |                | Input         | Serial 2 receive data                                                                                                                     |

| PA2            | 1              | I/O           | Port A2: Input/output port                                                                                                                |

| SCLK2          |                | I/O           | Serial 2 clock input/output                                                                                                               |

| CTS2           |                | Input         | Serial 2 data transmit enable (Clear to send)                                                                                             |

| PA3            | 1              | I/O           | Port 3: Input/output port                                                                                                                 |

| TXD3           |                | Output        | Serial 3 transmit data                                                                                                                    |

|                |                |               | Open-drain output mode by programmable                                                                                                    |

| PA4            | 1              | I/O           | Port A4: Input/output port                                                                                                                |

| RXD3           |                | Input         | Serial 3 receive data                                                                                                                     |

| PA5            | 1              | I/O           | Port A5: Input/output port                                                                                                                |

| SCLK3          |                | I/O           | Serial 3 clock input/output                                                                                                               |

| CTS3           |                | Input         | Serial 3 data transmit enable (Clear to send)                                                                                             |

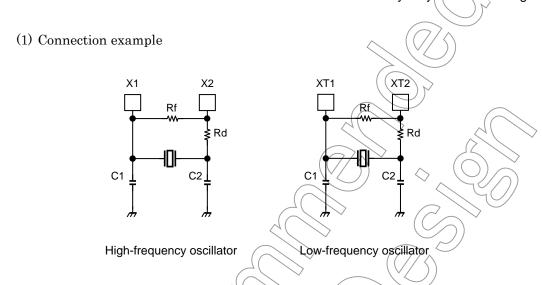

| SEG0 to SEG7   | 8              | Output        | Segment output                                                                                                                            |

| P20 to P27     | 8              | I/O           | Port 2: Input/output port                                                                                                                 |

| SEG8 to SEG15  |                | Output /      | Segment output                                                                                                                            |

| P10 to P17     | 8              | I/O           | Port 1: Input/output port                                                                                                                 |

| SEG16 to SEG23 |                | Output        | Segment output                                                                                                                            |

| P00 to P07     | 8              | (10)/         | Rort 0: Input/output port                                                                                                                 |

| SEG24 to SEG31 |                | Output        | Segment output                                                                                                                            |

| PB0 to PB7     | //8            | 1/0           | Port B: Input/output/port                                                                                                                 |

| SEG32 to SEG39 |                | Output        | Segment output                                                                                                                            |

| C0,C1          | 2              | /             | LCD drive power supply                                                                                                                    |

| V1 to V3       | 3              | $\rightarrow$ | LCD drive power supply                                                                                                                    |

| COM0 to COM3   | 4              |               | Common output                                                                                                                             |

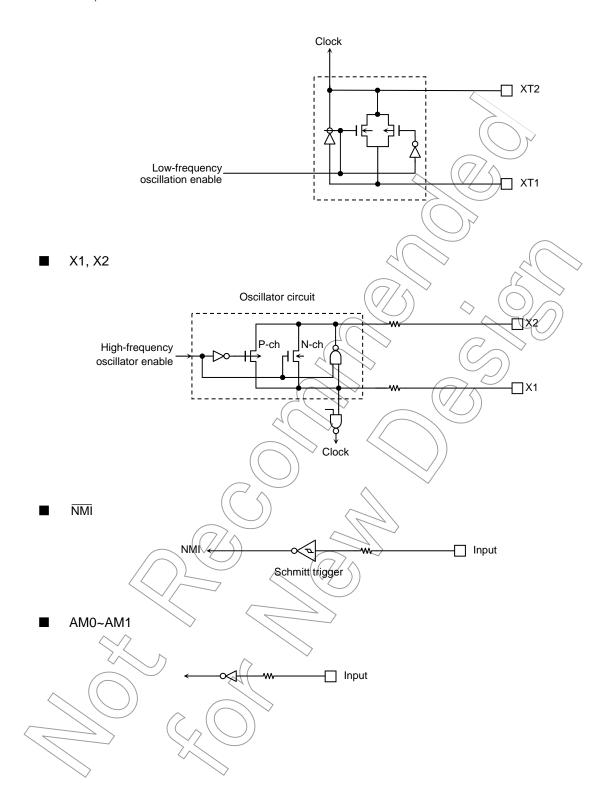

| NMI 💸          | 1              | Input         | Nonmaskable interrupt request pin: Causes an NMI interrupt on the falling edge; programmable to be rising-edge sensitive (Schmitt input). |

| AMO, AM1       | 2              | Input         | Operation mode                                                                                                                            |

|                | ))             |               | Both AM0 and AM1 should be held at logic 1.                                                                                               |

| EMU0           | 1 /            | Output        | This pin should be left open.                                                                                                             |

| EMU1           | 1              | Øutput        | This pin should be left open.                                                                                                             |

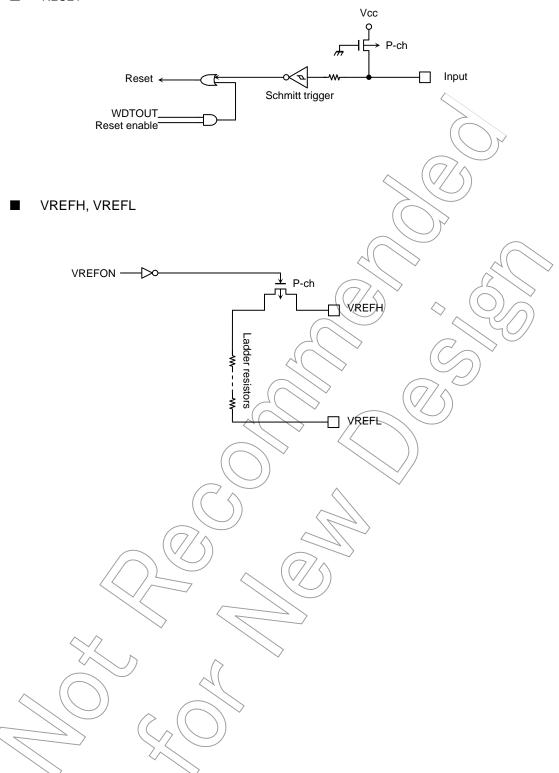

| RESET          | 1              | /Input        | Reset: Initializes the TMP91CW40. (Schmitt input, with pull-up resistor)                                                                  |

| VREFH          | 1              | Input         | Input pin for high reference voltage for the AD converter                                                                                 |

| VREFL          | 1              | Input         | Input pin for low reference voltage for the AD converter                                                                                  |

| AVCC           | 1              |               | Power supply pin for the AD converter                                                                                                     |

| AVSS           | 1              |               | Ground pin for the AD converter (0 V)                                                                                                     |

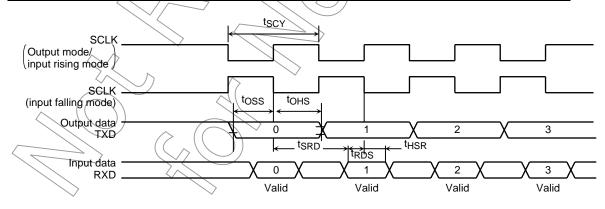

| X1/X2          | 2              | I/O           | Connection pins for a high-frequency oscillator                                                                                           |

| XT1/XT2        | 2              | I/O           | Connection pins for a low-frequency oscillator                                                                                            |

| DVCC           | 4              | ., 0          | Power supply pins (The DVCC pins should be connected to power supply.)                                                                    |

| DVSS           | 4              |               | Ground pins (The DVSS pins should be connected to ground (0 V).)                                                                          |

| טטעם           | +              |               | Stouria pina (The DVOO pina anoula de confidencea la grouna (0 V).)                                                                       |

# 3. Operation

This section describes the functions and basic operation of the TMP91CW40.

# 3.1 CPU

The TMP91CW40 contains a high-performance 16-bit CPU (900/L1 CPU). For a detailed description of the CPU, refer to "TLCS-900/L1 CPU" in the preceding chapter.

Functions unique to the TMP91CW40 not covered in "TLCS-900/L1 CPU" are described below.

# 3.1.1 Reset Operation

To reset the TMP91CW40, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then, set the RESET input to low level for at least 10 system clocks (1µs at 27 MHz). After turning on the power to the TMP91CW40, hold the RESET input at low level for at least 10 system clocks with the power supply voltage within the operating voltage range and the internal high-frequency oscillator oscillating stably.

Reset operation initializes the system clock fsys to fc/2. The CPU performs the following operations as a result of a reset:

• Sets the program counter (PC) according to the reset vector stored at addresses FFFF00H to FFFF02H.

PC<7:0>  $\leftarrow$  Value at address FFFF00H PC<15:8>  $\leftarrow$  Value at address FFFF01H

PC<23:16> ← Value at address FFFF02H

- Sets the stack pointer (XSP) to 100H.

- Sets the <IFF2:0> bits of the status register (SR) to 111 (setting the interrupt level mask register to level 7).

- Sets the MAX bit of the status register (SR) to 1 (selecting maximum mode).

- Clears the <RFP2:0> bits of the status register (SR) to 000 (selecting register bank 0).

After the reset state is released, the CPU starts executing instructions according to the PC. CRU internal registers other than the above are not changed.

The internal I/O peripherals, ports and other pins are initialized as follows upon a reset:

- All internal I/O registers are initialized.

- All port pins, including those multiplexed with internal I/O functions, are configured either as general-purpose inputs or general-purpose outputs.

Note: Reset operation does not affect the contents of the internal RAM or the CPU registers other than PC, SR and XSP.

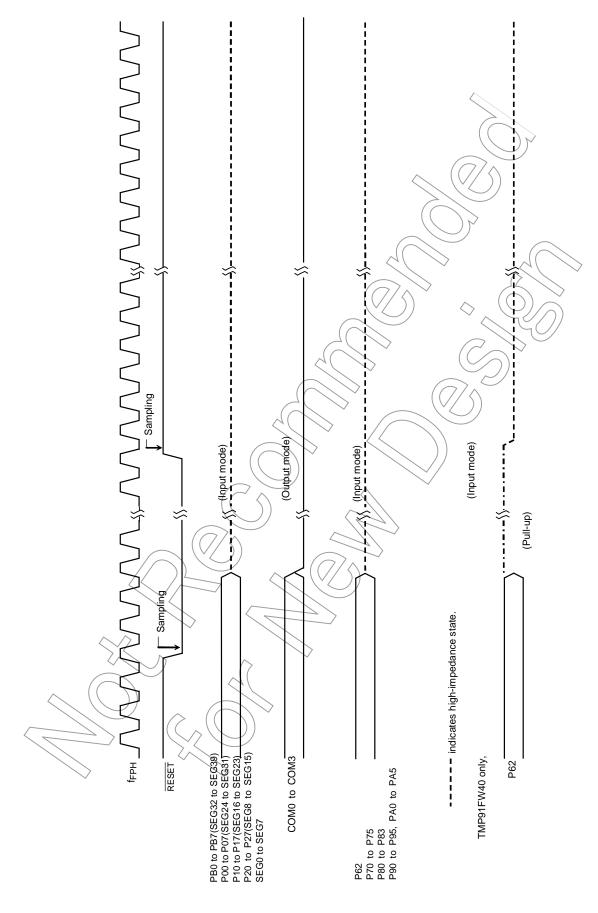

Figure 3.1.1 shows reset timings of the TMP91CW40.

Figure 3.1.1 TMP91CW40 Reset Timings

91CW40-8 2008-09-19

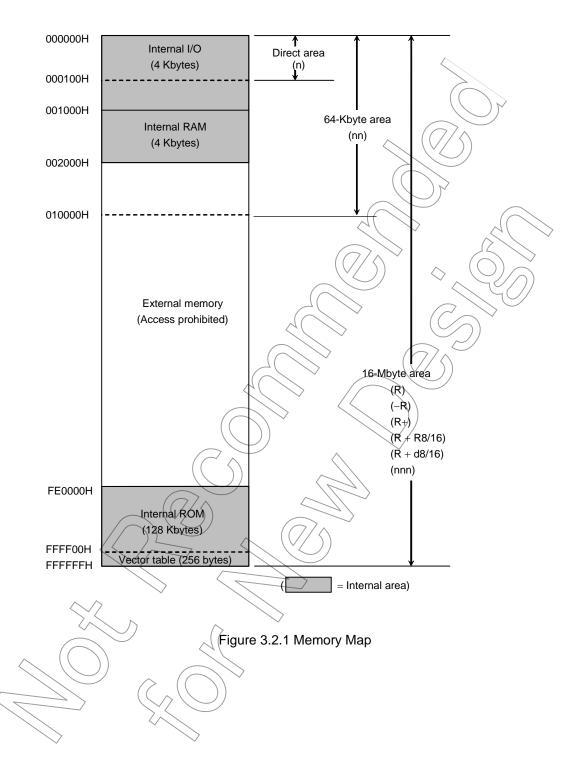

# 3.2 Memory Map

Figure 3.2.1 shows a memory map of the TMP91CW40.

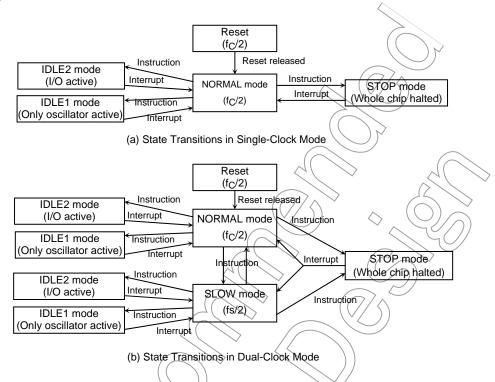

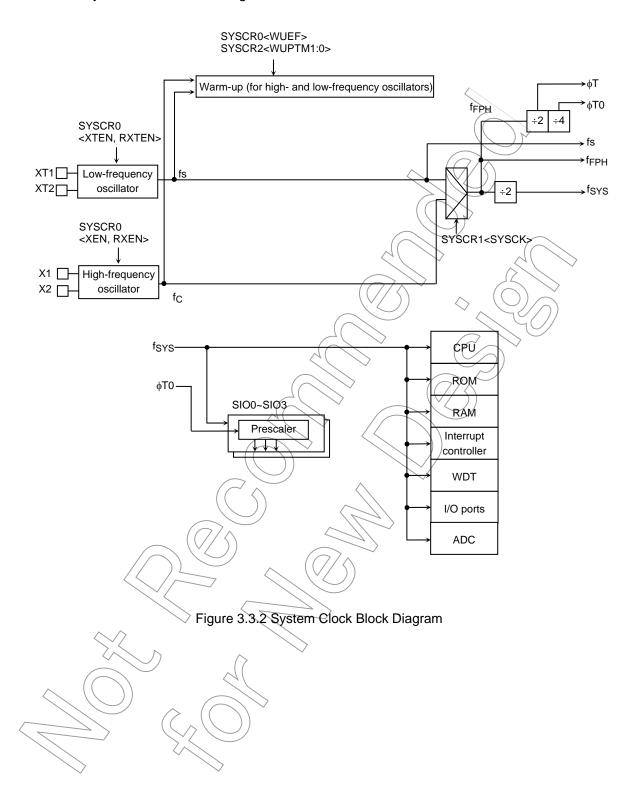

# 3.3 System Clock/Standby Control and Noise Reduction

The TMP91CW40 incorporates clock gear, standby control and noise reduction circuits to minimize power consumption and noise. Single-clock mode (X1 and X2 pins only) and dual-clock mode (X1, X2, XT1, and XT2 pins) are supported.

Figure 3.3.1 shows state transitions in each clock mode.

Figure 3.3.1 State Transitions in Each Operation Mode

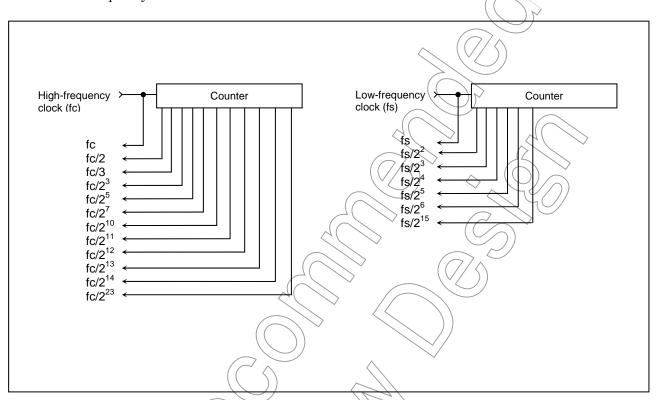

The clock frequency terms used in this document are defined as follows:

fc: Clock frequency supplied via the X1 and X2 pins fs: Clock frequency supplied via the X71 and XT2 pins

ffph: Clock frequency selected by SYSCR1<SYSCK>

fsys: Clock frequency obtained by dividing ffph by two

1/state: One period of fsys

# 3.3.1 System Clock Block Diagram

# 3.3.2 SFRs

|         |                          | 7                                                        | 6                                                       | 5                                                                                              | 4                                                                      | 3                                                                                   | 2                                                                                                   | 1                    | 0                                         |

|---------|--------------------------|----------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------|

| SYSCR0  | Bit symbol               | XEN                                                      | XTEN                                                    | RXEN                                                                                           | RXTEN                                                                  | RSYSCK                                                                              | WUEF                                                                                                | _                    | _                                         |

| (00E0H) | Read/Write               |                                                          |                                                         |                                                                                                | R                                                                      | 2/W                                                                                 |                                                                                                     |                      |                                           |

|         | After reset              | 1                                                        | 0                                                       | 1                                                                                              | 0                                                                      | 0                                                                                   | 0                                                                                                   | 0                    | 0                                         |

|         | Function                 | High-<br>frequency<br>oscillator<br>0: Stop<br>1: Active | Low-<br>frequency<br>oscillator<br>0: Stop<br>1: Active | High-<br>frequency<br>oscillator<br>after release<br>of STOP<br>mode<br>0: Stop<br>1: Active   | Low- frequency oscillator after release of STOP mode 0: Stop 1: Active | Clock selection after release of STOP mode 0: High-frequency 1: Low-frequency       | Warm-up timer (WUP) control 0 write: Don't care 1 write: Start WUP 0 read: WUP finished 1 read: WUP |                      | write 00.                                 |

|         | D: 1 1                   |                                                          |                                                         |                                                                                                |                                                                        |                                                                                     | counting                                                                                            |                      | $\sim$                                    |

| SYSCR1  | Bit symbol<br>Read/Write |                                                          |                                                         |                                                                                                |                                                                        | (sysck)                                                                             | - 🗸                                                                                                 | W                    | $\rightarrow$ ) -                         |

| (00E1H) |                          | //                                                       |                                                         |                                                                                                | $\mathcal{A}$                                                          | 0                                                                                   | i e                                                                                                 | ////                 | //                                        |

|         | After reset<br>Function  |                                                          |                                                         |                                                                                                |                                                                        | System                                                                              | 0                                                                                                   | Q<br>Always write 00 | 0                                         |

|         |                          |                                                          |                                                         |                                                                                                |                                                                        | clock<br>selection<br>0: High-<br>frequency<br>(fc)<br>1: Low-<br>frequency<br>(fs) |                                                                                                     |                      |                                           |

| SYSCR2  | Bit symbol               |                                                          | -(                                                      | WUPTM1                                                                                         | WUPTM0                                                                 | HALTM1                                                                              | HALTM0                                                                                              |                      | DRVE                                      |

| (00E2H) | Read/Write               |                                                          | R/W                                                     | )R/W                                                                                           | R/W /                                                                  | R/W                                                                                 | R/W                                                                                                 |                      | R/W                                       |

|         | After reset              |                                                          | 6                                                       | 1                                                                                              | 0                                                                      |                                                                                     | 1                                                                                                   |                      | 0                                         |

|         | Function                 |                                                          | Always write                                            | Oscillator war<br>00: Reserved<br>01: 2 <sup>8</sup> /input fr<br>10: 2 <sup>14</sup> /input f | equency                                                                | HALT mode s<br>00: Reserved<br>01: STOP mo<br>10: IDLE1 mo<br>11: IDLE2 mo          | ode<br>ode                                                                                          |                      | 1: Pins are<br>driven in<br>STOP<br>mode. |

| SYSCR3  | Bit symbol               |                                                          | /                                                       | $\mathcal{M}$                                                                                  |                                                                        |                                                                                     |                                                                                                     |                      | LCDCKMOD                                  |

| (00E5H) | Read/Write               |                                                          |                                                         | 7                                                                                              |                                                                        |                                                                                     |                                                                                                     |                      | R/W                                       |

| /       | After reset              | $\mathcal{T}_{\mathcal{A}}$                              |                                                         |                                                                                                |                                                                        |                                                                                     |                                                                                                     |                      | 0                                         |

| <       | Function                 |                                                          |                                                         |                                                                                                |                                                                        |                                                                                     |                                                                                                     |                      | LCD clock 0: fc 1: fs                     |

|         | 7/                       |                                                          | $\sim$                                                  | ))                                                                                             |                                                                        |                                                                                     |                                                                                                     |                      |                                           |

Note: Bits 7 to 4 of the SYSCR1 and bits 7 and 1 of the SYSCR2 are read as undefined.

Figure 3.3.3 SFRs for the System Clock

|                   |                                            | 7                                                                                                   | 6               | 5                  | 4               | 3               | 2                            | 1                                                            | 0                                                            |

|-------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|--------------------|-----------------|-----------------|------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|

| EMCCR0            | Bit symbol                                 | PROTECT                                                                                             | -               | ı                  | ı               | ı               | EXTIN                        | DRVOSCH                                                      | DRVOSCL                                                      |

| (00E3H)           | Read/Write                                 | R                                                                                                   | R/W             | R/W                | R/W             | R/W             | R/W                          | R/W                                                          | R/W                                                          |

|                   | After reset                                | 0                                                                                                   | 0               | 1                  | 0               | 0               | 0                            | 1                                                            | 1                                                            |

|                   | Function                                   | Protection<br>flag<br>0: OFF<br>1: ON                                                               | Always write 0. | Always write<br>1. | Always write 0. | Always write 0. | 1: External clock used as fc | fc oscillator<br>drive<br>capability<br>1: Normal<br>0: Weak | fs oscillator<br>drive<br>capability<br>1: Normal<br>0: Weak |

| EMCCR1<br>(00E4H) | Bit symbol Read/Write After reset Function | bol //rite Writing 1FH disables protection.  Set Writing a value other than 1FH enables protection. |                 |                    |                 |                 |                              |                                                              |                                                              |

Note: In case restarting the oscillator in the stop oscillation state (e.g. Restart the oscillator in STOP mode), set EMCCR0<br/>DRVOSCH>, <DRVOSCL>="1".

# 3.3.3 System Clock Control Unit

The system clock control unit generates system clock pulses (fsys) that are supplied to the CPU core and internal I/O. It accepts either fc or fs clock pulses generated by the high-frequency or low-frequency oscillator, respectively. SYSCR1<SYSCK> is used to select the high-frequency or low-frequency oscillator. SYSCR0<XEN> and <XTEN> are used to enable and disable the high-frequency and low-frequency oscillators, respectively, so that power consumption can be reduced.

A system reset initializes <XEN> to 1, <XTEN> to 0 and <SYSCK> to 0, setting the system clock f<sub>SYS</sub> to fc/2. For example, if a 27 MHz resonator is connected between the X1 and X2 pins, the f<sub>SYS</sub> clock operates at 13.5 MHz.

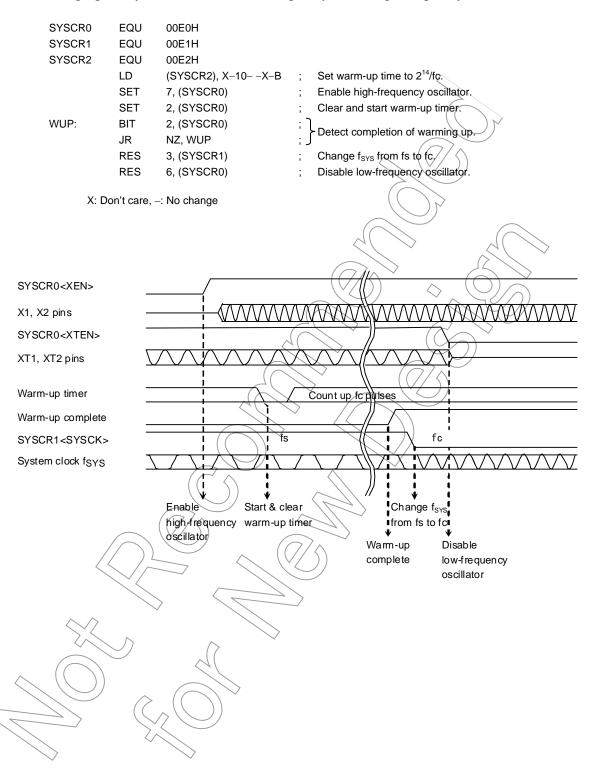

# (1) Switching between NORMAL mode and SLOW mode

A warm-up timer is provided to ensure stable oscillation of the resonator connected between the X1 and X2 pins or between the XT1 and XT2 pins before switching the system clock frequency. This warm-up time can be selected by SYSCR2<WUPTM1:0> according to the properties of the resonator to be used. SYSCR0<WUEF> is used to start the warm-up timer and to check whether or not the warm-up time has elapsed. For how to program the warm-up timer, refer to examples 1 and 2 on the pages that follow.

Table 3.3.1 shows the warm-up times for changing the system clock frequency.

Note 1: If the oscillator to be used has stable oscillation, no warm-up time is needed.

Note 2: Since the warm-up timer is operated by an oscillation clock, warm-up times may include some errors if there are fluctuations in oscillation frequency.

Table 3.3.1 Warm-Up Times (for changing the system clock frequency)

|                                                      |                              | \ \ \                      | _     |

|------------------------------------------------------|------------------------------|----------------------------|-------|

| Warm-Up Time Setting<br>SYSCR2 <wuptm1:0></wuptm1:0> | Changing to NORMAL Mode (fc) | Changing to SLOW Mode (fs) |       |

| 01 (28/ oscillation frequency)                       | 9.5 [μs]                     | 7.8 [ms]                   | at fo |

| 10 (2 <sup>14</sup> /oscillation frequency)          | 0.607 [ms]                   | 500 [ms]                   | fs    |

| 11 (2 <sup>16</sup> /oscillation frequency)          | 2.427 [ms]                   | 2000 [ms]                  | 1 .0  |

Example 1

Changing the system clock from high-frequency (fc) to low-frequency (fs)  $\,$

| SYSCR0<br>SYSCR1<br>SYSCR2    | EQU<br>EQU<br>EQU<br>LD               | 00E0H<br>00E1H<br>00E2H<br>(SYSCR2), X–11– –X–B ; Set warm-up time to 2 <sup>16</sup> /fş.                                                                                                                                                        |

|-------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WUP:                          | SET<br>SET<br>BIT<br>JR<br>SET<br>RES | 6, (SYSCR0) ; Enable low-frequency oscillator. 2, (SYSCR0) ; Clear and start warm-up timer. 2, (SYSCR0) ; Detect completion of warming up. 3, (SYSCR1) ; Change f <sub>SYS</sub> from fc to (s.) 7, (SYSCR0) ; Disable high-frequency oscillator. |

| X: Don't care, -              | -: No ch                              | ange                                                                                                                                                                                                                                              |

|                               |                                       |                                                                                                                                                                                                                                                   |

| SYSCR0 <xen></xen>            |                                       |                                                                                                                                                                                                                                                   |

| X1, X2 pins                   |                                       |                                                                                                                                                                                                                                                   |

| SYSCR0 <xten></xten>          |                                       |                                                                                                                                                                                                                                                   |

| XT1, XT2 pins                 |                                       |                                                                                                                                                                                                                                                   |

| Warm-up timer                 |                                       | Count up is pulses                                                                                                                                                                                                                                |

| Warm-up complete              | )                                     |                                                                                                                                                                                                                                                   |

| SYSCR1 <sysck></sysck>        | •                                     | fc                                                                                                                                                                                                                                                |

| System clock f <sub>SYS</sub> |                                       |                                                                                                                                                                                                                                                   |

| 4                             |                                       | Enable   Clear & start   Change f <sub>SYS</sub>   Disable   high-frequency   oscillator   warm-up timer   warm-up complete                                                                                                                       |

|                               | <u>)</u>                              |                                                                                                                                                                                                                                                   |

Example 2

Changing the system clock from low-frequency (fs) to high-frequency (fc)

#### 3.3.4 Prescaler Clock Control Unit

The internal I/O functions (SIO0 to SIO3) are provided with a clock prescaler. The prescaler clock sources  $\phi T$  and  $\phi T0$  are f<sub>FPH</sub>/2 and f<sub>FPH</sub>/4, respectively.

#### 3.3.5 Noise Reduction Circuits

The TMP91CW40 incorporates circuits providing the following features to reduce electromagnetic interference (EMI) and electromagnetic susceptibility (EMS):

- (1) Reducing drive capability of the high-frequency oscillator

- (2) Reducing drive capability of the low-frequency oscillator

- (3) Canceling double-drive operation of the high-frequency oscillator

- (4) Preventing software or system lockups using a protection register

These features are specified using the EMCCRO and EMCCR1 registers, as described below.

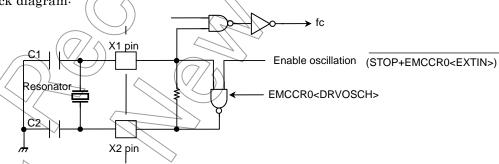

(1) Reducing drive capability of the high-frequency oscillator

# Purpose:

To suppress noise generated by the high-frequency oscillator and to reduce power consumption of the high-frequency oscillator when an external resonator is connected.

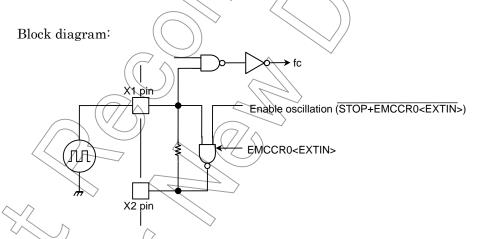

Block diagram:

Description:

2008-09-19

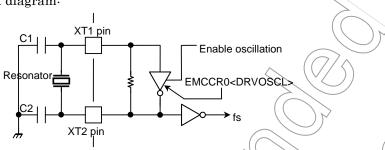

# (2) Reducing drive capability of the low-frequency oscillator

# Purpose:

To suppress noise generated by the low-frequency oscillator and to reduce power consumption of the low-frequency oscillator when an external resonator is connected.

# Description:

Setting the <DRVOSCL> bit of the EMCCRO register to 0 reduces the low-frequency oscillator's drive capability. A system reset initializes the <DRVOSCL> bit to 1.

# (3) Canceling double-drive operation of the high-frequency oscillator

#### Purpose:

To prevent malfunction due to noise coming through the X2 pin that is open when an external oscillator is used, with double drive operation not required.

#### Description:

Setting the **EXTIN** bit of the EMCCR0 register to 1 causes the high-frequency oscillator to stop oscillation with the X2 pin driven high.

A system reset initializes the <EXTIN> bit to 0.

Note: Do not write EMCCR0<EXTIN> = "1" when using external resonator.

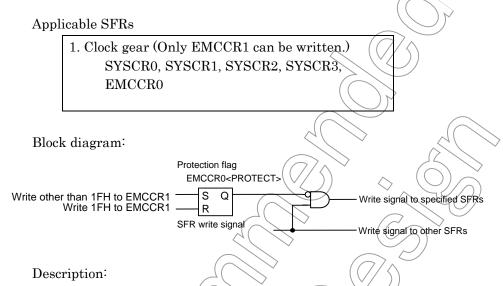

(4) Preventing software or system lockups using a protection register

# Purpose:

To prevent software or system lockups that may occur due to incoming noise.

Applying protection causes specified SFRs to be write-protected, thus preventing the system recovery routine from becoming unfetchable, for example, if the system clock stops or a memory control register (CS/WAIT controller) is modified.

Writing any code other than 1FH to the EMCCR1 register enables protection, preventing specified SFRs from being written.

Writing 1FH to the EMCCR1 register cancels protection. The state of protection can be determined by reading the <PROTECT> bit of the EMCCR0.

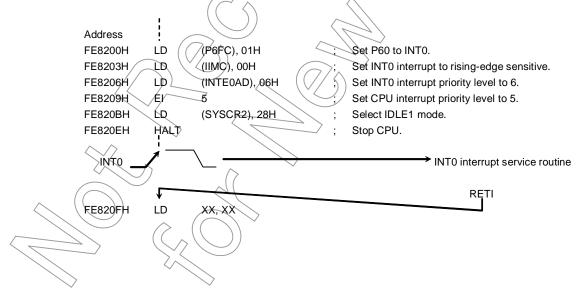

# 3.3.6 Standby Control

# (1) HALT mode

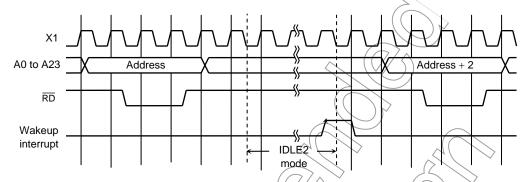

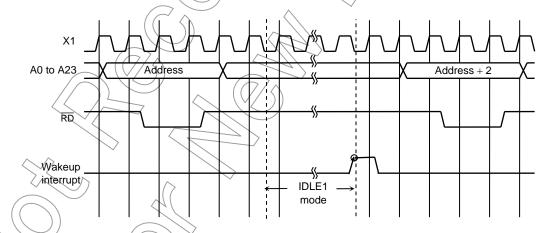

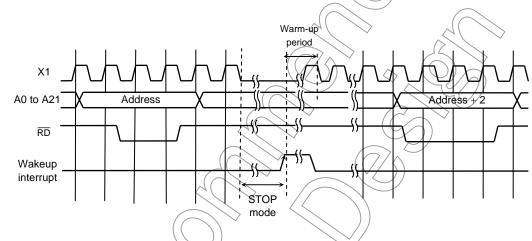

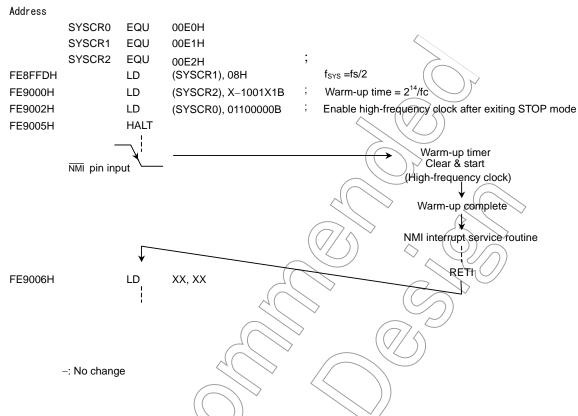

Executing the HALT instruction causes the TMP91CW40 to enter one of the HALT modes–IDLE2, IDLE1 or STOP–as specified by the SYSCR2 <HALTM1:0> bits.

The characteristics of IDLE2, IDLE1 and STOP modes are as follows:

a. IDLE2: The CPU stops.

Each internal I/O can be selectively enabled and disabled through use of a register bit in an SFR, as shown in Table 3.3.2.

Table 3.3.2 IDLE2 Mode Register Settings

| Internal I/O | SFR                   |

|--------------|-----------------------|

| SIO0         | SC0MOD1<12S0>         |

| SIO1         | SC1MOD1 <i2s1></i2s1> |

| SIO2         | SC2MOD1<12S2>         |

| SIO3         | SC3MOD1<12S3>         |

| AD converter | ADMOD1 <i2ad></i2ad>  |

| WDT          | WDMOD<12WDT>          |

|              |                       |

- b. IDLE1: Only the oscillator, RTC(real-time clock) and MLD are operational.

- c. STOP: The whole TMP91CW40 stops.

Table 3.3.3 shows the operation of each circuit block in HALT modes.

Table 3.3.3 TMP91CW40 Circuit Blocks in HALT Modes

|          | HALT mode                    | IDLE2                                    | IDLE1             | STOP            |  |

|----------|------------------------------|------------------------------------------|-------------------|-----------------|--|

|          | SYSCR2 <haltm1:0></haltm1:0> | 10                                       | 01                |                 |  |

|          | CPU                          |                                          | OFF               |                 |  |

|          | I/O ports                    | Holding the states when the HAL executed | T instruction was | See Table 3.3.6 |  |

| 송        | TC1 to TC3, TC5 to TC8       | ON                                       | OFF               |                 |  |

| block    | SIO0 to SIO3                 |                                          |                   |                 |  |

| Circuit  | AD converter                 | Selectable programmatically on           |                   |                 |  |

| Cir      | WDT                          | a block-by-block basis                   |                   |                 |  |

|          | RTC, MLD                     | ON                                       |                   |                 |  |

| $\wedge$ | LCDD                         | ON                                       |                   |                 |  |

|          | Interrupt controller         | ON                                       | _                 |                 |  |

# (2) Wakeup signaling

There are two ways to exit a HALT mode: An interrupt request or reset signal. Availability of wakeup signaling depends on the settings of the interrupt mask level bits, <IFF2:0>, of the CPU status register (SR) and the current HALT mode (see Table 3.3.4).

# • Wakeup via interrupt signaling

The operation upon return from a HALT mode varies, depending on the interrupt priority level programmed before executing the HALT instruction. If the interrupt priority level is greater than or equal to the processor's interrupt mask level, execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the HALT instruction. If the interrupt priority level is less than the processor's interrupt mask level, the HALT mode is not terminated. (Nonmaskable interrupts are always serviced upon return from a HALT mode, regardless of the current interrupt mask level.)

Only INT0, INT1, KWI0 to KWI3, INTRTC and INTALM0 to INTALM4 interrupts can, however, terminate a HALT mode even if the interrupt priority level is less than the processor's interrupt mask level. In that case, program execution resumes with the instruction immediately following the HALT instruction without executing the interrupt service routine. (The interrupt request flag remains set.)

# Wakeup via reset signaling

Reset signaling always brings the TMP91CW40 out of any HALT mode. A wakeup from STOP mode must allow sufficient time for the oscillator to restart and stabilize (see Table 3.3.5).

A reset does not affect the contents of the internal RAM, but initializes everything else, whereas an interrupt preserves all internal states that were in effect before the HALT mode was entered.

|           | isable of the result of the re |                                    |                                  |          |             |                                                    |            |             |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|----------|-------------|----------------------------------------------------|------------|-------------|--|--|--|

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt Masking                  | Unmasked I<br>(Request level) ≥  | •        | vel)        | Masked Interrupt<br>(Request level) < (Mask level) |            |             |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HALT mode                          | Programmable IDLE2               | IDLE1    | STOP        | Programmable IDLE2                                 | IDLE1      | STOP        |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NMI                                | <b>*</b>                         | <b>*</b> | <b>♦</b> *1 | -                                                  | -          | -           |  |  |  |

| es        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTWD                              | <b>*</b>                         | ×        | ×           | <b>\_</b> -                                        | -          | -           |  |  |  |

| sources   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INT0,INT1, KWI0 to KWI3 Note 1)    | •                                | •        | <b>*</b> 1  | A                                                  | $\Diamond$ | <b>♦</b> *1 |  |  |  |

|           | pts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTALM0 to INTALM4                 | •                                | •        | ×           |                                                    | $\Diamond$ | ×           |  |  |  |

| signaling | nterrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INTRTC                             | •                                | •        | ×           | (V) ) Y                                            | $\Diamond$ | ×           |  |  |  |

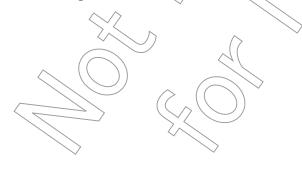

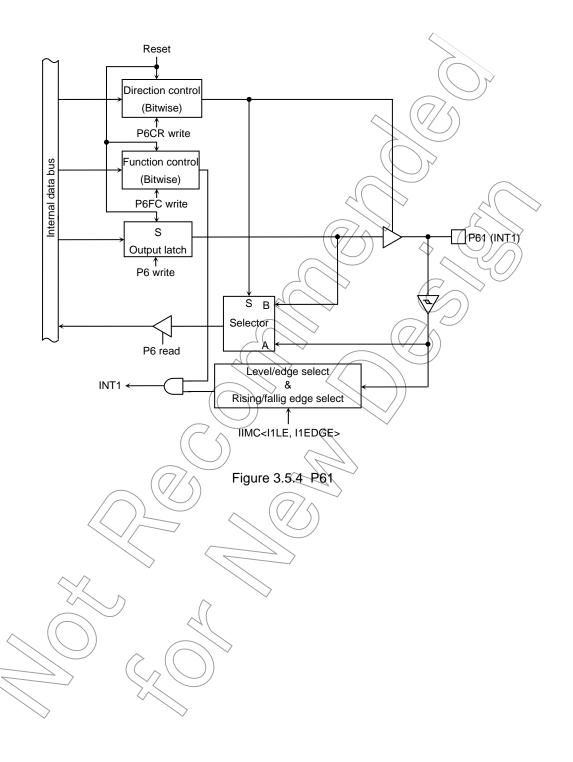

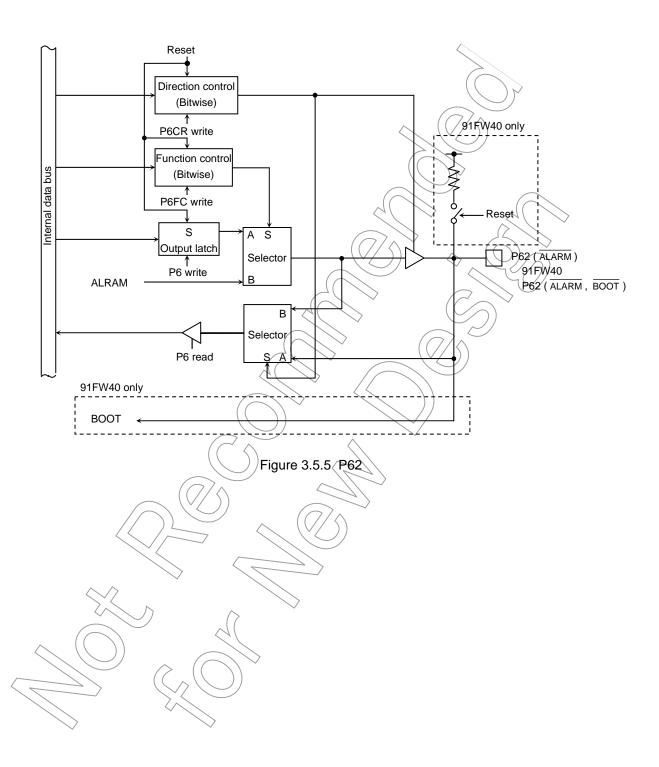

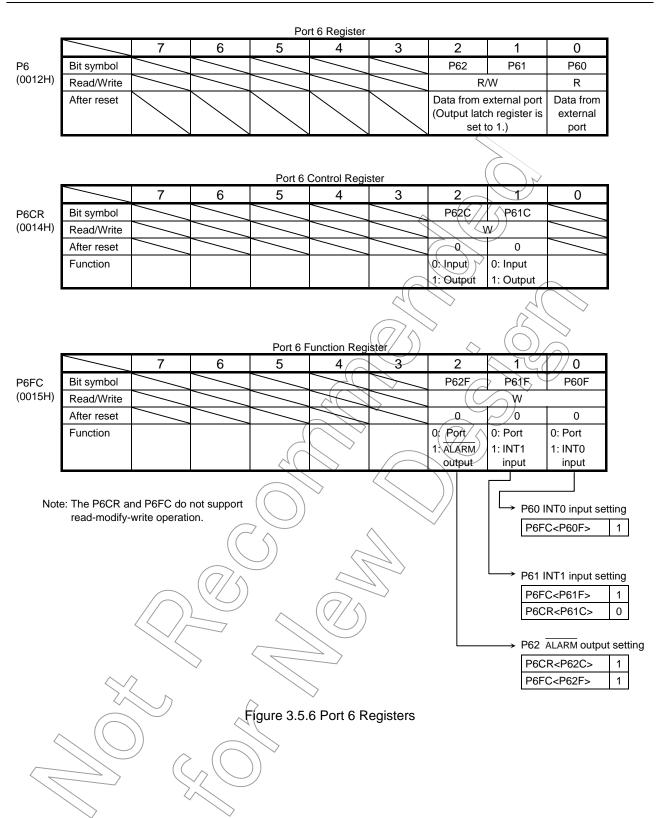

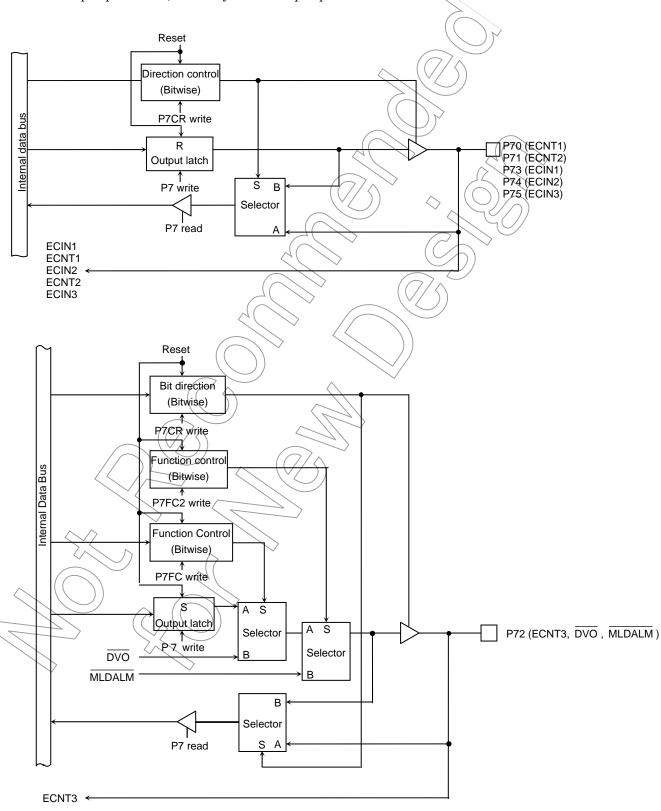

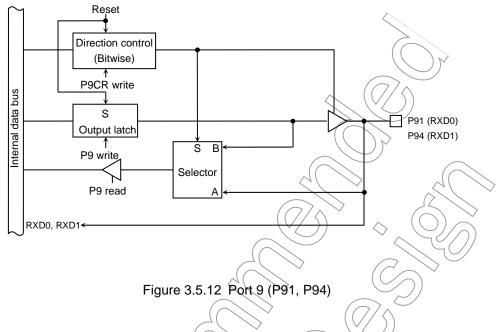

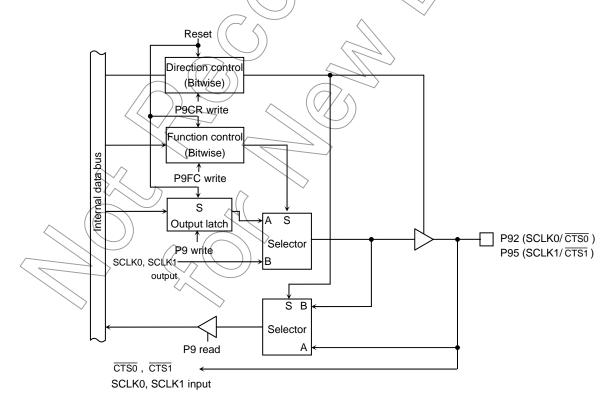

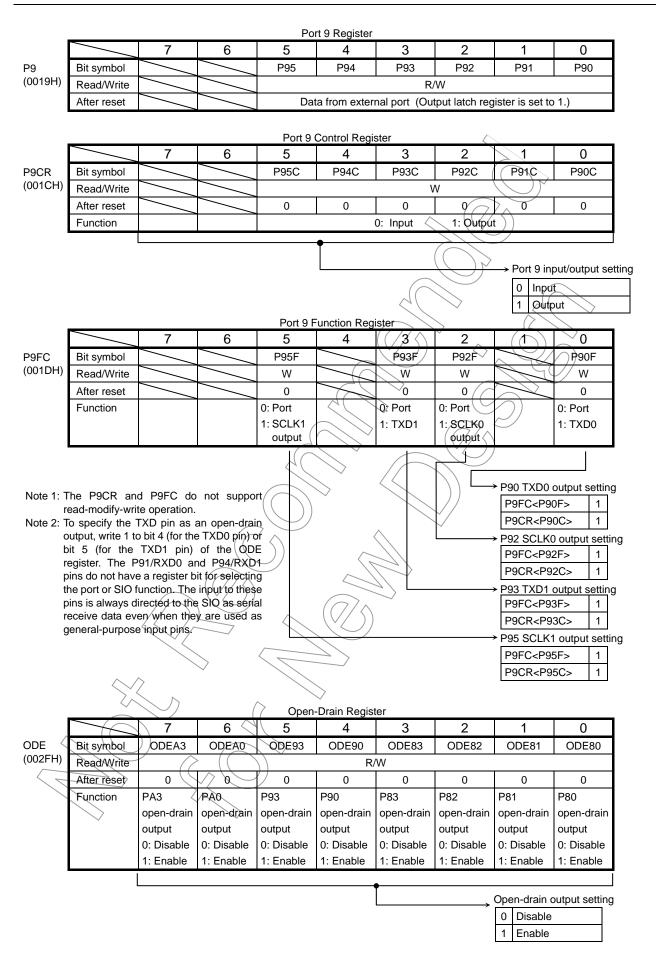

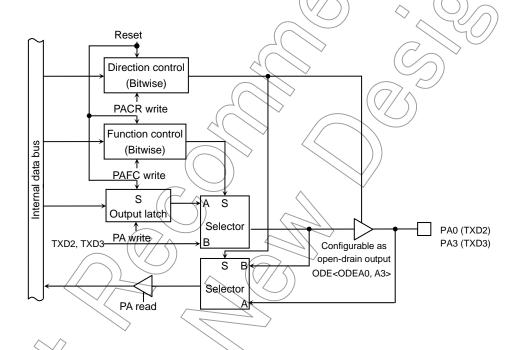

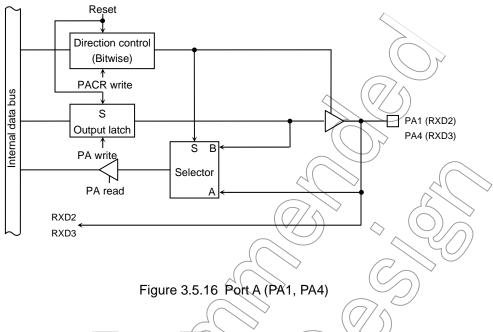

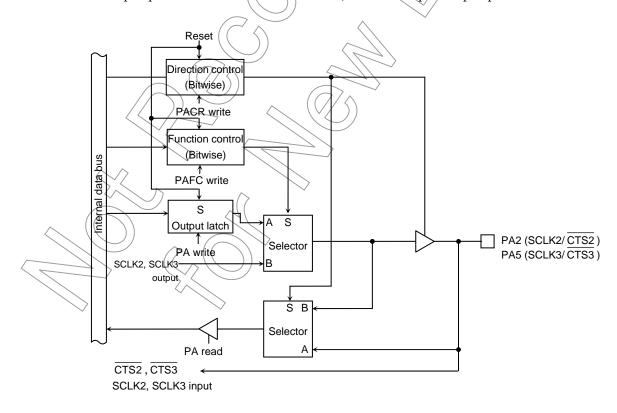

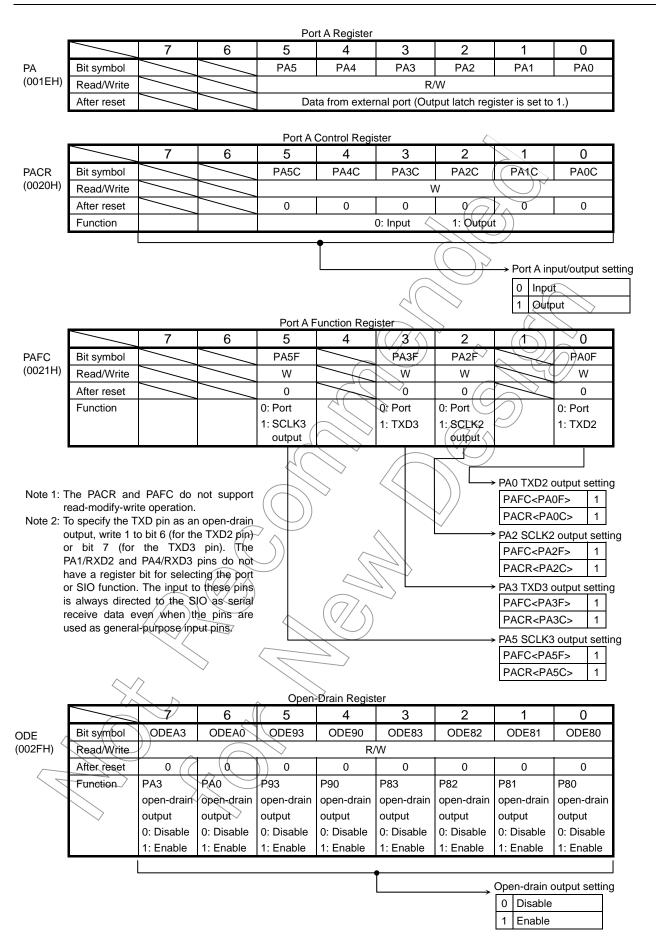

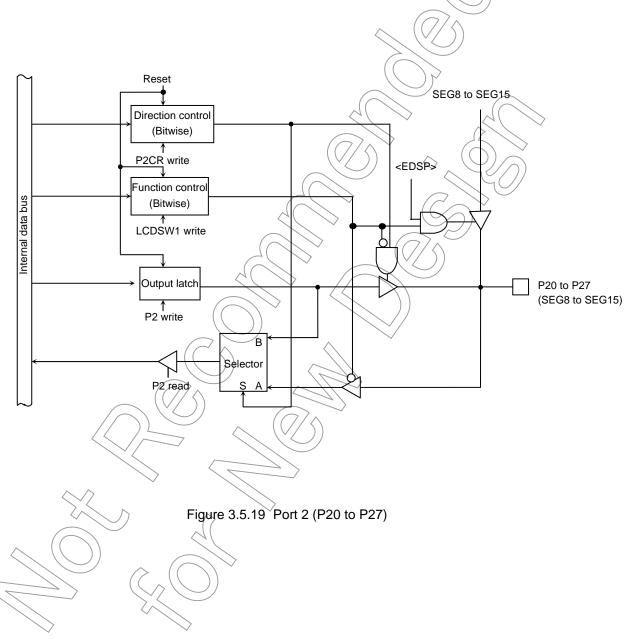

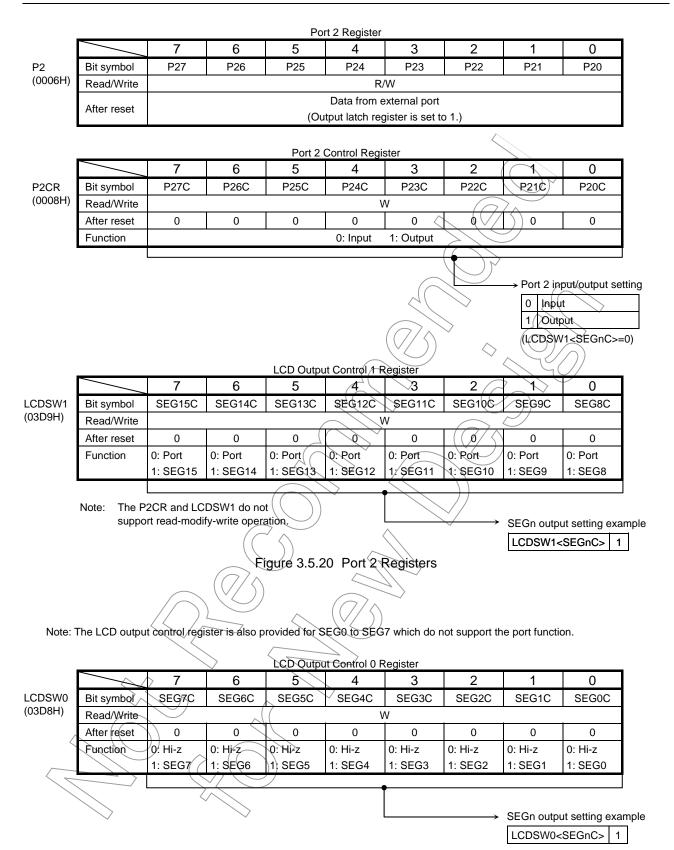

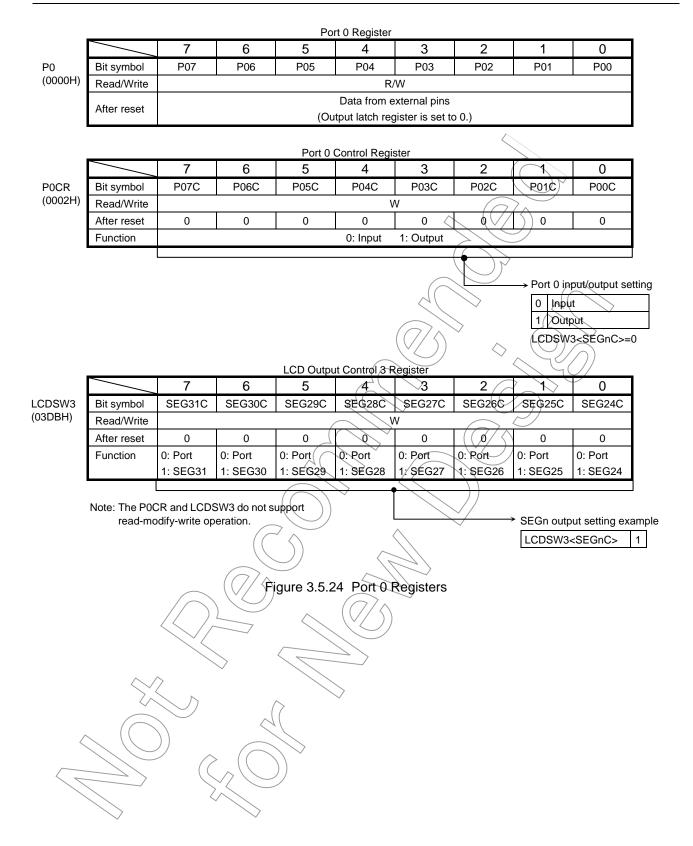

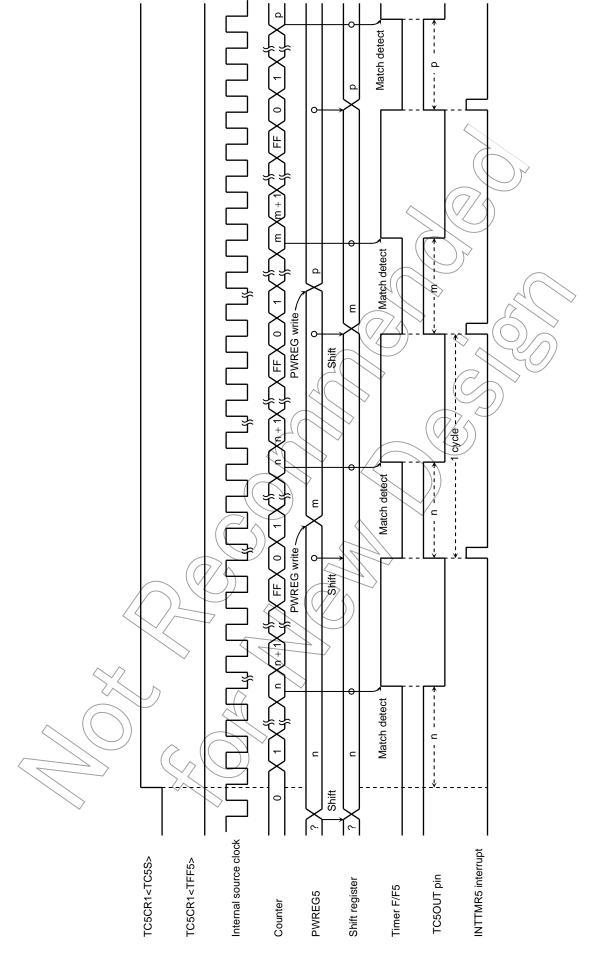

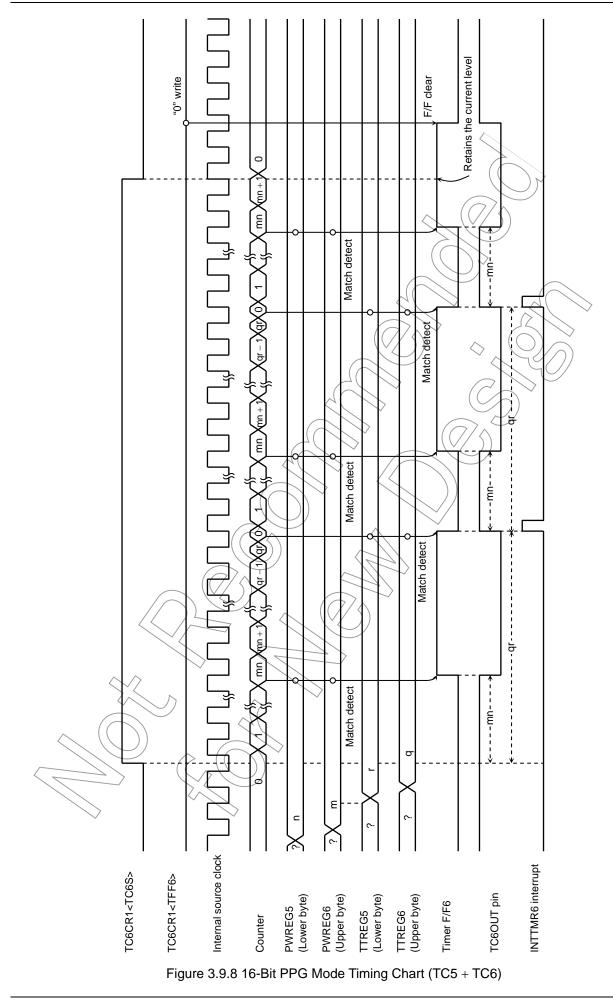

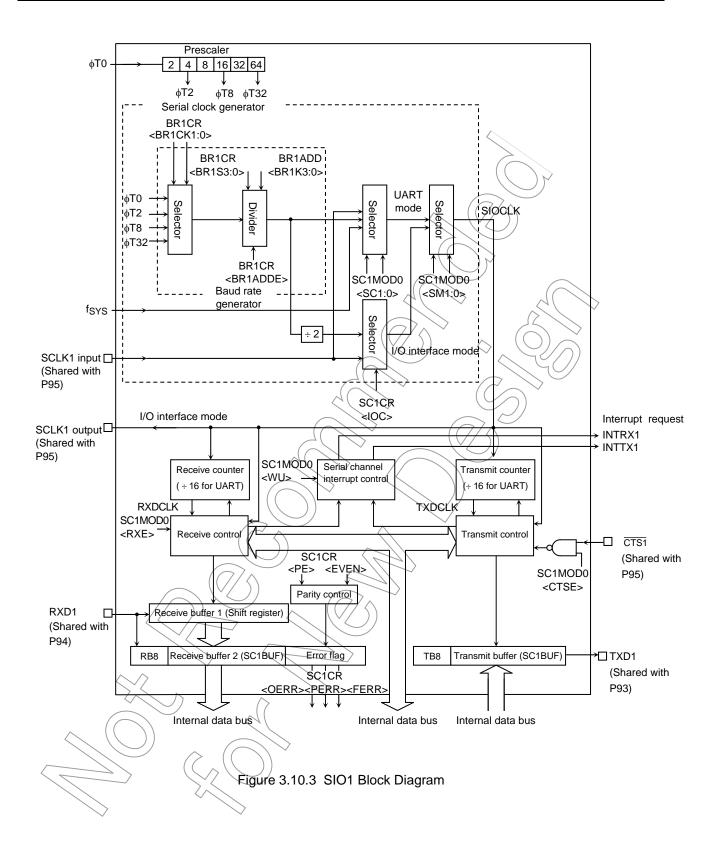

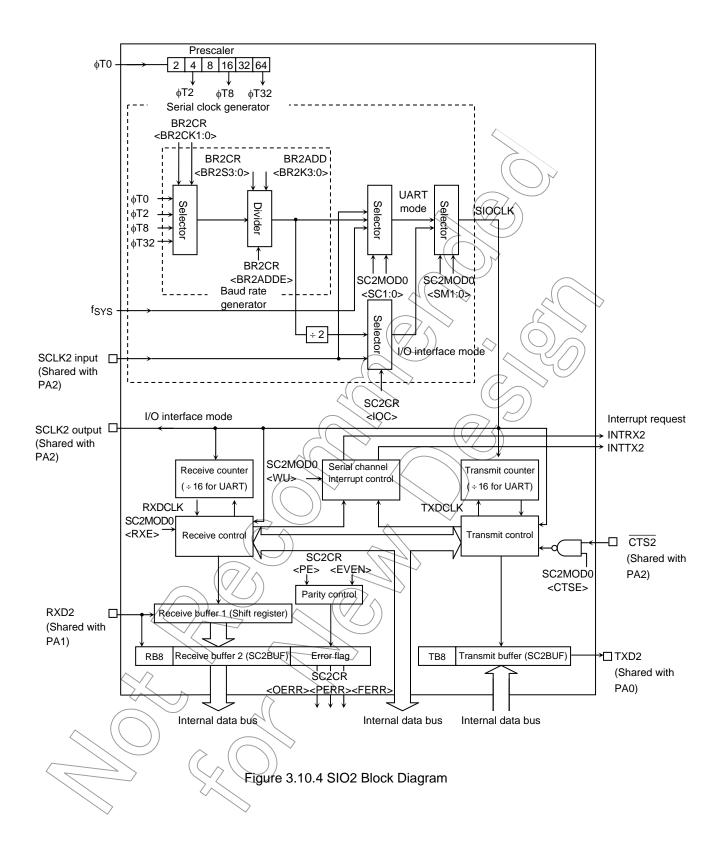

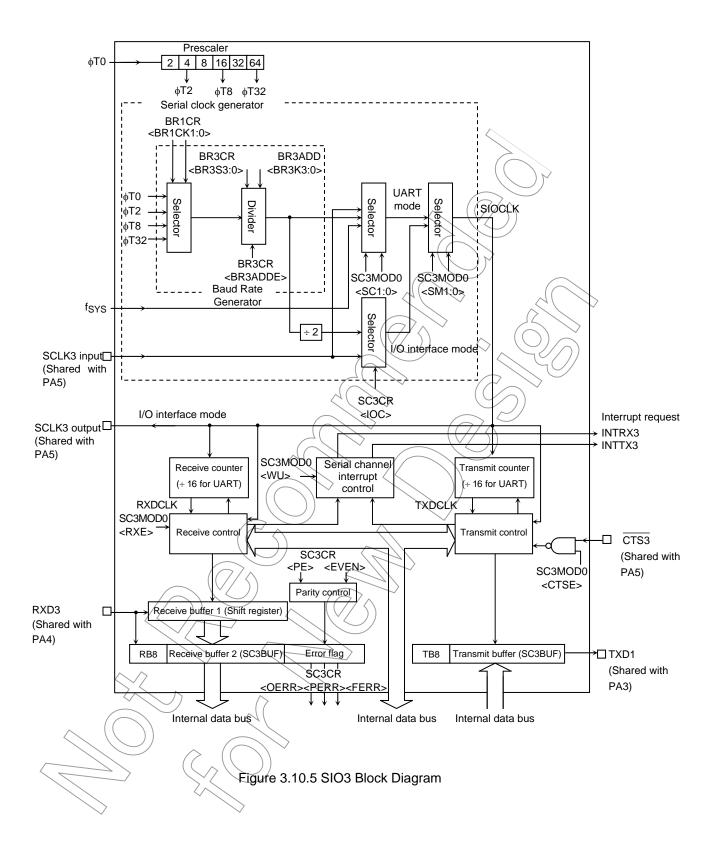

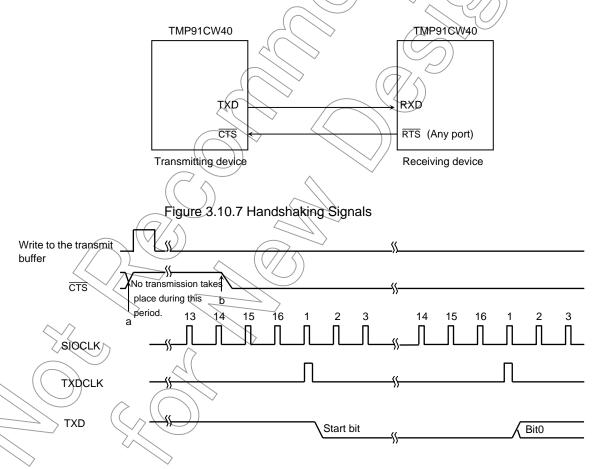

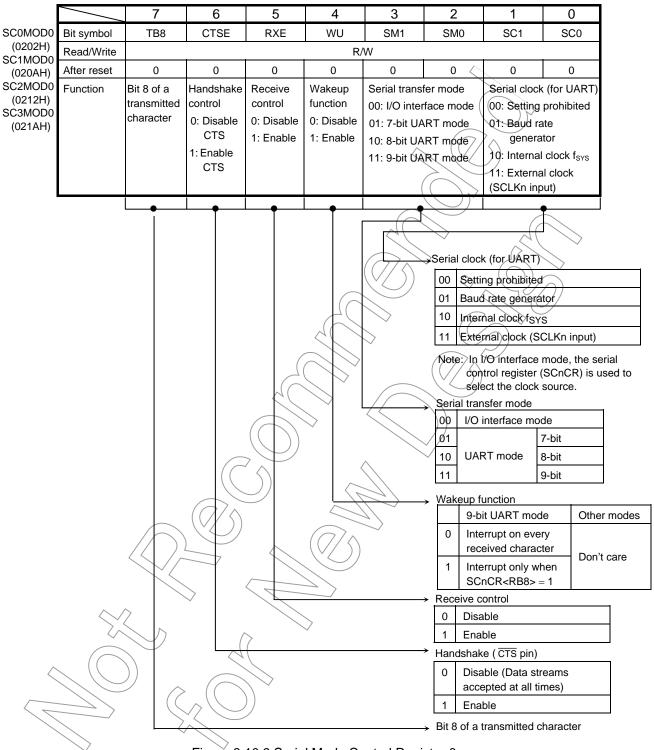

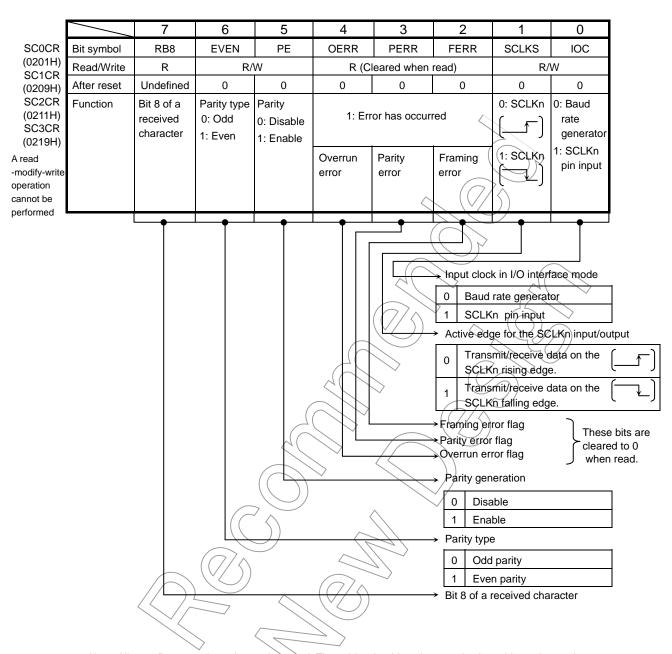

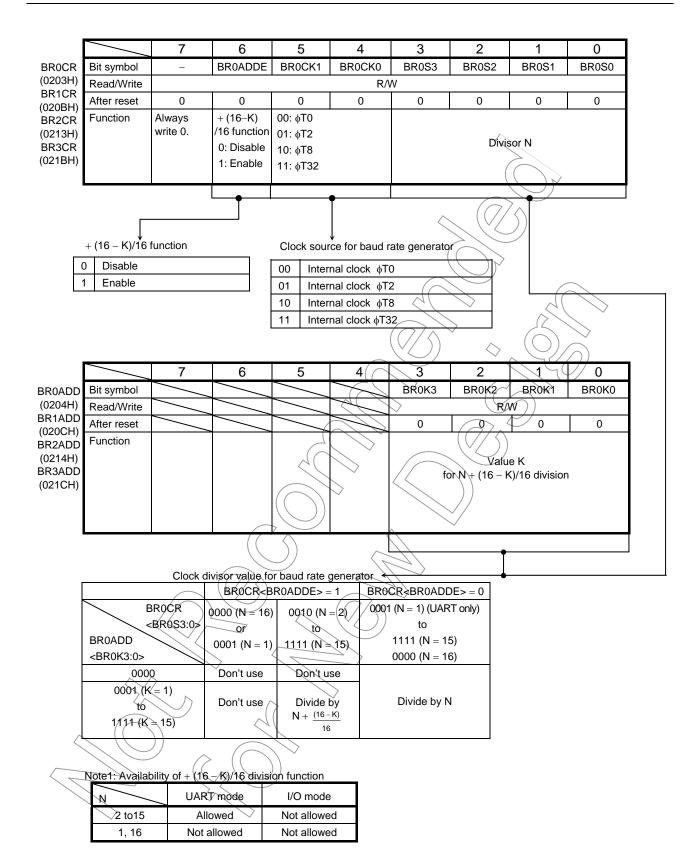

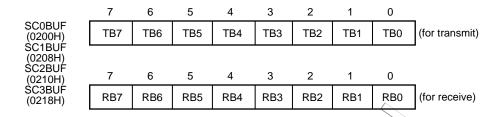

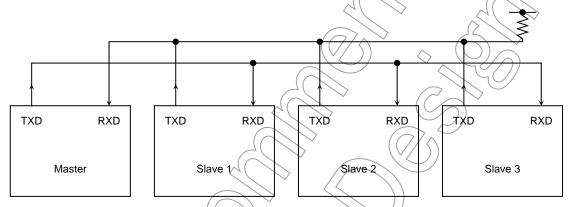

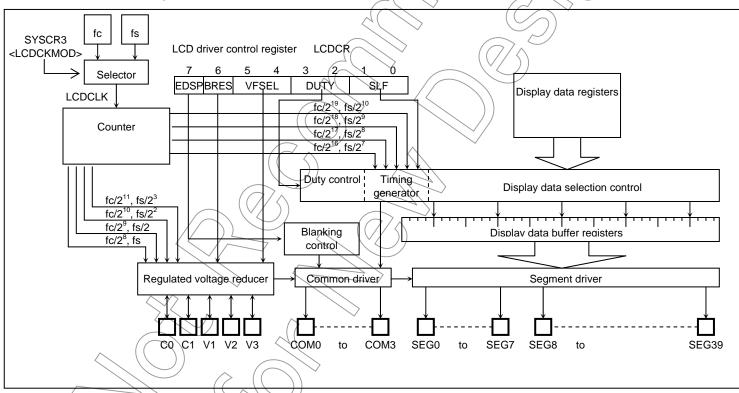

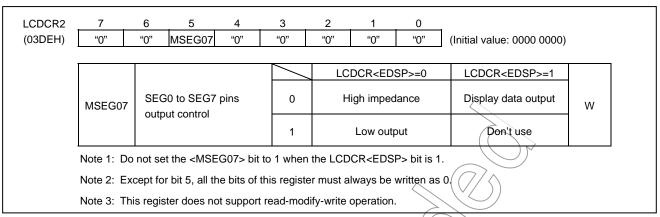

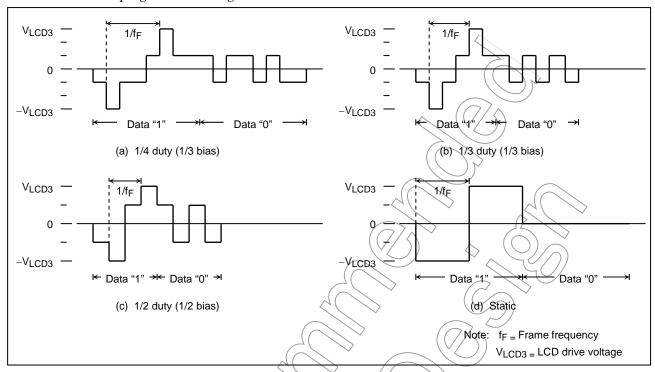

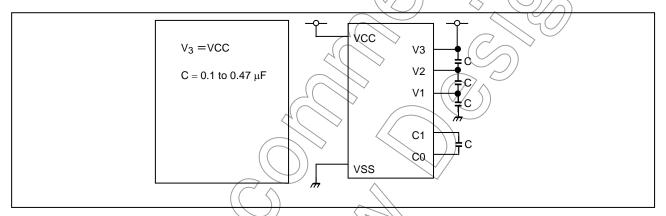

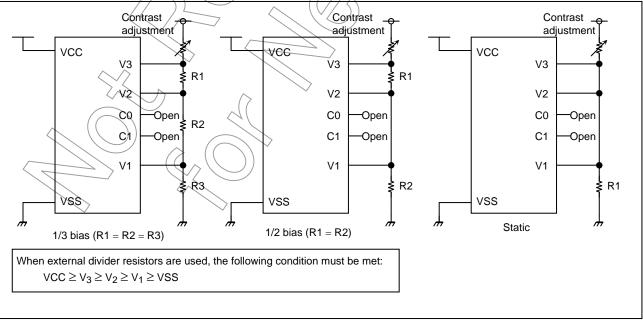

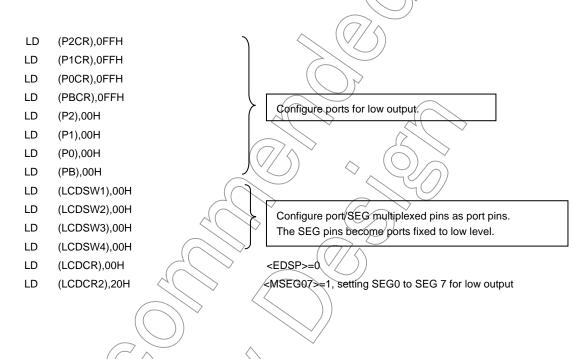

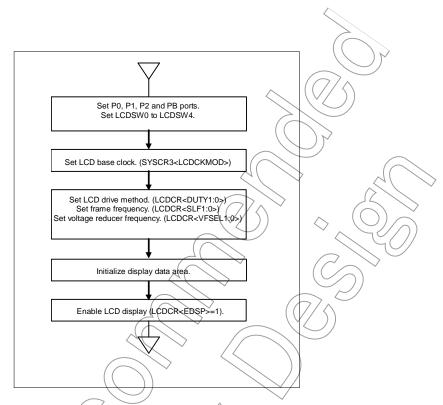

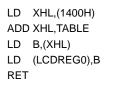

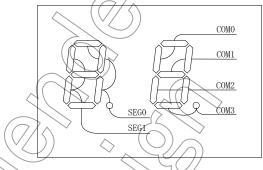

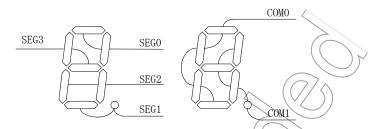

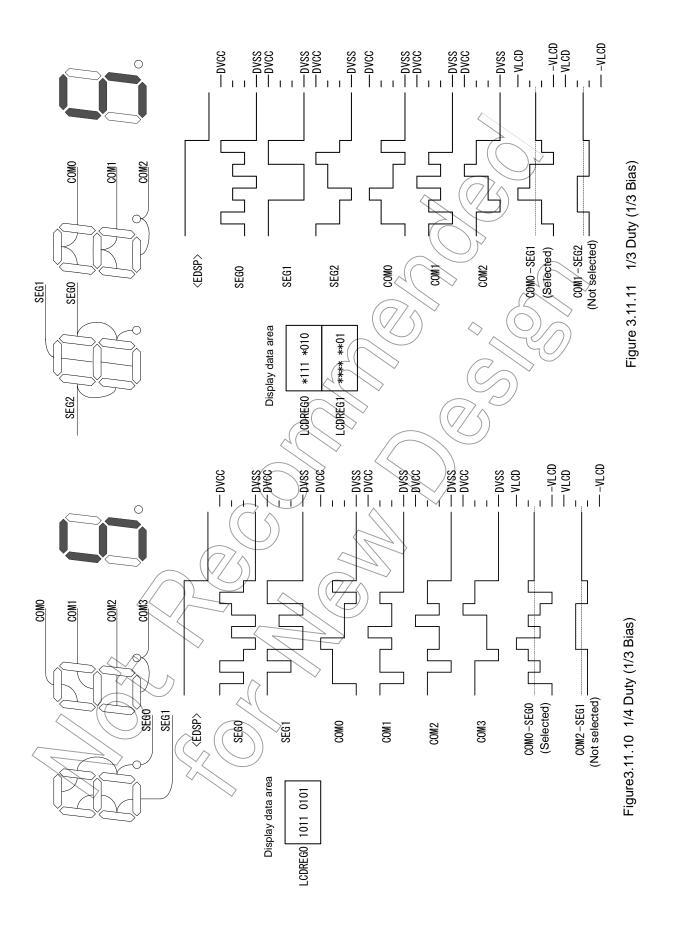

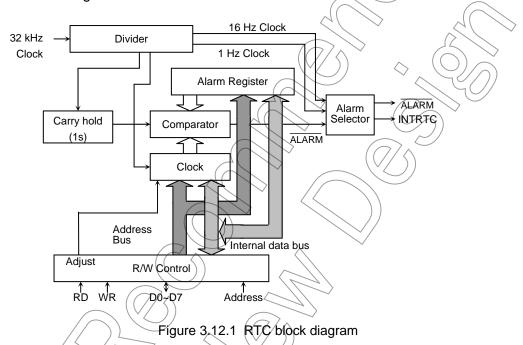

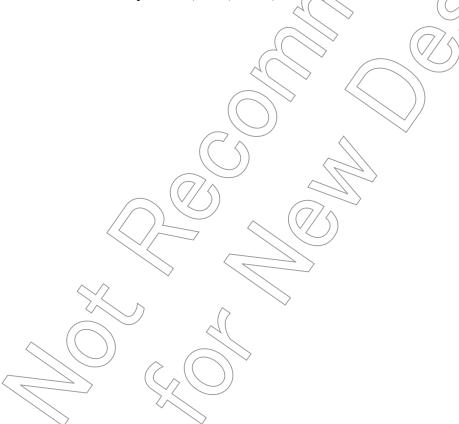

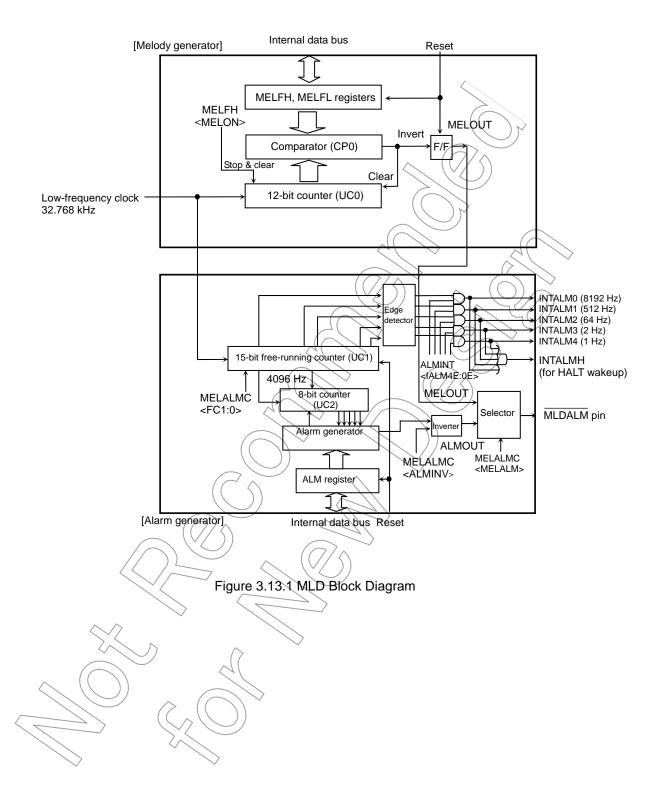

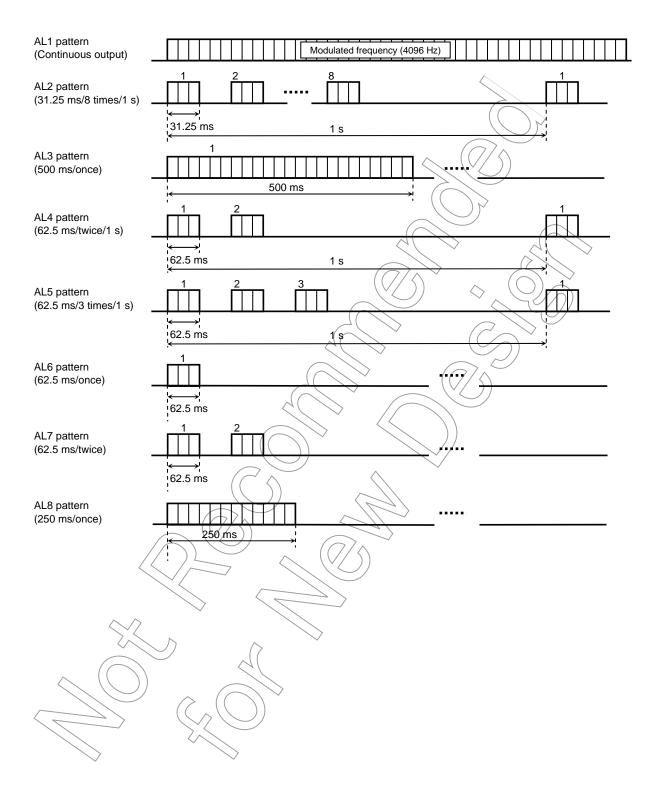

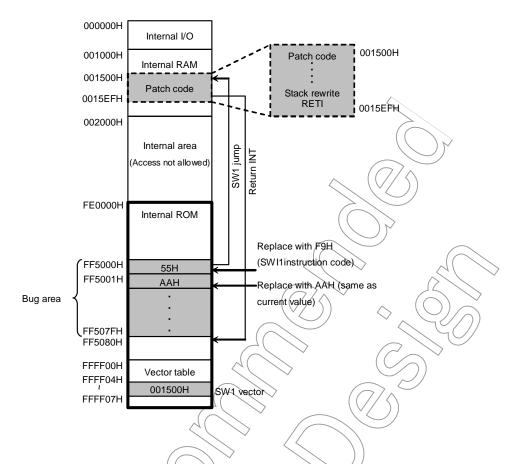

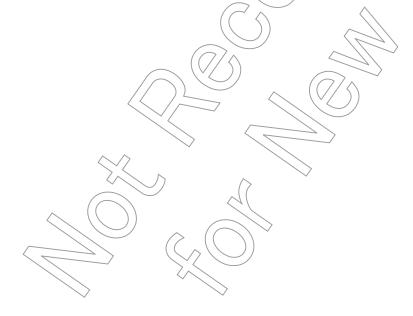

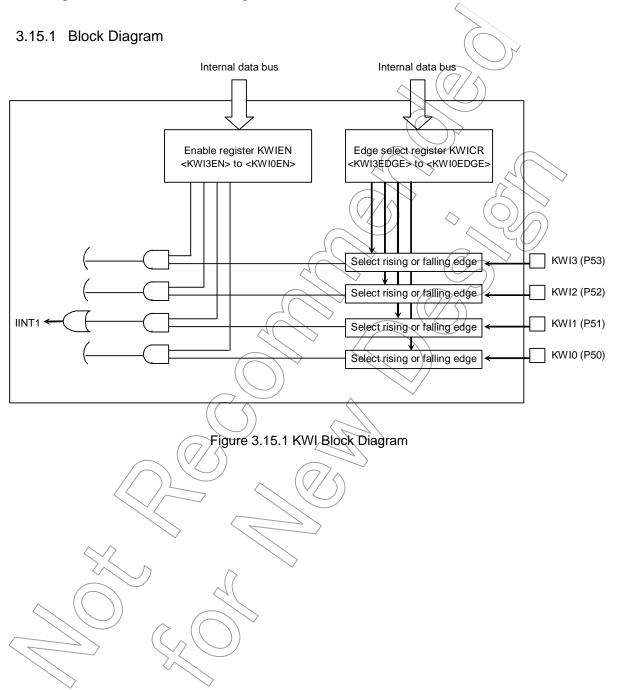

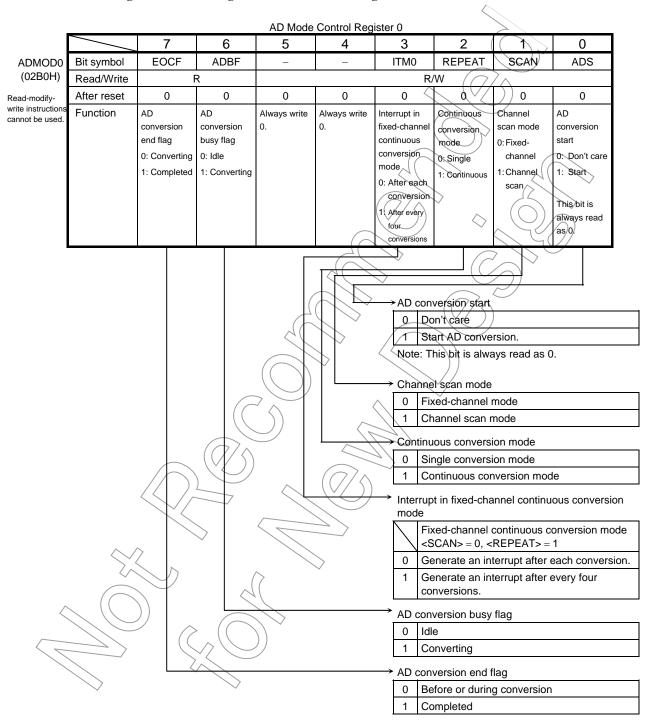

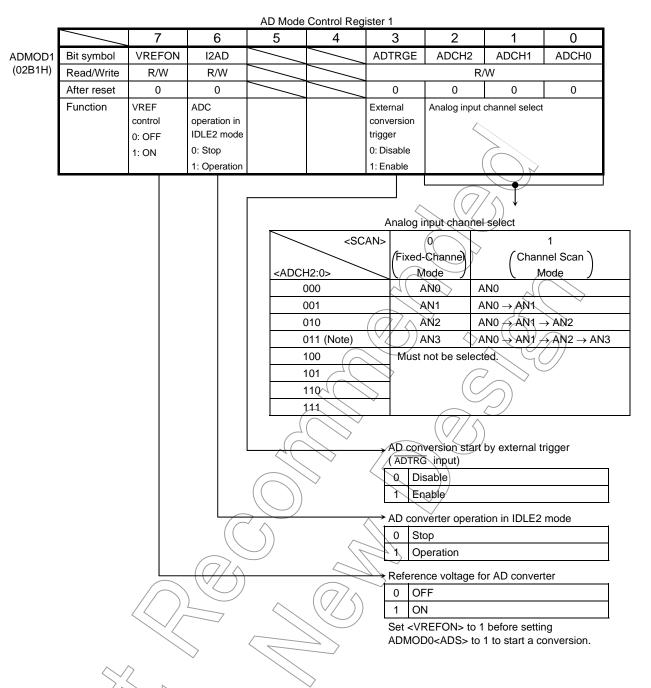

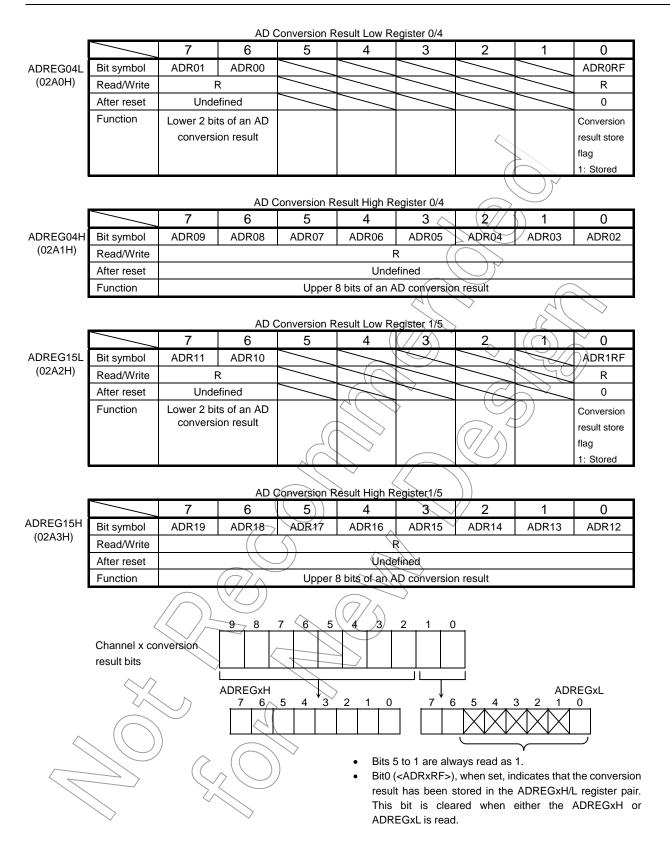

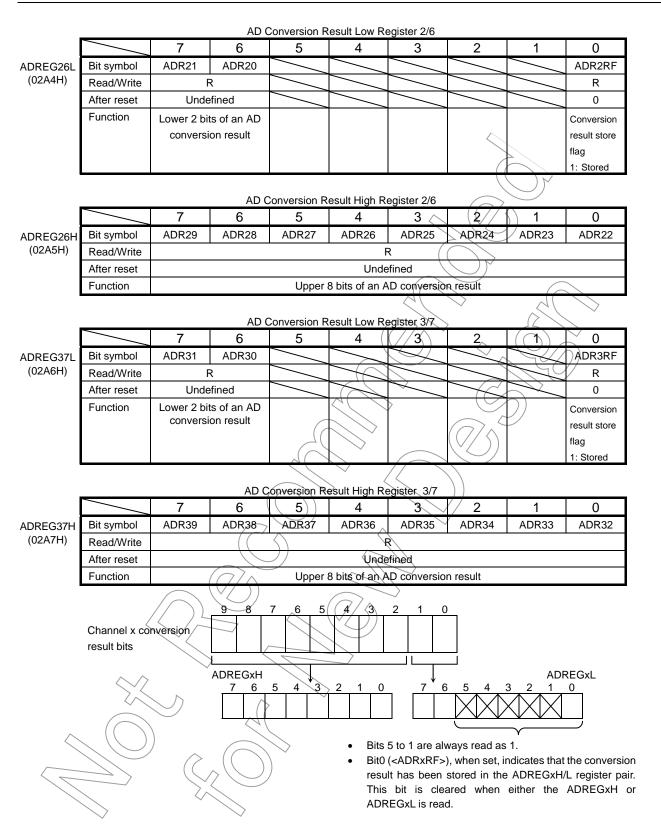

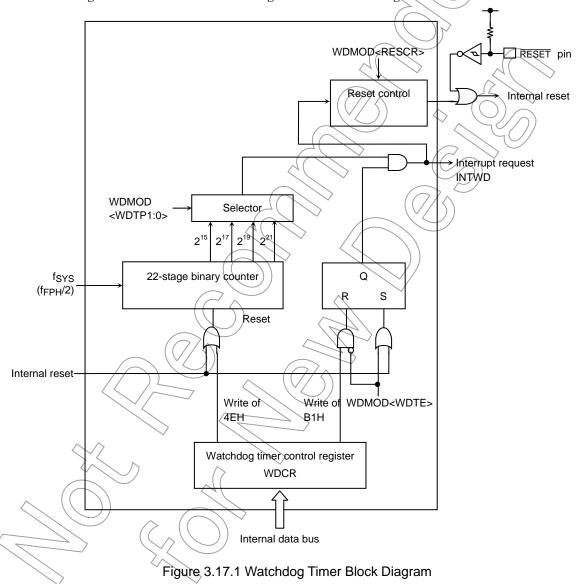

| gne       | Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | INTTMR1 to INTTMR3,                | •                                | ×        | ×           | *                                                  | ×          | ×           |  |  |  |