## Standard Products UT8SF2M40 80Megabit Flow-thru SSRAM

Preliminary Datasheet www.aeroflex.com/memories

April 2015

# A passion for performance.

## FEATURES

- □ Synchronous SRAM organized as 2Meg words x 40bit

- □ Continuous Data Transfer (CDT) architecture eliminates wait states between read and write operations

- □ Supports 40MHz to 80MHz bus operations

- □ Internally self-timed output buffer control eliminates the need for synchronous output enable

- **D** Registered inputs and outputs for flow-thru operation

- □ Single 2.5V to 3.3V supply

- □ Clock-to-output time

- Clk to Q = 12ns

- □ Clock Enable (CEN) pin to enable clock and suspend operation

- □ Synchronous self-timed writes

- □ Three Chip Enables (CS0, CS1, CS2) for simple depth expansion

- □ "ZZ" Sleep Mode option for partial power-down

- □ "SHUTDOWN" Mode option for deep power-down

- □ Four Word Burst Capability--linear or interleaved

- **Operational Environment**

- Total Dose: 100 krad(Si)

- SEL Immune:  $\leq 100 \text{MeV-cm}^2/\text{mg}$

- SEU error rate: 1.7x10<sup>-6</sup> errors/bit-day

- □ Package options:

- 288-lead CLGA, CCGA, and CBGA

- □ Standard Microelectronics Drawing (SMD) 5962-TBD

- QMLQ and Q+ pending

## INTRODUCTION

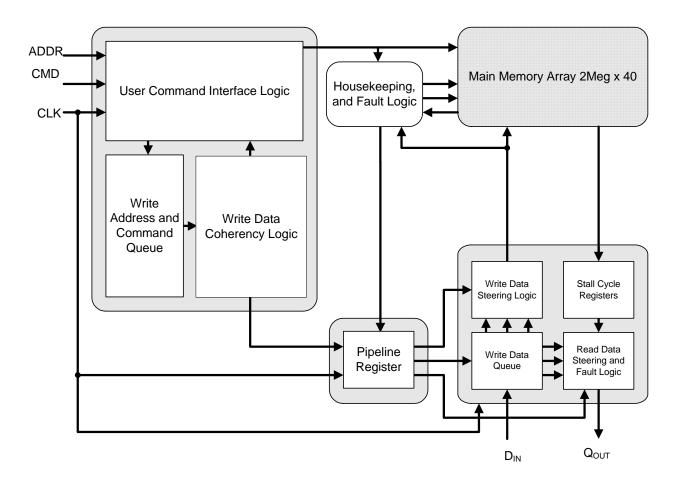

The UT8SF2M40 is a high performance 83,886,080-bit synchronous static random access memory (SSRAM) device that is organized as 2M words of 40 bits. This device is equipped with three chip selects ( $\overline{\text{CS0}}$ , CS1, and  $\overline{\text{CS2}}$ ), a write enable ( $\overline{\text{WE}}$ ), and an output enable ( $\overline{\text{OE}}$ ) pin, allowing for significant design flexibility without bus contention. The device supports a four word burst function using (ADV\_ $\overline{\text{LD}}$ ).

All synchronous inputs are registered on the rising edge of the clock provided the Clock Enable  $(\overline{CEN})$  input is enabled LOW. Operations are suspended when  $\overline{CEN}$  is disabled HIGH and the previous operation is extended. Write operation control signals are WE and six byte write enables  $\overline{BWE}[4:0]$ . All write operations are performed by internal self-timed circuitry.

For easy bank selection, three synchronous Chip Enables  $(\overline{CS0}, CS1, \overline{CS2})$  and an asynchronous Output Enable  $(\overline{OE})$  provide for output tri-state control. The output drivers are synchronously tri-stated during the data portion of a write sequence to avoid bus contention.

Figure 1. UT8SF2M40 Block Diagram

| NAME           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ТҮРЕ               |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| CS0            | <b>Chip Enable 0, Input, Active LOW:</b> Sampled on the rising edge of CLK. Used in conjunction with CS1 and $\overline{CS2}$ to select or deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input-Synchronous  |  |  |  |

| CS1            | <b>Chip Enable 1 Input, Active HIGH:</b> Sampled on the rising edge of CLK. Used in conjunction with $\overline{CS0}$ and $\overline{CS2}$ to select or deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input-Synchronous  |  |  |  |

| <u>C82</u>     | CS2Chip Enable 2 Input, Active LOW: Sampled on the rising edge of CLK.<br>Used in conjunction with CS0 and CS1 to select or deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |  |  |  |

| A[20:0]        | Address Inputs: Sampled at the rising edge of the CLK. A[1:0] is fed to the two-bit burst counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input-Synchronous  |  |  |  |

| BWE[4:0]       | <b>Byte Write Enable, Active LOW:</b> Qualified with $\overline{WE}$ , allows writes to each of six bytes of memory when active, and masks input data when disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input-Synchronous  |  |  |  |

| WE             | Write Enable Input, Active LOW: Sampled on the rising edge of CLK if<br>CEN is active LOW. This signal must be enabled LOW to initiate a write sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Input-Synchronous  |  |  |  |

| ADV_ <u>LD</u> | Advance/Load Input: Advances the on-chip address counter or loads a new address. When HIGH (and CEN is enabled LOW) the internal burst counter is advanced. When LOW, a new address can be loaded into the device for an access. After deselection, drive ADV_ID LOW to load a new address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input-Synchronous  |  |  |  |

| CLK            | <b>Clock Input:</b> Used to capture all synchronous inputs to the device. CLK is qualified with $\overline{\text{CEN}}$ . CLK is only recognized if $\overline{\text{CEN}}$ is active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input-Clock        |  |  |  |

| ŌĒ             | <b>Output Enable, Asynchronous Input, Active LOW:</b> Combined with the synchronous logic block inside the device to control the direction of the I/O pins. When LOW, the I/O pins are enabled to behave as outputs. When disabled HIGH, I/O pins are tri-stated, and act as input data pins. $\overline{OE}$ is masked during the data portion of a write sequence, during the first clock when emerging from a deselected state and when the device is deselected.                                                                                                                                                                                                                                                                                                                                                           | Input-Asynchronous |  |  |  |

| CEN            | Clock Enable Input, Active LOW: When enabled LOW, the clock signal is recognized by the SSRAM. When deasserted HIGH, the clock signal is masked. Because deasserting CEN does not deselect the device, CEN can be used to extend the previous cycle when required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input-Synchronous  |  |  |  |

| DQ[47:0]       | <b>Bidirectional Data I/Os:</b> As inputs, DQ[47:0] feed into an on-chip data register that is triggered by the rising edge of CLK. As outputs, DQ[47:0] delivers the data contained in the memory location specified by the addresses presented during the previous clock rise of the read cycle. The direction of the pins is controlled by $\overline{OE}$ . When $\overline{OE}$ is enabled LOW, the pins behave as outputs. When HIGH, DQs are placed in a tri-state condition. The outputs are automatically tri-stated during the data portion of a write sequence, during the first clock when emerging from a deselected state, and when the device is deselected, regardless of the state of $\overline{OE}$ . Aeroflex recommends connecting all DQ pins to either VDDQ or VSS through a $\geq 10k\Omega$ resistor. | I/O-Synchronous    |  |  |  |

| RESET          | <b>Reset Input, Active Low:</b> Resets device to known configuration. Reset is required at initial power-up, after exiting shutdown mode, or after any power interruption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input-ASynchronous |  |  |  |

## **Table 1: Pin Definitions**

## **Table 1: Pin Definitions**

| NAME                | DESCRIPTION                                                                                                                                                                           | TYPE               |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| ZZ                  | Input-Synchronous                                                                                                                                                                     |                    |  |  |

| SHUTDOWN            | Shutdown Input, Active HIGH: When HIGH, places device in shutdown mode. System clock can be stopped. Memory contents are not retained.                                                | Input-Asynchronous |  |  |

| READY <sup>1</sup>  | <b>Device Ready Output:</b> READY outputs a HIGH when device is available for normal operations. READY outputs a LOW when requesting an idle cycle or during power up initialization. | Output-Synchronous |  |  |

| MODE <sup>2</sup>   | Input-DC                                                                                                                                                                              |                    |  |  |

| EXTRES <sup>2</sup> | Input-DC                                                                                                                                                                              |                    |  |  |

| V <sub>DD</sub>     | Power supply inputs to the core of the device.                                                                                                                                        | Power Supply       |  |  |

| V <sub>DDQ</sub>    | Power supply for the I/O circuitry.                                                                                                                                                   |                    |  |  |

| V <sub>SS</sub>     | Ground inputs to the core of the device.                                                                                                                                              | Ground             |  |  |

| V <sub>SSQ</sub>    | Ground for I/O circuitry.                                                                                                                                                             | I/O Ground         |  |  |

| NUIL                | <b>Not used Input Low:</b> Pins designated as NUIL need to be externally connected by user to $V_{SSQ}$ through a $\geq 10k\Omega \pm 10\%$ resistor.                                 |                    |  |  |

| NUIH                | <b>Not used Input High:</b> Pins designated as NUIH need to be externally connected by user to $V_{DDQ}$ through a $\geq 10k\Omega \pm 10\%$ resistor.                                |                    |  |  |

| NC                  | No Connects. Not internally connected to the die.                                                                                                                                     |                    |  |  |

| TDO <sup>3</sup>    | $\frac{1}{1000} \frac{\text{JTAG Circuit Serial Data Output: Package pin requires a pull-up through}}{\ge 1000000000000000000000000000000000000$                                      |                    |  |  |

| TDI <sup>3</sup>    | JTAG Serial Input<br>Synchronous                                                                                                                                                      |                    |  |  |

| TMS <sup>3</sup>    | Test Mode Select<br>Synchronous                                                                                                                                                       |                    |  |  |

| TCK <sup>3</sup>    | <b>JTAG Circuit Clock Input:</b> Package pin requires a pull-up through $\geq 10 k\Omega \pm 10\%$ resistor to V <sub>DDO</sub> .                                                     | JTAG Clock         |  |  |

Note:

1. Reference application note AN-MEM-004 for additional READY signal information.

DC inputs are established at power up and cannot be switched while power is applied to the device.

Reference application note AN-MEM-005 for JTAG operations. JTAG operations are intended for terrestrial use and not guaranteed in radiation environment.

## **DEVICE OPERATION**

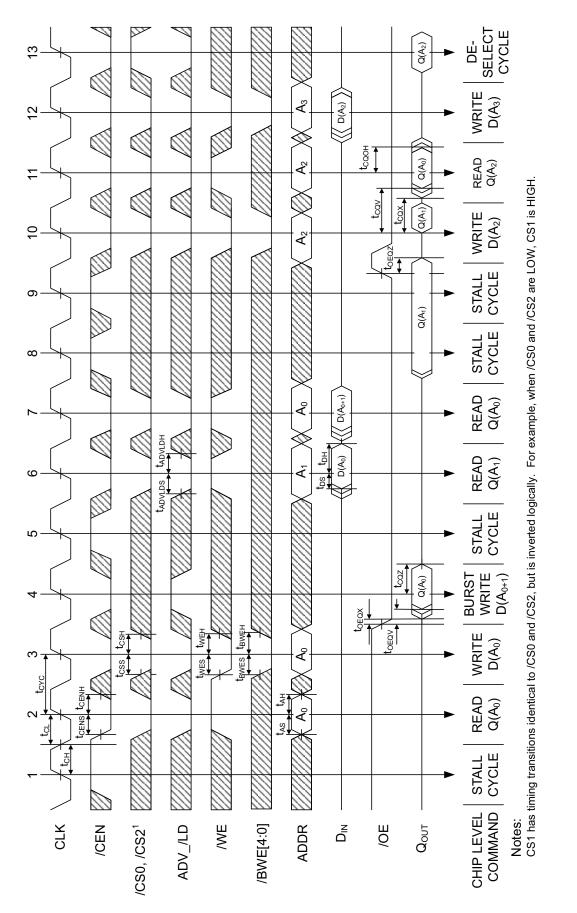

The UT8SF2M40 is synchronous flow-thru SSRAM designed specifically to eliminate wait states during Write/Read or Read/ Write transitions. All synchronous inputs and outputs are registered on the rising edge of clock. The clock signal is enabled by the Clock Enable input ( $\overline{CEN}$ ). When  $\overline{CEN}$  is HIGH, the clock signal is disregarded and all internal states are maintained. All synchronous operations are qualified by  $\overline{CEN}$ . Once power-up requirements have been satisfied, the input clock may only be stopped during sleep (ZZ is HIGH) or shutdown mode (SHUTDOWN is HIGH). Maximum access delay from the rising edge of clock ( $t_{COV}$ ) is 12ns (80 MHz device).

Access is initiated by asserting all three Chip Enables  $(\overline{CS0}, CS1, \overline{CS2})$  active at the rising edge of the clock with Clock Enable  $(\overline{CEN})$  and ADV\_ $\overline{LD}$  asserted LOW. The address presented to the device will be registered. Access can be either a Read or Write operation, depending on the status of the Write Enable  $(\overline{WE})$ .

Write operations are initiated by the Write Enable ( $\overline{WE}$ ) input. All write commands are controlled by built in synchronous self-timed circuitry.

Three synchronous Chip Enables ( $\overline{CS0}$ , CS1,  $\overline{CS2}$ ) and an asynchronous Output Enable ( $\overline{OE}$ ) simplify memory depth expansion. All operations (Reads, Writes, and Deselects) are pipelined. ADV\_ $\overline{LD}$  must be driven LOW once the device has been deselected in order to load a new address and command for the next operation.

## Single Read Accesses

A read access is initiated when the following device inputs are present at rising clock edge:  $\overline{CEN}$  is enabled LOW,  $\overline{CS0}$ , CS1, and  $\overline{CS2}$  are all enabled, the Write Enable input signal  $\overline{WE}$  is disabled HIGH and ADV\_ $\overline{LD}$  is asserted LOW. The addresses present at the address inputs A[20:0] are registered and presented to the memory. Data propagates to the input of the output register. Data will be available to the bus 12ns after the next rising clock edge provided  $\overline{OE}$  is enabled LOW. After the first clock of the read access, the output buffers are controlled by  $\overline{OE}$  and the internal control logic.  $\overline{OE}$  must be enabled LOW to drive requested data. During the next rising clock, any operation (Read/Write/Deselect) may be initiated.

## **Burst Read Accesses**

The UT8SF2M40 has an internal burst counter allowing up to four reads to be performed from a single address input. A new address can only be loaded when ADV\_ $\overline{\text{LD}}$  is driven LOW. New addresses are loaded into the SSRAM, as described by the Single Read Access section. The burst counter operates in either linear or interleave and is controlled by the MODE input at power up. When MODE pin is LOW, the burst sequence is linear. The burst sequence is interleaved when MODE is HIGH. A0 and A1 are controlled by the burst counter. The burst counter will wrap around when needed. The burst counter increments anytime ADV\_ $\overline{\text{LD}}$  is HIGH and  $\overline{\text{CEN}}$  is low. The operation selected by the state of  $\overline{\text{WE}}$  is latched at the beginning of the sequence and maintained throughout.

### **Single Write Accesses**

A write access is initiated when the following device inputs are present at rising clock edge:  $\overline{CEN}$  is enabled LOW,  $\overline{CS0}$ , CS1, and  $\overline{CS2}$  are all enabled, the Write Enable input signal  $\overline{WE}$  is enabled LOW and ADV\_ $\overline{LD}$  is asserted LOW. The addresses present at the address inputs A[20:0] are registered and presented to the memory core. Data I/Os are tri-stated at the next rising edge of clock regardless of state of  $\overline{OE}$ . The write is completed after the next rising clock edge using data present on DQ pins. Each byte of data is individually qualified by its applicable byte write enable input (see Table 2). When the input low, the applicable DQ inputs are registered to memory. When the input is high, the applicable DQ pins are ignored.

To avoid bus contention data should not be driven to DQs when outputs are active. The Output Enable ( $\overline{OE}$ ) may be disabled HIGH before applying data to the DQ lines. This will tri-state the DQ output drivers. As an additional feature DQ lines are automatically tri-stated during the data portion of a Write cycle, regardless of the state of  $\overline{OE}$ .

## **Burst Write Accesses**

The UT8SF2M40 has an internal burst counter allowing up to four writes to be performed from a single address input. A new address can only be loaded when ADV\_ $\overline{\text{LD}}$  is driven LOW. New addresses are loaded into the SSRAM, as described in the Single Write Access section. When ADV\_ $\overline{\text{LD}}$  is driven HIGH on the subsequent clock rise, where  $\overline{\text{CEN}}$  is LOW, the Chip Enables ( $\overline{\text{CS0}}$ , CS1,  $\overline{\text{CS2}}$ ) and  $\overline{\text{WE}}$  inputs are ignored and the burst counter is incremented. The  $\overline{\text{BWE}}[4:0]$  inputs must be LOW in each cycle of the burst write in order to qualify each respective byte of data.

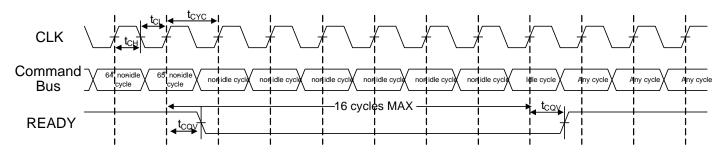

## **READY Status**

The UT8SF2M40 device operates as a Synchronous SRAM device. Data integrity housekeeping activities are performed in the background during normal user activity. These housekeeping activities are performed on a regular basis. However, when a housekeeping activity sequence cannot be completed due to user conflict for memory space, the READY pin asserts signifying to the user that an idle cycle is required. Please reference applications note AN-MEM-004 for more information.

## Byte Write Enables BWE[4:0]

The UT8SF2M40 device employs six byte write enable inputs to be used in conjunction with  $\overline{WE}$  to qualify each associated byte of data into the memory. When  $\overline{WE}$  is HIGH, the device is in read mode where all  $\overline{BWE}$ [4:0] are don't cares. When  $\overline{WE}$  is LOW, each  $\overline{BWE}$ [4:0] must also be low to write the associated data input pins into memory. Data input pins whose associated byte write enable pin is HIGH, will be masked.

| Byte Write<br>Enable Input | Data Input Pins |

|----------------------------|-----------------|

| BWE0                       | DQ[7:0]         |

| BWE1                       | DQ[15:8]        |

| BWE2                       | DQ[23:16]       |

| BWE3                       | DQ[31:24]       |

| BWE4                       | DQ[39:32]       |

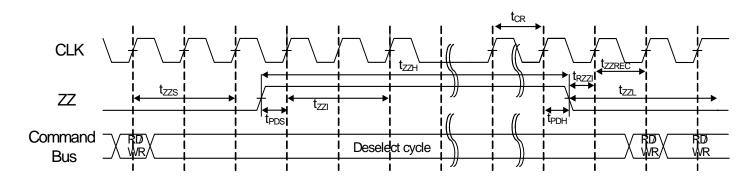

## **Sleep Mode**

The ZZ input lead is a synchronous input. Asserting the ZZ pin HIGH places the SSRAM into a power conservative "sleep" mode. To assure the completion of previous commands and through the pipeline prior to entering sleep mode, a minimum of two full clock cycles ( $t_{ZZS}$ ) are required between the last operation command and asserting the ZZ input. While in sleep mode, data integrity is guaranteed. Changing the input clock frequency or halting the input clock may be executed during sleep mode. The device must be deselected prior to entering sleep mode and remain deselected for the duration of  $t_{ZZREC}$  after the ZZ input returns LOW.

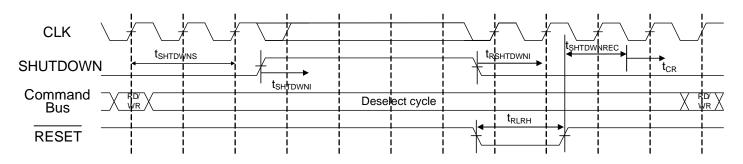

## Shutdown Mode

The SHUTDOWN input pin is an asynchronous input. Asserting SHUTDOWN places the device in a power saving shutdown mode. The system clock can be stopped. Memory contents are not maintained in shutdown mode. The SSRAM requires a reset cycle upon exiting shutdown mode.

| Table 3. Linear Burst Address Table |  |  |  |  |  |

|-------------------------------------|--|--|--|--|--|

| (MODE=V <sub>SS</sub> )             |  |  |  |  |  |

| Starting<br>Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|---------------------|-------------------|------------------|-------------------|

| A1, A0              | A1, A0            | A1, A0           | A1, A0            |

| 00                  | 01                | 10               | 11                |

| 01                  | 10                | 11               | 00                |

| 10                  | 11                | 00               | 01                |

| 11                  | 00                | 01               | 10                |

## Table 4. Interleaved Burst Address Table (MODE=V<sub>DDO</sub>)

|                     |                   | 222               |        |

|---------------------|-------------------|-------------------|--------|

| Starting<br>Address | Second<br>Address | Fourth<br>Address |        |

| A1, A0              | A1, A0            | A1, A0            | A1, A0 |

| 00                  | 01                | 10                | 11     |

| 01                  | 00                | 11                | 10     |

| 10                  | 11                | 00                | 01     |

| 11                  | 10                | 01                | 00     |

## Power Up/ Down Requirements

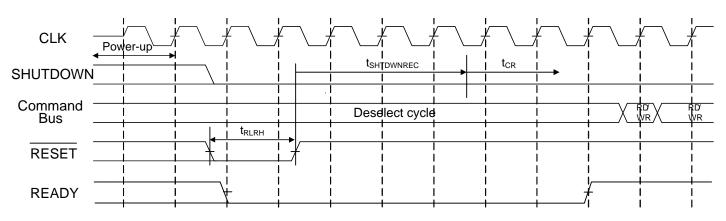

The SSRAM requires that  $V_{DD} \leq V_{DDQ}$  at all times. The SSRAM does require the user to provide an external reset after initial power application, exiting shutdown mode, or any power interruption to the device input voltage outside the specified limit. Performing a reset requires the assertion of the RESET device input lead (LOW) for a minimum of 1us ( $t_{RLRH}$ ). After the RESET input is returned HIGH, the device requires 50us ( $t_{SHTDWNREC}$ ) to complete the reset operation. Once the reset operation is complete, the device requires an additional 20us ( $t_{CR}$ ) to synchronize the clock input, providing a stable input clock is present. The device READY output lead asserts HIGH once  $t_{CR}$  is satisfied at the next rising clock. The READY out lead HIGH indicates the device is available for normal operations. For power down it is required that  $V_{DD}$  and  $V_{DDO}$  be powered down to  $\leq$ 0.5V for a minimum of 100ms.

## **Clock Conditioning Requirements**

The CLK signal input requirements are given in the Clock section of the AC Characterizations. AC Characterization performances listed herein are based on providing a clock input signal meeting these requirements.

## **Changing Clock Frequencies**

The CLK input frequency should be established at a power on, and may only be changed while in SLEEP mode (reference Table 6).

## **External Connections**

A precision 25kohm  $\leq \pm 0.2\%$  low TCR  $\leq 25$  ppm/°C resistor is required to be connected between device pin EXTRES (R15) and VSS.

In order to ensure proper operation in conjunction with JTAG boundary scan (reference applications note MEM-AN-005), Aeroflex requires that specific package pins be biased through soft connections to either V<sub>DDO</sub> or V<sub>SSO</sub>. Table 5 is a list of these required external biases.

## **Table 5. External Bias Conditions**

| Signal Name       | Package Pin       | <b>Bias Condition</b>                    |

|-------------------|-------------------|------------------------------------------|

|                   | H1, H20, N1, N2,  |                                          |

| NUIL <sup>1</sup> | N19, N20, P13,    | $\geq 10$ k $\Omega$ to V <sub>SSO</sub> |

| NUIL              | R7, R8, R10, R12, | $\geq 10$ KS2 to V <sub>SSQ</sub>        |

|                   | R13, R14, R16     |                                          |

| NUIH <sup>2</sup> | P16, R8           | $\geq 10 k\Omega$ to $V_{DDQ}$           |

| TDO               | R5                | $\geq 10 k\Omega$ to $V_{DDQ}$           |

| TCK               | R9                | $\geq 10$ k $\Omega$ to V <sub>SSQ</sub> |

|                   |                   | $\geq 10 k\Omega$ to $V_{DDQ}$ or        |

| $DQ[47:0]^3$      | ref Table 7       | V <sub>SSQ</sub>                         |

Notes: 1. NUIL = Not Used Input Low

2. NUIH = Not Used Input High

3. Aeroflex recommends connecting all DQ[47:0] to either V<sub>DDO</sub> or V<sub>SSO</sub> through  $\geq 10 k\Omega$  resistors.

| Operation                    | Address<br>Used | CSx* | ZZ | SHUT<br>DOWN | ADV_LD | WE | BWEx | OE | CEN | CLK | DQs      |

|------------------------------|-----------------|------|----|--------------|--------|----|------|----|-----|-----|----------|

| Standby Mode                 | None            | Н    | L  | L            | L      | Х  | Х    | Х  | L   | L-H | 3-State  |

| Continue Deselect            | None            | Х    | L  | L            | Н      | Х  | Х    | Х  | L   | L-H | 3-State  |

| Read Cycle (Start Burst)     | External        | L    | L  | L            | L      | Н  | Х    | L  | L   | L-H | Data Out |

| Read Cycle (Cont. Burst)     | Next            | Х    | L  | L            | Н      | Х  | Х    | L  | L   | L-H | Data Out |

| NOP/Dummy Read<br>(Start)    | External        | L    | L  | L            | L      | Н  | X    | Н  | L   | L-H | 3-State  |

| NOP/Dummy Read<br>(Cont.)    | Next            | Х    | L  | L            | Н      | Х  | X    | Н  | L   | L-H | 3-State  |

| Write Cycle (Start Burst)    | External        | L    | L  | L            | L      | L  | L    | Х  | L   | L-H | Data In  |

| Write Cycle (Cont. Burst)    | Next            | Х    | L  | L            | Н      | Х  | L    | Х  | L   | L-H | Data In  |

| Dummy Write (Start)          | None            | L    | L  | L            | L      | L  | Н    | Х  | L   | L-H | 3-State  |

| Dummy Write (Cont.<br>Burst) | Next            | Х    | L  | L            | Н      | Х  | Н    | Х  | L   | L-H | 3-State  |

| Clock Inhibit (Stall)        | N/A             | X    | L  | L            | Х      | Х  | Х    | Х  | Н   | L-H | N/A      |

| Sleep Mode                   | N/A             | Н    | Н  | L            | Х      | Х  | Х    | Х  | Х   | Х   | 3-State  |

| Shutdown Mode                | None            | Х    | Х  | Н            | Х      | Х  | Х    | Х  | Х   | Х   | 3-State  |

## Table 6: Truth Table for UT8SF2M40<sup>[1,2,3,4,5,6,7]</sup>

Notes:

\* All chip selects active when L, at least one chip select inactive when H

1. X = "Don't Care", H = Logic HIGH, L = Logic LOW.

2. Write is defined by WE and BWEx

3. When a Write cycle is detected, all I/Os are tri-stated.

4. The DQ pins are controlled by the current cycle and the  $\overline{\text{OE}}$  signal.

5.  $\overline{\text{CEN}} = \widehat{H}$  inserts wait states.

6. Device will power-up deselected and the I/Os in a tri-state condition, regardless of OE.

7. OE is asynchronous and is not sampled with the clock rise. It is masked internally during Write cycles. During a Read cycle DQs = tri-state when  $\overline{OE}$  is inactive or when the device is deselected and DQs = data when  $\overline{OE}$  is active.

## Table 7. 288-Lead Pipelined Signal Locations

|   | 1                 | 2                 | 3    | 4     | 5                | 6    | 7                 | 8                 | 9                | 10                | 11    | 12                | 13                | 14                | 15     | 16                | 17   | 18           | 19                | 20                |

|---|-------------------|-------------------|------|-------|------------------|------|-------------------|-------------------|------------------|-------------------|-------|-------------------|-------------------|-------------------|--------|-------------------|------|--------------|-------------------|-------------------|

| A |                   |                   | VDDQ | CS2   | WE               | VSS  | A10               | A8                | A4               | A18               | A19   | A14               | A15               | A2                | A0     | CS0               | VSS  | BWE1         |                   |                   |

| В |                   | VSS               | VSS  | OE    | BWE2             | A11  | A9                | A6                | A17              | VSS               | A20   | A16               | A13               | A12               | A1     | ZZ                | BWE3 | SHUT<br>DOWN | VSS               |                   |

| С | VDDQ              | VSSQ              | VSS  | READY | BWE0             | BWE4 | A7                | A5                | VSS              | VDD               | VSS   | VSSQ              | VDD               | VDD               | A3     | ADV_LD            | CS1  | VSS          | VSSQ              | VDD               |

| D | DQ33              | DQ35              | VDD  | VSS   | VSS              | VDDQ | VSSQ              | VDD               | VDD              | VSS               | VDD   | VDD               | VSSQ              | VDDQ              | VDD    | VSS               | VSS  | VDD          | VDDQ              | DQ32              |

| E | DQ37              | DQ1               | DQ39 | VDD   | VSSQ             | VSS  | VSSQ              | VDDQ              | VSS              | VSS               | VSS   | VSSQ              | VDDQ              | VSS               | VSS    | VSSQ              | VDD  | DQ38         | DQ36              | DQ34              |

| F | DQ3               | DQ5               | DQ7  | VDDQ  | VDDQ             | VSSQ | VSS               | VSS               | VDD              | VSS               | VDD   | VSS               | VSS               | VDDQ              | VSSQ   | VDDQ              | VDDQ | DQ4          | DQ0               | DQ2               |

| G | DQ9               | DQ11              | DQ13 | VDD   | VSSQ             | VDD  | VDDQ              | VDD               | VSS              | VDD               | VSS   | VDD               | VDDQ              | VSSQ              | VDD    | VSSQ              | VDD  | DQ10         | DQ6               | DQ8               |

| H | NUIL <sup>3</sup> | DQ15              | CEN  | VSS   | VSS              | VDD  | VDD               | VDD               | VSS              | VSS               | VSS   | VDD               | VDD               | VSS               | VSS    | VSS               | VSS  | CLK          | DQ12              | NUIL              |

| J | DQ19              | DQ17              | DQ21 | VDD   | VSSQ             | VDD  | VSS               | VDD               | VSS              | VDD               | VSS   | VDD               | VSS               | VSSQ              | VDD    | VSSQ              | VDD  | DQ14         | DQ16              | DQ18              |

| K | DQ27              | DQ25              | DQ23 | VDDQ  | VDDQ             | VSSQ | VSS               | VDDQ              | VDD              | VSS               | VDD   | VDDQ              | VSS               | VDDQ              | VSSQ   | VDDQ              | VDDQ | DQ20         | DQ24              | DQ22              |

| L | DQ31              | DQ41              | DQ29 | VDD   | VSSQ             | VSS  | VSSQ              | VDDQ              | VSS              | VSS               | VSS   | VSSQ              | VDDQ              | VSS               | VSS    | VSSQ              | VDD  | DQ26         | DQ30              | DQ28              |

| М | DQ45              | DQ47              | DQ43 | VDD   | VSS              | VSSQ | VDDQ              | VSSQ              | VDD              | VSS               | VDD   | VDD               | VSSQ              | VDDQ              | VSSQ   | VSS               | VDD  | DQ40         | DQ44              | DQ42              |

| N | NUIL <sup>3</sup> | NUIL <sup>3</sup> | vss  | VSS   | VDD              | VDDQ | VSSQ              | VDD               | VSS              | VDD               | VSS   | VSS               | VDD               | VSSQ              | VSSQ   | VDD               | VSS  | DQ46         | NUIL <sup>3</sup> | NUIL <sup>3</sup> |

| Р |                   | VSS               | VSS  | VDD   | VDDQ             | VSSQ | VSSQ              | VSSQ              | VSS              | VSS               | VDDQ  | MODE              | NUIL <sup>3</sup> | VDDQ              | TMS    | NUIH <sup>4</sup> | VSSQ | VSS          | VSS               |                   |

| R |                   |                   | VDD  | TDI   | TDO <sup>1</sup> | VDD  | NUIL <sup>3</sup> | NUIH <sup>4</sup> | TCK <sup>2</sup> | NUIL <sup>3</sup> | RESET | NUIL <sup>3</sup> | NUIL <sup>3</sup> | NUIL <sup>3</sup> | EXTRES | NUIL <sup>3</sup> | VDDQ | VDD          |                   |                   |

Notes:

1. Pin requires pull-up to  $V_{DDQ}$  of  $\geq 10k\Omega \pm 10\%$ . 2. Pin requires pull-down to  $V_{SS}$  of  $\geq 10k\Omega \pm 10\%$ . 3. NUIL = Not used Input Low. NUIL pins requires  $\geq 10k\Omega \pm 10\%$  pull-down to  $V_{SSQ}$ . 4. NUIH = Not Used Input High. NUIH pins requires  $\geq 10k\Omega \pm 10\%$  pull-up to  $V_{DDQ}$ .

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

(Referenced to  $V_{SS}$ )

| SYMBOL                            | PARAMETER                                                      | VALUE                         | UNIT |

|-----------------------------------|----------------------------------------------------------------|-------------------------------|------|

| V <sub>DD</sub> /V <sub>DDQ</sub> | Supply Voltage <sup>2</sup>                                    | -0.5 to 4.0                   | V    |

| V <sub>IN</sub>                   | Voltage on any pin <sup>2</sup>                                | -0.3 to V <sub>DDQ</sub> +0.3 | V    |

| I <sub>IO</sub>                   | DC I/O current per pin @ $T_J = 135^\circ$ for 15 years        | <u>+</u> 10                   | mA   |

| P <sub>D</sub>                    | Package power dissipation permitted (a) $T_C = 105^{\circ}C^3$ | 15                            | W    |

| T <sub>J</sub>                    | Maximum junction temperature                                   | +150                          | °C   |

| $\Theta_{ m JC}$                  | Thermal resistance junction to case                            | 3                             | °C/W |

| T <sub>STG</sub>                  | Storage temperature                                            | -65 to +150                   | °C   |

#### Notes:

1. Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. 2. All voltages are referenced to  $V_{SS}$ . 3. Per MIL-STD-883, Method 1012, Section 3.4.1  $P_D = (T_J(max) - T_C(max))$

## **OPERATIONAL ENVIRONMENTS**

| PARAMETER                                      | LIMIT                | UNITS                   |

|------------------------------------------------|----------------------|-------------------------|

| Total Ionizing Dose (TID)                      | 100                  | krad(Si)                |

| Heavy Ion Error Rate <sup>1</sup>              | 1.7x10 <sup>-6</sup> | Errors/Bit-Day          |

| Single Event Latchup (SEL) Immune <sup>2</sup> | ≤ 100                | MeV-cm <sup>2</sup> /mg |

#### Notes:

1. Adams 90% worst case environment, Geosynchronous orbit, 100mils of aluminum

2. Temperature =  $105^{\circ}$ C; V<sub>DD</sub> and V<sub>DDQ</sub> = 3.6V

## **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                | LIMITS                 |

|------------------|--------------------------|------------------------|

| V <sub>DD</sub>  | Core supply voltage      | 2.3V to $V_{DDQ}$      |

| V <sub>DDQ</sub> | I/O power supply voltage | 2.3V to 3.6V           |

| T <sub>C</sub>   | Case temperature range   | -55°C to +105°C        |

| V <sub>IN</sub>  | DC input voltage         | 0V to V <sub>DDQ</sub> |

| T <sub>J</sub>   | Junction Temperature     | -55°C to +125°C        |

## DC ELECTRICAL CHARACTERISTICS (Pre and Post-Radiation)\*

| PARAMETER                        | DESCRIPTION                           | CONDITI                                                                                                 | ION            | MIN                       | MAX              | UNIT |

|----------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|----------------|---------------------------|------------------|------|

| V <sub>DD</sub>                  | Core Power Supply<br>Voltage          |                                                                                                         |                | 2.3                       | V <sub>DDQ</sub> | V    |

| V <sub>DDQ</sub>                 | I/O Power Supply Voltage              |                                                                                                         |                | 2.3                       | 3.6              | V    |

| V <sub>OH</sub>                  | Output HIGH Voltage                   | For 3.0V I/O, I <sub>OH</sub> =-4mA                                                                     |                | 0.8 *<br>V <sub>DDQ</sub> |                  | V    |

|                                  |                                       | For 2.3V I/O, I <sub>OH</sub> =-1mA                                                                     |                | 2.0                       |                  | V    |

| V <sub>OL</sub>                  | Output LOW Voltage                    | For 3.0V I/O, I <sub>OL</sub> =8mA                                                                      |                |                           | 0.4              | V    |

|                                  |                                       | For 2.3V I/O, I <sub>OL</sub> =1mA                                                                      |                |                           | 0.4              | V    |

| V <sub>IH</sub>                  | Input HIGH Voltage                    | For 3.0V I/O                                                                                            |                | 2.0                       |                  | V    |

|                                  |                                       | For 2.3V I/O                                                                                            |                | 1.7                       |                  | V    |

| V <sub>IL</sub>                  | Input LOW Voltage                     | For 3.0V I/O                                                                                            |                |                           | 0.8              | V    |

|                                  |                                       | For 2.3V I/O                                                                                            |                |                           | 0.7              | V    |

| I <sub>IN1</sub>                 | Input Leakage Current                 | $V_{IN} = V_{DDQ}$ and $V_{SS}$<br>Except device pins TDI and                                           | d TMS          | -2                        | 2                | μΑ   |

| I <sub>IN2</sub>                 | Input Leakage Current                 | V <sub>IN</sub> = V <sub>DDQ</sub><br>Device pins TDI and TMS                                           |                |                           | 2                | μA   |

|                                  |                                       | $V_{IN} = V_{SS}$<br>Device pins TDI and TMS                                                            |                | -100                      |                  | μΑ   |

| I <sub>OZ</sub>                  | Three-State Output<br>Leakage Current | $V_{DD,} V_{DDQ} = (Max),$<br>$V_{O} = V_{DDQ} \text{ and } V_{SS,}$<br>$\overline{OE} = V_{DDQ} (Max)$ |                | -2                        | 2                | μΑ   |

| $I_{OS}^{1,2}$                   | Short-Circuit Output<br>Current       | $V_{DD}$ , $V_{DDQ} = (Max)$ ,<br>$V_{O} = V_{DDQ}$ and $V_{SS}$                                        |                | -100                      | 100              | mA   |

| I <sub>DD</sub> <sup>3</sup>     | V <sub>DD</sub> Supply Current in     | $V_{DD}$ , $V_{DDQ} = (Max)$ ,                                                                          | 105°C          |                           | 900              | mA   |

|                                  | Active Mode                           | $I_{OUT} = 0mA,$<br>$f = f_{max}$                                                                       | -55°C and 25°C |                           | 750              | mA   |

| I <sub>DDQ</sub> <sup>3</sup>    | V <sub>DDQ</sub> Supply Current in    | $V_{DD}$ , $V_{DDQ} = (Max)$ ,                                                                          | 105°C          |                           | 100              | mA   |

| -                                | Active Mode                           | $I_{OUT} = 0mA,$<br>$f = f_{max}$                                                                       | -55°C and 25°C |                           | 100              | mA   |

| I <sub>SHTDWN</sub> <sup>3</sup> | V <sub>DD</sub> Supply Current in     | $V_{DD}$ , $V_{DDQ} = (Max)$ ,                                                                          | 105°C          |                           | 250              | mA   |

|                                  | Shutdown Mode                         | $V_{IN} \ge V_{IH}$ or $V_{IN} \le V_{IL}$ ,<br>SHUTDOWN $\ge V_{IH}$                                   | -55°C and 25°C |                           | 200              | mA   |

$(V_{DD} = 2.3V \text{ to } V_{DDO}, V_{DDO} = 2.3 \text{ to } 3.6V; \text{ Unless otherwise noted, Tc is per the temperature range ordered})$

| I <sub>SHTDWNQ</sub> <sup>3</sup> | V <sub>DDQ</sub> Supply Current in<br>Shutdown Mode | $V_{DD,}V_{DDQ} = (Max),$<br>$V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL},$<br>$SHUTDOWN \ge V_{IH}$                                                  | 105°C<br>-55°C and 25°C | 15<br>15   | mA<br>mA |

|-----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|----------|

| I <sub>STBY</sub> <sup>3</sup>    | V <sub>DD</sub> Supply Current in<br>Standby Mode   | $V_{DD,} V_{DDQ} = (Max),$<br>$V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL},$<br>f = fmax, device<br>deselected                                        | 105°C<br>-55°C and 25°C | 650<br>500 | mA<br>mA |

| I <sub>STBYQ</sub> <sup>3</sup>   | V <sub>DDQ</sub> Supply Current in<br>Standby Mode  | $V_{DD,} V_{DDQ} = (Max),$<br>$V_{IN} \ge V_{IH} \text{ or } VIN < VIL,$<br>f = fmax, device<br>deselected                                                | 105°C<br>-55°C and 25°C | 100<br>100 | mA<br>mA |

| I <sub>ZZ</sub> <sup>3</sup>      | V <sub>DD</sub> Supply Current in<br>Sleep Mode     | $\begin{split} & V_{DD,} V_{DDQ} = (Max), \\ & V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL}, \\ & ZZ \ge V_{IH}, \\ & SHUTDOWN \le V_{IL} \end{split}$ | 105°C<br>-55°C and 25°C | 500<br>350 | mA<br>mA |

| I <sub>ZZQ</sub> <sup>3</sup>     | V <sub>DDQ</sub> Supply Current in<br>Sleep Mode    | $\begin{split} & V_{DD,} V_{DDQ} = (Max), \\ & V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL}, \\ & ZZ \ge V_{IH}, \\ & SHUTDOWN \le V_{IL} \end{split}$ | 105°C<br>-55°C and 25°C | 85<br>85   | mA<br>mA |

## CAPACITANCE

| SYMBOL                        | PARAMETER         | MIN | MAX | UNIT |

|-------------------------------|-------------------|-----|-----|------|

| $C_{IN}^{4}$                  | Input Capacitance |     | 15  | pF   |

| C <sub>I/O</sub> <sup>4</sup> | I/O Capacitance   |     | 15  | pF   |

#### Notes:

\* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

1. Supplied as a design limit but not guaranteed nor tested.

2. Not more than one output may be shorted at a time for maximum duration of one second.

3. Post-irradiation limits are the 105°C limits when specified.

4. Measured only for initial qualification and after process or design changes that could affect this parameter.

## AC CHARACTERISTICS (Pre and Post-Radiation)\*

| PARAMETER                          | DESCRIPTION                                                         | MIN                    | MAX                    | UNI  |

|------------------------------------|---------------------------------------------------------------------|------------------------|------------------------|------|

| $t_{\rm Powerup}^2$                | V <sub>DD</sub> to first valid command (READ or WRITE)              | 100                    |                        | ms   |

| Clock                              |                                                                     |                        | I                      |      |

| t <sub>CYC</sub> <sup>6</sup>      | Clock (CLK) cycle time                                              | 12.5                   | 25.0                   | ns   |

| t <sub>CH</sub>                    | CLK HIGH time                                                       | 0.4 * t <sub>CYC</sub> | 0.6 * t <sub>CYC</sub> | ns   |

| t <sub>CL</sub>                    | CLK LOW time                                                        | 0.4 * t <sub>CYC</sub> | 0.6 * t <sub>CYC</sub> | ns   |

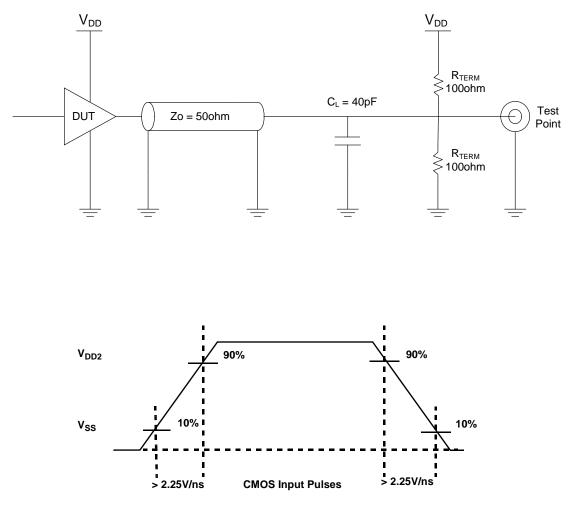

| $t_{r,} t_{f}^{2}$                 | Input clock rise/fall time (10-90%)                                 | 2.25                   |                        | V/ns |

| t <sub>clkPJ</sub> <sup>3,5</sup>  | Input clock period jitter                                           | -100                   | 100                    | ps   |

| t <sub>clkCCJ</sub> <sup>3,5</sup> | Input clock cycle to cycle jitter                                   |                        | 150                    | ps   |

| Setup Times                        |                                                                     |                        | 1                      |      |

| t <sub>AS</sub>                    | Address setup time prior to CLK                                     | 2.5                    |                        | ns   |

| t <sub>DS</sub>                    | Data setup time prior to CLK                                        | 1.5                    |                        | ns   |

| t <sub>CENS</sub>                  | Clock enable setup ( $\overline{\text{CEN}}$ ) time prior to CLK    | 3                      |                        | ns   |

| t <sub>WES</sub>                   | Write enable ( $\overline{\text{WE}}$ ) setup time prior to CLK     | 3                      |                        | ns   |

| t <sub>BWES</sub>                  | Byte Write enable ( $\overline{BWE}[4:0]$ ) setup time prior to CLK | 3                      |                        | ns   |

| t <sub>ADVLDS</sub>                | Advance load (ADV_LD) setup time prior to CLK                       | 2.5                    |                        | ns   |

| t <sub>CSS</sub>                   | Chip select (CSx) setup time prior to CLK                           | 3                      |                        | ns   |

| Hold Times                         |                                                                     |                        | <u> </u>               |      |

| t <sub>AH</sub>                    | Address hold time after CLK                                         | 1.2                    |                        | ns   |

| t <sub>DH</sub>                    | Data hold time after CLK                                            | 1.4                    |                        | ns   |

| t <sub>CENH</sub>                  | CEN hold time after CLK                                             | 1.2                    |                        | ns   |

| t <sub>WEH</sub>                   | WE hold time after CLK                                              | 1.5                    |                        | ns   |

| t <sub>BWEH</sub>                  | Byte Write enable ( $\overline{BWE}[4:0]$ ) hold time after CLK     | 1.5                    |                        | ns   |

| t <sub>ADVLDH</sub>                | ADV_LD hold time after CLK                                          | 0.9                    |                        | ns   |

| t <sub>CSH</sub>                   | CSx hold time after CLK                                             | 1.8                    |                        | ns   |

| Output Times                       | •                                                                   | -                      |                        |      |

| t <sub>CQV</sub> <sup>4</sup>      | Data valid after rising CLK                                         |                        | 12                     | ns   |

| $t_{OEQV}^4$                       | Output enable $(\overline{OE})$ active to data valid                |                        | 4.0                    | ns   |

| t <sub>CQOH</sub>                  | Data output hold time after rising CLK                              | 2.0                    |                        | ns   |

| t <sub>CQZ</sub> <sup>5</sup>      | Rising CLK to output three-state time                               |                        | 5.0                    | ns   |

| t <sub>CQX</sub> <sup>5</sup>      | Rising CLK to output enable time                                    | 1.3                    |                        | ns   |

$(V_{DD}=2.3V \text{ to } V_{DDQ}, V_{DDQ}=2.3 \text{ to } 3.6V; \text{ Unless otherwise noted, Tc is per the temperature range ordered.})^1$

| t <sub>OEQZ</sub> <sup>5</sup> | $\overline{OE}$ inactive to output three-state time |   | 4.5 | ns |

|--------------------------------|-----------------------------------------------------|---|-----|----|

| t <sub>OEQX</sub> <sup>5</sup> | $\overline{OE}$ active to output enable time        | 0 |     | ns |

Notes:

\* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured

1. AC Characteristics based on compliance with CLOCK input specifications 2. Supplied as a design guideline, not tested or guaranteed. 3. Period and Cycle to Cycle jitter is defined by JEDEC Standard 65B 4. Maximum data output valid times guaranteed up to 25pf load capacitance. For loads >25pf, a derating factor of parameter = [specification max(ns) + ( $C_{Load}$  -25pF)(44.2ps/pF]. 5. Guranteed by design.

6. Maximum Cycle Time is tested functionally.

## SHUTDOWN AND SLEEP MODE CHARACTERISTICS (Pre and Post-Radiation)\*

$(V_{DD} = 2.3V \text{ to } V_{DDO}, V_{DDO} = 2.3 \text{ to } 3.6V; \text{ Unless otherwise noted } T_C \text{ is for temperature range ordered.})$

| PARAMETER                             | DESCRIPTION                        | CONDITION                       | MIN                 | MAX                 | UNIT |

|---------------------------------------|------------------------------------|---------------------------------|---------------------|---------------------|------|

| t <sub>ZZS</sub> <sup>3</sup>         | Device operation to SLEEP mode     | $ZZ \ge V_{IH}$                 | 1 t <sub>CYC</sub>  |                     | ns   |

| t <sub>ZZH</sub> <sup>3</sup>         | SLEEP high pulse width             | $ZZ \ge V_{IH}$                 | 100                 |                     | μs   |

| t <sub>ZZL</sub> <sup>3</sup>         | SLEEP low pulse width              | $ZZ \leq V_{IH}$                | 100                 |                     | μs   |

| t <sub>SHTDWNS</sub> <sup>3</sup>     | Device operation to SHUTDOWN       | SHUTDOWN $\geq$ V <sub>IH</sub> | 2 t <sub>CYC</sub>  |                     | ns   |

| t <sub>ZZREC</sub> <sup>3</sup>       | SLEEP recovery time                | STANDBY $\leq V_{IL}$           | $100 + (3*t_{CYC})$ |                     | ns   |

| t <sub>SHTDWNREC</sub> <sup>1,3</sup> | SHUTDOWN recovery time             | $SHUTDOWN \le V_{IL}$           |                     | 50                  | us   |

| t <sub>ZZI</sub> <sup>4</sup>         | Active to SLEEP current            | $ZZ \ge V_{IH}$                 |                     | $100 + (3*t_{CYC})$ | ns   |

| t <sub>SHTDWNI</sub> <sup>4</sup>     | Active to SHUTDOWN current         | SHUTDOWN $\geq V_{IH}$          |                     | 250                 | ns   |

| t <sub>RZZI</sub> <sup>4</sup>        | Time to exit SLEEP current mode    | $STANDBY \le V_{IL}$            | 0                   |                     | ns   |

| t <sub>RSHTDWNI</sub> 4               | Time to exit SHUDOWN current mode  | SHUTDOWN $\leq$ V <sub>IL</sub> | 0                   |                     | ns   |

| t <sub>CR</sub> <sup>1,2,3</sup>      | Clock recovery prior to exiting ZZ | $ZZ \ge V_{IH}$                 |                     | 20                  | μs   |

| t <sub>RLRH</sub>                     | RESET low to high time             | Shutdown $\leq V_{IL}$          | 1                   |                     | μs   |

| t <sub>PDS</sub> <sup>3</sup>         | SLEEP setup time prior to CLK      |                                 | 2.0                 |                     | ns   |

| t <sub>PDH</sub> <sup>3</sup>         | SLEEP hold time after CLK          |                                 | 0.5                 |                     | ns   |

Notes:

\* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured

1. The clock must start up prior to exiting sleep or shutdown modes. Parameter is guaranteed by design.

T<sub>CR</sub> is necessary anytime the clock is stopped, after initial power on, or exiting shutdown mode.

Tested functionally.

Guaranteed by design.

Figure 3. Switching Waveform for Internal Housekeeping

Figure 4. Switching Waveform for SLEEP Mode

Figure 6. Switching Waveform for Power-Up

Notes: 1. Measurement of data output occurs at the low to high or high to low transition mid-point (i.e., CMOS input =  $V_{DD2}/2$

Figure 8. AC Test Loads and Input Waveforms

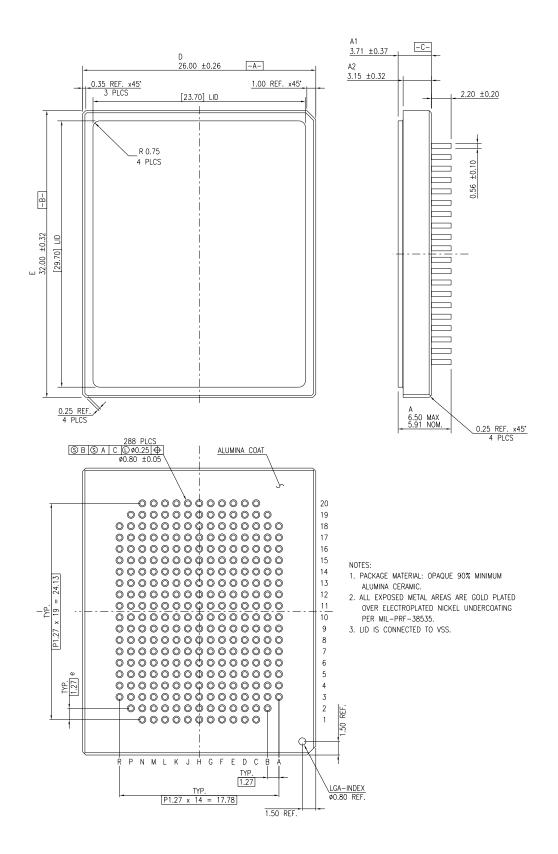

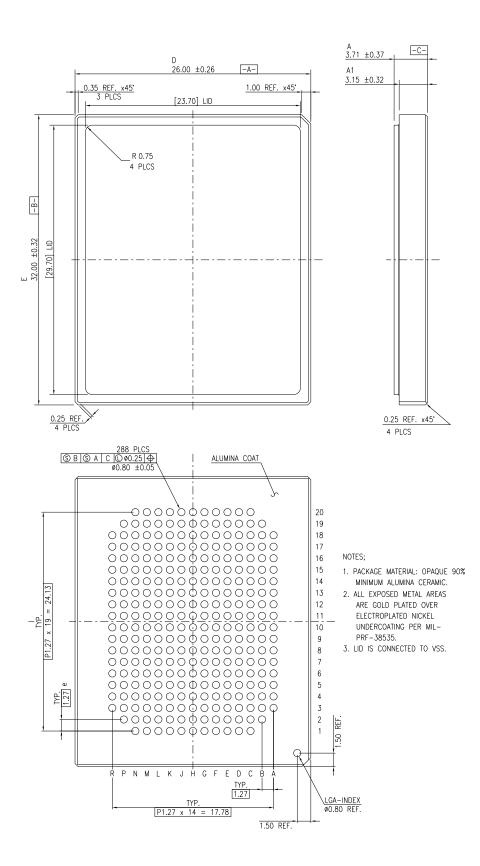

## PACKAGING

Figure 9. 288-Lead CCGA

PACKAGING

Figure 10. 288-Lead CLGA

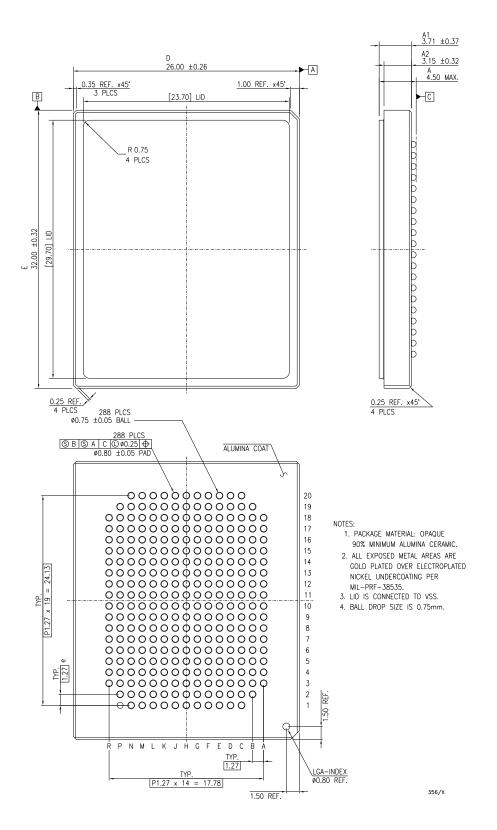

Figure 11. Advanced 288-lead CBGA, Ball dimensions (A, A1, A2) are subject to change

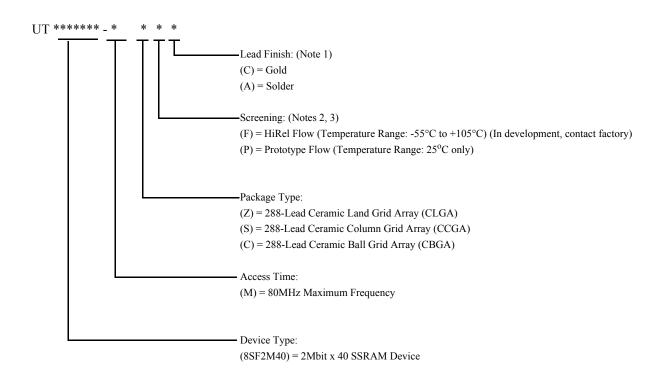

## **ORDERING INFORMATION**

## 2M x 40 SSRAM

- **Notes:** 1. Lead finish is per the table below.

- Prototype Flow per Aeroflex Manufacturing Flows Document. Devices are tested at 25°C only. Radiation is neither tested nor guaranteed.

HiRel flow per Aeroflex Manufacturing Flows Document. Radiation is neither tested nor guaranteed.

| Package Option | Associated Lead Finish Option |

|----------------|-------------------------------|

| (Z) 288-CLGA   | (C) Gold                      |

| (S) 288-CCGA   | (A) Hot Solder Dipped         |

| (C) 288-CBGA   | (A) Hot Solder Dipped         |

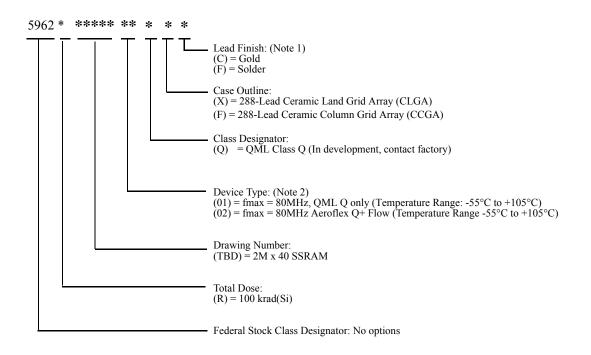

### 2M x 40 SSRAM: SMD

#### Notes:

1. Lead finish is per the table below.

2. Aeroflex's Q+ assembly flow, as defined in section 4.2.2.d of the SMD, provides QML-Q product through the SMD that is manufactured with Aeroflex's QML-V flow.

| Package Option | Associated Lead Finish Option |

|----------------|-------------------------------|

| (X) 288-CLGA   | (C) Gold                      |

| (F) 288-CCGA   | (F) Hot Solder Dipped         |

Aeroflex Colorado Springs - Datasheet Definition

Advanced Datasheet - Product In Development

Preliminary Datasheet - Shipping Prototype

Datasheet - Shipping QML & Reduced Hi-Rel

This product is controlled for export under the U.S. Department of Commerce (DoC). A license may be required prior to the export of this product from the United States.

# **Description of Change History**

| Revision Date               | Description of Change             |

|-----------------------------|-----------------------------------|

| April 2015<br>Version 1.0.0 | Release of Preliminary Data Sheet |