## **RS-485 Transceivers with Low-Voltage** Logic Interface

#### **General Description**

The MAX13430E-MAX13433E are full- and half-duplex RS-485 transceivers that feature an adjustable low-voltage logic interface for operation in multivoltage systems. This allows direct interfacing to low-voltage ASIC/FPGAs without extra components. The MAX13430E-MAX13433E RS-485 transceivers operate with a V<sub>CC</sub> voltage supply from +3V to +5V. The low-voltage logic interface operates with a voltage supply from +1.62V to V<sub>CC</sub>.

The MAX13430E/MAX13432E feature reduced slewrate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 500kbps. The MAX13431E/MAX13433E driver slew rates are not limited, enabling data transmission up to 16Mbps. The MAX13430E/MAX13431E are intended for half-duplex communications, and the MAX13432E/MAX13433E are intended for full-duplex communications.

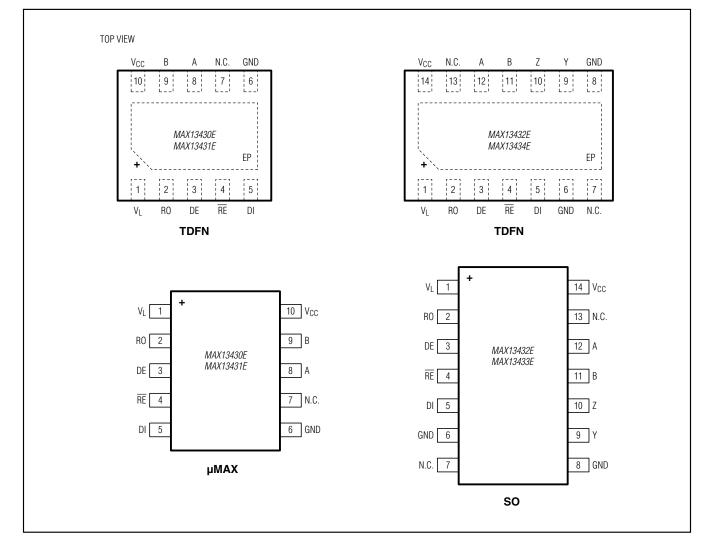

The MAX13430E/MAX13431E are available in 10-pin µMAX® and 10-pin TDFN packages. The MAX13432E/ MAX13433E are available in 14-pin TDFN and 14-pin SO packages.

| Industrial Control Systems | Motor C |

|----------------------------|---------|

| Portable Industrial        | HVAC    |

| Equipment                  |         |

#### **Applications**

ontrol

#### Wide +3V to +5V Input Supply Range

- Low-Voltage Logic Interface +1.62V (min)

- Ultra-Low Supply Current in Shutdown Mode 10µA ICC (max), 1µA IL (max)

Features

- Thermal Shutdown Protection

- Hot-Swap Input Structures on DE and RE

- 1/8-Unit Load Allows Up to 256 Transceivers on the Bus

- Enhanced Slew-Rate Limiting (MAX13430E/MAX13432E)

- Extended ESD Protection for RS-485 I/O Pins ±30kV Human Body Model ±15kV Air-Gap Discharge per IEC 61000-4-2 ±10kV Contact Discharge per IEC 61000-4-2

- Extended -40°C to +85°C Operating Temperature Range

- Space-Saving TDFN and µMAX Packages

Typical Application Circuits appears at end of data sheet.

| PART            | PIN-PACKAGE                | FULL/HALF<br>DUPLEX | DATA RATE<br>(Mbps) | SLEW RATE<br>LIMITED | TRANSCEIVERS<br>ON BUS | TOP<br>MARK | PACKAGE<br>CODE |

|-----------------|----------------------------|---------------------|---------------------|----------------------|------------------------|-------------|-----------------|

| MAX13430EETB+   | 10 TDFN-EP*<br>(3mm x 3mm) | Half                | 0.5                 | Yes                  | 256                    | AUS         | T1033-1         |

| MAX13430EEUB+   | 10 µMAX<br>(3mm x 3mm)     | Half                | 0.5                 | Yes                  | 256                    | _           | U10-2           |

| MAX13431EETB+   | 10 TDFN-EP*<br>(3mm x 3mm) | Half                | 16                  | No                   | 256                    | AUT         | T1033-1         |

| MAX13431EEUB+   | 10 µMAX<br>(3mm x 3mm)     | Half                | 16                  | No                   | 256                    | _           | U10-2           |

| MAX13432EESD+   | 14 SO                      | Full                | 0.5                 | Yes                  | 256                    | _           | S14-1           |

| MAX13432EETD+   | 14 TDFN-EP*<br>(3mm x 3mm) | Full                | 0.5                 | Yes                  | 256                    | AEG         | T1433-2         |

| MAX13433EESD+   | 14 SO                      | Full                | 16                  | No                   | 256                    | _           | S14-1           |

| MAX13433EESD/V+ | 14 SO                      | Full                | 16                  | No                   | 256                    | —           | S14-1           |

| MAX13433EETD+   | 14 TDFN-EP*<br>(3mm x 3mm) | Full                | 16                  | No                   | 256                    | AEH         | T1433-2         |

#### **Ordering Information/Selector Guide**

Note: All devices are specified over the extended -40°C to +85°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

<sup>\*</sup>EP = Exposed pad.

N denotes an automotive qualified part.

### **RS-485 Transceivers with Low-Voltage Logic Interface**

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)           |              |

|---------------------------------------------|--------------|

| Supply Voltage (V <sub>CC</sub> )           | -0.3V to +6V |

| Logic Supply Voltage (VL)                   | -0.3V to +6V |

| Control Input Voltage (RE)0.3V              | to (VL+0.3V) |

| Control Input Voltage (DE)                  |              |

| Driver Input Voltage (DI)                   | -0.3V to +6V |

| Driver Output Voltage (Y, Z, A, B)          | 8V to +13V   |

| Receiver Input Voltage (A, B)               |              |

| (MAX13430E/MAX13431E)                       | 8V to +13V   |

| Receiver Input Voltage (A, B)               |              |

| (MAX13432E/MAX13433E)                       | 25V to +25V  |

| Receiver Output Voltage (RO)0.3V to         |              |

| Driver Output Current                       |              |

| Short-Circuit Duration (RO, A, B) to GND    | Continuous   |

| Power Dissipation ( $T_A = +70^{\circ}C$ )  |              |

| 10-Pin µMAX (derate 8.8mW/°C above +70°C)   | 707mW        |

| 10-Pin TDFN (derate 24.4mW/°C above +70°C). | 1951mW       |

| 14-Pin TDFN (derate 24.4mW/°C above +70°<br>14-Pin SO (derate 11.9mW/°C above +70°C)<br>Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) ( |                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 10-Pin μMAX                                                                                                                                        | 113.1°C/W       |

| 10-Pin TDFN                                                                                                                                        | 41°C/W          |

| 14-Pin TDFN                                                                                                                                        | 41°C/W          |

| 14-Pin SO                                                                                                                                          | 84°C/W          |

| Junction-to-Ambient Thermal Resistance $(\theta_{JC})$ (                                                                                           | Note 1)         |

| 10-Pin μMAX                                                                                                                                        | 42°C/W          |

| 10-Pin TDFN                                                                                                                                        | 9°C/W           |

| 14-Pin TDFN                                                                                                                                        |                 |

| 14-Pin SO                                                                                                                                          | 34°C/W          |

| Operating Temperature Range                                                                                                                        | 40°C to +85°C   |

| Junction Temperature                                                                                                                               | +150°C          |

| Storage Temperature Range                                                                                                                          | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                                                                                                                  | +300°C          |

| Soldering Temperature (reflow)                                                                                                                     | +260°C          |

|                                                                                                                                                    |                 |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3V \text{ to } +5.5V, V_{L} = +1.8V \text{ to } V_{CC}, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are } V_{CC} = +5V, V_{L} = +1.8V \text{ at } T_{A} = +25^{\circ}\text{C}.)$  (Notes 2, 3)

| PARAMETER                                             | SYMBOL           | CONDITIONS                                                                                                               |      | ТҮР                | MAX             | UNITS |  |

|-------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----------------|-------|--|

| POWER SUPPLY                                          |                  |                                                                                                                          |      |                    |                 |       |  |

| V <sub>CC</sub> Supply-Voltage Range                  | V <sub>CC</sub>  |                                                                                                                          | 3    |                    | 5.5             | V     |  |

| V <sub>L</sub> Supply-Voltage Range                   | VL               |                                                                                                                          | 1.62 |                    | Vcc             | V     |  |

| ICC Supply Current                                    | lcc              | $DE = \overline{RE} = high, no load$<br>$DE = \overline{RE} = low, no load$<br>$DE = high, \overline{RE} = low, no load$ |      |                    | 2               | mA    |  |

| I <sub>CC</sub> Supply Current in Shutdown<br>Mode    | ISHDN            | $DE = Iow, \overline{RE} = high, no load$                                                                                |      |                    | 10              | μΑ    |  |

| V <sub>L</sub> Supply Current                         | ١L               | RO = no load                                                                                                             |      |                    | 1               | μΑ    |  |

| DRIVER                                                |                  |                                                                                                                          | -    |                    |                 |       |  |

|                                                       |                  | $R_{L} = 100\Omega, V_{CC} = +3V$                                                                                        | 2    |                    | Vcc             |       |  |

| Differential Driver Output                            |                  | $R_L = 54\Omega$ , $V_{CC} = +3V$                                                                                        |      |                    | VCC             | v     |  |

| (Figure 1)                                            | VOD              | $R_L = 100\Omega, V_{CC} = +4.5V$                                                                                        | 2.25 |                    | Vcc             |       |  |

|                                                       |                  | $R_L = 54\Omega, V_{CC} = +4.5V$ 2.25                                                                                    |      |                    | V <sub>CC</sub> |       |  |

| Change in Magnitude of<br>Differential Output Voltage | $\Delta V_{OD}$  | $R_L = 100\Omega$ or 54 $\Omega$ , Figure 1 (Note 4)                                                                     |      |                    | 0.2             | V     |  |

| Driver Common-Mode Output<br>Voltage                  | V <sub>OC</sub>  | $R_L = 100\Omega$ or 54 $\Omega$ , Figure 1                                                                              |      | V <sub>CC</sub> /2 | 3               | V     |  |

| Change in Magnitude of<br>Common-Mode Voltage         | ΔV <sub>OC</sub> | $R_L = 100\Omega$ or 54 $\Omega$ , Figure 1 (Note 4)                                                                     |      | 0.2                | V               |       |  |

### **RS-485 Transceivers with Low-Voltage** Logic Interface

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3V \text{ to } +5.5V, V_L = +1.8V \text{ to } V_{CC}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are V_{CC} = +5V, V_L = +1.8V \text{ at } T_A = +25^{\circ}\text{C}.)$  (Notes 2, 3)

| PARAMETER                                     | SYMBOL               | CONDITIONS                                    |                 | MIN         | ТҮР  | MAX         | UNITS |  |

|-----------------------------------------------|----------------------|-----------------------------------------------|-----------------|-------------|------|-------------|-------|--|

| Output Leakage Current                        |                      | DE = GND,                                     | $V_{IN} = +12V$ |             |      | 125         |       |  |

| (Y and Z)                                     | IOLK                 | $V_{CC} = V_{GND} \text{ or } +5.5V$          | $V_{IN} = -7V$  | -100        |      |             | μA    |  |

| Driver Short-Circuit Output                   | les-                 | $0 \le V_{OUT} \le +12V$                      |                 |             |      | +250        |       |  |

| Current (Note 5)                              | IOSD                 | $-7V \le V_{OUT} \le V_{CC}$                  |                 | -250        |      |             | mA    |  |

| Driver Short-Circuit Output                   |                      | $(V_{CC} - 1V) \le V_{OUT} \le +12$           | 2V              | 15          |      |             |       |  |

| Foldback Current (Note 5)                     | IOSDF                | $-7V \le V_{OUT} \le +1V$                     |                 |             |      | -15         | mA    |  |

| Thermal Shutdown Threshold                    | T <sub>TS</sub>      |                                               |                 |             | +150 |             | °C    |  |

| Thermal Shutdown Hysteresis                   | T <sub>TSH</sub>     |                                               |                 |             | 15   |             | °C    |  |

| RECEIVER                                      |                      |                                               |                 |             |      |             |       |  |

| Input Current (A and D)                       |                      | DE = GND,                                     | $V_{CM} = +12V$ |             |      | 125         |       |  |

| Input Current (A and B)                       | IA, B                | $V_{CC} = V_{GND} \text{ or } +5.5V$          | $V_{CM} = -7V$  | -100        |      |             | μA    |  |

| Receiver Differential Threshold Voltage       | V <sub>TH</sub>      | $-7V \le V_{CM} \le +12V$                     |                 | -200        |      | -50         | mV    |  |

| Receiver Input Hysteresis                     | $\Delta V_{TH}$      | $V_{CM} = 0$                                  |                 |             | 15   |             | mV    |  |

| Receiver Input Resistance                     | RIN                  | $-7V \le V_{CM} \le +12V$                     |                 | 96          |      |             | kΩ    |  |

| LOGIC INTERFACE                               |                      |                                               |                 |             |      |             |       |  |

| Input High Logic Level<br>(DI, DE, RE)        | VIH                  |                                               |                 | 2/3 x<br>VL |      |             | V     |  |

| Input Low Logic Level<br>(DI, DE, RE)         | VIL                  |                                               |                 |             |      | 1/3 x<br>VL | V     |  |

| Input Current (DI, DE, RE)                    | l <sub>IN</sub>      | $V_{DI} = V_{DE} = V_{\overline{RE}} = V_L =$ | +5.5V           |             |      | ±1          | μA    |  |

| Input Impedance on First<br>Transition        | R <sub>DE</sub> , RE |                                               |                 | 1           |      | 10          | kΩ    |  |

| Output High Logic Level (RO)                  | Voh                  | $I_{O} = -1 mA$ , $V_{A} - V_{B} = V_{T}$     | ΓH              | VL - 0.4    |      |             | V     |  |

| Output Low Logic Level (RO)                   | Vol                  | $I_{O} = 1 m A, V_{A} - V_{B} = -V_{T}$       | ſH              |             |      | 0.4         | V     |  |

| Receiver Three-State Output<br>Current (RO)   | I <sub>OZR</sub>     | $0 \le V_{RO} \le V_L$                        |                 | -1          | 0.01 | +1          | μA    |  |

| Receiver Output Short-Circuit<br>Current (RO) | IOSR                 | $0 \le V_{RO} \le V_L$                        |                 | -110        |      | +110        | mA    |  |

| ESD PROTECTION                                |                      |                                               |                 |             |      |             |       |  |

|                                               |                      | IEC 61000-4-2 Air Gap                         | Discharge       |             | ±15  |             |       |  |

| A, B, Y, Z to GND                             |                      | IEC 61000-4-2 Contact                         | Discharge       |             | ±10  |             | kV    |  |

|                                               |                      | Human Body Model                              |                 |             | ±30  |             |       |  |

| All Other Pins<br>(Except A, B, Y, and Z)     |                      | Human Body Model                              |                 |             | ±2   |             | kV    |  |

### **RS-485 Transceivers with Low-Voltage Logic Interface**

#### SWITCHING CHARACTERISTICS (MAX13431E/MAX13433E (16Mbps))

(V<sub>CC</sub> = +3V to +5.5V, V<sub>L</sub> = +1.8V to V<sub>CC</sub>, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are V<sub>CC</sub> = +5V, V<sub>L</sub> = +1.8V at T<sub>A</sub> = +25°C.) (Notes 2, 3)

| PARAMETER                                          | SYMBOL                                                     | CONDITIONS                                          | MIN | ТҮР | MAX | UNITS |  |

|----------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|-------|--|

| DRIVER                                             |                                                            |                                                     |     |     |     |       |  |

| Driver Propagation Delay                           | t <sub>DPLH</sub>                                          |                                                     |     |     | 50  | 20    |  |

| (Figures 2 and 3)                                  | $C_L = 50 \text{ pF}, \text{ R}_{\text{DIFF}} = 54 \Omega$ |                                                     |     |     | 50  | ns    |  |

| Driver Differential Output Rise or Fall Time       | t <sub>R</sub> , t <sub>F</sub>                            | $C_L$ = 50pF, $R_L$ = 54 $\Omega$ , Figures 2 and 3 |     |     | 15  | ns    |  |

| Differential Driver Output Skew<br>ItDPLH - tDPHLI | t <sub>DSKEW</sub>                                         | $C_L$ = 50pF, $R_L$ = 54 $\Omega$ , Figures 2 and 3 |     |     | 8   | ns    |  |

| Maximum Data Rate                                  |                                                            |                                                     | 16  |     |     | Mbps  |  |

| Driver Enable to Output High                       | t <sub>DZH</sub>                                           | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 4       |     |     | 150 | ns    |  |

| Driver Enable to Output Low                        | t <sub>DZL</sub>                                           | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 5       |     |     | 150 | ns    |  |

| Driver Disable Time from Low                       | tDLZ                                                       | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 4       |     |     | 100 | ns    |  |

| Driver Disable Time from High                      | t <sub>DHZ</sub>                                           | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 5       |     |     | 120 | ns    |  |

| Driver Enable from Shutdown<br>to Output High      | tDZH(SHDN)                                                 | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 4       |     |     | 5   | μs    |  |

| Driver Enable from Shutdown to Output Low          | t <sub>DZL(SHDN)</sub>                                     | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 5       |     |     | 5   | μs    |  |

| RECEIVER                                           | •                                                          |                                                     | •   |     |     |       |  |

| Receiver Propagation Delay                         | t <sub>RPLH</sub>                                          |                                                     |     |     | 80  |       |  |

| (Figures 6 and 7)                                  | <b>t</b> RPHL                                              | $C_L = 15pF$                                        |     |     | 80  | ns    |  |

| Receiver Output Skew                               | <b>t</b> RSKEW                                             | $C_L = 15 pF$ , Figures 6 and 7                     |     |     | 13  | ns    |  |

| Maximum Data Rate                                  |                                                            |                                                     | 16  |     |     | Mbps  |  |

| Receiver Enable to Output Low                      | t <sub>RZL</sub>                                           | Figure 8                                            |     |     | 50  | ns    |  |

| Receiver Enable to Output High                     | t <sub>RZH</sub>                                           | Figure 8                                            |     |     | 50  | ns    |  |

| Receiver Disable Time from Low                     | t <sub>RLZ</sub>                                           | Figure 8                                            |     |     | 50  | ns    |  |

| Receiver Disable Time from High                    | t <sub>RHZ</sub>                                           | Figure 8                                            |     |     | 50  | ns    |  |

| Receiver Enable from<br>Shutdown to Output High    | <sup>t</sup> RZH(SHDN)                                     | Figure 8                                            |     |     | 5   | μs    |  |

| Receiver Enable from<br>Shutdown to Output Low     | trzl(SHDN)                                                 | Figure 8                                            |     |     | 5   | μs    |  |

| DRIVER/RECEIVER                                    |                                                            | ·                                                   | · · |     |     | •     |  |

| Time to Shutdown                                   | <b>t</b> SHDN                                              |                                                     | 50  | 340 | 700 | ns    |  |

## **RS-485 Transceivers with Low-Voltage** Logic Interface

#### SWITCHING CHARACTERISTICS (MAX13430E/MAX13432E (500kbps))

(V<sub>CC</sub> = +3V to +5.5V,  $V_L$  = +1.8V to V<sub>CC</sub>,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are  $V_{CC}$  = +5V,  $V_L$  = +1.8V at  $T_A$  = +25°C.) (Notes 2, 3)

| PARAMETER                                          | SYMBOL                          | CONDITIONS                                           | MIN | ТҮР | MAX        | UNITS |

|----------------------------------------------------|---------------------------------|------------------------------------------------------|-----|-----|------------|-------|

| DRIVER                                             |                                 | ·                                                    | •   |     |            | •     |

| Driver Propagation Delay                           | t <sub>DPLH</sub>               | $C_{L} = 50 pF, R_{L} = 54 \Omega$                   | 180 |     | 800        | 20    |

| (Figures 2 and 3)                                  | <b>t</b> DPHL                   | $C_{L} = 50 \text{pr},  \text{R}_{L} = 54 \text{sz}$ | 180 |     | 800        | ns    |

| Driver Differential Output Rise or<br>Fall Time    | t <sub>R</sub> , t <sub>F</sub> | $C_L$ = 50pF, $R_L$ = 54 $\Omega,$ Figures 2 and 3   | 200 |     | 800        | ns    |

| Differential Driver Output Skew<br>ItDPLH - tDPHLI | <b>t</b> DSKEW                  | $C_L$ = 50pF, $R_L$ = 54 $\Omega$ , Figures 2 and 3  |     |     | 100        | ns    |

| Maximum Data Rate                                  |                                 |                                                      | 500 |     |            | kbps  |

| Driver Enable to Output High                       | tdzh                            | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 4        |     |     | 2.5        | μs    |

| Driver Enable to Output Low                        | t <sub>DZL</sub>                | $C_L$ = 50pF, $R_L$ = 500 $\Omega$ , Figure 5        |     |     | 2.5        | μs    |

| Driver Disable Time from Low                       | tDLZ                            | $C_L$ = 50pF, $R_L$ = 500 $\Omega$ , Figure 4        |     |     | 100        | ns    |

| Driver Disable Time from High                      | t <sub>DHZ</sub>                | $C_L$ = 50pF, $R_L$ = 500 $\Omega$ , Figure 5        |     |     | 120        | ns    |

| Driver Enable from Shutdown to Output High         | tDZH(SHDN)                      | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 4        |     |     | 5          | μs    |

| Driver Enable from Shutdown to Output Low          | t <sub>DZL</sub> (SHDN)         | $C_L = 50 pF$ , $R_L = 500 \Omega$ , Figure 5        |     |     | 5          | μs    |

| RECEIVER                                           | 1                               |                                                      |     |     |            |       |

| Receiver Propagation Delay<br>(Figures 6 and 7)    | t <sub>RPLH</sub>               | C <sub>L</sub> = 15pF                                |     |     | 200<br>200 | ns    |

| Receiver Output Skew                               | <b>t</b> RSKEW                  | $C_L = 15 pF$ , Figures 6 and 7                      |     |     | 30         | ns    |

| Maximum Data Rate                                  |                                 |                                                      | 500 |     |            | kbps  |

| Receiver Enable to<br>Output Low                   | t <sub>RZL</sub>                | Figure 8                                             |     |     | 50         | ns    |

| Receiver Enable to<br>Output High                  | trzh                            | Figure 8                                             |     |     | 50         | ns    |

| Receiver Disable Time<br>from Low                  | t <sub>RLZ</sub>                | Figure 8                                             |     |     | 50         | ns    |

| Receiver Disable Time<br>from High                 | t <sub>RHZ</sub>                | Figure 8                                             |     |     | 50         | ns    |

| Receiver Enable from<br>Shutdown to Output High    | t <sub>RZH</sub> (SHDN)         | Figure 8                                             |     |     | 5          | μs    |

| Receiver Enable from<br>Shutdown to Output Low     | trzl(SHDN)                      | Figure 8                                             |     |     | 5          | μs    |

## **RS-485 Transceivers with Low-Voltage Logic Interface**

#### SWITCHING CHARACTERISTICS (MAX13430E/MAX13432E (500kbps)) (continued)

(V<sub>CC</sub> = +3V to +5.5V, V<sub>L</sub> = +1.8V to V<sub>CC</sub>, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are V<sub>CC</sub> = +5V, V<sub>L</sub> = +1.8V at T<sub>A</sub> = +25°C.) (Notes 2, 3)

| PARAMETER                                                                                                                                        | SYMBOL        | CONDITIONS | MIN | ТҮР | МАХ | UNITS |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|-----|-----|-----|-------|--|

| DRIVER/RECEIVER                                                                                                                                  |               |            |     |     |     |       |  |

| Time to Shutdown                                                                                                                                 | <b>t</b> SHDN |            | 50  | 340 | 700 | ns    |  |

| <b>Note 2:</b> Parameters are 100% production tested at $T_A = +25^{\circ}C$ , unless otherwise noted. Limits over temperature are guaranteed by |               |            |     |     |     |       |  |

design.Note 3: All currents into the device are positive. All currents out of the device are negative. All voltages are referenced to device ground, unless otherwise noted.

Note 4:  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the DI input changes state.

Note 5: The short-circuit output current is the peak current just prior to current limiting; the short-circuit foldback output current applies during current limiting to allow a recovery from bus contention.

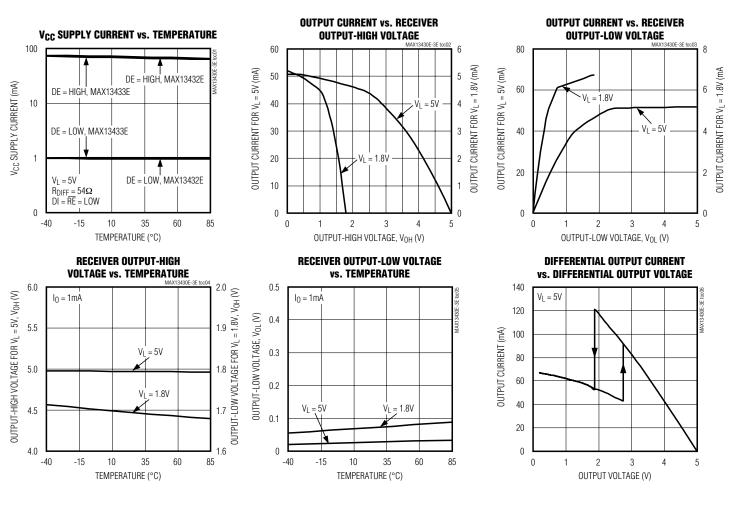

$(V_{CC} = +5V, V_L = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteriststics**

Maxim Integrated

6

#### **Typical Operating Characteristics (continued)**

$(V_{CC} = +5V, V_L = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

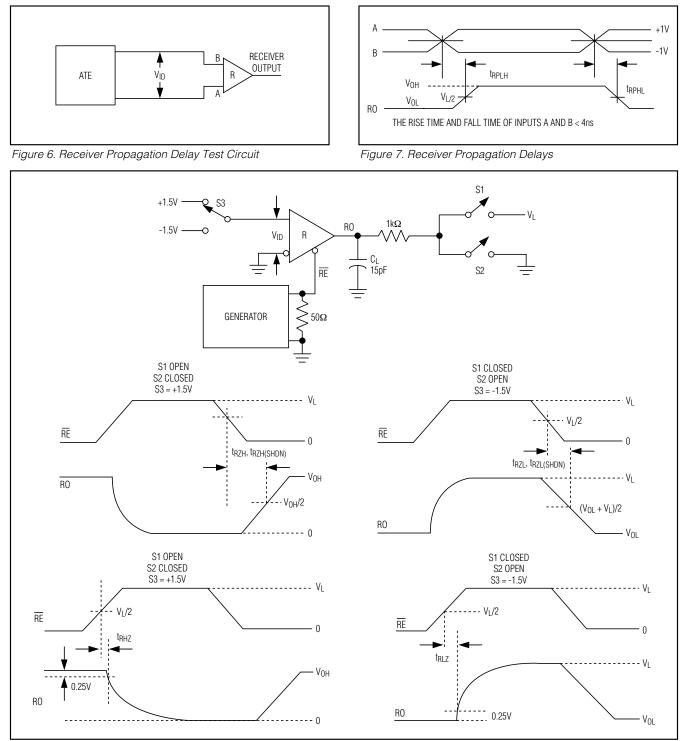

### **RS-485 Transceivers with Low-Voltage Logic Interface**

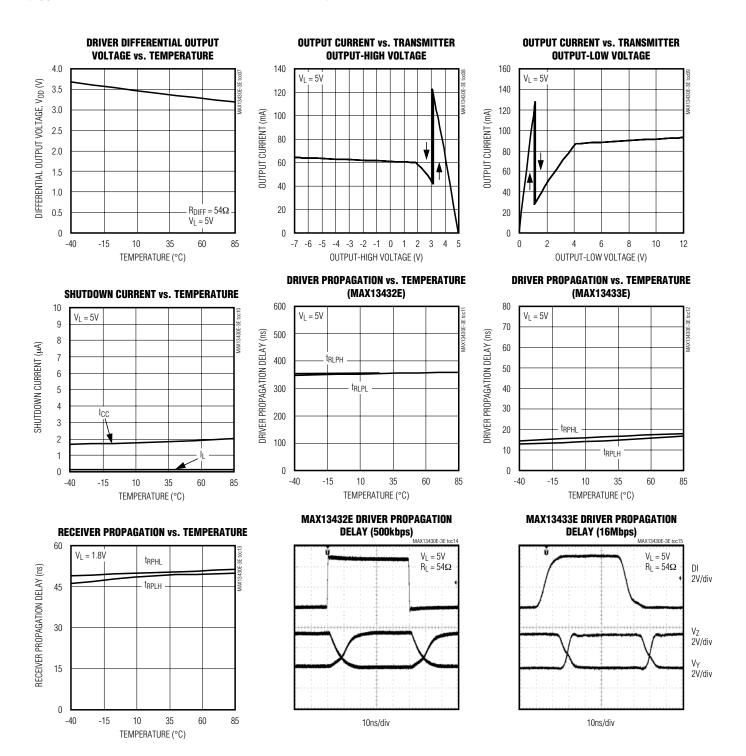

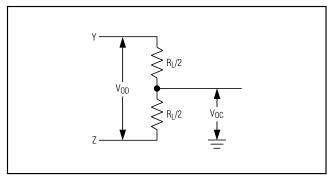

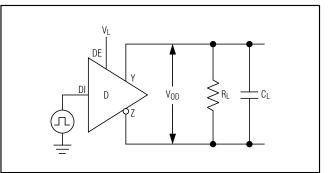

Figure 1. Driver DC Test Load

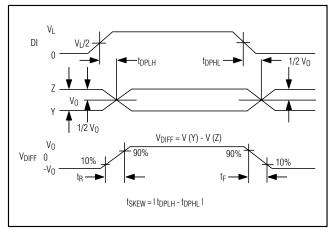

Figure 3. Driver Propagation Delays

#### **Test Circuits and Waveforms**

Figure 2. Driver Timing Test Circuit

### **RS-485 Transceivers with Low-Voltage** Logic Interface

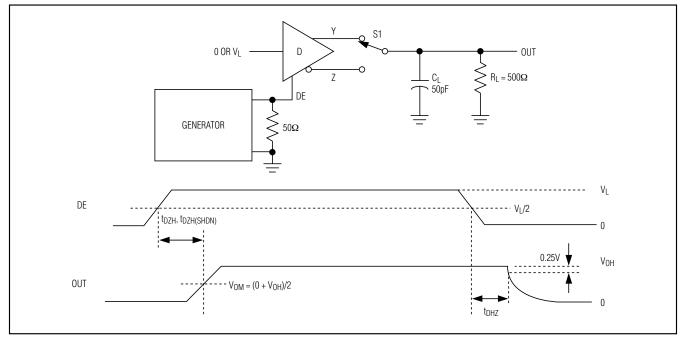

### Test Circuits and Waveforms (continued)

Figure 4. Driver Enable and Disable Times (t<sub>DHZ</sub>, t<sub>DZH</sub>, and t<sub>DZH(SHDN)</sub>)

Figure 5. Driver Enable and Disable Times (t<sub>DZL</sub>, t<sub>DLZ</sub>, and t<sub>DZL(SHDN)</sub>)

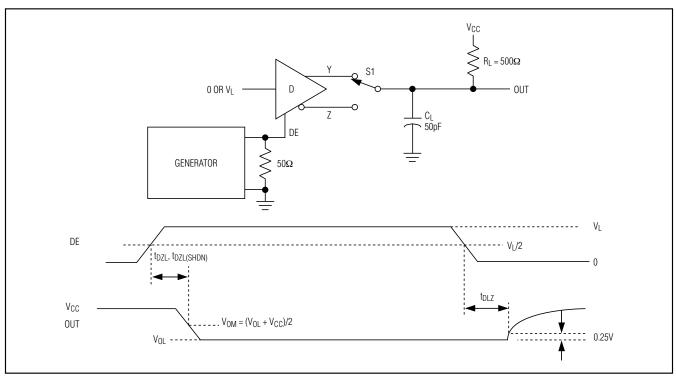

# **RS-485 Transceivers with Low-Voltage Logic Interface**

Test Circuits and Waveforms (continued)

Figure 8. Receiver Enable and Disable Times

### **RS-485 Transceivers with Low-Voltage** Logic Interface

#### \_Pin Configurations

# **RS-485 Transceivers with Low-Voltage Logic Interface**

#### Pin Description

| PIN                                                                  |                                      |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX13430E                                                            | MAX13430E/MAX13431E NAME   μMAX TDFN |                                                                                                                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                            |  |  |

| μΜΑΧ                                                                 |                                      |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                     |  |  |

| 1                                                                    | 1                                    | VL                                                                                                                                                                                                                                                                             | $V_L$ Input Logic-Supply Voltage. Bypass $V_L$ with a 0.1 $\mu F$ ceramic capacitor located as close as possible to the input.                                                                                                                                                                      |  |  |

| 2                                                                    | 2                                    | RO                                                                                                                                                                                                                                                                             | Receiver Output. When $\overline{RE}$ is low and if (A - B) $\geq$ -50mV, RO is high; if (A - B) $\leq$ -200mV, RO is low.                                                                                                                                                                          |  |  |

| 3 3 DE impedance when DE is low. Drive RE high and DE low to enter l |                                      | Driver Output Enable. Drive DE high to enable driver outputs. These outputs are high impedance when DE is low. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode. DE is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details.) |                                                                                                                                                                                                                                                                                                     |  |  |

| 4                                                                    | 4                                    | RE                                                                                                                                                                                                                                                                             | Active-Low Receiver Output Enable. Drive $\overline{RE}$ low to enable RO; RO is high impedance when $\overline{RE}$ is high. Drive $\overline{RE}$ high and DE low to enter low-power shutdown mode. $\overline{RE}$ is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details.) |  |  |

| 5                                                                    | 5                                    | DI                                                                                                                                                                                                                                                                             | Driver Input. With DE high, a low on DI forces noninverting output low and inverting output high. Similarly, a high on DI forces noninverting output high and inverting output low.                                                                                                                 |  |  |

| 6                                                                    | 6                                    | GND                                                                                                                                                                                                                                                                            | Ground                                                                                                                                                                                                                                                                                              |  |  |

| 7                                                                    | 7                                    | N.C.                                                                                                                                                                                                                                                                           | No Connection. Not internally connected. N.C. can be connected to GND.                                                                                                                                                                                                                              |  |  |

| 8                                                                    | 8                                    | А                                                                                                                                                                                                                                                                              | Noninverting Receiver Input and Noninverting Driver Output                                                                                                                                                                                                                                          |  |  |

| 9                                                                    | 9                                    | В                                                                                                                                                                                                                                                                              | Inverting Receiver Input and Inverting Driver Output                                                                                                                                                                                                                                                |  |  |

| 10                                                                   | 10                                   | $V_{CC}$ Input Supply Voltage. Bypass $V_{CC}$ with a 1µF ceramic capacitor located as as possible to the input for full ESD protection. If full ESD protection is not require bypass $V_{CC}$ with a 0.1µF ceramic capacitor.                                                 |                                                                                                                                                                                                                                                                                                     |  |  |

| _                                                                    | —                                    | EP                                                                                                                                                                                                                                                                             | Exposed Pad (TDFN Only). Connect EP to GND.                                                                                                                                                                                                                                                         |  |  |

## **RS-485 Transceivers with Low-Voltage** Logic Interface

### \_Pin Description (continued)

| PIN       |                     |                 |                                                                                                                                                                                                                                                                                                     |  |  |

|-----------|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX13432E | MAX13432E/MAX13433E |                 | FUNCTION                                                                                                                                                                                                                                                                                            |  |  |

| SO        | TDFN                |                 |                                                                                                                                                                                                                                                                                                     |  |  |

| 1         | 1                   | VL              | $V_L$ Input Logic Supply Voltage. Bypass $V_L$ with a 0.1 $\mu F$ ceramic capacitor located as close as possible to the input.                                                                                                                                                                      |  |  |

| 2         | 2                   | RO              | Receiver Output. When $\overline{RE}$ is low and if (A - B) $\geq$ -50mV, RO is high; if (A - B) $\leq$ -200mV, RO is low.                                                                                                                                                                          |  |  |

| 3         | 3                   | DE              | Driver Output Enable. Drive DE high to enable driver outputs. These outputs are high impedance when DE is low. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode. DE is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details.)                      |  |  |

| 4         | 4                   | RE              | Active-Low Receiver Output Enable. Drive $\overline{RE}$ low to enable RO; RO is high impedance when $\overline{RE}$ is high. Drive $\overline{RE}$ high and DE low to enter low-power shutdown mode. $\overline{RE}$ is a hot-swap input (see the <i>Hot-Swap Capability</i> section for details.) |  |  |

| 5         | 5                   | DI              | Driver Input. With DE high, a low on DI forces noninverting output low and inverting output high. Similarly, a high on DI forces noninverting output high and inverting output low.                                                                                                                 |  |  |

| 6         | 6                   | GND             | Ground                                                                                                                                                                                                                                                                                              |  |  |

| 7, 13     | 7, 13               | N.C.            | No Connection. Not internally connected. N.C. can be connected to GND.                                                                                                                                                                                                                              |  |  |

| 8         | 8                   | GND             | Ground                                                                                                                                                                                                                                                                                              |  |  |

| 9         | 9                   | Y               | Noninverting Driver Output                                                                                                                                                                                                                                                                          |  |  |

| 10        | 10                  | Z               | Inverting Driver Output                                                                                                                                                                                                                                                                             |  |  |

| 11        | 11                  | В               | Inverting Receiver Input                                                                                                                                                                                                                                                                            |  |  |

| 12        | 12                  | А               | Noninverting Receiver Input                                                                                                                                                                                                                                                                         |  |  |

| 14        | 14                  | V <sub>CC</sub> | $V_{CC}$ Input Supply Voltage. Bypass $V_{CC}$ with a 1µF ceramic capacitor located as close as possible to the input for full ESD protection. If full ESD protection is not required, bypass $V_{CC}$ with a 0.1µF ceramic capacitor.                                                              |  |  |

| _         | _                   | EP              | Exposed Pad (TDFN Only). Connect EP to GND.                                                                                                                                                                                                                                                         |  |  |

## **RS-485 Transceivers with Low-Voltage Logic Interface**

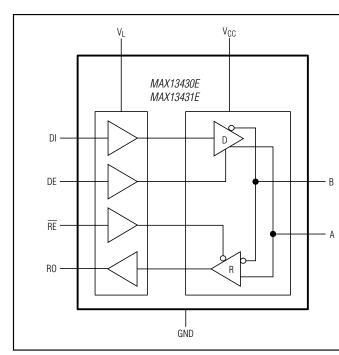

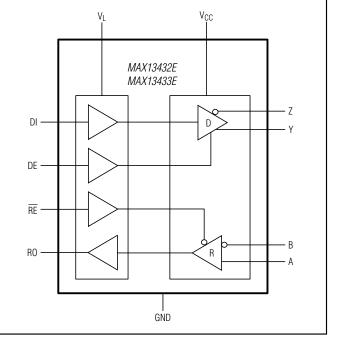

### Function Tables and Functional Diagrams

#### MAX13432E/MAX13433E (Full Duplex)

| TRANSMITTING |        |                  |                    |                    |  |  |

|--------------|--------|------------------|--------------------|--------------------|--|--|

|              | INPUTS |                  | OUTPUTS            |                    |  |  |

| RE           | DE     | DI               | Z                  | Y                  |  |  |

| Х            | 1      | 1                | 0                  | 1                  |  |  |

| Х            | 1      | 0                | 1                  | 0                  |  |  |

| 0            | 0      | Х                | High-<br>Impedance | High-<br>Impedance |  |  |

| 1            | 0      | Х                | Shutdown           |                    |  |  |

|              |        |                  |                    |                    |  |  |

|              |        | RECEI            | VING               |                    |  |  |

|              | INPUTS |                  | Ουτ                | PUT                |  |  |

| RE           | DE     | A-B              | R                  | 0                  |  |  |

| 0            | Х      | ≥ -50mV          | -                  | 1                  |  |  |

| 0            | Х      | ≤-200mV          | 0                  |                    |  |  |

| 0            | Х      | Open/<br>Shorted | 1                  |                    |  |  |

| 1            | 1      | Х                | High-Impedance     |                    |  |  |

| 1            | 0      | Х                | Shute              | down               |  |  |

#### MAX13430E/MAX13431E (Half Duplex)

| TRANSMITTING |           |                  |                    |                    |  |  |  |

|--------------|-----------|------------------|--------------------|--------------------|--|--|--|

| INPUTS       |           |                  | OUTPUTS            |                    |  |  |  |

| RE           | DE        | DI               | В                  | А                  |  |  |  |

| Х            | 1         | 1                | 0                  | 1                  |  |  |  |

| Х            | 1         | 0                | 1                  | 0                  |  |  |  |

| 1            | 0         | х                | High-<br>Impedance | High-<br>Impedance |  |  |  |

| 0            | 0         | Х                | Shutdown*          |                    |  |  |  |

|              |           |                  |                    |                    |  |  |  |

|              | RECEIVING |                  |                    |                    |  |  |  |

| INPUTS       |           |                  | OUTPUT             |                    |  |  |  |

| RE           | DE        | A-B              | RO                 |                    |  |  |  |

| 0            | Х         | ≥ -50mV          | 1                  |                    |  |  |  |

| 0            | Х         | ≤-200mV          | 0                  |                    |  |  |  |

| 0            | х         | Open/<br>Shorted | 1                  |                    |  |  |  |

| 1            | 1         | Х                | High-Impedance     |                    |  |  |  |

| 1            | 0         | Х                | Shutdown*          |                    |  |  |  |

X = Don't care.

\*Shutdown mode, driver and receiver outputs are in high impedance.

Figure 9. Functional Diagrams

#### **Detailed Description**

The MAX13430E–MAX13433E are full- and half-duplex RS-485 transceivers that feature an adjustable low-voltage logic interface for application in multivoltage systems. This allows direct interfacing to low-voltage ASIC/FPGAs without extra components. The MAX13430E–MAX13433E RS-485 transceivers operate with a V<sub>CC</sub> voltage supply from +3V to +5V. The low-voltage logic interface operates with a voltage supply from +1.62V to V<sub>CC</sub>.

The MAX13430E–MAX13433E are  $\pm$ 30kV ESD-protected RS-485 transceivers with one driver and one receiver. All devices have a 1/8-unit load receiver input impedance, allowing up to 256 transceivers on the bus. These devices include fail-safe circuitry, guaranteeing a logic-high receiver output when receiver inputs are open or shorted. The receivers output a logic-high if all transmitters on a terminated bus are disabled (high impedance). All devices feature hot-swap capability to eliminate false transitions on the bus during power-up or hot insertion.

The MAX13430E/MAX13432E feature reduced slewrate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 500kbps. The MAX13431E/MAX13433E driver slew rates are not limited, enabling data transmission up to 16Mbps.

The MAX13430E–MAX13433E transceivers draw 2mA of supply current when unloaded or when fully loaded with the drivers disabled. The MAX13430E/MAX13431E are intended for half-duplex communications, and the MAX13432E/MAX13433E are intended for full-duplex communications.

#### Low-Voltage Logic Interface

$V_{L}$  is the voltage supply for the low-voltage logic interface and receiver output.  $V_{L}$  operates with voltage supply from +1.62V to  $V_{CC}.$

#### Fail Safe

The MAX13430E family guarantees a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver input threshold between -50mV and -200mV. If the differential receiver input voltage (A - B) is greater than or equal to -50mV, RO is logic-high.

If (A - B) is less than or equal to -200mV, RO is logiclow. In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to 0V by the termination. With the receiver thresholds of the MAX13430E family, this results in a logic-high with a 50mV minimum noise margin. The -50mV to -200mV threshold complies with the ±200mV EIA/TIA/RS-485 standard.

#### **Hot-Swap Capability**

When circuit boards are inserted into a hot or powered backplane, differential disturbances to the data bus can lead to data errors. Upon initial circuit-board insertion, the data communication processor undergoes its own power-up sequence. During this period, the processor's logic-output drivers are high impedance and are unable to drive the DE and RE inputs of these devices to a defined logic level. Leakage currents up to ±10µA from the high-impedance state of the processor's logic drivers could cause standard CMOS enable inputs of a transceiver to drift to an incorrect logic level. Additionally, parasitic circuit-board capacitance could cause coupling of VL or GND to the enable inputs. Without the hot-swap capability, these factors could improperly enable the transceiver's driver or receiver. When VL rises, an internal pulldown circuit holds DE low and RE high. After the initial power-up sequence, the pulldown circuit becomes transparent, resetting the hot-swap tolerable input.

#### ±30kV ESD Protection

ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX13430E family of devices have extra protection against static electricity. Maxim's engineers have developed state-of-theart structures to protect these pins against ESD of  $\pm$ 30kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the MAX13430E–MAX13433E keep working without latchup or damage. ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX13430E–MAX13433E are characterized for protection to the following limits:

- ±30kV using the Human Body Model

- ±10kV using the Contact Discharge method specified in IEC 61000-4-2

- ±15kV using the Air Gap Discharge method specified in IEC 61000-4-2

### **RS-485 Transceivers with Low-Voltage Logic Interface**

#### ESD Test Conditions

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

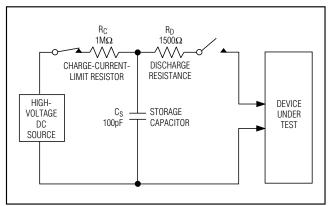

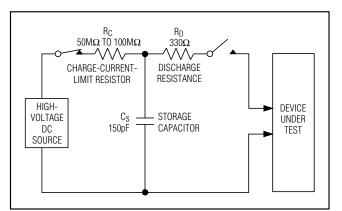

#### Human Body Model

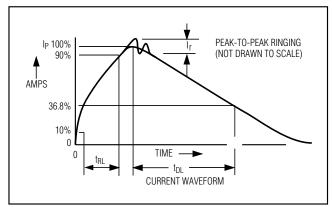

Figure 10a shows the Human Body Model, and Figure 10b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5k\Omega$  resistor.

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does

Figure 10a. Human Body ESD Test Model

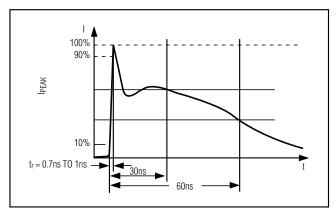

Figure 10c. IEC 61000-4-2 ESD Test Model

not specifically refer to integrated circuits. The MAX13430E family of devices helps you design equipment to meet IEC 61000-4-2, without the need for additional ESD-protection components.

The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 10c shows the IEC 61000-4-2 model, and Figure 10d shows the current waveform for IEC 61000-4-2 ESD Contact Discharge test.

Figure 10b. Human Body Current Waveform

Figure 10d. IEC 61000-4-2 ESD Generator Current Waveform

#### Applications Information

#### 256 Transceivers on the Bus

The standard RS-485 receiver input impedance is a one-unit load (12k $\Omega$ ), and the standard driver can drive up to 32 unit loads. The MAX13430E family of transceivers has a 1/8-unit load receiver input impedance (96k $\Omega$ ), allowing up to 256 transceivers to be connected in parallel on one communication line. Any combination of these devices, as well as other RS-485 transceivers with a total of 32-unit loads or less, can be connected to the line.

#### **Reduced EMI and Reflections**

The MAX13430E/MAX13432E feature reduced slewrate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 500kbps.

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention. The first, a foldback current limit on the output stage, provides immediate protection against short circuits over the whole common-mode voltage range (see the *Typical Operating Characteristics.*) The second, a thermal-shutdown circuit, forces the driver outputs into a high-impedance state if the die temperature exceeds +150°C (typ).

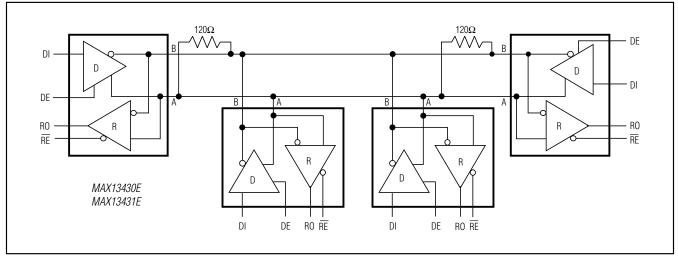

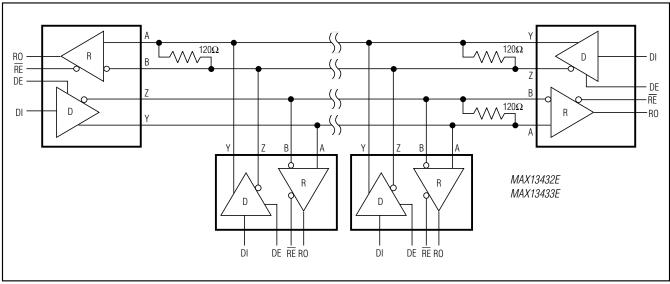

#### **Typical Applications**

The MAX13430E/MAX13433E transceivers are designed for bidirectional data communications on multipoint bus transmission lines. Figures 11 and 12 show typical network applications circuits. To minimize reflections, terminate the line at both ends with its characteristic impedance, and keep stub lengths off the main line as short as possible. The slew-rate-limited MAX13430E/MAX13432E allow the RS-485 network to be more tolerant of imperfect termination.

# **RS-485 Transceivers with Low-Voltage Logic Interface**

**Typical Application Circuits**

Figure 11. Typical Half-Duplex RS-485 Network

Figure 12. Typical Full-Duplex RS-485 Network

#### Chip Information

Package Information

PROCESS: BICMOS

For the latest package outline information and land patterns, go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |  |

|--------------|--------------|----------------|--|

| 10 µMAX      | U10-2        | <u>21-0061</u> |  |

| 14 TDFN-EP   | T1433-2      | <u>21-0137</u> |  |

| 10 TDFN-EP   | T1033-1      | <u>21-0137</u> |  |

| 14 SO        | S14-1        | <u>21-0041</u> |  |

# **RS-485 Transceivers with Low-Voltage Logic Interface**

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                            | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------|------------------|

| 0                  | 10/08            | Initial release                                                        | —                |

| 1                  | 5/09             | Updated Ordering Information                                           | 1                |

| 2                  | 5/10             | Added an automotive temperature grade part to the Ordering Information | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

20

© 2010 Maxim Integrated

Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000 The Maxim logo and Maxim Integrated are trademarks of Maxim Integrated Products, Inc.

Downloaded from: http://www.datasheetcatalog.com/