# The 24bit Audio CODEC series

# Monaural Audio CODEC with Touch Panel Interface

# **BU26154MUV**

# **General Description**

BU26154 is a low-power compact audio CODEC. BU26154 also incorporates touch panel interface and Cap-Less headphones amplifier, speaker amplifier which is most suitable for digital still cameras, electronic dictionaries. BU26154 has built-in voltage regulator for the stability of CODEC characteristic that is sensitive to the outside noise. Speaker amplifier that can change AB / D Class. Therefore, when the interference including the FM radio influences it, BU26154 can prevent interference by operating AB grade. As digital code processing, it is equipped with the high-pass filter as the noise cut use of the specific frequency band, Notch filter and the Equalizer of 5 bands and P<sup>2</sup>Bass+, Noise gate, and flexible sound quality effect processing is possible.

### **Features**

- Various sound processing functions

- ♦ P²Bass+

- Noise gate

- ♦ Fast release ALC

- ♦ 5-band Equalizer/Notch Filter

- High PSRR is attained by built-in regulator

- Speaker amplifier can be switched to AB class and D class

- Touch panel interface.

# **Applications**

- Electronic Dictionary

- Digital Still Camera

- Digital Single-lens Reflex Camera

- Digital Mirror-less Camera

- Digital Video Camera, others

# **Typical Application Circuit(s)**

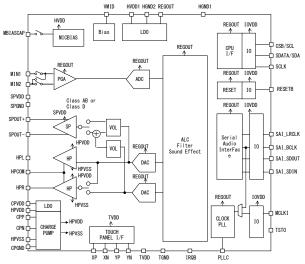

Figure 1. Block Diagram

# **Key Specifications**

| HVDD Power Supply:  | 2.7V to 3.6V |

|---------------------|--------------|

| SPVDD Power Supply: | 2.7V to 5.5V |

| CPDD Power Supply:  | 2.7V to 3.6V |

| TVDD Power Supply:  | 2.7V to 3.6V |

| MIC-ADC SNR:        | 92dB(Typ)    |

| DAC-SP SNR:         | 95dB (Typ)   |

| DAC-HP SNR:         | 93dB (Tvp)   |

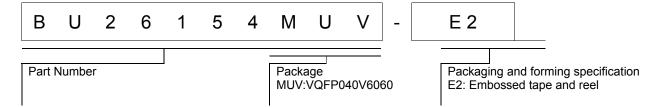

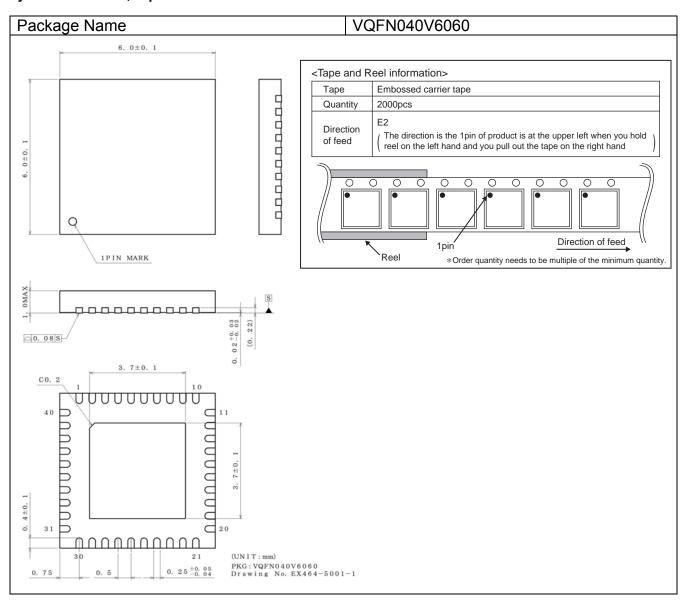

Package(s) VQFN040V6060 W (Typ) x D (Typ) x H (Max) 6.00mm x 6.00mm x 1.00mm

OProduct structure: Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays

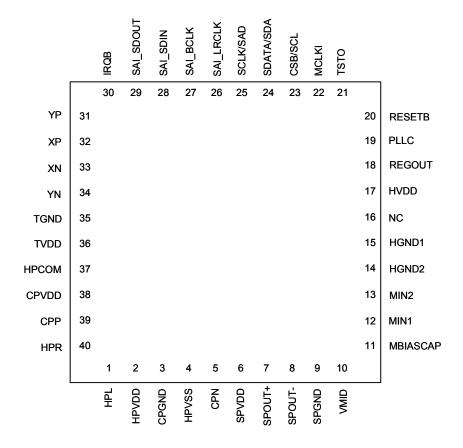

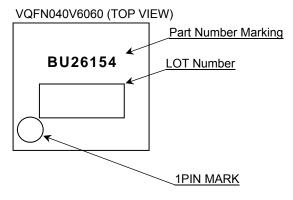

# Pin Configuration(s)

# Top view

Figure 2. Pin Configuration(s)

# Pin Description(s)

| No    | Name    | I/O | Power  | Function                                                              | Reset   | No use  |

|-------|---------|-----|--------|-----------------------------------------------------------------------|---------|---------|

| 110   | Ivanic  | 1/0 | 1 OWC1 |                                                                       | (Note1) | (Note3) |

| 17    | HVDD    | Р   | _      | High voltage power supply pin                                         | _       | _       |

| 17    | 11100   | '   |        | A capacitor is connected between HVDD and HGND1.                      |         |         |

| 6     | SPVDD   | Р   | _      | Speaker power supply pin                                              | _       | _       |

|       | 0       | ļ · |        | A capacitor is connected between SPVDD and SPGND.                     |         |         |

| 38    | CPVDD   | Р   | _      | Voltage power supply pin for charge pump                              | _       | _       |

| 40    | N O     |     |        | A capacitor is connected between CPVDD and CPGND.                     |         |         |

| 16    | N.C     | -   | -      | A no connect pin.                                                     | -       | -       |

| 36    | TVDD    | Р   | -      | Voltage power supply for the touch panel                              | -       | _       |

|       |         |     |        | Please connect a capacitor between TVDD and TGND.                     |         |         |

| 15    | HGND1   | Р   |        | High voltage ground 1 It is used on the same voltage as HGND2, SPGND, |         |         |

| 13    | ПОМОТ   |     | _      | CPGND, and TGND.                                                      | -       | -       |

|       |         |     |        | High voltage ground 2                                                 |         |         |

| 14    | HGND2   | Р   | _      | It is used on the same voltage as HGND1, SPGND,                       | _       | _       |

| • • • | 1101102 | '   |        | CPGND, and TGND.                                                      |         |         |

|       |         |     |        | Ground pin for Speaker                                                |         |         |

| 9     | SPGND   | Р   | _      | It is used on the same voltage as HGND1, HGND2,                       | _       | _       |

|       |         |     |        | CPGND, and TGND.                                                      |         |         |

|       |         |     |        | Ground pin for charge pump                                            |         |         |

| 3     | CPGND   | Р   | -      | It is used on the same voltage as HGND1, HGND2,                       | -       | _       |

|       |         |     |        | SPGND, and TGND.                                                      |         |         |

|       |         |     |        | Ground pin for touch panel interface                                  |         |         |

| 35    | TGND    | Р   | -      | It is used on the same voltage as HGND1, HGND2,                       | -       | -       |

|       |         |     |        | CPGND, and SPGND.                                                     |         |         |

|       |         |     |        | Regulator output                                                      |         |         |

| 18    | REGOUT  | 0   | HVDD   | A capacitor is connected between REGOUT and HGND1.                    | HGND2   | -       |

|       |         |     |        | Please connect as close as possible to the chip.                      |         |         |

|          |                       | 1  | T       |                                                                                                         | T                                     |          |

|----------|-----------------------|----|---------|---------------------------------------------------------------------------------------------------------|---------------------------------------|----------|

|          |                       |    |         | A positive side voltage output pin for the headphones                                                   |                                       |          |

| 2        | HPVDD                 | 0  | CPVDD   | driver.                                                                                                 | CPGND                                 | (Note 2) |

|          |                       |    |         | A capacitor is connected between HPVDD and CPGND.                                                       |                                       |          |

|          |                       |    |         | Please connect as close as possible to the chip.  A negative side voltage output pin for the headphones |                                       |          |

|          |                       |    |         | driver.                                                                                                 |                                       |          |

| 4        | HPVSS                 | 0  | CPVDD   | A capacitor is connected between HPVSS and CPGND.                                                       | CPGND                                 | (Note 2) |

|          |                       |    |         | Please connect as close as possible to the chip.                                                        |                                       |          |

| 20       | MOLIZI                |    | LIVED   |                                                                                                         | (in n t)                              | LICNIDA  |

| 22       | MCLKI                 | l  | HVDD    | Master Clock pin                                                                                        | (input)                               | HGND1    |

| 21       | TSTO                  | 0  | HVDD    | Output pin for test-mode. Make it open.                                                                 | HGND1                                 | Open     |

|          |                       |    |         | Reset pin                                                                                               |                                       |          |

| 20       | RESETB                | ı  | HVDD    | "L" level: Reset enables.                                                                               | (input)                               | -        |

|          |                       |    |         | "H" level: Reset disable.                                                                               |                                       |          |

|          |                       |    |         | 3 wire interface: data input output pin                                                                 |                                       |          |

| 24       | SDATA                 | 10 | HVDD    | It is indicated as SDATA.                                                                               | (input)                               | _        |

|          | /SDA                  |    |         | 2 wire interface: data input output pin <sup>(Note 1)</sup>                                             | (                                     |          |

|          |                       |    |         | It is indicated as SDA.                                                                                 |                                       |          |

|          |                       |    |         | 3 wire interface: Serial clock input pin                                                                |                                       |          |

|          | 00114                 |    |         | It is indicated as SCLK.                                                                                |                                       |          |

| 25       | SCLK                  | ı  | HVDD    | 2 wire interface: Slave address select input pin.                                                       | (input)                               | HGND1    |

|          | /SAD                  |    |         | It is indicated as SAD.                                                                                 | ( 1 7                                 |          |

|          |                       |    |         | SAD pin = "L" level slave address is "0011010"                                                          |                                       |          |

|          |                       |    |         | SAD pin = "H" level slave address is "0011011"                                                          |                                       |          |

|          | 000                   |    |         | 3 wire interface: chip select input pin                                                                 |                                       |          |

| 23       | CSB                   | ı  | HVDD    | It is indicated as CSB.                                                                                 | (input)                               | -        |

|          | /SCL                  |    |         | 2 wire interface: Serial clock input pin *1                                                             | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |          |

|          | 041 1 00114           | 10 | 111/100 | It is indicated as SCL.                                                                                 | (* 1)                                 | LICAIDA  |

| 26       | SAI_LRCLK             | 10 | HVDD    | SAI LR clock input/output pin                                                                           | (input)                               | HGND1    |

| 27       | SAI_BCLK              | IO | HVDD    | SAI bit clock input/output pin                                                                          | (input)                               | HGND1    |

| 28       | SAI_SDIN              | 1  | HVDD    | SAI serial data input pin                                                                               | (input)                               | HGND1    |

| 29       | SAI_SDOUT             | 0  | HVDD    | SAI serial data output pin                                                                              | HGND1                                 | Open     |

| 30       | IRQB                  | 0  | HVDD    | An interrupt output terminal. When an interrupt occurs, chip outputs "L".                               | HGND1                                 | Open     |

|          |                       |    |         | Analog reference voltage pin                                                                            |                                       |          |

| 10       | VMID                  | 0  | REGOUT  | A capacitor is connected between VMID and HGND2.                                                        | HGND2                                 | -        |

|          |                       |    |         | Microphone bias voltage output pin                                                                      |                                       |          |

| 11       | MBIASCAP              | 0  | HVDD    | A capacitor is connected between HGND2.                                                                 | HGND2                                 | Open     |

|          | 111211100111          |    |         | Please connect as close as possible to the chip.                                                        |                                       | оро      |

|          |                       |    |         | Analog microphone input 1                                                                               |                                       |          |

|          |                       |    |         | Single-end and differential can be chosen.                                                              |                                       |          |

| 12       | MIN1                  | ı  | REGOUT  | When differential is chosen, it connects with microphone                                                | Hi-Z                                  | Open     |

|          |                       |    |         | + pin.                                                                                                  |                                       |          |

|          |                       |    |         | Analog microphone input 2                                                                               |                                       |          |

| 40       | BAINIO                |    | DECOUR  | Single-end and differential can be chosen.                                                              | 11: 7                                 | 0        |

| 13       | MIN2                  | I  | REGOUT  | When differential is chosen, it connects with microphone                                                | Hi-Z                                  | Open     |

|          |                       |    |         | - pin.                                                                                                  |                                       |          |

| 8        | SPOUT-                | 0  | SPVDD   | speaker output - pin                                                                                    | SPGND                                 | Open     |

| 7        | SPOUT+                | 0  | SPVDD   | speaker output + pin                                                                                    | SPGND                                 | Open     |

| 1        | HPL                   | 0  | SPVDD   | Headphones output Lch terminal                                                                          | CPGND                                 | Open     |

| 40       | HPR                   | 0  | SPVDD   | Headphones output Rch terminal                                                                          | CPGND                                 | Open     |

| 39       | CPP                   | 0  | CPVDD   | Charge pump flying capacitor, positive side output pin                                                  | Hi-Z                                  | Open     |

| 5        | CPN                   | 0  | CPVDD   | Charge pump flying capacitor, negative side output pin                                                  | Hi-Z                                  | Open     |

|          |                       |    |         | PLL filter pin                                                                                          |                                       |          |

| 19       | PLLC                  | 0  | HVDD    | When clock of the MCLKI pin input is used, make it open.                                                | HGND2                                 | Open     |

| 13       | , LLO                 |    | 11400   | When clock of the SAI_BCLK pin input is used, it is                                                     | TIONUZ                                | Орсп     |

|          |                       |    |         | necessary to connect resistors and a capacitor.                                                         |                                       |          |

| 31       | YP                    | 0  | TVDD    | YP pin for the touch panel interface                                                                    | Hi-Z                                  | Open     |

| 32       | XP                    | 0  | TVDD    | XP pin for the touch panel interface                                                                    | Hi-Z                                  | Open     |

| 33       | XN                    | 0  | TVDD    | XN pin for the touch panel interface                                                                    | Hi-Z                                  | Open     |

| 34       | YN                    | 0  | TVDD    | YN pin for the touch panel interface                                                                    | Hi-Z                                  | Open     |

| 37       | HPCOM                 |    | -       | Headphones amplifier common pin                                                                         | (input)                               | -        |

| /NI-1- 4 | ) In case of 2 wire s |    |         |                                                                                                         | mnor noice d                          |          |

<sup>(</sup>Note 1) In case of 2 wire serial, if this pin is used with external pull-up resistor, it possibly gets noise from power. Therefore, tamper noise design is required in the noisy environment.

(Note 2) At the time of power down, in HPVDD and HPVSS, is short-circuited.

# **Description of Block(s)**

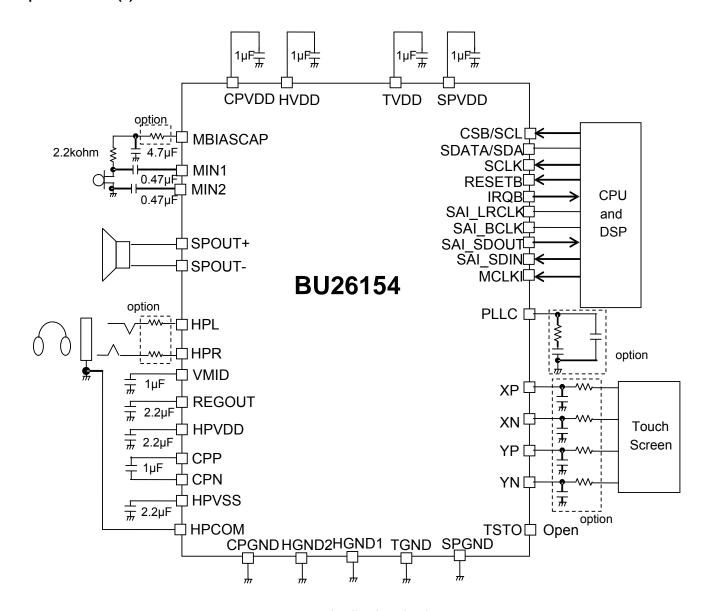

Figure 3. BU26154 Application circuit

Absolute Maximum Ratings (Ta = 25°C)

(HGND1=HGND2=SPGND=CPGND=TGND=0V)

| Parameter                             | Symbol                                                                                | Condition                                              | Rating             | Unit |

|---------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|

| HVDD Supply Voltage                   | HVDD                                                                                  | -                                                      | -0.3 to 4.5        | V    |

| SPVDD Supply Voltage                  | SPVDD                                                                                 | -                                                      | -0.3 to 7.0        | V    |

| CPVDD Supply Voltage                  | CPVDD                                                                                 | -                                                      | -0.3 to 4.5        | V    |

| Input Voltage                         | MCLKI, SAI_LRCLK, SAI_BCLK, SAI_SDIN, put Voltage  VIN  SDATA/SDA, SCLK. CSB/SCL pins |                                                        | -0.3 to HVDD+0.3   | V    |

|                                       |                                                                                       | MIN1, MIN2 pins                                        | -0.3 to REGOUT+0.3 | V    |

| Storage Temperature                   | T <sub>stg</sub>                                                                      | -                                                      | -55 to +150        | °C   |

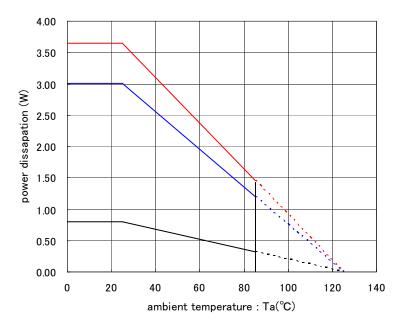

| Power Dissipation <sup>(Note 1)</sup> | D4                                                                                    | Ta=25°C (Note 1)                                       | 0.80               | W    |

| Power Dissipation                     | Pd                                                                                    | Ta=25°C (Note 2)                                       | 3.01               | W    |

| Output Current 1                      | IOSP                                                                                  | SPOUT+, SPOUT- pins                                    | -560 to +560       | mA   |

| Output Current 2                      | IOHP                                                                                  | HPL, HPR pins                                          | -100 to +100       | mA   |

| Output Current 3                      | IOCP                                                                                  | HPVSS,HPVDD,CP,CN<br>pin                               | -500 to +500       | mA   |

| Output Current 4                      | IOREGO                                                                                | REGOUT pin                                             | -30 to 0           | mA   |

| Output Current 5                      | 100                                                                                   | Except SPOUT+,SPOUT-, HPL,HPR, REGOUT,HPVDD,HPVSS pins | -8 to +8           | mA   |

Do not short the output pin to another output pin, power supply pin or GND pin.(Output pin includes an IO pin which is in output mode) (Note 1) 74.2mm×74.2mm×1.6tmm FR4 1Layer Glass epoxy base Surface Copper foil 0%) Mounting

Above Ta=25°C, reduced by 8.0mW/°C. Thermal beer is on a base.

(Note 2) 74.2mm×74.2mm×1.6tmm FR4. 4 Layer Glass epoxy base (2,3layer Copper foil 100%) Mounting

Above Ta=25°C, reduced by 30.12mW/°C. Thermal beer is on a base.

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

# **Recommended Operating Conditions**

(HGND1=HGND2=SPGND=CPGND=TGND=0V)

| Parameter             | Symbol          | Condition       | Rating     | Unit |

|-----------------------|-----------------|-----------------|------------|------|

| HVDD Supply Voltage   | HVDD            | HVDD=CPVDD=TVDD | 2.7 to 3.6 | V    |

| SPVDD Supply Voltage  | SPVDD           | -               | 2.7 to 5.5 | V    |

| CPVDD Supply Voltage  | CPVDD           | HVDD=CPVDD=TVDD | 2.7 to 3.6 | V    |

| TVDD Supply Voltage   | TVDD            | HVDD=CPVDD=TVDD | 2.7 to 3.6 | V    |

| Operating Temperature | T <sub>op</sub> | -               | -20 to +85 | °C   |

(Note 1) The radiation-proof design is not carried out.

# **Electrical Characteristics**

DC Characteristics

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)

| Parameter                     | Symbol              | Conditions                                                                            | Min                  | Тур          | Max                   | Unit | Related Pin          |

|-------------------------------|---------------------|---------------------------------------------------------------------------------------|----------------------|--------------|-----------------------|------|----------------------|

| "H" Input Voltage1            | VIH1                | HGND1=0V                                                                              | HVDD *0.8            | -            | HVDD+0.3              | V    | All Digital<br>Input |

| "L" Input Voltage 1           | VIL1                | HGND1=0V                                                                              | -0.3                 | -            | HVDD *0.2             | V    | All Digital<br>Input |

| "H" Input Voltage 2           | VIH2                | HGND1=0V                                                                              | HVDD-0.4             | -            | HVDD+0.3              | V    | All Digital<br>Input |

| "L" Input Voltage 2           | VIL2                | HGND1=0V                                                                              | -0.3                 | -            | 0.4                   | V    | All Digital<br>Input |

| "H" output Voltage            | VOH                 | IOH=-1mA                                                                              | HVDD *0.85           | -            | -                     | V    | Except SDA           |

| "L" output Voltage 1          | VOL1                | IOL=1mA                                                                               | -                    | -            | HVDD *0.15            | V    | Except SDA           |

| "L" output Voltage 2          | VOL2                | IOL=3mA                                                                               | -                    | -            | 0.4                   | V    | SDA                  |

| "H" Input Leakage<br>Current  | IIH                 | VIH= HVDD                                                                             | -                    | -            | 10                    | μA   | All Digital<br>Input |

| "L" Input Leakage<br>Current  | IIL                 | VIL=HGND1                                                                             | -10                  | -            | -                     | μΑ   | All Digital<br>Input |

| "Z" output Leakage<br>Current | IOZH                | VOH=HVDD                                                                              | -                    | -            | 10                    | μA   | SDA                  |

| "Z" output Leakage<br>Current | IOZL                | VOL=HGND1                                                                             | -10                  | -            | -                     | μА   | SDA                  |

| Operating Current1            | IDDO1               | Playback(fs48kHz)<br>no Load, Hp-amp<br>use<br>Sin1kHz-Full Scale<br>output           | -                    | 10           | 13                    | mA   | -                    |

| Operating Current2            | IDDO2               | Playback(fs48kHz)<br>no Load, D-class,<br>Sp-amp use<br>Sin1kHz-Full Scale<br>output  | -                    | 10.5         | 13.7                  | mA   | -                    |

| Operating Current3            | IDDO3               | Playback(fs48kHz)<br>no Load, AB-class,<br>Sp-amp use<br>Sin1kHz-Full Scale<br>output | -                    | 12           | 15.6                  | mA   | -                    |

| Operating Current4            | IDDO4               | Record(fs48kHz)<br>Sin1kHz-Full Scale<br>input                                        | -                    | 9.5          | 12.4                  | mA   | -                    |

| Operating Current5            | IDDO5               | Touch Panel<br>Interface Operate                                                      | -                    | 0.6          | 1                     | mA   | -                    |

| Operating Current6            | IDDO6               | Touch Panel Interface Interrupt Wait Ta = -40 to 55 °C                                | -                    | 220          | 320                   | uA   | -                    |

| Standby Current               | IDDS                | 25 °C                                                                                 | -                    | 0.5          | 5                     | μΑ   | -                    |

|                               | Interface Interrunt | electric current at the time of                                                       | the wait Please refe | r to a touch | n nanel interface cla |      | he movement setting  |

<sup>(</sup>Note 1) Touch Panel Interface Interrupt electric current at the time of the wait. Please refer to a touch panel interface clause for the movement setting condition.

<sup>(</sup>Note 2) Standby current is total value for all power supply currents. (Note 3) Standby current's condition is power off state by RESETB=L

### **AC Characteristics**

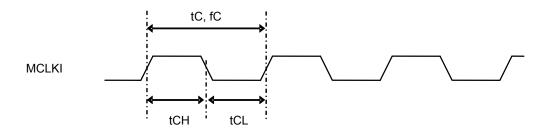

Clock

PLL not used

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)

| Parameter        | Symbol | Min    | Max    | Unit |

|------------------|--------|--------|--------|------|

| MCLKI Frequency  | fC     | 4.096  | 49.152 | MHz  |

| MCLKI Period     | tC     | 1/fC   | 1/fC   | ns   |

| MCLKI "H" Length | tCH    | tC*0.4 | -      | ns   |

| MCLKI "L" Length | tCL    | tC*0.4 | -      | ns   |

PLL used

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V,Ta=25°C)

| Parameter        | Symbol | Min    | Max  | Unit |

|------------------|--------|--------|------|------|

| MCLKI Frequency  | fC     | 6.75   | 54   | MHz  |

| MCLKI Period     | tC     | 1/fC   | 1/fC | ns   |

| MCLKI "H" Length | tCH    | tC*0.4 | -    | ns   |

| MCLKI "L" Length | tCL    | tC*0.4 | -    | ns   |

When PLL is use, clock from SAI\_BCLK pin other than MCLKI pin could be inputted. Please refer to SAI slave clause about the BCLK pin input frequency.

Figure 4

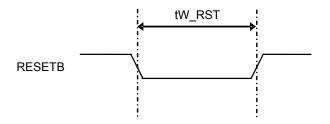

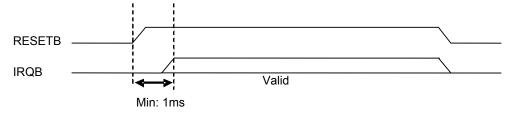

### Reset

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)

| Parameter          | Symbol | Min | Max. | Unit |

|--------------------|--------|-----|------|------|

| RESETB pulse width | tW_RST | 5   | -    | μs   |

Figure 5

When Reset pin is made low-level, internal LDO goes to power mode.

1ms is necessary until REGOUT pin becomes low-level. The recommended tW\_RST is over 1ms.

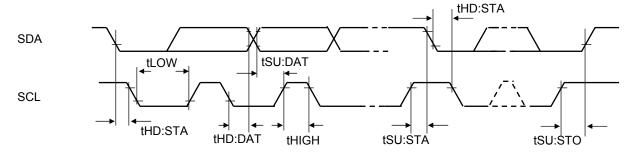

# 2-Wire Serial Interface

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C, CL=30pF)

| Descriptor                                | 0                   | Standard Mode |      | Fast Mode |     | Unit  |

|-------------------------------------------|---------------------|---------------|------|-----------|-----|-------|

| Parameter                                 | Symbol              | Min           | Max  | Min       | Max | Offic |

| SCL Frequency                             | f <sub>SCL</sub>    | -             | 100  | -         | 400 | kHz   |

| SCL "L" Length                            | t <sub>LOW</sub>    | 4.7           | -    | 1.3       | -   | μs    |

| SCL "H" Length                            | t <sub>HIGH</sub>   | 4.0           | -    | 0.6       | -   | μs    |

| Hold Time under Repeat [Start] Condition  | t <sub>HD:STA</sub> | 4.0           | -    | 0.6       | -   | μs    |

| Setup Time under Repeat [Start] Condition | t <sub>su:sta</sub> | 4.0           | -    | 0.6       | -   | рs    |

| Data Hold Time                            | t <sub>HD:DAT</sub> | 0             | 3.45 | 0         | 0.9 | μs    |

| Data Setup Time                           | t <sub>SU:DAT</sub> | 250           | -    | 100       | -   | ns    |

| Setup Time under [Stop] Condition         | t <sub>su:sto</sub> | 4.0           | -    | 0.6       | -   | μs    |

Figure 6

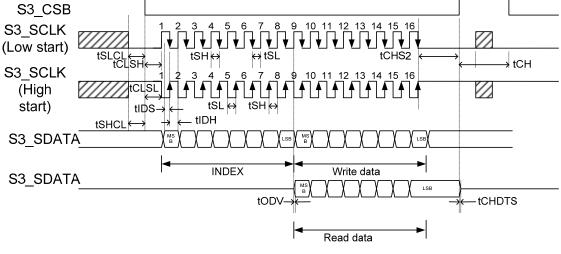

# 3-Wire Serial Interface

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C, CL=30pF)

| Parameter                             | Symbol | Min | Max | Unit |

|---------------------------------------|--------|-----|-----|------|

| SCLK Low to Chip Select enable        | tSLCL  | 100 | -   | ns   |

| Chip Select Enable to SCLK Low        | tCLSL  | 100 | -   | ns   |

| Chip Select Enable to SCLK High       | tCLSH  | 100 | -   | ns   |

| CLK High to Chip Select enable        | tSHCL  | 100 | -   | ns   |

| SCLK High Pulse Width                 | tSH    | 50  | -   | ns   |

| SCLK Low Pulse Width                  | tSL    | 50  | -   | ns   |

| Input Data Setup time                 | tIDS   | 30  | -   | ns   |

| Input Data Hold time                  | tIDH   | 30  | -   | ns   |

| SCLK last edge to Chip Select disable | tCHS2  | 100 | -   | ns   |

| Chip Select High Pulse Width          | tCH    | 100 | -   | ns   |

| Output Data Valid                     | tODV   | -   | 40  | ns   |

| Chip Select High to Data Transition   | tCHDTS | -   | 40  | ns   |

Two kinds of timing are supported depending on the SCLK pin level at data transfer start. Read or Write is selected by LSB logic INDEX.

Figure 7

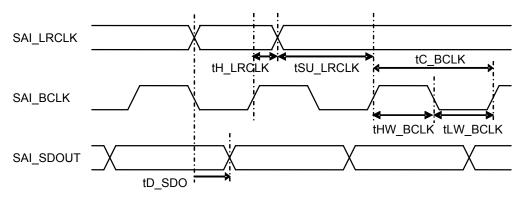

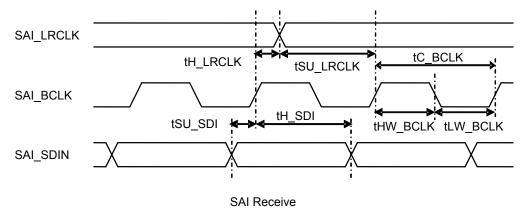

# Serial Audio Interface (Slave)

(HGND1= HGND2=SPĠND=ĆPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, VDD=3.3V, Ta=25°C, CL=30pF)

| Parameter            | Symbol          | Min  | Max   | Unit |  |

|----------------------|-----------------|------|-------|------|--|

| SAI_BCLK Period      | tC_BCLK         | 32fs | 128fs | Hz   |  |

| SAI_BCLK "H" Length  | tHW_BCLK        | 73   | -     | ns   |  |

| SAI_BCLK "L" Length  | tLW_BCLK        | 73   | -     | ns   |  |

| SAI_LRCLK Hold Time  | tH_LRCLK        | 20   | -     | ns   |  |

| SAI_LRCLK Setup Time | tSU_LRCLK       | 20   | -     | ns   |  |

| SAI_SDOUT Delay Time | tD_SDO (Note 1) | -    | 80    | ns   |  |

| SAI_SDIN Setup Time  | tSU_SDI         | 20   | -     | ns   |  |

| SAI_SDIN Hold Time   | tH_SDI          | 20   | -     | ns   |  |

(Note 1) tD\_SDO is the delay time from previous SAI\_BCLK transition and SAI\_LRCLK transition.

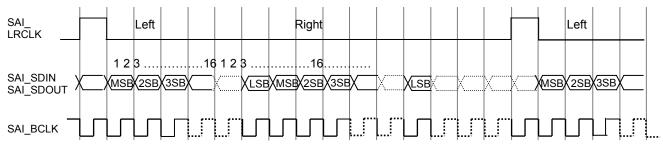

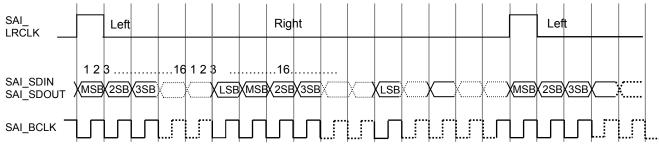

SAI Transmit

Figure 8

Figure 9

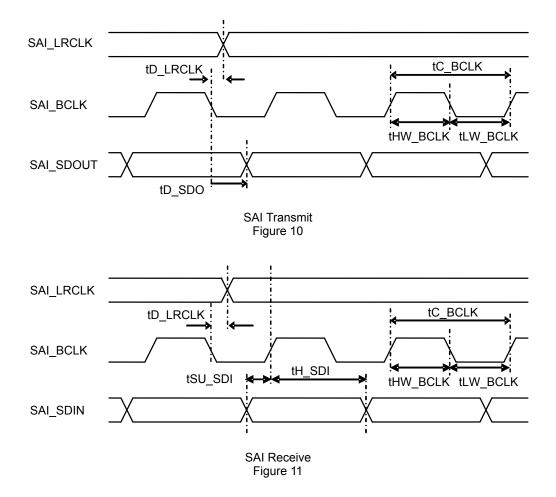

# SAI (Master) - Serial Audio Interface (Master)

(HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C, CL=30pF)

| Parameter            | Symbol   | Min  | Max  | Unit |

|----------------------|----------|------|------|------|

| SAI_BCLK Period      | tC_BCLK  | 32fs | 64fs | Hz   |

| SAI_BCLK "H" Length  | tHW_BCLK | 146  | -    | ns   |

| SAI_BCLK "L" Length  | tLW_BCLK | 146  | -    | ns   |

| SAI_LRCLK Delay time | tD_LRCLK | -    | 20   | ns   |

| SAI_SDOUT Delay Time | tD_SDO   | -    | 20   | ns   |

| SAI_SDIN Setup Time  | tSU_SDI  | 50   | -    | ns   |

| SAI_SDIN Hold Time   | tH_SDI   | 0    | -    | ns   |

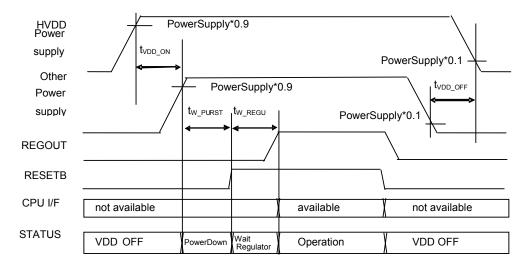

# **Power Supply Sequence**

Please power on/off the LSI with all kind of power at the same time.

Each power supply should power up/down in 50ms. Also, keep all power supply in the ON state or the OFF state. Please avoid partial ON or partial OFF states.

Please keep RESETB pin "L" level until all power supply become ON state. The CPU I/F become available when all power supply is powered on after  $t_{W\_PURST}$  and  $t_{W\_REGU}$  time exceeds.

HVDD must be powered on first, but HVDD must be powered off last. About SPVDD, there is no limitation above.

| Parameter                                            | Symbol               | Min | Тур | Max | Unit |

|------------------------------------------------------|----------------------|-----|-----|-----|------|

| Power On Delay Time                                  | t <sub>VDD_ON</sub>  | 0   | -   | 50  | ms   |

| Power Off Delay Time                                 | t <sub>VDD_OFF</sub> | 0   | -   | 50  | ms   |

| Reset Time after Power ON                            | t <sub>w_PURST</sub> | 1   | -   | -   | μs   |

| Wait Time for Regulator Starting after Reset Release | t <sub>w_REGU</sub>  | 1   | -   | -   | ms   |

Figure 12

**Analog Characteristics**

| (HGND1= HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)                                                                                                                |                |                           |                   |                   |                   |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------|-------------------|-------------------|-------------------|------|

| Parameter                                                                                                                                                                                                | Symbol         | Condition                 | Min               | Тур               | Max               | Unit |

| Regulator Output                                                                                                                                                                                         |                |                           |                   |                   |                   |      |

| REGOUT Output Level                                                                                                                                                                                      | VREGOUT        | -                         | 1.7               | 1.8               | 1.9               | V    |

| Mic Input (MIC Gain=18dB / Digital                                                                                                                                                                       | Volume=0.0dB   | / ALC=OFF)                |                   |                   |                   |      |

| Full Scale Input Signal Level                                                                                                                                                                            | VMINFS1        | MIN1,MIN2                 | -                 | -                 | 0.124             | Vp-p |

| Input Resistance                                                                                                                                                                                         | RMIN1          | MIN1,MIN2                 | 20                | 30                | 40                | kΩ   |

| Mic Input (MIC Gain=9.0dB / Digita                                                                                                                                                                       | l Volume=0.0dB | /ALC=OFF)                 |                   |                   |                   |      |

| Full Scale Input Signal Level                                                                                                                                                                            | VMINFS2        | MIN1,MIN2                 | -                 | -                 | 0.454             | Vp-p |

| Input Resistance                                                                                                                                                                                         | RMIN2          | MIN1,MIN2                 | 20                | 30                | 40                | kΩ   |

| Analog Reference Level(VMID-pin)                                                                                                                                                                         | )              |                           |                   |                   |                   |      |

| Analog Reference Voltage                                                                                                                                                                                 | VREF           | -                         | 0.9x<br>REGOUT/2  | 1.0x<br>REGOUT/2  | 1.1x<br>REGOUT/2  | V    |

| Microphone Bias(MBIASCAP -pin)                                                                                                                                                                           |                |                           |                   |                   |                   |      |

|                                                                                                                                                                                                          |                | IMIC = -1mA,<br>MICBCON=0 | 1.50x<br>REGOUT/2 | 1.67x<br>REGOUT/2 | 1.84x<br>REGOUT/2 | V    |

| Output Voltage<br>where, VMIC <hvdd*0.85< td=""><td>VMIC</td><td>IMIC = -1mA,<br/>MICBCON=1</td><td>2.00x<br/>REGOUT/2</td><td>2.22x<br/>REGOUT/2</td><td>2.45x<br/>REGOUT/2</td><td>V</td></hvdd*0.85<> | VMIC           | IMIC = -1mA,<br>MICBCON=1 | 2.00x<br>REGOUT/2 | 2.22x<br>REGOUT/2 | 2.45x<br>REGOUT/2 | V    |

|                                                                                                                                                                                                          | VIVIIO         | IMIC = -1mA,<br>MICBCON=2 | 2.50x<br>REGOUT/2 | 2.78x<br>REGOUT/2 | 3.06x<br>REGOUT/2 | V    |

|                                                                                                                                                                                                          |                | IMIC = -1mA,<br>MICBCON=3 | 3.00x<br>REGOUT/2 | 3.33x<br>REGOUT/2 | 3.67x<br>REGOUT/2 | V    |

| Output Current                                                                                                                                                                                           | IMIC           | -                         | _                 | -                 | 2                 | mA   |

(HGND1=HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)

| Parameter                           | Symbol         | , HVDD=3.3V, SPVDD=3.3V, CP<br>Conditions                      | Min | Typ  | Max | Unit     |

|-------------------------------------|----------------|----------------------------------------------------------------|-----|------|-----|----------|

| Analog Inputs to ADC out (MIC Gain= |                | I Volume=0.0dB / ALC=OFF)                                      |     |      |     |          |

| S/(N+D)                             | SND1           | -1dBFS/ A-weighted                                             | -   | 78   | -   | dB       |

| S/N                                 | SNR1           | A-weighted                                                     | -   | 89   | -   | dB       |

| Power Supply Rejection Ratio        | PSRR1          | HVDD on 100mVp-p, 1kHz<br>noise, no signal input               | -   | 90   | -   | dB       |

| Analog Inputs to ADC out (MIC Gain= | 9.0dB / Digita | al Volume=0.0dB / ALC=OFF)                                     |     |      |     |          |

| S/(N+D)                             | SND2           | -1dBFS/ A-weighted                                             | -   | 80   | -   | dB       |

| S/N                                 | SNR2           | A-weighted                                                     | -   | 92   | -   | dB       |

| Power Supply Rejection Ratio        | PSRR2          | HVDD on 100mVp-p, 1kHz<br>noise, no signal input               | -   | 90   | -   | dB       |

| DAC to Headphone OUT(HPR/HPL, v     | vith 16Ω/50pl  | Fload)                                                         |     |      |     |          |

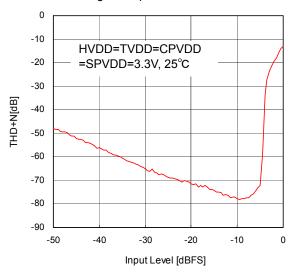

| Total Harmonic Distortion           | THD+N3         | 1kHz,input -12dBFS                                             | -   | 75   | -   | dB       |

| Signal to Noise Ratio               | SNR3           | A-weighted                                                     | -   | 93   | -   | dB       |

| Power Supply Rejection Ratio        | PSRR3          | HVDD on<br>100mVp-p,1kHz noise, no<br>signal input<br>CPVDD on | -   | 90   | -   | dB       |

| ,,,,,                               |                | 100mVp-p,1kHz noise, no<br>signal input                        | -   | 90   | -   | dB       |

| Output Offset Voltage               | VOF            | No signal input                                                | -   | ±1   | -   | mV       |

| Charge Pump Oscillator Frequency    | CPOSC          | -                                                              | -   | 500  | -   | kHz      |

| HPVDD Port Output Voltage           | HPVDO          | -                                                              | -   | 1.8  | -   | V        |

| HPVSS Port Output Voltage           | HPVSO          | -                                                              | -   | -1.8 | -   | V        |

| DAC to Speaker OUT D-class Mode (   | SPOUT+/-, w    | rith 8Ω/50pF load)                                             |     |      | 1   |          |

| Output Power                        | Po4            | THD=10%, SPVOL=6dB                                             | -   | 700  | -   | mW       |

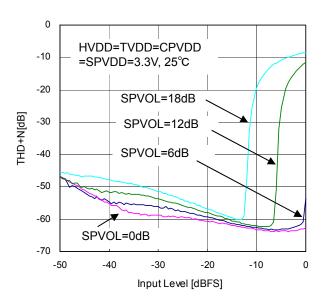

| Total Harmonic Distortion           | THD+N4         | Po=310mW                                                       | -   | 66   | -   | dB       |

| Signal to Noise Ratio               | SNR4           | A-weighted, THD+N=1%                                           | _   | 95   | -   | dB       |

| Power Supply Rejection Ratio        | PSRR4          | HVDD on<br>100mVp-p,1kHz noise                                 | -   | 90   | -   | dB       |

| r ower cupply responding rand       | TOTAL          | SPVDD on<br>100mVp-p,1kHz noise                                | -   | 60   | -   | dB       |

| PWM frequency                       | PWMF           | -                                                              | -   | 370  | -   | kHz      |

| Efficiency                          | EFF            | -                                                              | -   | 90   | -   | %        |

| DAC to Speaker OUT AB-class Mode    | (SPOUT+/       | uith 8Ω/50pF load)                                             |     |      | 1   | 1        |

| Output Power                        | Po5            | THD=10%, SPVOL=6dB                                             | _   | 700  | _   | mW       |

| Total Harmonic Distortion           | THD+N5         | Po=310mW                                                       | _   | 62   | _   | dB       |

| Signal to Noise Ratio               | SNR5           | A-weighted, THD+N=1%                                           | _   | 95   | _   | dB       |

| 2.3 12 110.00 110.00                | 3.1.10         | HVDD on                                                        |     |      |     |          |

| Power Supply Rejection Ratio        | PSRR5          | 100mVp-p,1kHz noise<br>SPVDD on                                | -   | 90   | -   | dB<br>dB |

| Microphone Bias(MBIASCAP-pin) *1    |                | 100mVp-p,1kHz noise                                            |     |      |     |          |

| Output Noise Voltage                | VMICN6         | 22Hz to 22kHz,<br>MICBCON=1                                    | -   | 5    | -   | μV       |

| Power Supply Rejection Ratio        | PSRR6          | HVDD on<br>100mVp-p,1kHz noise<br>Load=1mA<br>MICBCON=1        | -   | 70   | -   | dB       |

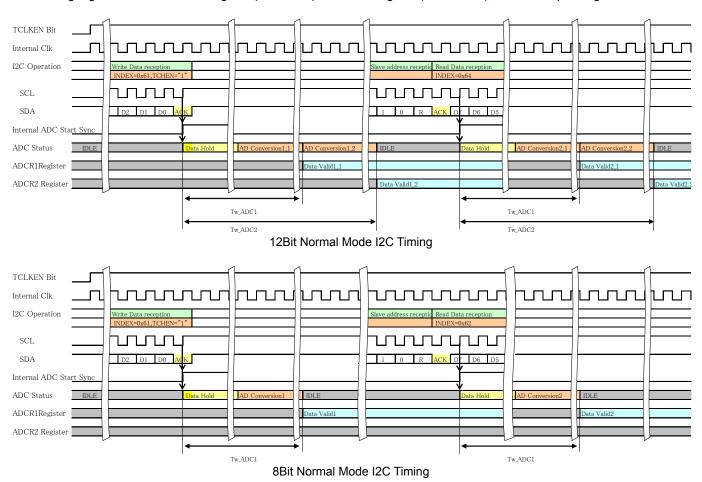

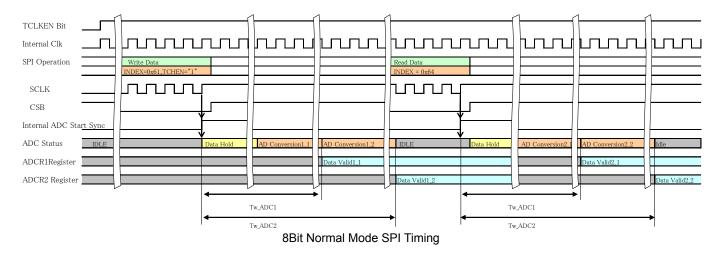

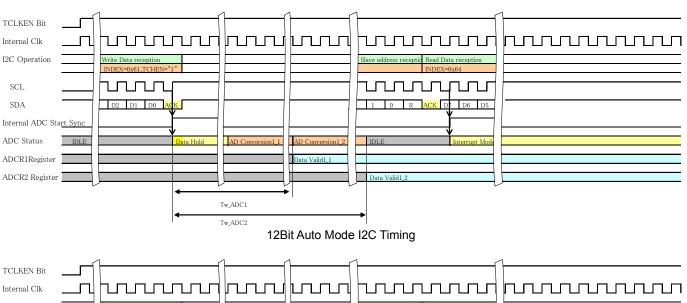

(HGND1=HGND2=SPGND=CPGND=TGND=0V, HVDD=3.3V, SPVDD=3.3V, CPVDD=3.3V, TVDD=3.3V, Ta=25°C)

| Parameter                        | Symbol  | Conditions | Min | Тур | Max | Unit |

|----------------------------------|---------|------------|-----|-----|-----|------|

| Touch Panel Interface            |         |            |     |     |     |      |

| ADC Resolution                   | N       | -          | -   | -   | 12  | Bit  |

| Differential Non-Linearity Error | DNL     | -          | -3  | -   | 3   | LSB  |

| Integral Non-Linearity Error     | INL     | -          | -4  | -   | 4   | LSB  |

| Offset Error                     | OFTERR  | -          | -   | 1   | -   | LSB  |

| Gain Error                       | GAERR   | -          | -   | 0.5 | -   | LSB  |

| Touch Panel Driver Switch        | SWONR   | -          | -   | 5   | -   | Ω    |

| Interrupt Pull up Registance     | IRQR1   | RSEL=0     | 40  | 50  | 70  | kΩ   |

| Interrupt Pull-up Resistance     | IRQR2   | RSEL=1     | 70  | 90  | 120 | kΩ   |

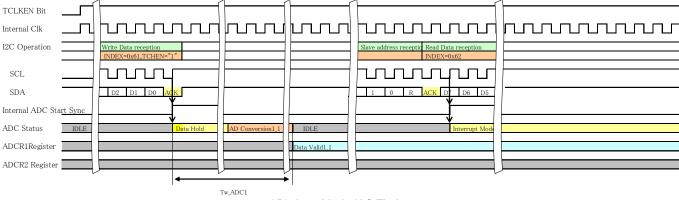

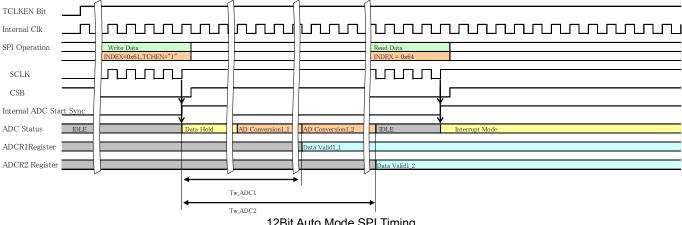

| ADO Ocazania Timina              | Tw_ADC1 |            | -   | -   | 35  | μs   |

| ADC Conversion Timing            | Tw_ADC2 |            | -   | -   | 43  | μs   |

### **Function Description**

Clock Control

Main modules that make sound path of the LSI inside operate with 1024fs Audio Clock.

Audio Clock can be selected whether divided clock of 256fs/512fs/1024fs from MCLKI or generated clock from Audio PLL. When PLL is used, PLL generates internal clock. The input clock into PLL can be selected from either MCLKI port or SAI\_BCLK port by setting Clock Input / Output Control register. PLL generates 256fs clock of sampling frequency.

The registers about Audio Clock setting: Sampling Rate Setting Register, FPLLM, FPLLNL, FPLLNH, FPLLD, FPLLFL, FPLLFDH, FPLLFDH, Clock Input / Output Control register, Clock Input Select Register

- · The sequence of PLL setting

- 1. Stop PLL output by setting PLLOE bit to "0".

- 2. Disable PLL by setting PLLEN bit to "0".

- Set PFLLM, FPPNL, FPLLNH, FPLLD, FPLLFL, FPLLFH, FPLLFDL, FPLLFDH.

- 4. Set input port by PLLISEL bit.

- 5. Set PLLEN bit to "1".

- 6. Wait for the PLL stabilizing time as the table "PLL Stabilizing Time".

- 7. Set PLLOE bit to "1".

- 8. Start recording or playback.

PLL Stabilizing Time

PLL stability time

10msec

- Related Register

Sampling Rate Setting Register

PLLNL, PLLNH Register

PLLML, PLLMH Register

**PLLDIV** Register

Clock Enable Register

Clock Input / Output Control Register

When PLL is Used.

The LSI support audio PLL function that can generate precise audio clock from wide range of clock frequency. Then, it can be realize audio function without external clock generator for audio. The LSI supports following cases.

The LSI generates audio clock with input clock provided from MCLKI port or BCLKI port.

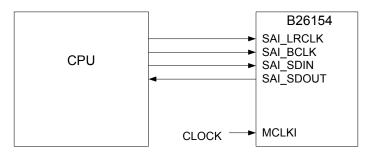

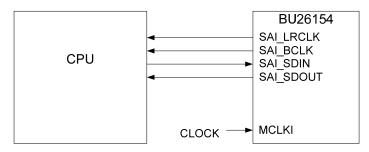

■case1: PLLISEL (0x0e/0x0f)=0x1, MST(0x64/0x65)="0"

Audio clock is generated by the PLL BU26154 with MCLKI clock. SAI LRCLK and SAI BCLK are provided by the CPU.

Figure 13

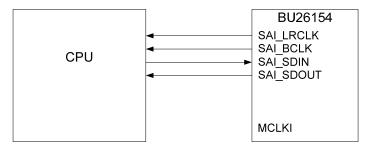

■case2: PLLISEL (0x0e/0x0f)=0x1, MST(0x64/0x65)="1"

Audio clock is generated by the PLL in BU26154 from MCLKI clock. SAI\_LRCLK and SAI\_BCLK are provided from the LSI.

Figure 14

■case3: PLLISEL (0x0e/0x0f)=0x2, MST(0x64/0x65)="1" Audio clock is generated by PLL in BU26154 form SAI clock.

Figure 15

When PLL is not Used.

Audio clock is generated by the CPU and supplied to the LSI when PLL is not used. Then CPU and the LSI are synchronized.

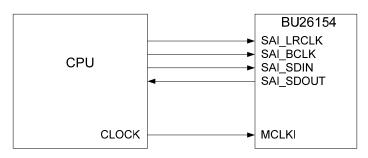

# ■case 5: MST (0x64/0x65) ="0"

Audio clock (256fs, 512fs, 1024fs) is generated by the CPU and supplied to MCLKI port of the LSI. LRCLK and BCLK are also provided from the CPU.

Figure 16

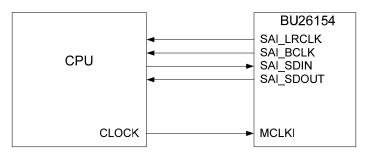

# ■case6: MST (0x64/0x65)="1"

Audio clock (256fs, 512fs, 1024fs) is generated by the CPU and supplied to MCLKI port of the LSI. SAI\_LRCLK and SAI\_BCLK are provided from the LSI.

Figure 17

Even when using the same sampling frequency, the setting condition is different depending on clock frequency. When changing MCLKI input frequency, PLLOE should be set to "0", then PLLOE should be set to "1" back.

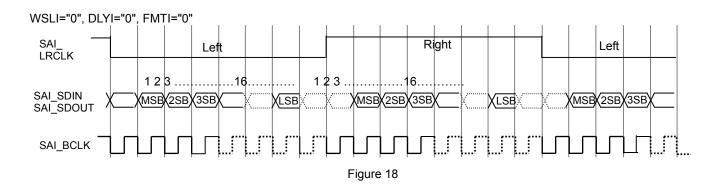

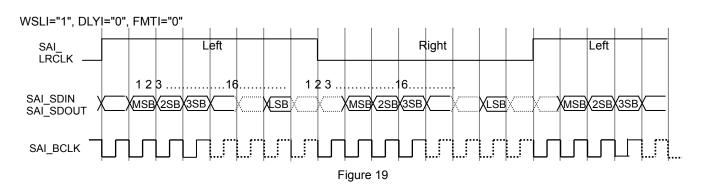

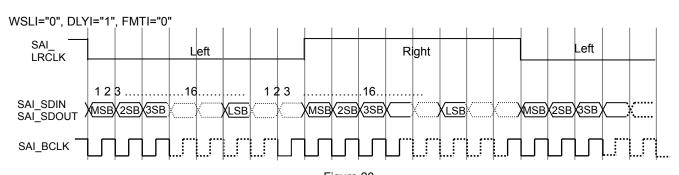

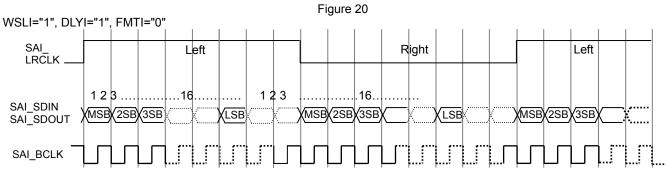

SAI (Serial Audio System Interface)

The LSI supports SAI formats.

Figure 21

DLYI="0", FMTI="1"

Flame synchronous transfer mode: R channel data is transferred right after L channel data.

Figure 22

DLYI="1", FMTI="1"

Flame synchronous transfer mode: R channel data is transferred right after L channel data.

Figure 23

- Related Register SAI Transmitter Control Register SAI Receiver Control Register

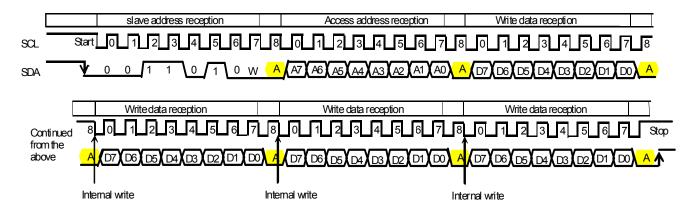

### 2 wire serial interface

This LSI has 2 wire serial interfaces. The LSI operates as a slave device. The address is fixed at "0011010".

### - Format

The followings are the protocol of the LSI.

Write (MSB first)

Start Condition (Set SDA level from "H" to "L" during SCL="H")

Slave Address (0011010) +W (0) (8bit)

Write Address (8bit)

Write Data (8bit)

. . .

Stop Condition (Set SDA level from "L" to "H" during SCL="H")

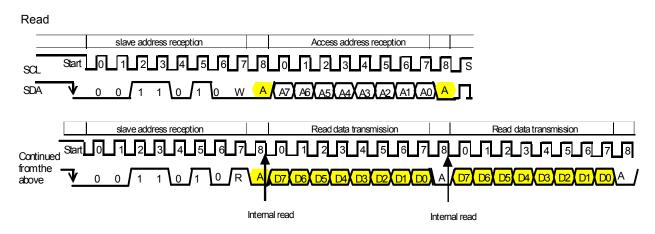

# Read (MSB first)

**Start Condition**

Slave Address (0011010) +W (0) (8bit)

Read Address (8bit)

(Stop Condition) Start Condition

Slave Address (0011010) +R (1) (8bit)

Read Data (8bit)

The following shows the wave form of the LSI.

The yellow gridding shows that slave device drives the bus.

The symbol in the wave form means as following table.

| Unit   | Description                                 |  |  |

|--------|---------------------------------------------|--|--|

| W/R    | 0: It is Read Write 1                       |  |  |

| Α      | 0: ACK(Acknowledge) 1: NAK(Not Acknowledge) |  |  |

| A[7-0] | Address (8bit)                              |  |  |

| D[7-0] | Data(8bit)                                  |  |  |

Write

Figure 24

In case there is no Stop or Start condition after internal register is written (Above figure: Internal Write), the slave device becomes continuous write mode and the next received 8 bits of data will be written into the internal register addressed by incremented by two to the current address.

Figure 25

If the Master device returns ACK (acknowledge) after the 8 bit data transferred from the LSI becomes continuous read mode. The next received 8 bits of data will be read from the internal register addressed by incremented by two to the current address.

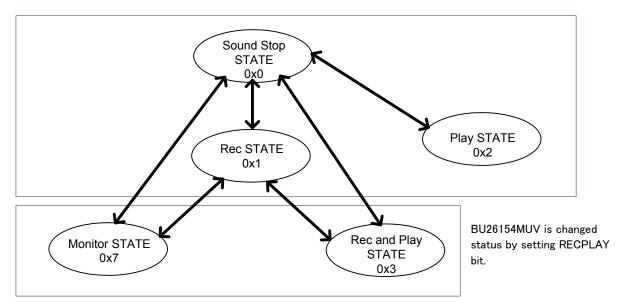

State transition about sound control

The following shows state transition about sound control. A change state is carried out by RECPLAY bit setup.

Figure 26

- (1) Sound Stop STATE (RECPLAY=0x0) Sound activity is stopped.

- (2) Rec STATE (RECPLAY =0x1)

Recording is enabled through microphone.

- (3) Play STATE (RECPLAY =0x2) Playback is enabled from SAI.

- (4) Monitor STATE (RECPLAY =0x7)

- Monitoring recording via microphone is enabled. ALC function is only effective in recording path. Only 2ch sound effects are available in Notch filter mode. In the time of transition Rec STATE to Monitor STATE, please set off the register bits of EQ2EN-EQ3EN.

- (5) Rec and Play STATE (RECPLAY =0x3)

Playback is enabled from SAI with recording via microphone. ALC function is only effective in recording path.

Only 2ch sound effects are available in Notch filter mode. In the time of transition Rec STATE to Monitor STATE, please set off the register bits of EQ2EN-EQ3EN.

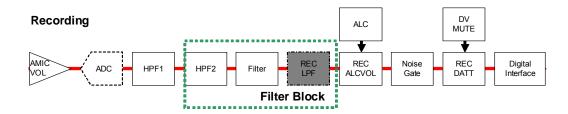

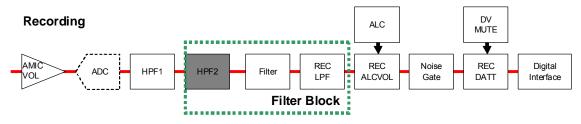

Signal Flow

It uses signal flow Case1 or Case2 at the time of recording (analog microphone).

# Case1:

### Case2:

Figure 27

| Name          | Function                                                                      | Related Register                         | Setting                                    |  |  |  |

|---------------|-------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------|--|--|--|

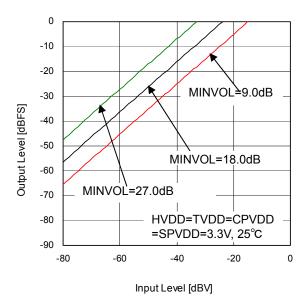

| AMICVOL       | Analog Microphone volume                                                      | Mic input volume control                 | Volume setting<br>9dB to +35.25dB          |  |  |  |

| HPF1          | High path filter for record DC cut                                            | DSP Filter Function Enable               | HPF Enable/Disable                         |  |  |  |

| HPF2          | High pass Filter for Record                                                   | DSP Filter Function Enable               | HPF Enable/Disable order setting           |  |  |  |

|               |                                                                               | High Pass Filter2 Cut-off Control        | Cut-off frequency setting                  |  |  |  |

|               |                                                                               | Sound Effect Mode                        | Sound Effect mode setting                  |  |  |  |

|               |                                                                               | DSP Filter Function Enable               | Each filters Enable/Disable setting        |  |  |  |

| Filter        | Notch filter is available                                                     | EQ Band N Gain Setting                   | Each filters gain setting                  |  |  |  |

|               |                                                                               | Programmable EQ Band N Coeffeicient-a0/1 | Each sound effects characteristics setting |  |  |  |

| DEOLDE        | Low pass Filter for recording.                                                | Rec Programmable LPF Setting             | LPF Enable/Disable setting order setting   |  |  |  |

| RECLPF        |                                                                               | Rec Programmable LPF Cutoff Coef         | Cut-off frequency setting                  |  |  |  |

| REC<br>ALCVOL | ALC use:ALC controls volume<br>ALC not use: It's available as<br>Boost volume |                                          |                                            |  |  |  |

| ALC           | Auto Level Controller Function. ALC is processed to recording data            | refer to application note                |                                            |  |  |  |

| Noise Gate    | The purpose is for reducing a floor noise                                     |                                          |                                            |  |  |  |

|               | Record Digital Attenuator.                                                    | Record Digital Attenuator Control        | Record Digital Attenuator Control          |  |  |  |

| RECDATT       | It's available fader function for reducing a Pop-noise when                   | Digital Volume Control Function Enable   | Digital Volume Control Function Enable     |  |  |  |

|               | changing volume.                                                              | Mixer & Volume Control                   | Mixer & Volume Control                     |  |  |  |

| DVMUTE        | Record Digital Volume Mute                                                    | Digital Volume Control Function Enable   | Digital Volume Control Function Enable     |  |  |  |

<sup>\*</sup> Please refer to the Sound Effect Mode register for Filter Block. When Filter Block is connected with the reproduction route, nothing is processed in the recording route.

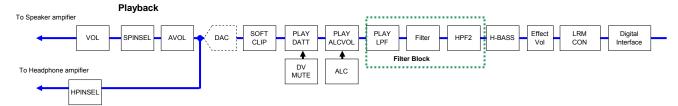

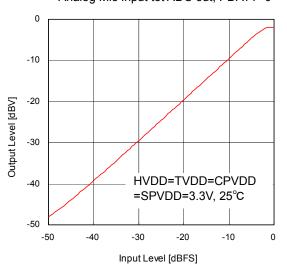

# Signal flow at the time of the reproduction

Figure 28

| Name                 | Function                                                                                                             | Related Register                                                                                             | Setting                                                                                                                                   |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| LRMCON               | Mixer of the Lch/Rch data input from SAI.                                                                            | Mixer & Volume Control                                                                                       | Mixer setting                                                                                                                             |  |

| Effect Vol           | It is digital before the sound is processed Volume.                                                                  | Playback Effect Volume                                                                                       | Volume setting<br>-71.5dB to 0dB (0.5dBstep)                                                                                              |  |

| P <sup>2</sup> Bass+ | Block for P <sup>2</sup> Bass + processing.                                                                          | P <sup>2</sup> Bass+ Enable<br>P <sup>2</sup> Bass+ Parameter*                                               | Setting of P <sup>2</sup> Bass+                                                                                                           |  |

| Filter               | Notch filter is available                                                                                            | Sound Effect Mode DSP Filter Function Enable EQ Band N Gain Setting Programmable EQ Band N Coeffeicient-a0/1 | Sound mode setting Enable/Disable of each filter Gain setting of each filter Characteristic setting of each filter and acoustic treatment |  |

| PLAYLPF              | It is programmable LPF for the reproduction.                                                                         | Play Programmable LPF Setting  Play Programmable LPF Cutoff                                                  | Degree setting of LPF for<br>Enable/Disable reproduction of<br>LPF for reproduction<br>Characteristic setting of LPF for                  |  |

|                      |                                                                                                                      | Coef                                                                                                         | reproduction                                                                                                                              |  |

| PLAY<br>ALCVOL       | Boost Volume. Please refer to the application note for the ALC function                                              |                                                                                                              | for the ALC function.                                                                                                                     |  |

| ALC                  | It is an auto level controller. ALC is processed to the reproduction data.                                           | 1                                                                                                            |                                                                                                                                           |  |

|                      | Digital Attenuator of the reproduction route.                                                                        | Playback Digital Attenuator<br>Control                                                                       | Volume setting<br>-71.5dB to 0dB (0.5dBstep)                                                                                              |  |

| PLAYDATT             | Fader can be used for the noise reduction at the Volume setting                                                      | Digital Volume Control Function<br>Enable                                                                    | Fader ON/OFF setting (Synchronize with DVMUTE.)                                                                                           |  |

|                      | change.                                                                                                              | Mixer & Volume Control                                                                                       | Setting at Fade time (Synchronize with DVMUTE.)                                                                                           |  |

| DVMUTE               | Reproduction route (PLAYDATT) is compulsorily put into the state of Mute. The value of PLAYDATT need not be changed. | Digital Volume Control Function<br>Enable                                                                    | MUTE ON/ Turning off setting                                                                                                              |  |

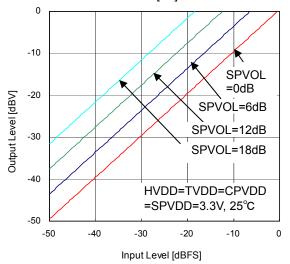

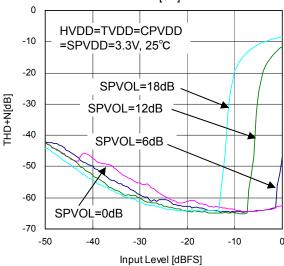

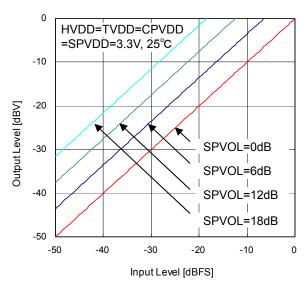

| SPVOL                | The Analog Boost Volume of Speaker amplifier setting.                                                                | Speaker Amplifier Input Control                                                                              | Volume setting<br>0dB/6dB/12dB/18dB                                                                                                       |  |

|                      | The Analog Volume of reproduction                                                                                    | Analog volume control                                                                                        | Volume setting<br>-28dB to +18dB*At BTL                                                                                                   |  |

| AVOL                 | route setting. Fader can be used for the Pop-noise reduction at the Volume setting                                   | Amplifier Volume Fader Control                                                                               | Fader ON/OFF setting (Synchronize with AVMUTE.)                                                                                           |  |

|                      | change.                                                                                                              | Amplifier Volume Control Function Enable                                                                     | Setting at Fade time (Synchronize with AVMUTE.)                                                                                           |  |

| AVMUTE               | Reproduction route (SPVOL) is compulsorily put into the state of Mute. The value of SPVOL need not be changed.       | Amplifier Volume Control Function Enable                                                                     | MUTE ON/OFF setting                                                                                                                       |  |

| SPINSEL              | It selects the input path to speaker amplifier.                                                                      | Speaker Amplifier Input Control                                                                              | Selection of speaker amplifier playback path                                                                                              |  |

| HPINSEL              | It selects the input path to headphone amplifier.                                                                    | Headphone Amplifier Input Control                                                                            | Selection of headphone amplifier playback path                                                                                            |  |

<sup>\*</sup> Please refer to Sound Effect Mode Register for Filter Block. When Filter Block is connected with the recording route, nothing is processed in the reproduction route.

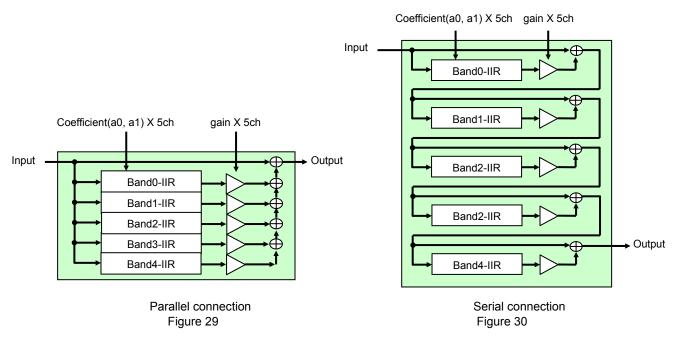

Filter (5bands-Programmable IIR Filter)

A five bands equalizer features a second-order IIR type Band Pass Filter. Volume control of MUTE, -71.5dB to +12dB (0.5dB step) can be controlled at all paths.

Each channels of the filter can be selected parallel connection or serial connection

The followings are block diagrams at parallel connection and serial connection

The filter coefficient is programmable. From required center frequency and band width, Programmable Equalizer Coefficient-a0 Control Register and Programmable Notch Filter Coefficient-a1 Control Register value is decided. Followings are the setting formula.

a0 =  $(1 - \tan \pi f_b/f_s) / (1 + \tan \pi f_b/f_s)$ a1 =  $-2\cos 2\pi f_0/f_s / (1 + \tan \pi f_b/f_s)$

f0: Band center frequency [Hz] fb: -3dB band width [Hz] fs: Sampling frequency [Hz]

\* Actual setting value is an integral number that the result of above formula multiplied by 2<sup>14</sup> then round up numbers of five and above and round down anything under five to a integer.

DSP filtering function: ON / OFF

DSP Filter Function Enable register can set ON or OFF of each filter function. Please change this register when RECPLAY bit is 0x0. If this register is changed on playback or recording, the noise may be generated.

### ALC Auto Level Control

Please refer the application note "AutoLevelControlApplicationNote".

P<sup>2</sup>Bass+ (Perfect Pure Bass Plus) Please refer the application note.

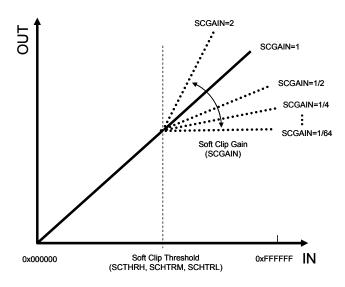

# Soft clip limiter

Soft clip function is reduced power comsumption. If ALC cannot be responded to input waveform, soft clip function is reduced input waveform. In case of input waveform is overed threshold level, soft clip reduce output waveform.

Figure 31

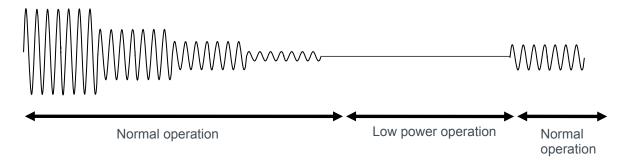

Low Power Consumption Operation

When PCM data is inputted into LSI consecutive "0" is detected, it will disable the output amplifier automatically and perform low power consumption mode operation by stopping the internal clock. When data except "0" are inputted, it will automatically return to original movement.

When "0" is detected in both LCHRCH, this function is effective. When you use only LCH, please input "0" data into the RCH side. When you use only RCH, please input "0" data into the LCH side. This function is effective only at the time of the playback of the speaker amplifier. At the time of headphones amplifier playback and the recording, please set it to disable. In addition, set the enable function and "0" count level in Zero Detection Setting Register.

Figure 32

Change of the SP/HP playback

When it changes of Speaker Amplifier and Headphone Amplifier, it prepares for COEFSEL bit because it does not perform the re-setting of filter coefficients. A side register is used when COEFSEL bit is "0". B side register is used when COEFSEL bit is "1". The target registers are as follows. Please be careful in setting addresses.

| A   | A side register | B side register |                | Register                                                      |

|-----|-----------------|-----------------|----------------|---------------------------------------------------------------|

| MAP | INDEX(R)        | MAP             | INDEX(R)       | -                                                             |

| 2   | 0x24/0x26/0x28  | 2               | 0x2a/0x2c/0x2e | P <sup>2</sup> BASS+ Parameter0/1/2                           |

| 0   | 0x46            | 2               | 0x46           | Play HPF2 Setting                                             |

| 0   | 0x4c/0x4e       | 2               | 0x4c/0x4e      | Play Programmable HPF2L/H Coef                                |

| 0   | 0x5c            | 2               | 0x5c           | Sound Effect Mode                                             |

| 0   | 0x66            | 2               | 0x66           | DSP Filter Function Enable                                    |

| 0   | 0x70            | 2               | 0x70           | Playback Effect Volume Control                                |

| 0   | 0x3e            | 2               | 0x73           | Playback Digital Attenuator Control                           |

| 0   | 0x74 to 0x7c    | 2               | 0x74 to 0x7c   | EQ Band0/1/2/3/4 Gain Setting                                 |

| 0   | 0x80 to 0xa6    | 2               | 0x7e to 0xa4   | Programmable Equalizer Band0/1/2/3/4<br>Coefficient-a0/a1 L/H |

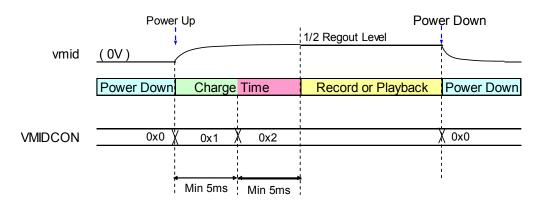

### Analog block

VMID is used as analog circuit reference voltage for both recording path and playback path. Therefore, both case for recording and playback, VMID need to do power up. At the power up, the wait time in proportion to the capacitor value is needed to charge external capacitor connected with VMID pin. If recording and playback start before completion of charge, it may generate noise. The following is a sequence of recommendation. Refer to the Analog Reference Power Management Register for the function of VMIDCON.

# VMID Power UP/DOWN Sequence (External capacitor 1uF)

Figure 33

### Playback Path

The LSI can be executed sound output from 4 paths bellow. The output can be selected by Speaker Amplifier Output Control Resister and Analog Reference Power Management Register.

Digital Input (SAI) → DAC → D-class Speaker Amplifier

$\label{eq:definition} \mbox{Digital Input (SAI)} \rightarrow \mbox{DAC} \rightarrow \mbox{AB-class Speaker Amplifier}$

Digital Input (SAI) → DAC → Headphone Amplifier

Analog Microphone Input (MIN pin) → ADC → DAC → Headphone Amplifier

### <attention>

No guaranty of record path sound quality during speaker amplifier active.

### Speaker amplifier

The speaker amplifier of BU26154 can choose operation mode among one of D-class operation or the AB-class operation. It can prevent interference with FM radio influence by making AB-class operation.

It performs the change of the enable / disable setting of the speaker amplifier and the AB-class/D-class operation in Speaker Amplifier Power Management Register.

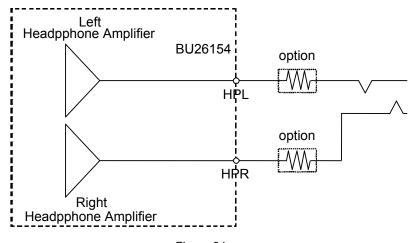

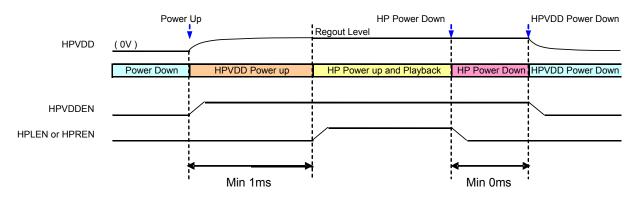

### Headphones amplifier

The headphones amplifier of BU26154 operates in a ground reference. Therefore the LSI can delete the condenser for the AC coupling to get outside. In addition, the LSI can suppress a POP noise when you want to suppress a POP noise by connecting the optional resistance of the chart below outside.

Figure 34

In addition, it is necessary to operate LDO for headphone amplifier when operating headphones amplifier. The power up of headphones amplifier and LDO for headphone set in Analog Reference Power Management Register. Please power up the headphones amplifier after 1mS waiting time for LDO for headphones. At the time of the power down, please power down HPVDD after the power down of the headphones amplifier.

HPVDD Power UP/DOWN Sequence

Figure 35

About HPCOM pin HPCOM pin is a signal ground pin of the headphones amplifier.

### Microphone amplifier

The microphone input can support two modes, a single-end and differential. When using it in single-end input, it writes "0" in the MINDIF bit of the MIC Interface Control register. When using differential input, it writes "1".

In the case of single-end input, it can input from MINP pin or MINN pin. Please set of the input pin in MIC Select Control Register.

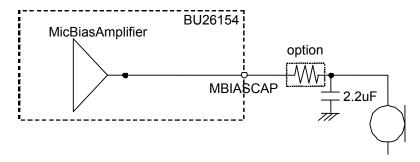

### Microphone bias

The Case of using Microphone bias, it shows a recommended connection diagram. By all means, please connect a condenser (2.2uF at the minimum) to MBIASCAP outside pin. On this occasion, the LSI can improve noise characteristics by connecting the option resistance on the chart below (the optional resistance is up to  $50 \Omega$ ).

Figure 36

In addition, according to the capacity of the outside condenser, it is necessary to wait until microphone bias is stable. In waiting time of MICBIAS, please set the value of the MICTIME bit at the MIC Input Charging Time register.

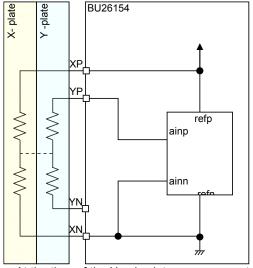

Touch Screen Controller

SAR 12 bits ADC is integrated into this LSI and is available as 4 lines type touch screen controller.

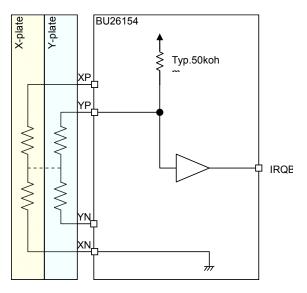

There is the function of the X-axis, the position sensing of the Y-axis, the pen pressure detection and the pen interrupt detection.

It becomes independent to Codec and is controllable without minding timing. But the hard reset (reset signal input by RESETB pin) communizes it.

### Clock control

When enabled clock is to be used for touch screen controller, set TCLKEN bit of Clock Enable Register to "1". The touch screen controller function uses a built-in oscillator. Therefore it is not necessary to perform clock control listing in item clock control when using only the touch screen controller.

### Position sensing

This LSI is available for the position sensing of the touch screen. The twice measurement of the X-axis measurement, the Y-axis measurement is necessary for position sensing.

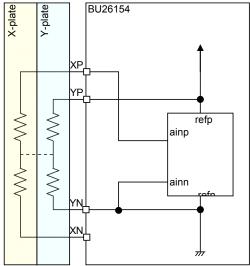

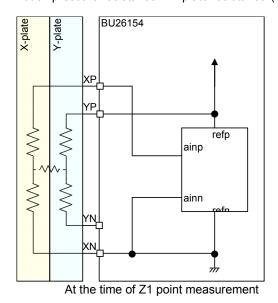

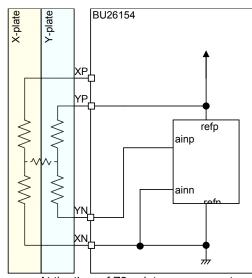

At the time of the X-axis plate measurement

At the time of the Y-axis plate measurement

Figure 37

### The Pen Pressure Detection