Order Number: 272644-005

# 8XC196NU COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

- 50 MHz Operation<sup>†</sup>

- 1 Mbyte of Linear Address Space

- Optional 48 Kbytes of ROM

- 1 Kbyte of Register RAM

- Register-register Architecture

- Footprint and Functionally Compatible Upgrade for the 8XC196NP

- 32 I/O Port Pins

- 16 Prioritized Interrupt Sources

- 4 External Interrupt Pins and NMI Pin

- 2 Flexible 16-bit Timer/Counters with Quadrature Counting Capability

- 3 Pulse-width Modulator (PWM) Outputs with High Drive Capability

- Full-duplex Serial Port with Dedicated Baud-rate Generator

- Peripheral Transaction Server

- † 40 MHz standard; 50 MHz is Speed Premium

- Chip-select Unit

- 6 Chip-select Pins

- Dynamic Demultiplexed/Multiplexed Address/Data Bus for Each Chip Select

- Programmable Wait States (0-3) for Each Chip Select

- Programmable Bus Width (8- or 16-bit) for Each Chip Select

- Programmable Address Range for Each Chip Select

- Event Processor Array (EPA) with 4 High-speed Capture/Compare Channels

- Multiply and Accumulate Executes in 640 ns Using the 32-bit Hardware Accumulator

- 960 ns 32/16 Unsigned Division

- 100-pin SQFP or 100-pin QFP Package

- Complete System Development Support

- High-speed CHMOS Technology

The 8XC196NU is a member of Intel's 16-bit MCS<sup>®</sup> 96 microcontroller family. The device features 1 Mbyte of linear address space, a demultiplexed bus, and a chip-select unit. The external bus can dynamically switch between multiplexed and demultiplexed operation.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

\*Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-548-4725

# **CONTENTS**

# 8XC196NU Commercial CHMOS 16-bit Microcontroller

| 4.0         | Product Overview                                           | 4  |

|-------------|------------------------------------------------------------|----|

| 1.0         |                                                            |    |

| 2.0         | Nomenclature Overview                                      |    |

| 3.0         | Pinout                                                     | 3  |

| 4.0         | Signals                                                    | 12 |

| 5.0         | Address Map                                                | 19 |

| 6.0         | Electrical Characteristics                                 | 20 |

| 6.          | S.1 DC Characteristics                                     | 21 |

| 6           | 5.2 AC Characteristics                                     |    |

| 0.          | 6.2.1 Relationship of XTAL1 to CLKOUT                      |    |

|             | 6.2.2 Explanation of AC Symbols                            |    |

|             | 6.2.3 AC Characteristics — Multiplexed Bus Mode            |    |

|             | 6.2.4 AC Characteristics — Demultiplexed Bus Mode          |    |

|             | 6.2.5 HOLD#, HLDA# Timings                                 |    |

|             | 6.2.6 AC Characteristics — Serial Port, Synchronous Mode 0 |    |

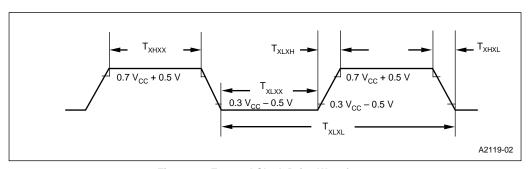

|             | 6.2.7 External Clock Drive                                 |    |

| 7.0         | Thermal Characteristics                                    |    |

| 7.0         |                                                            |    |

| 8.0         | 8XC196NU Errata                                            |    |

| 9.0         | Datasheet Revision History                                 | 38 |

| Figu        | urae                                                       |    |

| 1 igu<br>1. | 8XC196NU Block Diagram                                     | 1  |

| 2.          | The 8XC196NU Family Nomenclature                           |    |

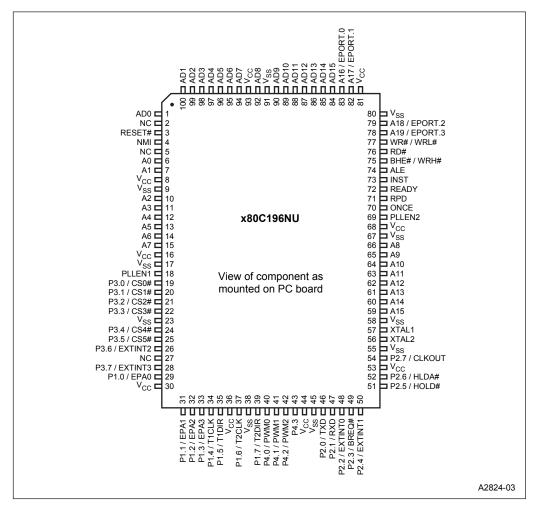

| 3.          | 80C196NU 100-pin SQFP Package                              |    |

| 4.          | 80C196NU 100-pin QFP Package                               |    |

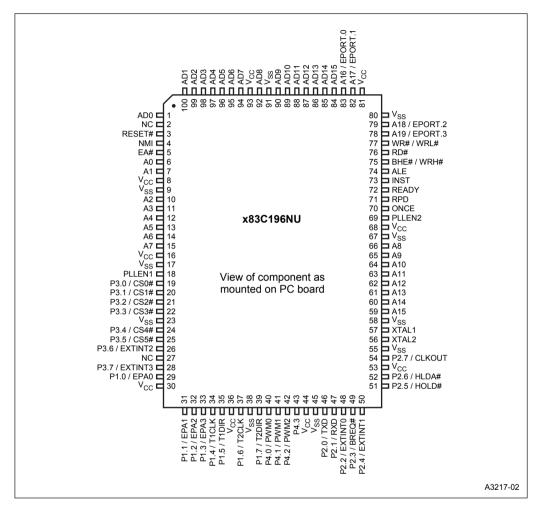

| 5.          | 83C196NU 100-pin QFP Package                               | 9  |

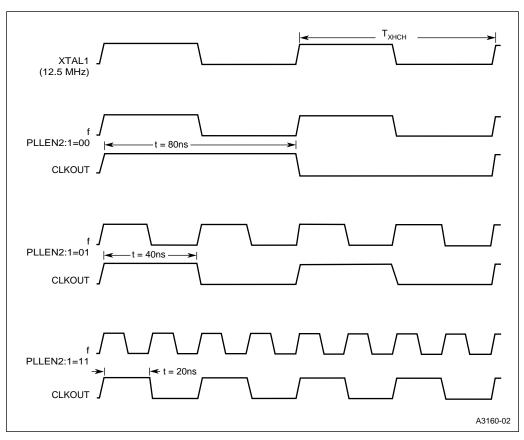

| 6.          | Effect of Clock Mode on CLKOUT                             | 23 |

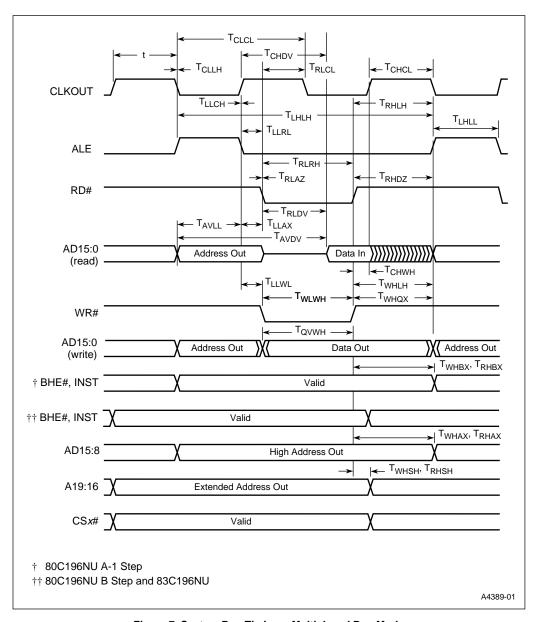

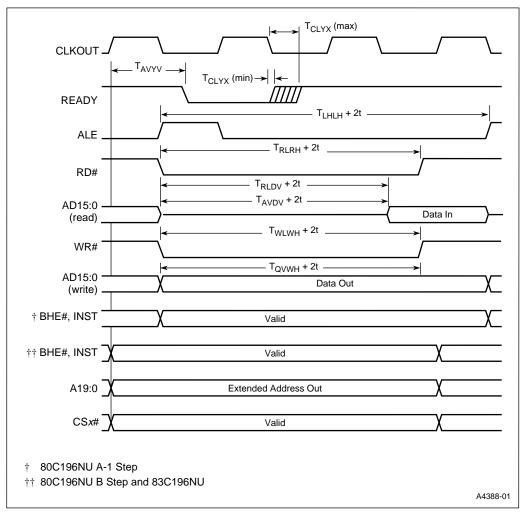

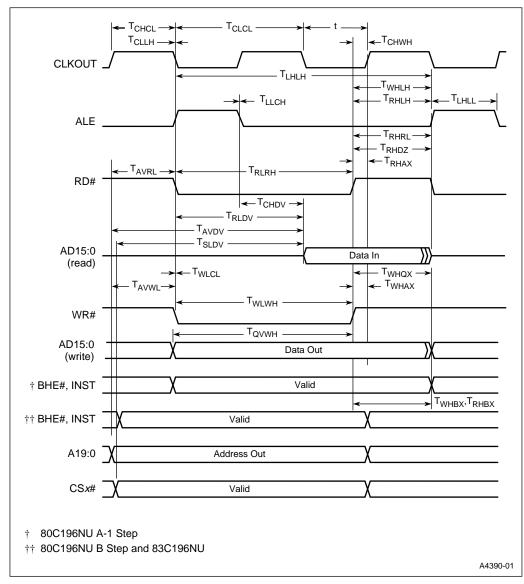

| 7.          | System Bus Timings, Multiplexed Bus Mode                   |    |

| 8.          | READY Timing, Multiplexed Bus Mode                         |    |

| 9.          | System Bus Timings, Demultiplexed Bus Mode                 |    |

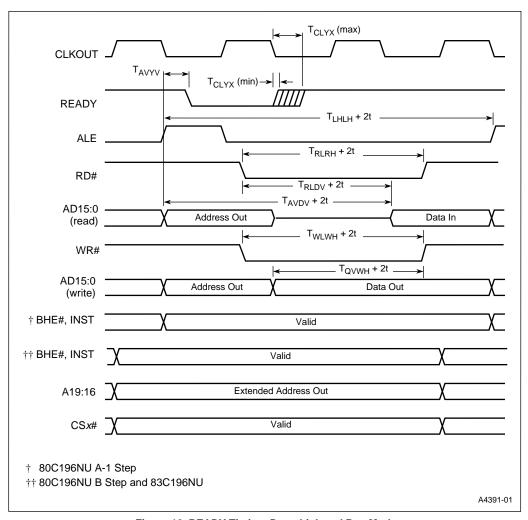

| 10.         | READY Timing, Demultiplexed Bus Mode                       |    |

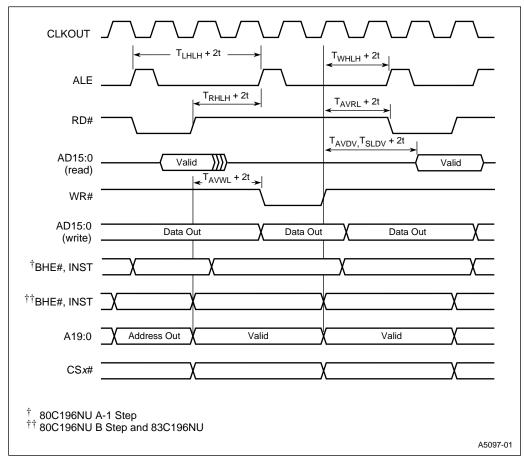

| 11.         | Deferred Bus Mode Timing Diagram                           |    |

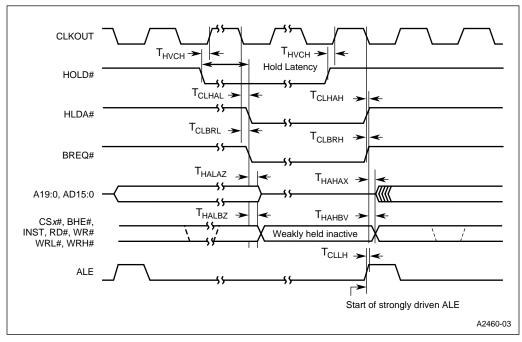

| 12.         | HOLD#, HLDA# Timing Diagram                                |    |

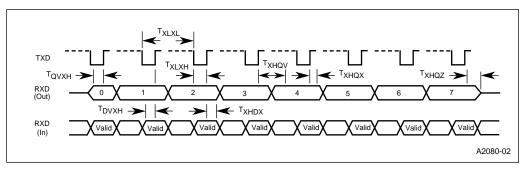

| 13.         | Serial Port Waveform — Synchronous Mode 0                  |    |

| 14.         | External Clock Drive Waveforms                             |    |

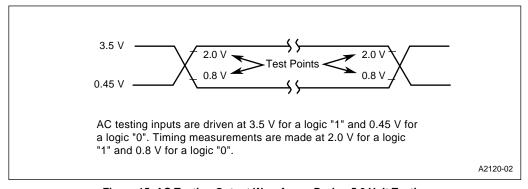

| 15.         | AC Testing Output Waveforms During 5.0 Volt Testing        |    |

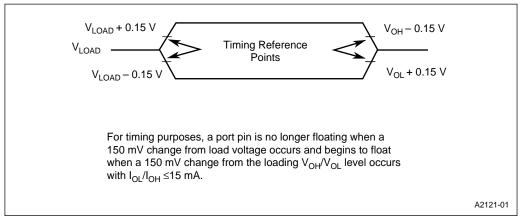

| 16.         | Float Waveforms During 5.0 Volt Testing                    | 37 |

# **Tables**

| 1.  | Description of Product Nomenclature                                             | 2  |

|-----|---------------------------------------------------------------------------------|----|

| 2.  | 80C196NU 100-pin SQFP Pin Assignment                                            |    |

| 3.  | 80C196NU 100-pin SQFP Pin Assignment Arranged by Functional Categories          |    |

| 4.  | 80C196NU 100-pin QFP Pin Assignment                                             |    |

| 5.  | 80C196NU 100-pin QFP Pin Assignment Arranged by Functional Categories           |    |

| 6.  | 83C196NU 100-pin QFP Pin Assignment                                             |    |

| 7.  | 83C196NU 100-pin QFP Pin Assignment Arranged by Functional Categories           | 11 |

| 8.  | Signal Descriptions                                                             | 12 |

| 9.  | 8XC196NU Address Map                                                            | 19 |

| 10. | DC Characteristics Over Specified Operating Conditions                          | 21 |

| 11. | AC Timing Symbol Definitions                                                    | 24 |

| 12. | AC Characteristics the 8XC196NU Will Meet, Multiplexed Bus Mode                 | 25 |

| 13. | AC Characteristics the External Memory System Must Meet, Multiplexed Bus Mode   | 26 |

| 14. | AC Characteristics the 8XC196NU Will Meet, Demultiplexed Bus Mode               | 29 |

| 15. | AC Characteristics the External Memory System Must Meet, Demultiplexed Bus Mode | 30 |

| 16. | HOLD#, HLDA# Timings                                                            | 34 |

| 17. | Serial Port Timing — Synchronous Mode 0                                         | 35 |

| 18. | External Clock Drive                                                            | 36 |

| 19. | Thermal Characteristics                                                         | 38 |

# 1.0 PRODUCT OVERVIEW

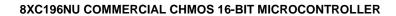

The 8XC196NU is a member of Intel's 16-bit MCS<sup>®</sup> 96 microcontroller family. The device features 1 Mbyte of linear address space, a demultiplexed bus, and a chip-select unit. The external bus can dynamically switch between multiplexed and demultiplexed operation.

Figure 1. 8XC196NU Block Diagram

# 2.0 NOMENCLATURE OVERVIEW

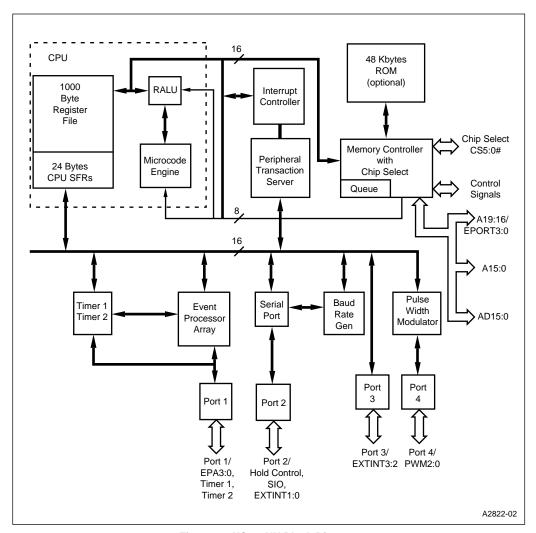

Figure 2. The 8XC196NU Family Nomenclature

**Table 1. Description of Product Nomenclature**

| Parameter                       | Options | Description                                                                       |

|---------------------------------|---------|-----------------------------------------------------------------------------------|

| Temperature and Burn-in Options | х       | Commercial operating temperature range (0°C to 70°C) with Intel standard burn-in. |

| Backgaing Ontions               | х       | QFP                                                                               |

| Packaging Options               | x       | SQFP                                                                              |

| Program–memory Options          | 0       | Without ROM                                                                       |

| Program—memory Options          | 3       | ROM                                                                               |

| Process Information             | С       | CHMOS                                                                             |

| Product Family                  | 196NU   | _                                                                                 |

| Device Speed                    | no mark | 40 MHz                                                                            |

| Device Speed                    | 50      | 50 MHz                                                                            |

**NOTE:** To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x".

# 3.0 PINOUT

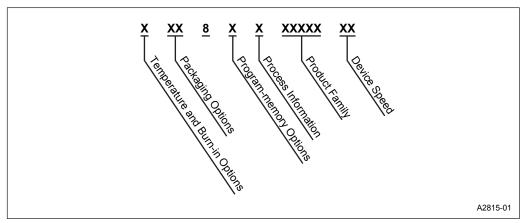

Figure 3. 80C196NU 100-pin SQFP Package

Table 2. 80C196NU 100-pin SQFP Pin Assignment

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | RESET#          | 26  | EXTINT3/P3.7    | 51  | CLKOUT/P2.7     | 76  | WR#/WRL#        |

| 2   | NMI             | 27  | EPA0/P1.0       | 52  | V <sub>cc</sub> | 77  | EPORT.3/A19     |

| 3   | NC              | 28  | V <sub>cc</sub> | 53  | V <sub>ss</sub> | 78  | EPORT.2/A18     |

| 4   | A0              | 29  | EPA1/P1.1       | 54  | XTAL2           | 79  | V <sub>SS</sub> |

| 5   | A1              | 30  | EPA2/P1.2       | 55  | XTAL1           | 80  | V <sub>cc</sub> |

| 6   | V <sub>cc</sub> | 31  | EPA3/P1.3       | 56  | V <sub>ss</sub> | 81  | EPORT.1/A17     |

| 7   | V <sub>SS</sub> | 32  | T1CLK/P1.4      | 57  | NC              | 82  | EPORT.0/A16     |

| 8   | A2              | 33  | T1DIR/P1.5      | 58  | A15             | 83  | AD15            |

| 9   | A3              | 34  | V <sub>cc</sub> | 59  | A14             | 84  | AD14            |

| 10  | A4              | 35  | T2CLK/P1.6      | 60  | A13             | 85  | AD13            |

| 11  | A5              | 36  | V <sub>SS</sub> | 61  | A12             | 86  | AD12            |

| 12  | A6              | 37  | T2DIR/P1.7      | 62  | A11             | 87  | AD11            |

| 13  | A7              | 38  | PWM0/P4.0       | 63  | A10             | 88  | AD10            |

| 14  | V <sub>cc</sub> | 39  | PWM1/P4.1       | 64  | A9              | 89  | AD9             |

| 15  | V <sub>ss</sub> | 40  | PWM2/P4.2       | 65  | A8              | 90  | V <sub>SS</sub> |

| 16  | NC              | 41  | P4.3            | 66  | V <sub>ss</sub> | 91  | AD8             |

| 17  | PLLEN1          | 42  | V <sub>cc</sub> | 67  | V <sub>cc</sub> | 92  | V <sub>cc</sub> |

| 18  | CS0#/P3.0       | 43  | V <sub>ss</sub> | 68  | PLLEN2          | 93  | AD7             |

| 19  | CS1#/P3.1       | 44  | TXD/P2.0        | 69  | ONCE            | 94  | AD6             |

| 20  | CS2#/P3.2       | 45  | RXD/P2.1        | 70  | RPD             | 95  | AD5             |

| 21  | CS3#/P3.3       | 46  | EXTINT0/P2.2    | 71  | READY           | 96  | AD4             |

| 22  | V <sub>SS</sub> | 47  | BREQ#/P2.3      | 72  | INST            | 97  | AD3             |

| 23  | CS4#/P3.4       | 48  | EXTINT1/P2.4    | 73  | ALE             | 98  | AD2             |

| 24  | CS5#/P3.5       | 49  | HOLD#/P2.5      | 74  | BHE#/WRH#       | 99  | AD1             |

| 25  | EXTINT2/P3.6    | 50  | HLDA#/P2.6      | 75  | RD#             | 100 | AD0             |

**NOTE:** To be compatible with future products, tie the NC (no connection) pins as follows: Pin 57 =  $V_{SS}$ , Pin 16 =  $V_{CC}$ , and Pin 3 = NC.

Table 3. 80C196NU 100-pin SQFP Pin Assignment Arranged by Functional Categories

| Address & Data |     | Address & Data (continued) |       | Input/Output |     |  |

|----------------|-----|----------------------------|-------|--------------|-----|--|

| Name           | Pin | Name                       | Pin   | Name         | Pin |  |

| A0             | 4   | AD12                       | 86    | CS0#/P3.0    | 18  |  |

| A1             | 5   | AD13                       | 85    | CS1#/P3.1    | 19  |  |

| A2             | 8   | AD14                       | 84    | CS2#/P3.2    | 20  |  |

| A3             | 9   | AD15                       | 83    | CS3#/P3.3    | 21  |  |

| A4             | 10  |                            |       | CS4#/P3.4    | 23  |  |

| A5             | 11  | Bus Control & S            | tatus | CS5#/P3.5    | 24  |  |

| A6             | 12  | Name                       | Pin   | EPA0/P1.0    | 27  |  |

| A7             | 13  | ALE                        | 73    | EPA1/P1.1    | 29  |  |

| A8             | 65  | BHE#/WRH#                  | 74    | EPA2/P1.2    | 30  |  |

| A9             | 64  | BREQ#                      | 47    | EPA3/P1.3    | 31  |  |

| A10            | 63  | HOLD#                      | 49    | EPORT.0      | 82  |  |

| A11            | 62  | HLDA#                      | 50    | EPORT.1      | 81  |  |

| A12            | 61  | INST                       | 72    | EPORT.2      | 78  |  |

| A13            | 60  | RD#                        | 75    | EPORT.3      | 77  |  |

| A14            | 59  | READY                      | 71    | P2.2         | 46  |  |

| A15            | 58  | WR#/WRL#                   | 76    | P2.3         | 47  |  |

| A16            | 82  |                            |       | P2.4         | 48  |  |

| A17            | 81  | Processor Con              | trol  | P2.5         | 49  |  |

| A18            | 78  | Name                       | Pin   | P2.6         | 50  |  |

| A19            | 77  | CLKOUT                     | 51    | P2.7         | 51  |  |

| AD0            | 100 | EXTINT0                    | 46    | P3.6         | 25  |  |

| AD1            | 99  | EXTINT1                    | 48    | P3.7         | 26  |  |

| AD2            | 98  | EXTINT2                    | 25    | P4.3         | 41  |  |

| AD3            | 97  | EXTINT3                    | 26    | PWM0/P4.0    | 38  |  |

| AD4            | 96  | NMI                        | 2     | PWM1/P4.1    | 39  |  |

| AD5            | 95  | ONCE                       | 69    | PWM2/P4.2    | 40  |  |

| AD6            | 94  | RESET#                     | 1     | RXD/P2.1     | 45  |  |

| AD7            | 93  | RPD                        | 70    | T1CLK/P1.4   | 32  |  |

| AD8            | 91  | XTAL1                      | 55    | T1DIR/P1.5   | 33  |  |

| AD9            | 89  | XTAL2                      | 54    | T2CLK/P1.6   | 35  |  |

| AD10           | 88  | PLLEN1                     | 17    | T2DIR/P1.7   | 37  |  |

| AD11           | 87  | PLLEN2                     | 68    | TXD/P2.0     | 44  |  |

| Power & Ground  |     |  |  |  |  |  |

|-----------------|-----|--|--|--|--|--|

| Name            | Pin |  |  |  |  |  |

| V <sub>CC</sub> | 6   |  |  |  |  |  |

| V <sub>cc</sub> | 14  |  |  |  |  |  |

| V <sub>cc</sub> | 28  |  |  |  |  |  |

| V <sub>CC</sub> | 34  |  |  |  |  |  |

| V <sub>CC</sub> | 42  |  |  |  |  |  |

| V <sub>cc</sub> | 52  |  |  |  |  |  |

| V <sub>cc</sub> | 67  |  |  |  |  |  |

| V <sub>cc</sub> | 80  |  |  |  |  |  |

| V <sub>cc</sub> | 92  |  |  |  |  |  |

| V <sub>SS</sub> | 7   |  |  |  |  |  |

| V <sub>SS</sub> | 15  |  |  |  |  |  |

| V <sub>SS</sub> | 22  |  |  |  |  |  |

| V <sub>SS</sub> | 36  |  |  |  |  |  |

| V <sub>SS</sub> | 43  |  |  |  |  |  |

| V <sub>SS</sub> | 53  |  |  |  |  |  |

| V <sub>ss</sub> | 56  |  |  |  |  |  |

| V <sub>SS</sub> | 66  |  |  |  |  |  |

| V <sub>SS</sub> | 79  |  |  |  |  |  |

| V <sub>SS</sub> | 90  |  |  |  |  |  |

| No Connection |    |  |  |  |  |

|---------------|----|--|--|--|--|

| Name Pir      |    |  |  |  |  |

| NC            | 3  |  |  |  |  |

| NC            | 16 |  |  |  |  |

| NC            | 57 |  |  |  |  |

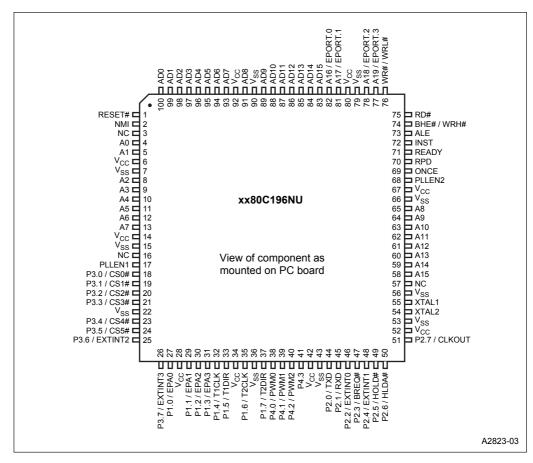

Figure 4. 80C196NU 100-pin QFP Package

Table 4. 80C196NU 100-pin QFP Pin Assignment

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | AD0             | 26  | EXTINT2/P3.6    | 51  | HOLD#/P2.5      | 76  | RD#             |

| 2   | NC              | 27  | NC              | 52  | HLDA#/P2.6      | 77  | WR#/WRL#        |

| 3   | RESET#          | 28  | EXTINT3/P3.7    | 53  | V <sub>cc</sub> | 78  | EPORT.3/A19     |

| 4   | NMI             | 29  | EPA0/P1.0       | 54  | CLKOUT/P2.7     | 79  | EPORT.2/A18     |

| 5   | NC              | 30  | V <sub>cc</sub> | 55  | V <sub>SS</sub> | 80  | V <sub>SS</sub> |

| 6   | A0              | 31  | EPA1/P1.1       | 56  | XTAL2           | 81  | V <sub>cc</sub> |

| 7   | A1              | 32  | EPA2/P1.2       | 57  | XTAL1           | 82  | EPORT.1/A17     |

| 8   | V <sub>cc</sub> | 33  | EPA3/P1.3       | 58  | V <sub>SS</sub> | 83  | EPORT.0/A16     |

| 9   | V <sub>ss</sub> | 34  | T1CLK/P1.4      | 59  | A15             | 84  | AD15            |

| 10  | A2              | 35  | T1DIR/P1.5      | 60  | A14             | 85  | AD14            |

| 11  | A3              | 36  | V <sub>cc</sub> | 61  | A13             | 86  | AD13            |

| 12  | A4              | 37  | T2CLK/P1.6      | 62  | A12             | 87  | AD12            |

| 13  | A5              | 38  | V <sub>ss</sub> | 63  | A11             | 88  | AD11            |

| 14  | A6              | 39  | T2DIR/P1.7      | 64  | A10             | 89  | AD10            |

| 15  | A7              | 40  | PWM0/P4.0       | 65  | A9              | 90  | AD9             |

| 16  | V <sub>cc</sub> | 41  | PWM1/P4.1       | 66  | A8              | 91  | V <sub>ss</sub> |

| 17  | V <sub>SS</sub> | 42  | PWM2/P4.2       | 67  | V <sub>SS</sub> | 92  | AD8             |

| 18  | PLLEN1          | 43  | P4.3            | 68  | V <sub>cc</sub> | 93  | V <sub>cc</sub> |

| 19  | CS0#/P3.0       | 44  | V <sub>cc</sub> | 69  | PLLEN2          | 94  | AD7             |

| 20  | CS1#/P3.1       | 45  | V <sub>ss</sub> | 70  | ONCE            | 95  | AD6             |

| 21  | CS2#/P3.2       | 46  | TXD/P2.0        | 71  | RPD             | 96  | AD5             |

| 22  | CS3#/P3.3       | 47  | RXD/P2.1        | 72  | READY           | 97  | AD4             |

| 23  | V <sub>ss</sub> | 48  | EXTINT0/P2.2    | 73  | INST            | 98  | AD3             |

| 24  | CS4#/P3.4       | 49  | BREQ#/P2.3      | 74  | ALE             | 99  | AD2             |

| 25  | CS5#/P3.5       | 50  | EXTINT1/P2.4    | 75  | BHE#/WRH#       | 100 | AD1             |

**NOTE:** To be compatible with future proliferations, tie the NC (no connect) pin as follows:

Pin 2 =  $V_{SS}$ Pin 5 = EA# on products with internal memory ( $V_{CC}$  = internal memory,  $V_{SS}$  = external memory)

Pin 27 =  $V_{CC}$

Table 5. 80C196NU 100-pin QFP Pin Assignment Arranged by Functional Categories

| Address & Data |     | Address & D<br>(continued |        | Input/Output |     |  |

|----------------|-----|---------------------------|--------|--------------|-----|--|

| Name           | Pin | Name                      | Pin    | Name         | Pin |  |

| A0             | 6   | AD12                      | 87     | CS0#/P3.0    | 19  |  |

| A1             | 7   | AD13                      | 86     | CS1#/P3.1    | 20  |  |

| A2             | 10  | AD14                      | 85     | CS2#/P3.2    | 21  |  |

| A3             | 11  | AD15                      | 84     | CS3#/P3.3    | 22  |  |

| A4             | 12  |                           |        | CS4#/P3.4    | 24  |  |

| A5             | 13  | Bus Control & S           | Status | CS5#/P3.5    | 25  |  |

| A6             | 14  | Name                      | Pin    | EPA0/P1.0    | 29  |  |

| A7             | 15  | ALE                       | 74     | EPA1/P1.1    | 31  |  |

| A8             | 66  | BHE#/WRH#                 | 75     | EPA2/P1.2    | 32  |  |

| A9             | 65  | BREQ#                     | 49     | EPA3/P1.3    | 33  |  |

| A10            | 64  | HOLD#                     | 51     | EPORT.0      | 83  |  |

| A11            | 63  | HLDA#                     | 52     | EPORT.1      | 82  |  |

| A12            | 62  | INST                      | 73     | EPORT.2      | 79  |  |

| A13            | 61  | RD#                       | 76     | EPORT.3      | 78  |  |

| A14            | 60  | READY                     | 72     | P2.2         | 48  |  |

| A15            | 59  | WR#/WRL#                  | 77     | P2.3 49      |     |  |

| A16            | 83  | •                         |        | P2.4         | 50  |  |

| A17            | 82  | Processor Co              | ntrol  | P2.5         | 51  |  |

| A18            | 79  | Name                      | Pin    | P2.6         | 52  |  |

| A19            | 78  | CLKOUT                    | 54     | P2.7         | 54  |  |

| AD0            | 1   | EXTINT0                   | 48     | P3.6         | 26  |  |

| AD1            | 100 | EXTINT1                   | 50     | P3.7         | 28  |  |

| AD2            | 99  | EXTINT2                   | 26     | P4.3         | 43  |  |

| AD3            | 98  | EXTINT3                   | 28     | PWM0/P4.0    | 40  |  |

| AD4            | 97  | NMI                       | 4      | PWM1/P4.1    | 41  |  |

| AD5            | 96  | ONCE                      | 70     | PWM2/P4.2    | 42  |  |

| AD6            | 95  | RESET#                    | 3      | RXD/P2.1     | 47  |  |

| AD7            | 94  | RPD                       | 71     | T1CLK/P1.4   | 34  |  |

| AD8            | 92  | XTAL1                     | 57     | T1DIR/P1.5   | 35  |  |

| AD9            | 90  | XTAL2                     | 56     | T2CLK/P1.6   | 37  |  |

| AD10           | 89  | PLLEN1                    | 18     | T2DIR/P1.7   | 39  |  |

| AD11           | 88  | PLLEN2                    | 69     | TXD/P2.0     | 46  |  |

| Power & Ground  |     |  |  |  |  |  |

|-----------------|-----|--|--|--|--|--|

| Name            | Pin |  |  |  |  |  |

| V <sub>cc</sub> | 8   |  |  |  |  |  |

| V <sub>CC</sub> | 16  |  |  |  |  |  |

| V <sub>cc</sub> | 30  |  |  |  |  |  |

| V <sub>cc</sub> | 36  |  |  |  |  |  |

| V <sub>cc</sub> | 44  |  |  |  |  |  |

| V <sub>cc</sub> | 53  |  |  |  |  |  |

| V <sub>cc</sub> | 68  |  |  |  |  |  |

| V <sub>cc</sub> | 81  |  |  |  |  |  |

| V <sub>cc</sub> | 93  |  |  |  |  |  |

| V <sub>SS</sub> | 9   |  |  |  |  |  |

| V <sub>SS</sub> | 17  |  |  |  |  |  |

| V <sub>SS</sub> | 23  |  |  |  |  |  |

| V <sub>SS</sub> | 38  |  |  |  |  |  |

| V <sub>SS</sub> | 45  |  |  |  |  |  |

| V <sub>SS</sub> | 55  |  |  |  |  |  |

| V <sub>SS</sub> | 58  |  |  |  |  |  |

| V <sub>SS</sub> | 67  |  |  |  |  |  |

| V <sub>SS</sub> | 80  |  |  |  |  |  |

| V <sub>SS</sub> | 91  |  |  |  |  |  |

| No Connection |     |  |  |  |  |

|---------------|-----|--|--|--|--|

| Name          | Pin |  |  |  |  |

| NC            | 2   |  |  |  |  |

| NC            | 5   |  |  |  |  |

| NC            | 27  |  |  |  |  |

Figure 5. 83C196NU 100-pin QFP Package

Table 6. 83C196NU 100-pin QFP Pin Assignment

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | AD0             | 26  | EXTINT2/P3.6    | 51  | HOLD#/P2.5      | 76  | RD#             |

| 2   | NC              | 27  | NC              | 52  | HLDA#/P2.6      | 77  | WR#/WRL#        |

| 3   | RESET#          | 28  | EXTINT3/P3.7    | 53  | V <sub>cc</sub> | 78  | EPORT.3/A19     |

| 4   | NMI             | 29  | EPA0/P1.0       | 54  | CLKOUT/P2.7     | 79  | EPORT.2/A18     |

| 5   | EA#             | 30  | V <sub>cc</sub> | 55  | V <sub>ss</sub> | 80  | V <sub>SS</sub> |

| 6   | A0              | 31  | EPA1/P1.1       | 56  | XTAL2           | 81  | V <sub>cc</sub> |

| 7   | A1              | 32  | EPA2/P1.2       | 57  | XTAL1           | 82  | EPORT.1/A17     |

| 8   | V <sub>cc</sub> | 33  | EPA3/P1.3       | 58  | V <sub>ss</sub> | 83  | EPORT.0/A16     |

| 9   | V <sub>ss</sub> | 34  | T1CLK/P1.4      | 59  | A15             | 84  | AD15            |

| 10  | A2              | 35  | T1DIR/P1.5      | 60  | A14             | 85  | AD14            |

| 11  | A3              | 36  | V <sub>cc</sub> | 61  | A13             | 86  | AD13            |

| 12  | A4              | 37  | T2CLK/P1.6      | 62  | A12             | 87  | AD12            |

| 13  | A5              | 38  | V <sub>ss</sub> | 63  | A11             | 88  | AD11            |

| 14  | A6              | 39  | T2DIR/P1.7      | 64  | A10             | 89  | AD10            |

| 15  | A7              | 40  | PWM0/P4.0       | 65  | A9              | 90  | AD9             |

| 16  | V <sub>cc</sub> | 41  | PWM1/P4.1       | 66  | A8              | 91  | V <sub>SS</sub> |

| 17  | V <sub>ss</sub> | 42  | PWM2/P4.2       | 67  | V <sub>SS</sub> | 92  | AD8             |

| 18  | PLLEN1          | 43  | P4.3            | 68  | V <sub>cc</sub> | 93  | V <sub>cc</sub> |

| 19  | CS0#/P3.0       | 44  | V <sub>cc</sub> | 69  | PLLEN2          | 94  | AD7             |

| 20  | CS1#/P3.1       | 45  | V <sub>SS</sub> | 70  | ONCE            | 95  | AD6             |

| 21  | CS2#/P3.2       | 46  | TXD/P2.0        | 71  | RPD             | 96  | AD5             |

| 22  | CS3#/P3.3       | 47  | RXD/P2.1        | 72  | READY           | 97  | AD4             |

| 23  | V <sub>ss</sub> | 48  | EXTINT0/P2.2    | 73  | INST            | 98  | AD3             |

| 24  | CS4#/P3.4       | 49  | BREQ#/P2.3      | 74  | ALE             | 99  | AD2             |

| 25  | CS5#/P3.5       | 50  | EXTINT1/P2.4    | 75  | BHE#/WRH#       | 100 | AD1             |

**NOTE:** To be compatible with future proliferations, tie the NC (no connect) pins as follows:

$\begin{aligned} &\text{Pin 2} = \text{V}_{\text{SS}} \\ &\text{Pin 27} = \text{V}_{\text{CC}}. \end{aligned}$

Table 7. 83C196NU 100-pin QFP Pin Assignment Arranged by Functional Categories

| Address & Data |     | Address & Da<br>(continued) |       | Input/Outpu | t   |

|----------------|-----|-----------------------------|-------|-------------|-----|

| Name           | Pin | Name                        | Pin   | Name        | Pin |

| A0             | 6   | AD12                        | 87    | CS0#/P3.0   | 19  |

| A1             | 7   | AD13                        | 86    | CS1#/P3.1   | 20  |

| A2             | 10  | AD14                        | 85    | CS2#/P3.2   | 21  |

| A3             | 11  | AD15                        | 84    | CS3#/P3.3   | 22  |

| A4             | 12  | Bus Control & S             | tatus | CS4#/P3.4   | 24  |

| A5             | 13  | Name                        | Pin   | CS5#/P3.5   | 25  |

| A6             | 14  | ALE                         | 74    | EPA0/P1.0   | 29  |

| A7             | 15  | BHE#/WRH#                   | 75    | EPA1/P1.1   | 31  |

| A8             | 66  | BREQ#                       | 49    | EPA2/P1.2   | 32  |

| A9             | 65  | HOLD#                       | 51    | EPA3/P1.3   | 33  |

| A10            | 64  | HLDA#                       | 52    | EPORT.0     | 83  |

| A11            | 63  | INST                        | 73    | EPORT.1     | 82  |

| A12            | 62  | RD#                         | 76    | EPORT.2     | 79  |

| A13            | 61  | READY                       | 72    | EPORT.3     | 78  |

| A14            | 60  | WR#/WRL#                    | 77    | P2.2        | 48  |

| A15            | 59  |                             |       | P2.3        | 49  |

| A16            | 83  | Processor Con               | trol  | P2.4        | 50  |

| A17            | 82  | Name                        | Pin   | P2.5        | 51  |

| A18            | 79  | CLKOUT                      | 54    | P2.6        | 52  |

| A19            | 78  | EXTINT0                     | 48    | P2.7        | 54  |

| AD0            | 1   | EXTINT1                     | 50    | P3.6        | 26  |

| AD1            | 100 | EXTINT2                     | 26    | P3.7        | 28  |

| AD2            | 99  | EXTINT3                     | 28    | P4.3        | 43  |

| AD3            | 98  | NMI                         | 4     | PWM0/P4.0   | 40  |

| AD4            | 97  | ONCE                        | 70    | PWM1/P4.1   | 41  |

| AD5            | 96  | RESET#                      | 3     | PWM2/P4.2   | 42  |

| AD6            | 95  | RPD                         | 71    | RXD/P2.1    | 47  |

| AD7            | 94  | XTAL1                       | 57    | T1CLK/P1.4  | 34  |

| AD8            | 92  | XTAL2                       | 56    | T1DIR/P1.5  | 35  |

| AD9            | 90  | PLLEN1                      | 18    | T2CLK/P1.6  | 37  |

| AD10           | 89  | PLLEN2                      | 69    | T2DIR/P1.7  | 39  |

| AD11           | 88  | EA#                         | 5     | TXD/P2.0    | 46  |

| Power & Ground  |     |  |  |  |

|-----------------|-----|--|--|--|

| Name            | Pin |  |  |  |

| V <sub>CC</sub> | 8   |  |  |  |

| V <sub>CC</sub> | 16  |  |  |  |

| V <sub>CC</sub> | 30  |  |  |  |

| V <sub>cc</sub> | 36  |  |  |  |

| V <sub>cc</sub> | 44  |  |  |  |

| V <sub>cc</sub> | 53  |  |  |  |

| V <sub>cc</sub> | 68  |  |  |  |

| V <sub>cc</sub> | 81  |  |  |  |

| V <sub>cc</sub> | 93  |  |  |  |

| V <sub>SS</sub> | 9   |  |  |  |

| V <sub>SS</sub> | 17  |  |  |  |

| V <sub>SS</sub> | 23  |  |  |  |

| V <sub>SS</sub> | 38  |  |  |  |

| V <sub>SS</sub> | 45  |  |  |  |

| V <sub>SS</sub> | 55  |  |  |  |

| V <sub>ss</sub> | 58  |  |  |  |

| V <sub>SS</sub> | 67  |  |  |  |

| V <sub>SS</sub> | 80  |  |  |  |

| V <sub>SS</sub> | 91  |  |  |  |

| No Connection |     |  |  |

|---------------|-----|--|--|

| Name          | Pin |  |  |

| NC            | 2   |  |  |

| NC            | 27  |  |  |

# 4.0 SIGNALS

**Table 8. Signal Descriptions**

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A15:0  | I/O  | System Address Bus  These address lines provide address bits 0–15 during the entire external memory cycle during both multiplexed and demultiplexed bus modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| A19:16 | I/O  | Address Lines 16–19 These address lines provide address bits 16–19 during the entire external memory cycle, supporting extended addressing of the 1 Mbyte address space.  NOTE: Internally, there are 24 address bits; however, only 20 external address pins (A19:0) are implemented. The internal address space is 16 Mbytes (000000–FFFFFFH) and the external address space is 1 Mbyte (00000–FFFFFFH). The device resets to FF2080H in internal memory or F2080H in external memory.  A19:16 are multiplexed with EPORT.3:0.                                                                                                                                                                                                                                                                                                  |  |

| AD15:0 | I/O  | Address/Data Lines  The functions of these pins depend on the bus size and mode. When a bus access is not occurring, these pins revert to their I/O port function.  16-bit Multiplexed Bus Mode: AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode: AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  16-bit Demultiplexed Mode: AD15:0 drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode: AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus. |  |

| ALE    | 0    | Address Latch Enable  This active-high output signal is asserted only during external memory cycles.  ALE signals the start of an external bus cycle and indicates that valid address information is available on the system address/data bus (A19:16 and AD15:0 for a multiplexed bus; A19:0 for a demultiplexed bus). ALE differs from ADV# in that it does not remain active during the entire bus cycle.  An external latch can use this signal to demultiplex the address bits 0–15 from the address/data bus in multiplexed mode.                                                                                                                                                                                                                                                                                           |  |

Table 8. Signal Descriptions (Continued)

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BHE#   | 0    | Byte High Enable <sup>†</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|        |      | During 16-bit bus cycles, this active-low output signal is asserted for word reads and writes and high-byte reads and writes to external memory. BHE# indicates that valid data is being transferred over the upper half of the system data bus. Use BHE#, in conjunction with A0, to determine which memory byte is being transferred over the system bus:                                                                                                                                         |  |  |

|        |      | BHE# A0 Byte(s) Accessed                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|        |      | 0 0 both bytes 0 1 high byte only 1 0 low byte only                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|        |      | BHE# is multiplexed with WRH#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|        |      | <sup>†</sup> The chip configuration register 0 (CCR0) determines whether this pin functions as BHE# or WRH#. CCR0.2 = 1 selects BHE#; CCR0.2 = 0 selects WRH#.                                                                                                                                                                                                                                                                                                                                      |  |  |

| BREQ#  | 0    | Bus Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|        |      | This active-low output signal is asserted during a hold cycle when the bus controller has a pending external memory cycle. When the bus-hold protocol is enabled (WSR.7 is set), the P2.3/BREQ# pin can function only as BREQ#, regardless of the configuration selected through the port configuration registers (P2_MODE, P2_DIR, and P2_REG). An attempt to change the pin configuration is ignored until the bus-hold protocol is disabled (WSR.7 is cleared).  BREQ# is multiplexed with P2.3. |  |  |

| CLKOUT | 0    | Clock Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| OLNOO1 |      | Output of the internal clock generator. The CLKOUT frequency is ½ the internal operating frequency (f). CLKOUT has a 50% duty cycle.  CLKOUT is multiplexed with P2.7.                                                                                                                                                                                                                                                                                                                              |  |  |

| CS5#:0 | 0    | Chip-select Lines 0–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 035#.0 |      | The active-low output CS x# is asserted during an external memory cycle when the address to be accessed is in the range programmed for chip select x. If the external memory address is outside the range assigned to the six chip selects, no chip-select output is asserted and the bus configuration defaults to the CS5# values.                                                                                                                                                                |  |  |

|        |      | Immediately following reset, CS0# is automatically assigned to the range FF2000–FF20FFH (F2000–F20FFH if external).                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|        |      | CS5:0# is multiplexed with P3.5:0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| EA#    | I    | External Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|        |      | This active-low input signal determines whether memory accesses to special purpose and program memory partitions (FF2000–FFDFFFH) are directed to internal or external memory. These memory accesses are directed to internal memory if EA# is deasserted and to external memory if EA# is asserted. For an access to any other memory location, the value of EA# is irrelevant.                                                                                                                    |  |  |

|        |      | EA# is not latched and can be switched dynamically during normal operating mode. Be sure to thoroughly consider the issues, such as different access times for internal and external memory, before using this dynamic switching capability.                                                                                                                                                                                                                                                        |  |  |

|        |      | Always connect EA# to $\rm V_{\rm SS}$ when using a microcontroller that has no internal nonvolatile memory.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

Table 8. Signal Descriptions (Continued)

| Name      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPA3:0    | I/O  | Event Processor Array (EPA) Input/Output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |      | These are the high-speed input/output pins for the EPA capture/compare channels. For high-speed PWM applications, the outputs of two EPA channels (either EPA0 and EPA1 or EPA2 and EPA3) can be remapped to produce a PWM waveform on a shared output pin.                                                                                                                                                                                                                                     |

|           |      | EPA3:0 are multiplexed with P1.3:0.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EPORT.3:0 | I/O  | Extended Addressing Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |      | This is a standard, 4-bit, bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |      | EPORT.3:0 are multiplexed with A19:16.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EXTINT3:0 | I    | External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |      | In normal operating mode, a rising edge on EXTINTx sets the EXTINTx interrupt pending bit. EXTINTx is sampled during phase 2 (CLKOUT high). The minimum high time is one state time.                                                                                                                                                                                                                                                                                                            |

|           |      | In standby and powerdown modes, asserting the EXTINTx signal for at least 50 ns causes the device to resume normal operation. The interrupt need not be enabled, but the pin must be configured as a special-function input. If the EXTINTx interrupt is enabled, the CPU executes the interrupt service routine. Otherwise, the CPU executes the instruction that immediately follows the command that invoked the power-saving mode.                                                          |

|           |      | In idle mode, asserting any enabled interrupt causes the device to resume normal operation.                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |      | EXTINT0 is multiplexed with P2.2, EXTINT1 is multiplexed with P2.4, EXTINT2 is multiplexed with P3.6, and EXTINT3 is multiplexed with P3.7.                                                                                                                                                                                                                                                                                                                                                     |

| HLDA#     | 0    | Bus Hold Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           |      | This active-low output indicates that the CPU has released the bus as the result of an external device asserting HOLD#. When the bus-hold protocol is enabled (WSR.7 is set), the P2.6/HLDA# pin can function only as HLDA#, regardless of the configuration selected through the port configuration registers (P2_MODE, P2_DIR, and P2_REG). An attempt to change the pin configuration is ignored until the bus-hold protocol is disabled (WSR.7 is cleared). HLDA# is multiplexed with P2.6. |

| HOLD#     |      | Bus Hold Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |      | An external device uses this active-low input signal to request control of the bus. When the bus-hold protocol is enabled (WSR.7 is set), the P2.5/HOLD# pin can function only as HOLD#, regardless of the configuration selected through the port configuration registers (P2_MODE, P2_DIR, and P2_REG). An attempt to change the pin configuration is ignored until the bus-hold protocol is disabled (WSR.7 is cleared).                                                                     |

|           |      | HOLD# is multiplexed with P2.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INST      | 0    | Instruction Fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |      | This active-high output signal is valid only during external memory bus cycles. When high, INST indicates that an instruction is being fetched from external memory. The signal remains high during the entire bus cycle of an external instruction fetch. INST is low for data accesses, including interrupt vector fetches and chip configuration byte reads. INST is low during internal memory fetches.                                                                                     |

Table 8. Signal Descriptions (Continued)

| Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                                                                                                                                           |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI      | I    | Nonmaskable Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                                                                                                                                                           |

|          |      | interrupt. NMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | has the high | e, a rising edge on NMI generates a nonmaskable<br>ghest priority of all prioritized interrupts. Assert NMI for<br>ne to guarantee that it is recognized. |

| ONCE     | - 1  | On-circuit Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                                                                                                                           |

|          |      | Holding ONCE high during the rising edge of RESET# places the device into on-circuit emulation (ONCE) mode. This mode puts all pins into a high-impedance state, thereby isolating the device from other components in the system. The value of ONCE is latched when the RESET# pin goes inactive. While the device is in ONCE mode, you can debug the system using a clip-on emulator. To exit ONCE mode, reset the device by pulling the RESET# signal low. To prevent accidental entry into ONCE mode, connect the ONCE pin to V <sub>SS</sub> . |              |                                                                                                                                                           |

| P1.7:0   | I/O  | Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                                                                                                                           |

|          |      | This is a standable special-fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | ctional port that is multiplexed with individually select-<br>nals.                                                                                       |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | llows: P1.0/EPA0, P1.1/EPA1, P1.2/EPA2, P1.3/EPA3, R, P1.6/T2CLK, and P1.7/T2DIR.                                                                         |

| P2.7:0   | I/O  | Port 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                                                                                                                           |

|          |      | able special-f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | unction sigr |                                                                                                                                                           |

|          |      | Port 2 is multiplexed as follows: P2.0/TXD, P2.1/RXD, P2.2/EXTINT0, P2.3/BREQ#, P2.4/EXTINT1, P2.5/HOLD#, P2.6/HLDA#, and P2.7/CLKOUT.                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                                                                                                                           |

| P3.7:0   | I/O  | Port 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                                                                                                                           |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •            | onal, standard I/O port.                                                                                                                                  |

|          |      | Port 3 is multiplexed as follows: P3.0/CS0#, P3.1/CS1#, P3.2/CS2#, P3.3/CS3#, P3.4/CS4#, P3.5/CS5#, P3.6/EXTINT2, and P3.7/EXTINT3.                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                                                                                                                                           |

| P4.3:0   | I/O  | Port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                                                                                                                                           |

|          |      | This is a 4-bit, bidirectional, standard I/O port with high-current drive capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                                                                                                                                                           |

|          |      | Port 4 is multiplexed as follows: P4.0/PWM0, P4.1/PWM1, and P4.2/PWM2. P4.3 is not multiplexed.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                                                                                                                                           |

| PLLEN2:1 | I    | Phase-locked Loop 1 and 2 Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                                                                                                                                                           |

|          |      | These input pins are used to enable the on-chip clock multiplier feature and select either the doubled or quadrupled clock speed as follows:                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                                                                                                                                           |

|          |      | PLLEN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PLLEN1       | Mode                                                                                                                                                      |

|          |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0            | Standard mode; clock multiplier circuitry disabled.<br>Internal clock equals the XTAL1 input frequency.                                                   |

|          |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0            | Reserved <sup>†</sup>                                                                                                                                     |

|          |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1            | Doubled mode; clock multiplier circuitry enabled. Internal clock is twice the XTAL1 input frequency.                                                      |

|          |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1            | Quadrupled mode; clock multiplier circuitry enabled.<br>Internal clock is four times the XTAL1 input frequency.                                           |

|          |      | † This reserved combination causes the device to enter an unsupported test                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                                                                                                                                           |

|          |      | mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                                                                                                                                                           |

Table 8. Signal Descriptions (Continued)

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |