# KNX/ EIB TRANSCEIVER PRODUCTION DATA - JAN 15, 2015

E981.03

# **Key Features**

- ► Certified with KNX® TP1-256 application

- Autonomous MAC and individual physical address

- Included protocol handling

- Included power supply for bus powered applications with selectable bus current limitation

# **KNX®** Interface

- Extended frames with up to 254 byte payload

- Analog Mode (direct RX / TX interface)

- Autonomous Telegram trigger

- Alarm Telegram

- Autonomous poll data transfer

## **UART** host interface

- Supports 9.6 k, 19.2 k, 115.2 k

- ▶ 9 bit mode for easy data stream interpretation

- Optional CRC (at 19.2kBd and 115.2 kBd)

## SPI™ host interface

▶ if not used 4 GPIOs are available

# Included power supplies:

- ▶ 20V supply, up to 20mA

- 3.3V (70mA) / 5V (70mA) DC/DC converter

# **General Description**

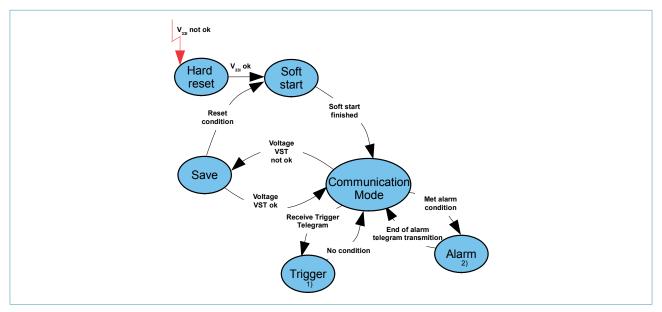

The E981.03 combines the TP1-256 physical layer, the communication controller and two DC supply outputs for bus powered applications. The internal power management assures **KNX** conformance under all load conditions.

The connection between the E981.03 and the host processor can be established by either UART or SPI compatible interfaces, or in direct Analog Mode.

# **Applications**

- Sensors, actuators, routers, gateways,

Bus-powered or externally supplied

- Security applications

# **Ordering Information**

| Ordering-No.: | Temp Range     | Package |

|---------------|----------------|---------|

| E98103A38B    | -25°C to +85°C | QFN32L7 |

**KNX** is a **Konnex Association** registered trademark. SPI™ is a Motorola Inc. trademark.

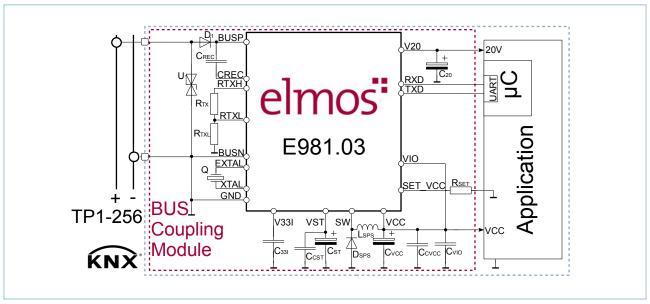

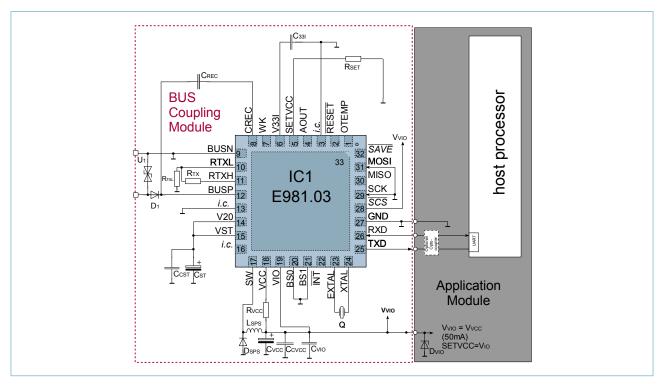

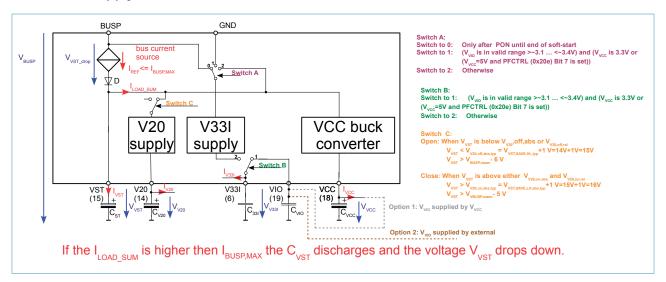

# **Typical Application Circuit**

$Elmos \ Semiconductor \ AG \ reserves \ the \ right \ to \ change \ the \ detail \ specifications \ as \ may \ be \ required \ to \ permit \ improvements \ in \ the \ design \ of \ its \ products.$

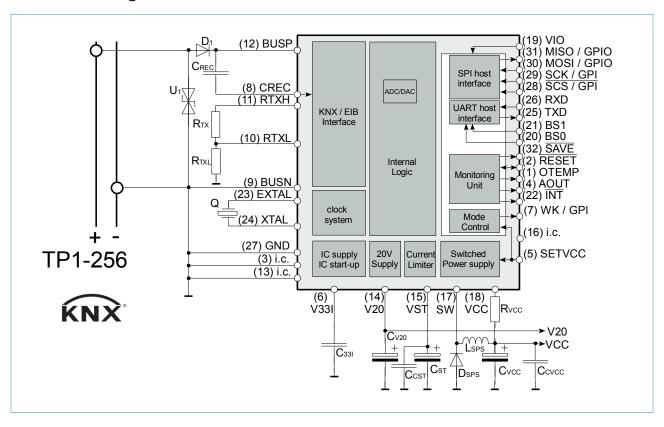

# **Functional Diagram**

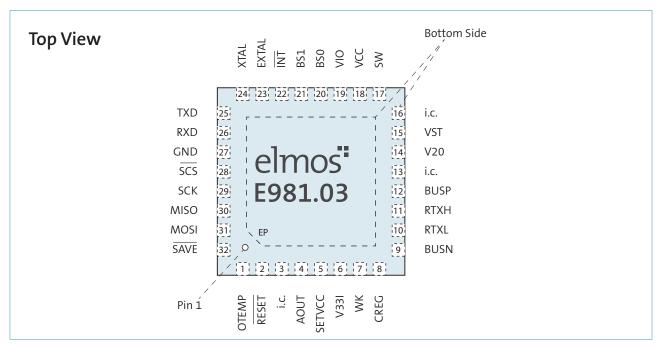

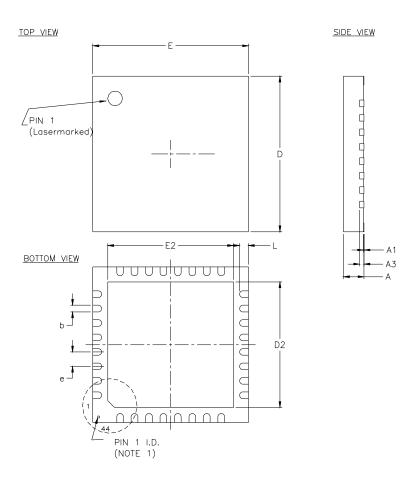

# **Pin Configuration**

Note: Not to scale, EP Exposed die pad

# **Pin Description**

| Pin | Name   | Type 1) | Pull | Description                                                                                                                                                                        |

|-----|--------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ОТЕМР  | D_O     | -    | Over-temperature warning                                                                                                                                                           |

| 2   | RESET  | D_IO    | Up   | Bidirectional reset pin (low active)                                                                                                                                               |

| 3   | i.c.   | -       | -    | Reserved for factory use, connect to GND during operation.                                                                                                                         |

| 4   | AOUT   | A_O     | -    | Analog multiplexer output                                                                                                                                                          |

| 5   | SETVCC | D_I     | 2)   | Combination of - selection of the VCC output voltage and - alarm function activation                                                                                               |

| 6   | V33I   | S       | -    | 3.3V internal supply: Connect to external capacitor                                                                                                                                |

| 7   | WK     | HV_D_IO | -    | Output with tri-state capability; used for <b>KNX</b> telegram trigger<br>Output [default]: VIO related output levels<br>Input: VST tolerant. Thresholds V <sub>V33i</sub> related |

| 8   | CREC   | HV_A_I  | -    | Receive pin for KNX bus communication                                                                                                                                              |

| 9   | BUSN   | S       | -    | Connection to the negative bus line                                                                                                                                                |

| 10  | RTXL   | HV_A_IO | -    | Ground connection of external resistor RTX                                                                                                                                         |

| 11  | RTXH   | HV_A_IO | -    | KNX send output pin - upper connection of external resistor RTX                                                                                                                    |

| 12  | BUSP   | HV_S    | -    | Connection to positive KNX bus via external diode for reverse polarity protection                                                                                                  |

| 13  | i.c.   | -       | -    | Reserved for factory use, connect to GND during operation.                                                                                                                         |

| 14  | V20    | HV_S    | -    | 20V DC supply output                                                                                                                                                               |

| 15  | VST    | HV_S    | -    | Connection to external storage capacitor CST                                                                                                                                       |

| 16  | i.c.   | -       | -    | Do not connect externally                                                                                                                                                          |

| 17  | SW     | HV_A_IO | -    | Switched output of DC/ DC converter                                                                                                                                                |

| 18  | VCC    | A_I     | -    | DC/ DC converter output voltage control input                                                                                                                                      |

| 19  | VIO    | S       | -    | Supply for digital IO pins (connect to VCC if no external supply is used)                                                                                                          |

| 20  | BS0    | D_I     | Down | Baud rate select pin 0                                                                                                                                                             |

| 21  | BS1    | D_I     | Down | Baud rate select pin 1                                                                                                                                                             |

| 22  | ĪNT    | D_0     | -    | Used for KNX collision trigger (low active)                                                                                                                                        |

| 23  | EXTAL  | D_0     | -    | External crystal terminal 2                                                                                                                                                        |

| 24  | XTAL   | D_I     | -    | External crystal terminal 1 or clock input if no crystal is connected                                                                                                              |

| 25  | TXD    | D_0     | -    | UART transmit signal: from E981.03 to host processor (push/pull)                                                                                                                   |

| 26  | RXD    | D_I     | Down | UART receive signal: from host processor to E981.03                                                                                                                                |

| 27  | GND    | S       | -    | GND pin                                                                                                                                                                            |

| 28  | SCS    | D_I     | Up   | SPI chip select (low active) or <b>G</b> eneral <b>P</b> urpose <b>I</b> nput if SPI is disabled                                                                                   |

| 29  | SCK    | D_I     | Down | SPI clock or GPI if SPI is disabled                                                                                                                                                |

| 30  | MISO   | D_IO    | -    | SPI master in slave out data line or GPIO if SPI is disabled                                                                                                                       |

| 31  | MOSI   | D_IO    | -    | SPI master out slave in data line or GPIO if SPI is disabled                                                                                                                       |

| 32  | SAVE   | D_O     | Up   | VST under voltage pre alarm signal (low active)                                                                                                                                    |

| 33  | EP     |         |      | Exposed Die Pad                                                                                                                                                                    |

<sup>1)</sup> D = digital, A = analog, S = supply, I = input, O = output, HV = high voltage

<sup>2)</sup> Internally weak pulled to V33I/2. A open pin is the alarm condition. To select a VCC voltage push it to VIO or pull it to GND.

# 1 Absolute Maximum Ratings

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages with respect to ground. Currents flowing into terminals are positive, those drawn out of a terminal are negative.

| Description                                                                                                                                                        | Symbol                  | Min    | Max                     | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|-------------------------|------|

| BUSP voltage                                                                                                                                                       | V <sub>BUSP</sub>       | -0.3   | 55                      | V    |

| BUSP voltage during surge pulse (t < 150μs)                                                                                                                        | V <sub>BUSP_surge</sub> | -0.3   | 65                      | V    |

| Junction temperature                                                                                                                                               | T <sub>j</sub>          | -45    | 150                     | °C   |

| Storage temperature                                                                                                                                                | T <sub>s</sub>          | -45    | 150                     | °C   |

| ESD immunity (human body model, this test can be applied between any two pins of the IC)                                                                           | V <sub>ESD,hbm</sub>    | -2     | 2                       | kV   |

| Voltage at digital and analog VIO pins:<br>RESET, SAVE, XTAL, INT, SETVCC, OTEMP, SCS, SCK, MOSI,<br>MISO, RXD, TXD, BSO, BS1, AOUT                                | V                       | -0.3 V | V <sub>IO</sub> + 0.3 V |      |

| Voltage at WK pin                                                                                                                                                  | V <sub>wK</sub>         | -0.3   | 40                      | V    |

| Voltage at VST pin                                                                                                                                                 | V <sub>VST</sub>        | -0.3   | 40                      | V    |

| Voltage at SW pin                                                                                                                                                  | V <sub>sw</sub>         | -5 V   | V <sub>ST</sub> + 0.3 V |      |

| Voltage at VCC pin                                                                                                                                                 | V <sub>vcc</sub>        | -0.3   | 8                       | V    |

| Voltage at VIO pin                                                                                                                                                 | V <sub>VIO</sub>        | -0.3   | 7                       | V    |

| Overall current through digital and analog VIO pins (latch up immunity): RESET, SAVE, XTAL, INT, SETVCC, OTEMP, SCS, SCK, MOSI, MISO, RXD, TXD, BSO, BS1, WK, AOUT | I                       | -100   | 100                     | mA   |

| Current through digital and analog VIO pins (latch up immunity): RESET, SAVE, XTAL, INT, SETVCC, OTEMP, SCS, SCK, MOSI, MISO, RXD, TXD, BSO, BS1, WK               | I                       | -70    | 70                      | mA   |

| Voltage at pin EXTAL                                                                                                                                               | V <sub>EXTAL</sub>      | -0.3   | +3.6                    | V    |

| Input voltage at CREC pin                                                                                                                                          | V <sub>CREC</sub>       | -15 V  | V <sub>BUSP</sub>       |      |

| Voltage at pins RTXH, RTXL                                                                                                                                         | V <sub>RTX</sub>        | -0.3 V | V <sub>BUSP</sub>       |      |

| Current through RTXL pin                                                                                                                                           | I <sub>RTXL</sub>       | 0      | 800                     | mA   |

| Current through AOUT pin                                                                                                                                           | I <sub>AOUT</sub>       | -10    | 10                      | mA   |

| Voltage at pin V33I pin                                                                                                                                            | V <sub>V33I</sub>       | -0.3   | +3.6                    | V    |

| Voltage at pin V20                                                                                                                                                 | V <sub>V20</sub>        | -0.3 V | V <sub>ST</sub> + 0.3 V |      |

# **2 Recommended Operation Conditions**

| Description                                  | Condition | Symbol               | Min | Тур | Max  | Unit |

|----------------------------------------------|-----------|----------------------|-----|-----|------|------|

| Ambient temperature                          |           | T <sub>amb</sub>     | -25 | 25  | 85   | °C   |

| External storage capacitance 4)              |           | C <sub>ST</sub>      | 270 | 330 | 1000 | μF   |

| C <sub>st</sub> equivalent series resistance |           | R <sub>ESR,CST</sub> | 0.1 |     | 1    | Ω    |

| C <sub>st</sub> voltage capability           |           | V <sub>CST</sub>     | 35  |     |      | V    |

| Parallel ceramic capacitance VST to GND      |           | C <sub>CER,ST</sub>  | 80  | 100 | 120  | nF   |

| Average bus idle voltage                     |           | V <sub>BUSP</sub>    | 20  | 30  | 33   | V    |

| 20V supply external capacitance 7)           |           | C <sub>20</sub>      | 10  | 22  |      | μF   |

| C20 equivalent series resistance             |           | R <sub>ESR,C20</sub> | 0.1 |     | 1    | Ω    |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

| Description                                                                                        | Condition                             | Symbol                        | Min     | Тур     | Max                   | Unit |

|----------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|---------|---------|-----------------------|------|

| 20V load current, this current is positive from the supply to the output                           |                                       | I <sub>V20</sub> 8)           | 0       |         | 20                    | mA   |

| V <sub>cc</sub> output capacitance                                                                 | L <sub>sps</sub> =330μH               | C <sub>VCC,L330µ</sub>        | 10      | 47      | 0.6 · C <sub>ST</sub> | μF   |

| V <sub>cc</sub> output capacitance                                                                 | L <sub>SPS</sub> =1000μH              | C <sub>VCC,L1000µ</sub>       | 68      | 100     | 0.6 · C <sub>ST</sub> | μF   |

| C <sub>vcc</sub> equivalent series resistance                                                      | L <sub>SPS</sub> =330μH <sup>2)</sup> | R <sub>ESR,CVCC,L330µ</sub>   | 0.2     | 0.5     | 0.8                   | Ω    |

| C <sub>vcc</sub> equivalent series resistance                                                      | L <sub>2)SPS</sub> =1000μH            | R <sub>ESR,CVCC, L1000µ</sub> | 1       | 1.25    | 1.5                   | Ω    |

| Ceramic capacitance V <sub>cc</sub> to ground                                                      |                                       | C <sub>CVCC</sub>             | 80      | 100     | 120                   | nF   |

| DC / DC converter inductance                                                                       |                                       | L <sub>SPS</sub>              | 270     | 330     | 1200                  | μН   |

| L <sub>sps</sub> series resistance                                                                 |                                       | R <sub>L,SPS</sub>            | 1       | 3       | 10                    | Ω    |

| Saturation current of L <sub>SPS</sub>                                                             | 3)                                    | <br>  sat,SPS                 | 160     |         |                       | mA   |

| Maximum forward voltage of the external diode                                                      | I=150mA                               | V <sub>f,DSPS</sub>           |         | 0.6     | 1                     | V    |

| Reverse recovery time of the external diode                                                        |                                       | t <sub>rr,DSPS</sub>          |         |         | 50                    | ns   |

| V <sub>cc</sub> load current in 3.3 V mode, this current is positive from the supply to the output | L <sub>SPS</sub> =330μH               | VCC3.3,L330μ 8)               | 0       |         | 50                    | mA   |

| V <sub>cc</sub> load current in 3.3 V mode, this current is positive from the supply to the output | L <sub>SPS</sub> =1000μH              | I <sub>VCC3.3,L1000μ</sub> 8) | 0       |         | 70                    | mA   |

| V <sub>cc</sub> load current in 5V mode, this current is positive from the supply to the output    | L <sub>SPS</sub> =330μH               | I <sub>VCC5,L330μ</sub> 8)    | 0       |         | 30                    | mA   |

| V <sub>cc</sub> load current in 5V mode, this current is positive from the supply to the output    | L <sub>SPS</sub> =1000μH              | I <sub>VCC5,L1000μ</sub> 8)   | 0       |         | 70                    | mA   |

| Digital IO interface voltage <sup>6)</sup>                                                         | V <sub>IO,norm</sub> =5V              | V <sub>IO,5</sub>             | 4.75    |         | 5.25                  | V    |

| Digital IO interface voltage <sup>6)</sup>                                                         | V <sub>IO,norm</sub> =3.3V            | V <sub>IO,33</sub>            | 3.15    |         | 3.45                  | V    |

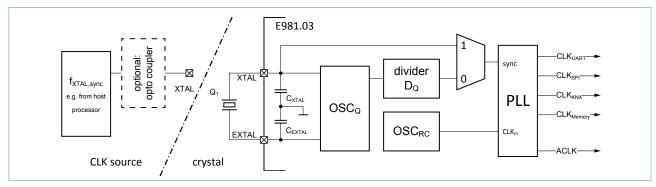

| Crystal frequency (+- 50 ppm)                                                                      |                                       | f <sub>o</sub>                |         | 7.3728  |                       | MHz  |

| Synchronization clock frequency applied at pin XTAL                                                | no crystal in-<br>stalled             | f <sub>XTAL,sync</sub>        | 126.537 | 126.562 | 126.588               | Hz   |

| Receiver decoupling capacitance                                                                    |                                       | C <sub>CREC</sub>             | 50      | 56      | 62                    | nF   |

| External send resistance                                                                           |                                       | R <sub>TX</sub>               | 44.5    | 47      | 49.4                  | Ω    |

| External send resistor power dissipation 1)                                                        |                                       | P <sub>RTX</sub>              | 1       |         |                       | W    |

| System level ESD protection resistance 5)                                                          |                                       | $R_{SET;}R_{VCC}$             |         | 1       |                       | kΩ   |

| System level ESD protection zener-diode 5)                                                         |                                       | $V_{zDiode}$                  |         |         | 6.2                   | V    |

| Analog monitor (AOUT - pin) current                                                                |                                       | I <sub>AOUT</sub>             | -50     |         | 50                    | μΑ   |

| External send pull-down                                                                            |                                       | R <sub>TXL</sub>              | 9       | 10      | 11                    | kΩ   |

- 1) For telegram rates >  $50\% P_{RTX} = 2 W$  is recommended.

- 2) The lower limit is necessary for DC/ DC control.

The upper limit is a result of ripple considerations: voltage ripple is ESR \* current ripple of LSPS.

To guarantee this over lifetime it is useful to use a low ESR capacitor and realize the lower limit with a series resistor.

- 3)  $I_{sat.SPS}$  is the DC current that causes an inductance drop of 20 %.

- 4) Smaller  $C_{st}$  down to 47  $\mu$ F can be used, however the load step capability has to be proved experimentally.

- 5) Only necessary in case of the E981.03 being connected to a separate application module.

These components only ensuring to meet the absolute maximum rating in case of connecting and disconnecting the application module. If the connector guarantees to connect GND potential first, the ESD protection is not needed.

- 6) For better elaboration of the ADC results a stable VIO is highly recommended.

- 7) High capacitance may affect the Reset / Power up Sequence time, as it is loaded with current limitation  $I_{V20(max)}$

- 8) To use the maximum current capability on VCC and V20 it is needed to change MAX\_BUS\_CURR settings before switching on high current consumption. Additionally a continuous under voltage condition on BUSP could reduce available current. To prevent unexpected under voltage conditions it is strongly recommended to observe VVST and implement a power management system. The voltage VVST could be observed ADC converted trough UART or SPI. For details read chapter 6.3 and 10.2.

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# **3 Electrical Characteristics**

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25^{\circ}C ... +85^{\circ}C, unless otherwise noted.$  Positive currents are flowing into the device pins. Typical values are at  $T_{AMB} = +25^{\circ}C$ , unless otherwise noted.)

| Description                                                                      | Condition                                                      | Symbol                        | Min   | Тур                              | Max  | Unit |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------|-------|----------------------------------|------|------|--|

| E981.03 Modes, Sequences and Functions - DC Characteristics                      |                                                                |                               |       |                                  |      |      |  |

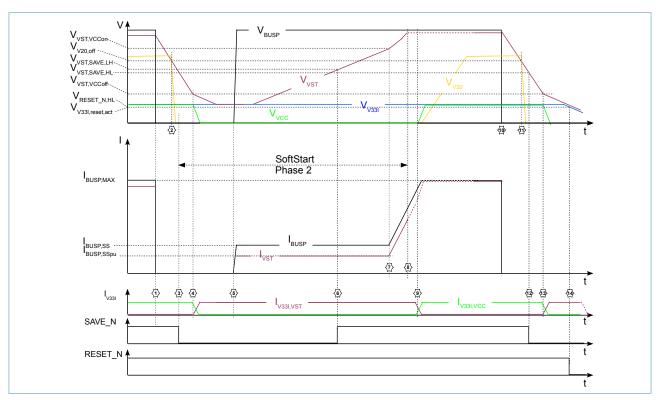

| Voltage level at V33I pin for activating hard reset mode                         |                                                                | V <sub>V33I,reset,act</sub>   | 2.6   |                                  |      |      |  |

| Voltage level at V33I pin for leaving hard reset mode                            |                                                                | V <sub>V33I,reset,deact</sub> |       |                                  | 3.0  |      |  |

| First voltage level at VST pin for switching VCC supply on                       |                                                                | V <sub>ST,VCC,on,abs</sub>    |       | 16                               |      | V    |  |

| Second voltage level at VST pin for switching VCC supply on                      |                                                                | $V_{\text{VST,VCC,on,rel}}$   | -     | V <sub>BUSP,mean</sub><br>- 6 V  | -    | V    |  |

| Voltage level for switching KNX IC current from BUSP to VST                      |                                                                | V <sub>VST,V33ana</sub>       | -     | 12                               | -    | V    |  |

| Voltage level for switching VST load current in soft start mode to maximum level |                                                                | $V_{\rm VST,V33dig}$          |       | 15                               |      | V    |  |

| Current at BUSP during soft start                                                |                                                                | I <sub>BUSP,SS</sub>          |       | 9                                | 10   | mA   |  |

| Voltage level at VST pin for switching VCC supply off                            |                                                                | V <sub>VST,VCC,off</sub>      |       | 9                                |      | V    |  |

| Voltage level at VCC pin for RESET deactivation (3.3 V)                          | V <sub>VCC</sub> = 3.3 V                                       | V <sub>RESET,LH,3</sub>       | 2.8   |                                  | 3.05 | V    |  |

| Voltage level at VCC pin for RESET deactivation (5V)                             | V <sub>VCC</sub> = 5 V                                         | V <sub>RESET,LH,5</sub>       | 4.20  |                                  | 4.5  | V    |  |

| <u>Voltage</u> hysteresis at VCC pin for RESET generation                        |                                                                | V                             | 0.095 |                                  |      | V    |  |

| Voltage <u>leve</u> l at VST pin for activation of SAVE pin                      |                                                                | V <sub>VST,</sub> SAVE,HL     | 13    |                                  | 15   | V    |  |

| Absolute V <sub>VST</sub> le <u>vel fo</u> r<br>deactivation of SAVE pin         |                                                                | V <sub>VST,SAVE,LH,abs</sub>  | 14    |                                  | 16   | V    |  |

| Relative V <sub>vsT</sub> lev <u>el for</u><br>deactivation of SAVE pin          |                                                                | V <sub>VST,</sub> SAVE,LH,rel |       | V <sub>BUSP,mean</sub><br>- 6 V  |      | V    |  |

| V <sub>BUSP</sub> level for deactivation of SAVE pin                             |                                                                | $V_{\text{BUSP,SAVE,LH}}$     |       | 18.5                             |      | V    |  |

| Hysteresis of SAVE pin activation / deactivation levels                          |                                                                | $V_{ST,\overline{SAVE},hyst}$ | 1     |                                  |      | V    |  |

| SAVE output voltage at logic-level low                                           | $I_{\overline{SAVE}} = 5 \text{ mA}$<br>$V_{10} = 5 \text{ V}$ | $V_{\overline{SAVE},low,5}$   |       |                                  | 0.7  | V    |  |

| TOVV                                                                             | $I_{\overline{SAVE}} = 2 \text{ mA}$                           | $V_{\overline{SAVE,low,2}}$   |       |                                  | 0.4  | V    |  |

| Pull up current at pin SAVE                                                      | $V_{\overline{SAVE}} = 0 V$ $V_{\overline{IO}} = 5 V$          | I_SAVE,pu                     |       | -500                             |      | μΑ   |  |

| Absolute V <sub>20</sub> supply activation threshold                             |                                                                | V <sub>V20,on,abs</sub>       |       | V <sub>VST,SAVE,LH</sub><br>+1 V |      |      |  |

| Relative V <sub>20</sub> supply activation threshold                             |                                                                | V <sub>V20,on,rel</sub>       |       | V <sub>BUSP,mean</sub>           |      |      |  |

| Absolute V <sub>20</sub> supply deactivation threshold                           |                                                                | V <sub>V20,off,abs</sub>      |       | V <sub>VST,SAVE,HL</sub><br>+1 V |      |      |  |

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25$ °C ... +85°C, unless otherwise noted. Positive currents are flowing into the device pins. Typical values are at  $T_{AMB} = +25$ °C, unless otherwise noted.)

| Description                                                                                     | Condition                                                           | Symbol                                        | Min                    | Тур                             | Max  | Unit            |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|------------------------|---------------------------------|------|-----------------|

| Relative V20 supply deactivation threshold                                                      |                                                                     | V <sub>V20,off,rel</sub>                      |                        | V <sub>BUSP,mean</sub><br>- 6 V |      |                 |

| High threshold at pin WK. 1)                                                                    |                                                                     | $V_{WK,high}$                                 | 2.0                    |                                 | 2.5  | V               |

| Low threshold at pin WK. 1)                                                                     |                                                                     | V <sub>WK,low</sub>                           | 1.1                    |                                 | 1.6  | V               |

| Pull down current at pin<br>WK (active in input mode) 1)                                        | $\begin{vmatrix} V_{WK} = V_{VIO}/2, \\ V_{VIO} = 5V \end{vmatrix}$ | I <sub>WK,pd</sub>                            |                        | 60                              |      | μΑ              |

| High level at pin WK                                                                            | I <sub>wk</sub> = -2mA                                              | V <sub>WK,OUT,high2</sub>                     | V <sub>VIO</sub> -1V   |                                 |      | V               |

| High level at pin WK                                                                            | I <sub>wk</sub> = -0.5mA                                            | V <sub>WK,OUT,high5</sub>                     | V <sub>VIO</sub> -0.5V |                                 |      | V               |

| Low level at pin WK                                                                             | $I_{WK} = 5mA$                                                      | V <sub>WK,OUT,low</sub>                       |                        |                                 | 0.7  | V               |

| E981.03 mode parameters - AC Cha                                                                | racteristics                                                        |                                               |                        |                                 |      |                 |

| Maximum duration of hard reset mode                                                             | $V_{BUSP} > 20 V$<br>$C_{33I} = 100 nF$                             | t <sub>33I,on</sub>                           |                        |                                 | 20   | ms              |

| Wait time between KNX bus communication free and sending Reset indication to the host processor |                                                                     | t <sub>w,ri</sub>                             | 40                     |                                 |      | bit<br>times    |

| Duration of an active driven wake-<br>up pulse to MCU causes by a valid<br>trigger telegram     |                                                                     | t <sub>TRIGGER,pw</sub>                       | 80                     | 100                             | 120  | ms              |

| Debounce time of alarm condition at pin SETVCC                                                  |                                                                     | t <sub>ALARM,deb</sub>                        |                        | 100                             | 120  | ms              |

| Reset Concept - DC Characteristics                                                              |                                                                     |                                               |                        |                                 |      |                 |

| Actively driven low level on pin RESET                                                          | $I_{\overline{RESET}} < 5 \text{ mA}$<br>$V_{VIO} > 3 \text{ V}$    | $V_{\overline{\text{RESET}},\text{low, out}}$ |                        |                                 | 0.4  | V               |

| Pull up current at pin RESET 2)                                                                 | $V_{\text{NIO}} = 0 \text{ V}$ $V_{\text{VIO}} = 5 \text{ V}$       | I <sub>RESET,pu</sub>                         |                        | -500                            |      | μΑ              |

| Low level at pin RESET input path                                                               |                                                                     | $V_{\overline{RESET}, low, in}$               |                        |                                 | 0.2  | V <sub>IO</sub> |

| High level at pin RESET input path                                                              |                                                                     | V                                             | 0.8                    |                                 |      | V <sub>IO</sub> |

| Minimum voltage at pin VIO for interpreting the input path of RESET 3)                          |                                                                     | $V_{IO,min,\overline{RESET}}$                 | 2.0                    |                                 |      | V               |

| Reset Concept - AC Characteristics                                                              |                                                                     |                                               |                        |                                 |      |                 |

| Debounce time of input pin RESET for activation soft reset mode                                 |                                                                     | t <sub>RESET,deb</sub>                        | 10                     |                                 |      | μs              |

| Minimum active time of RESET 4)                                                                 |                                                                     | t <sub>RESET,min</sub>                        | 10                     |                                 | 20   | ms              |

| Power Supply – DC Characteristics                                                               |                                                                     |                                               |                        |                                 |      |                 |

| Voltage drop between BSUP and VST PIN                                                           |                                                                     | V <sub>ST_drop</sub>                          | 2                      | 2.4                             | 3    | V               |

| Maximum DC BUSP current                                                                         | MAX_BUS_CURR<br>(0x20F) = 0xBF                                      | <br> BUSP(max)                                | 11.4                   | 12                              | 12.6 | mA              |

<sup>1)</sup> The WK pin is configurable as input or as output which sent a trigger pulse on received trigger telegram. To configure this change bit EN\_OUT to "0" in Register TRIGGER (0x214). Default configuration is output.

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

<sup>2)</sup> The  $\overline{RESET}$  pin is an open drain input/output with pull current source to  $V_{10}$

<sup>3)</sup> The input at pin  $\overline{RESET}$  is not active in reset and startup modes and in case of low  $V_{10}$

<sup>4)</sup> In case of RESET activation by E981.03.

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25^{\circ}C ... +85^{\circ}C, unless otherwise noted.$  Positive currents are flowing into the device pins. Typical values are at  $T_{AMB} = +25^{\circ}C$ , unless otherwise noted.)

| Description                                                                               | Condition                                                                                             | Symbol                     | Min     | Тур    | Max     | Unit              |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|---------|--------|---------|-------------------|

| Maximum DC BUSP current                                                                   | MAX_BUS_CURR<br>(0x20F) = 0xFF                                                                        | BUSP(max)                  | 17.1    | 18     | 18.9    | mA                |

| Maximum DC BUSP current                                                                   | MAX_BUS_CURR<br>(0x20F) = 0x3F                                                                        | I <sub>BUSP(max)</sub>     | 22.8    | 24     | 25.2    | mA                |

| Maximum DC BUSP current                                                                   | MAX_BUS_CURR<br>(0x20F) = 0x7F                                                                        | <br> BUSP(max)             | 28.5    | 30     | 31.5    | mA                |

| Maximum bus current slope in 0.25 mA/ms mode                                              | CURRENT_SLOPE<br>(0x210) = 0x00                                                                       | slope,<br>lim025_di/<br>dt | 0.17    | 0.2    | 0.23    | mA /<br>ms        |

| Maximum bus current slope in 0.5 mA/ms mode (default)                                     | (0x210) = 0x01                                                                                        | slope,<br>lim05_di/dt      | 0.35 1) | 0.4 1) | 0.45 1) | mA /<br>ms        |

| Maximum bus current slope in 1.25 mA/ms mode                                              | (0x210) = 0x02                                                                                        | slope,<br>lim125_di/<br>dt | 0.87 1) | 1 1)   | 1.13 1) | mA /<br>ms        |

| Maximum bus current slope in 2.5 mA/ms mode                                               | (0x210) = 0x03                                                                                        | slope,<br>lim25_di/dt      | 1.75    | 2      | 2.25    | mA /<br>ms        |

| Output voltage at pin V20                                                                 | V <sub>VST</sub> > 20V,<br>I <sub>V20</sub> = 0 I <sub>V20(max)</sub><br>(positive output<br>current) | V <sub>V20</sub>           | 18.5    | 20     | 21.5    | V                 |

| Voltage drop linear voltage regulator at under-voltage                                    | V <sub>VST</sub> <20V,<br>I <sub>V20</sub> =020mA<br>(positive output<br>current)                     | V <sub>V20,DROP</sub>      |         | 0.5    | 0.8     | V                 |

| Short circuit current                                                                     | (positive output current)                                                                             | I <sub>V20(SC)</sub>       | 25      |        | 50      | mA                |

| Output voltage in 3.3V mode                                                               | I <sub>LOAD,YCC</sub> <= 50 mA<br>(positive output current)<br>SETVCC = GND                           | V <sub>VCC3.3</sub>        | 3.15    | 3.3    | 3.45    | V                 |

| Output voltage in 5V mode                                                                 | I <sub>LOAD,VCC</sub> <= 30 mA (positive output current)<br>SETVCC = VIO                              | V <sub>VCC5</sub>          | 4.75    | 5      | 5.25    | V                 |

| Voltage ripple in 3.3V mode. This ripple is already included in output voltage tolerance. | CVCC = $47\mu$ F<br>ESR = $0.5\Omega$<br>LSPS = $330\mu$ H<br>RLSPS = $3\Omega$<br>SETVCC = GND       | V <sub>VCC,PP3.3</sub>     |         | 70     |         | mV                |

| Voltage ripple in 5V mode. This ripple is already included in output voltage tolerance.   | CVCC = $47\mu$ F<br>ESR = $0.5\Omega$<br>LSPS = $330\mu$ H<br>RLSPS = $3\Omega$<br>SETVCC = VIO       | V <sub>VVC,PP5</sub>       |         | 70     |         | mV                |

| Voltage at pin SETVCC for selection of VCC = 3.3 V and no active alarm condition          |                                                                                                       | V <sub>SETVCC,low</sub>    |         |        | 0.6     | V                 |

| Voltage at pin SETVCC for an active alarm condition                                       |                                                                                                       | V <sub>SETVCC,alarm</sub>  | 0.4     |        | 0.6     | V <sub>V33I</sub> |

<sup>1)</sup> guaranteed by design

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25$ °C ... +85°C, unless otherwise noted. Positive currents are flowing into the device pins. Typical values are at  $T_{AMB} = +25$ °C, unless otherwise noted.)

| Description                                                                    | Condition                                                | Symbol                   | Min                    | Тур     | Max     | Unit              |

|--------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|------------------------|---------|---------|-------------------|

| Voltage at pin SETVCC for selection of VCC = 5 V and no active alarm condition |                                                          | $V_{_{SETVCC},high}$     | 0.8                    |         |         | V <sub>V33I</sub> |

| Pull resistance at pin SETVCC to V33I                                          |                                                          | R <sub>p33,SETVCC</sub>  |                        | 200     |         | kΩ                |

| Pull resistance at pin SETVCC to GND                                           |                                                          | R <sub>p0,SETVCC</sub>   |                        | 200     |         | kΩ                |

| Voltage at pin V33I                                                            |                                                          | V <sub>V33I</sub>        | 3.22                   | 3.3     | 3.38    | V                 |

| Clock System - AC Characteristics                                              |                                                          |                          |                        |         |         |                   |

| Crystal frequency (±50ppm)                                                     | CLK_FAC L/H (0x20A<br>/ 0x20B) = 0xE330<br>(reset value) | $f_{Q}$                  |                        | 7.3728  |         | MHz               |

| Synchronization clock frequency applied at pin XTAL                            | no crystal installed<br>EXTAL is n.c.                    | f <sub>XTAL,sync</sub>   | 126.537                | 126.562 | 126.588 | Hz                |

| Host UART Interface - DC Character                                             | istics                                                   |                          |                        |         |         |                   |

| Input low voltage at pin RXD                                                   |                                                          | V <sub>RXD,low</sub>     |                        |         | 0.2     | V <sub>IO</sub>   |

| Input high voltage at pin RXD                                                  |                                                          | V <sub>RXD,high</sub>    | 0.8                    |         |         | V <sub>IO</sub>   |

| Pull down current at pin RXD                                                   | $V_{RXD} = 5 \text{ V}, V_{IO} = 5 \text{ V}$            | I <sub>RXD,pd</sub>      |                        | 100     |         | μΑ                |

| Low level on TXD pin                                                           | $I_{TXD} = 5 \text{ mA}, V_{IO} = 5$                     | V <sub>TXD,low,5</sub>   |                        |         | 0.7     | V                 |

| Low level on 1XD pin                                                           | $I_{TXD} = 2 \text{ mA}$                                 | V <sub>TXD,low,2</sub>   |                        |         | 0.4     | V                 |

| High level on TXD pin                                                          | $I_{TXD} = -5 \text{ mA}, V_{IO} = 5$                    | V <sub>TXD,high,5</sub>  | V <sub>IO</sub> -0.7 V |         |         |                   |

| Trigit level on 170 pill                                                       | $I_{TXD} = -2 \text{ mA}$                                | V <sub>TXD,high,2</sub>  | V <sub>10</sub> -0.4 V |         |         |                   |

| Low level on pin BS0                                                           |                                                          | V <sub>BS0,low</sub>     |                        |         | 0.2     | V <sub>IO</sub>   |

| High level on pin BS0                                                          |                                                          | V <sub>BS0,high</sub>    | 0.8                    |         |         | V <sub>IO</sub>   |

| Pull down current on pin BS0                                                   | $V_{10} = 5 \text{ V}, V_{BS0} = 5 \text{ V}$            | I <sub>PD,BS0</sub>      |                        | 30      |         | μΑ                |

| Low level on pin BS1                                                           |                                                          | V <sub>BS1,low</sub>     |                        |         | 0.2     | V <sub>IO</sub>   |

| High level on pin BS1                                                          |                                                          | V <sub>BS1,high</sub>    | 0.8                    |         |         | V <sub>IO</sub>   |

| Pull down current on pin BS1                                                   | $V_{10} = 5 \text{ V}, V_{850} = 5 \text{ V}$            | I <sub>PD,BS1</sub>      |                        | 30      |         | μΑ                |

| Host UART Interface - AC Character                                             | istics                                                   |                          |                        |         |         |                   |

| UART receiver timeout between subsequent byte of a service                     |                                                          | t <sub>UART,IBG,RX</sub> | 2.5                    |         |         | ms                |

| Baud rate deviation                                                            |                                                          | $\Delta f_{UART}$        | -3%                    |         | 3%      |                   |

| Host SP Interface - DC Characteristi                                           | cs                                                       |                          |                        |         |         |                   |

| Input high voltage at pin SCS, SCK, MOSI, MISO                                 |                                                          | V <sub>SPI,high</sub>    | 0.8                    |         |         | V <sub>IO</sub>   |

| Input low voltage at pin SCS, SCK, MOSI, MISO                                  |                                                          | V <sub>SPI,low</sub>     |                        |         | 0.2     | V <sub>IO</sub>   |

| Pull down current on pin SCS                                                   | $V_{\overline{SCS}}$ =5 V, $V_{IO}$ =5 V                 | I <sub>PU,SCS</sub>      |                        | -30     |         | μΑ                |

| Pull down current on pin SCK                                                   | V <sub>SCK</sub> =5 V, V <sub>IO</sub> =5 V              | I <sub>PU,SCK</sub>      |                        | -30     |         | μΑ                |

| High output level on MISO, MOSI                                                | $I_{MISO} = -5 \text{mA}, V_{IO} = 5 \text{V}$           | V <sub>MISO,high,5</sub> | V <sub>10</sub> -0.7V  |         |         |                   |

| pin                                                                            | I <sub>MISO</sub> = -2 mA                                | V <sub>MISO,high,2</sub> | V <sub>10</sub> -0.4 V |         |         |                   |

| Low output level on MISO, MOSI                                                 | $I_{MISO} = 5\text{mA}, V_{IO} = 5\text{V}$              | V <sub>MISO,low,5</sub>  |                        |         | 0.7     | V                 |

| pin                                                                            | $I_{MISO} = 2 \text{ mA}$                                | V <sub>MISO,low,2</sub>  |                        |         | 0.4     | V                 |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25^{\circ}C ... +85^{\circ}C, unless otherwise noted.$  Positive currents are flowing into the device pins. Typical values are at  $T_{AMB} = +25^{\circ}C$ , unless otherwise noted.)

| Description                                                                                                                                                                                                                          | Condition                 | Symbol                   | Min    | Тур                           | Max    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------|-------------------------------|--------|------|

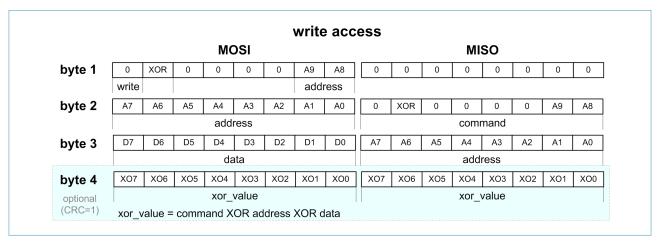

| Host SP Interface - AC Characteristic                                                                                                                                                                                                | CS                        |                          |        |                               |        |      |

| Time between falling SCS edge and first rising SCK edge                                                                                                                                                                              |                           | t <sub>LS1</sub>         | 30     |                               |        | ns   |

| Time between last falling SCK edge and rising SCS edge                                                                                                                                                                               |                           | t <sub>LS2</sub>         | 30     |                               |        | ns   |

| Inter byte gap - time between last<br>falling SCK edge of a byte<br>transmission and first rising SCK<br>edge of subsequent byte within a<br>SPI transfer relevant especially for<br>read accesses between address<br>and data bytes |                           | t <sub>IBG</sub>         | 1      |                               |        | μs   |

| Period of SPI clock                                                                                                                                                                                                                  |                           | t <sub>P_SCK</sub>       | 250    |                               |        | ns   |

| MOSI data setup time (time between MOSI data valid and falling edge of SCK                                                                                                                                                           |                           | t <sub>setup</sub>       | 30     |                               |        | ns   |

| Input low voltage at pin MOSI data<br>hold time (time between falling<br>edge of SCK and MOSI data invali-<br>dation)                                                                                                                |                           | t <sub>hold</sub>        | 20     |                               |        | ns   |

| MISO data valid time (time between rising edge of SCK and MISO data valid)                                                                                                                                                           | C <sub>MISO</sub> < 20 pF | t <sub>valid</sub>       |        |                               | 35     | ns   |

| Time between rising edge of SCS and high impedance at MISO                                                                                                                                                                           |                           | t <sub>MISO_Z</sub>      |        | 100                           |        | ns   |

| Monitoring Functions                                                                                                                                                                                                                 |                           |                          |        |                               |        |      |

| ADC scaling factor for low voltage $V_{\text{BUSP}}$ signal used for measurement $(V_{\text{ADC}} / V_{\text{BUSP}})$                                                                                                                |                           | Scale <sub>VBUSP,</sub>  | 1/16.1 | 1/15                          | 1/13.9 |      |

| ADC scaling factor for low voltage $V_{20}$ signal used for measurement $(V_{ADC}/V_{20})$                                                                                                                                           |                           | Scale <sub>V20,ADC</sub> | 1/8.4  | 1/8                           | 1/7.6  |      |

| ADC scaling factor for low voltage V <sub>cc</sub> signal used for measurement (V <sub>ADC</sub> / V <sub>cc</sub> )                                                                                                                 |                           | Scale <sub>VCC,ADC</sub> | 1/2.14 | 1/2                           | 1/1.86 |      |

| ADC scaling factor for low voltage V <sub>CC</sub> signal used for measurement (V <sub>ADC</sub> / V <sub>ST</sub> )                                                                                                                 |                           | Scale <sub>VST,ADC</sub> | 1/10.7 | 1/10.05                       | 1/9.4  |      |

| ADC scaling factor for low voltage V <sub>IO</sub> signal used for ADC measurement (V <sub>ADC</sub> / V <sub>IO</sub> )                                                                                                             |                           | Scale <sub>VIO,ADC</sub> | 1/2.36 | 1/2.2                         | 1/2.04 |      |

| Averaging time for mean value of $V_{\text{\tiny BUSP}}$                                                                                                                                                                             |                           | t <sub>vbusp(AV)</sub>   |        | 5                             |        | ms   |

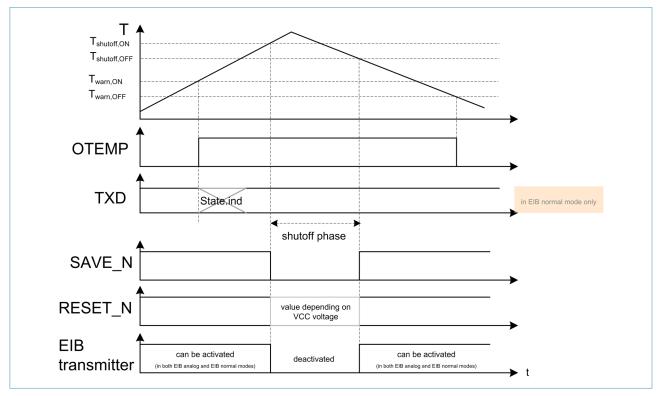

| Temperature limit for activating temperature warning                                                                                                                                                                                 |                           | T <sub>warn,on</sub>     | 110    | 120                           | 140    | °C   |

| Temperature limit for deactivating temperature warning                                                                                                                                                                               |                           | $T_{warn,off}$           |        | T <sub>warn,on</sub><br>-10°C |        | °C   |

| Temperature limit for reducing power consumption                                                                                                                                                                                     |                           | T <sub>shutoff,on</sub>  |        | T <sub>warn,on</sub><br>+30°C |        | °C   |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

$(V_{BUSP} = 19V ... 33V, T_{AMB} = -25^{\circ}C ... +85^{\circ}C, unless otherwise noted. Positive currents are flowing into the device pins. Typical values are at <math>T_{AMB} = +25^{\circ}C$ , unless otherwise noted.)

| Description                                                                                                    | Condition                                                            | Symbol                    | Min                   | Тур                           | Max    | Unit |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------|-----------------------|-------------------------------|--------|------|

| Temperature limit for switching on power consuming functions                                                   |                                                                      | $T_{shutoff,off}$         |                       | T <sub>warn,on</sub><br>+20°C |        | °C   |

| High level at pin OTEMP                                                                                        | $I_{\text{OTEMP}} = -5 \text{ mA},$<br>$V_{\text{VIO}} = 5V$         | V <sub>OTEMP,high,5</sub> | V <sub>10</sub> -0.7V |                               |        |      |

|                                                                                                                | $I_{OTEMP} = -2 \text{ mA}$                                          | V <sub>OTEMP,high,2</sub> | V <sub>10</sub> -0.4V |                               |        |      |

| Low level at pin OTEMP                                                                                         | $I_{\text{OTEMP}} = 5 \text{ mA},$<br>$V_{\text{VIO}} = 5 \text{ V}$ | V <sub>OTEMP,low,5</sub>  |                       |                               | 0.7    | V    |

| · ·                                                                                                            | $I_{OTEMP} = 2 \text{ mA}$                                           | V <sub>OTEMP,low,2</sub>  |                       |                               | 0.4    | V    |

| Temperature step per LSB                                                                                       |                                                                      | $\Delta T_{LSB}$          |                       | 2.5                           |        | K    |

| Aout scaling factor for low voltage VBUSP signal used for measurement (V <sub>AOUT</sub> / V <sub>BUSP</sub> ) |                                                                      | Scale <sub>VBUSP,</sub>   | 1/12.2                | 1/12                          | 1/11.8 |      |

| Aout scaling factor for low voltage VBUSP signal used for measurement (V <sub>AOUT</sub> / V <sub>BUSP</sub> ) |                                                                      | Scale <sub>VBUSP,</sub>   | 1/8.1                 | 1/8                           | 1/7.9  |      |

# **4 Hardware Configuration**

Pins of SPI and UART interfaces,  $\overline{SAVE}$ ,  $\overline{RESET}$ , WK,  $\overline{INT}$  and OTEMP are prepared for galvanic insulation with optical coupler. MISO, TXD,  $\overline{SAVE}$ ,  $\overline{RESET}$ , WK,  $\overline{INT}$  and OTEMP can provide a current of 5 mA for driving a diode of an optical coupler in case of VIO = 5 V.

For lower power consumption set VIO\_SW bit in PS\_CTRL register.

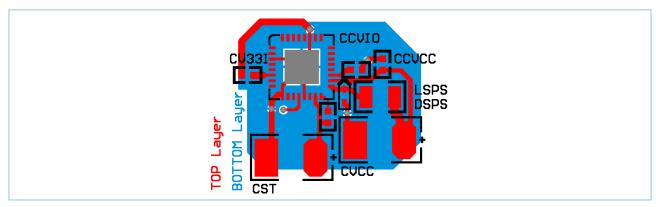

# 4.1 PCB Design Rules

Figure 1. PCB Layout

Remark! The layout example is incomplete! The layout only gives an example about the placement of the DC/DC converter components, the external capacitors and GND routing.

## 4.2 Minimal Function of E981.03

Figure 2. Schematic Example (minimal application)

DC/ DC converter active (3.3 V): OTEMP not used:  $I_{max}$ =50 mA open SETVCC = GND: VCC = 3.3 V WK not used: open BS1 = BS0 = GND: SAVE not used: UART 19.2 k baud open **RESET** not used: V20 not used: V20 = VSTopen UART optional with optical coupler AOUT not used: open

> MOSI = GND MISO = open

SPI not used

$\frac{\mathsf{SCK} = \mathsf{GND}}{\mathsf{SCS}} = \mathsf{VIO}$

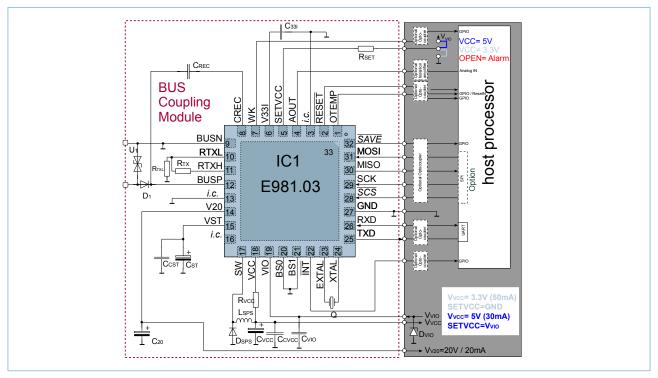

# 4.3 Full Normal Mode Application

Figure 3. Schematic Example (full application)

| DC/DC converter active (3.3 V/5 V): | $I_{max} = 50/30 \text{ mA}$  | OTEMP used |

|-------------------------------------|-------------------------------|------------|

| SETVCC = GND:                       | VCC = 3 V                     | WK used    |

| SETVCC = VIO:                       | VCC = 5 V                     | SAVE used  |

| BS1 = BS0 = GND:                    | UART 19.2 k baud              | RESET used |

| V20 used:                           | additional C <sub>v20</sub> , | AOUT used  |

|                                     | $I_{max} = 20 \text{ mA}$     |            |

| UART optional with optical coupler  |                               |            |

optional with optocoupler optional with optocoupler optional with optocoupler optional with optocoupler optional with insulation amplifier for analog Signal

SPI optional with optical coupler

In Normal Mode alarm functionality is usable. Alarm is detected in case of an open SETVCC pin.

For other schematics read application notes.

Table 1. Recommended Components

| Component           | Recommended value                                                                                                | Remarks                                                              |

|---------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| U1                  | model: SMAJ43CA, SMBJ43CA                                                                                        |                                                                      |

| D1                  | model: BYG21                                                                                                     |                                                                      |

| C <sub>ST</sub>     | 330 μF / 35 V                                                                                                    | ESR < 1 Ω                                                            |

| C <sub>CST</sub>    | ceramic 100 nF / 35 V                                                                                            | ±20%                                                                 |

| C <sub>20</sub>     | 22 μF / 35 V                                                                                                     | ESR < 1 Ohm                                                          |

| L <sub>SPS</sub>    | 330 μH, $R_{LSPS}$ , typ = 3 $\Omega$ , $R_{LSPS,max}$ = 10 $\Omega$ , $I_{sat,SPS}$ = 160 mA, $T_{amb}$ < 85 °C | ±20%                                                                 |

| C <sub>vcc</sub>    | 47 μF / 6 V                                                                                                      | 0.2 Ω < ESR < 0.8 Ω                                                  |

| C <sub>cvcc</sub>   | ceramic 100 nF / 8V                                                                                              | ±20%                                                                 |

| C <sub>CVIO</sub>   | ceramic 100 nF / 8V                                                                                              | ±20%                                                                 |

| D <sub>SPS</sub>    | 40 V, 200 mA, t <sub>rr</sub> < 15 ns                                                                            | e.g. BAT64                                                           |

| C <sub>33I</sub>    | ceramic 100 nF                                                                                                   | ±20%                                                                 |

| $R_{TX}$            | 47 Ω                                                                                                             | ±5 % / 1 W                                                           |

| C <sub>REC</sub>    | Ceramic 56 nF                                                                                                    | ±10 %                                                                |

| Q                   | f = 7.3728 MHz, tolerance 50 ppm                                                                                 | Do not use external capacitors or crystals with internal capacitors. |

| R <sub>SET</sub> 1) | 1 kΩ                                                                                                             |                                                                      |

| R <sub>VCC</sub> 1) | 1 kΩ                                                                                                             |                                                                      |

| D <sub>VIO</sub> 1) | 6.2 V, 500 mW                                                                                                    |                                                                      |

| R <sub>TXL</sub>    | 10 kΩ                                                                                                            | ±1%                                                                  |

<sup>1)</sup> Only necessary in case of the E981.03 being connected to a separate application module. These components only ensuring to meet the absolute maximum rating in case of connecting and disconnecting the application module. If the connector guarantees to connect GND potential first, the ESD protection is not needed.

# **5 Interfaces Description**

### **5.1** KNX/ EIB – Interface

The KNX/ EIB - Interface is a full compatible KNX TP1 transceiver with autonomous Medium Access Control and individual physical Address. The telegram on KNX bus is analyzed and dependent on its contents and

communication mode, the data will be processed. In Analog Mode, the signals SEND and REC are directly bypassed to the host UART interface pins RXD and TXD.

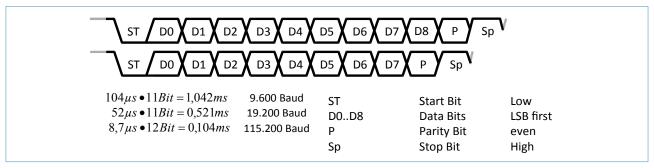

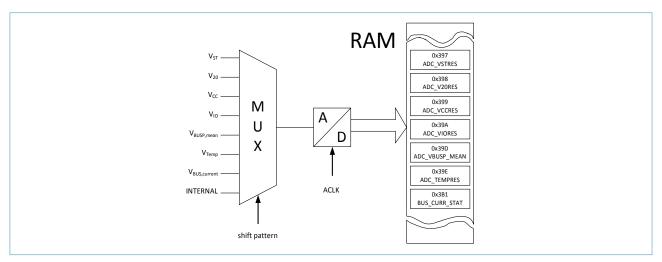

### 5.2 UART - Interface

The E981.03 has a full duplex UART interface to transmit and receive bytes asynchronously. The protocol between E981.03 and host controller is a two-wire protocol with software handshake.

The UART host interface consists of the following three parts

UART physical layer realizes media access and bit decoding / encoding or output driver for KNX bypass in Analog Mode

- UART logical layer provides byte framing capabilities

- UART service layer defines control and data access sequences

To secure UART communication, a CRC calculation for receive and transmit path can be activated separately.

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Table 2. Baud rate configuration

| BS1 | BS0 | Description  | CRC check useable | Remark                         |

|-----|-----|--------------|-------------------|--------------------------------|

| GND | VIO | 9.6 k baud   | No                | 8 bit, even parity, 1 stop-bit |

| GND | GND | 19.2 k baud  | Yes               | 8 bit, even parity, 1 stop-bit |

| VIO | GND | 115.2 k baud | Yes               | 9 bit, even parity, 1 stop-bit |

| VIO | VIO | Analog Mode  | No                |                                |

Figure 4. UART Bit

The bit D8 in 9-bit UART has the following meaning:

0: data byte 1: service byte

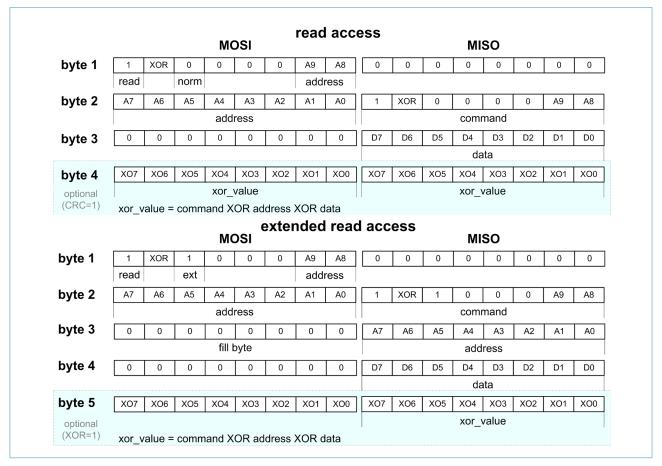

# 5.3 SPI compatible – Interface

E981.03 has a slave SPI compatible - interface to transmit and receive data. The interface can be used alternatively for E981.03 configuration and KNX communication. In analog mode the interface is the only possibility to configure parameters like bus current.

To secure SPI compatible communication, a CRC calculation can also be activated.

The user could switch off the SPI compatible - Interface by setting ON0 and ON1 to zero (Register SPI\_CTRL). In this case 4 GPIOS could be used trough the UART – Interface. The GPIOs have VIO related I/O levels.

The pins MOSI and MISO are useable as general purpose inputs or outputs. The pins SCS and SCK can be used as input pins. For read and write

## 5.4 Telegram Transmission

After successful upload of the frame E981.03 sends the frame on **KNX** bus after the **KNX** specified bus idle time detected.

The repeat flag of the frame transmitted is handled by the E981.03.

- In first transmission the repeat flag is set to 1.

- In repeated frames the repeat bit is cleared to 0.

The acknowledge frame sent by the receivers of the frame is checked and

In case of BUSY acknowledged frames E981.03

waits for at least 150 bit times after the BUSY acknowledge before starting a new transmission attempt. These 150 bit times refer to the end of the BUSY acknowledged frame independent from other communication on the EIB bus. In case of bus com-

- munication between the two (BUSY) repetitions the time between the interposed frame and the BUSY repetition is 50 bit times.

- In case of NACK acknowledged frames E981.03 starts a new transmission attempt.

- No acknowledge and corrupted acknowledge will be handled as NACK.

- BUSY and NACK acknowledge will be handled as BUSY.

If the repeat flag in the uploaded frame is not set, E981.03 will send the frame only once even in case of not ACK acknowledgment.

The maximum number of repetitions is defined in the register MAX\_RST\_CNT and can be modified e.g. by a host UART service or SPI.

$Elmos \ Semiconductor \ AG \ reserves \ the \ right \ to \ change \ the \ detail \ specifications \ as \ may \ be \ required \ to \ permit \ improvements \ in \ the \ design \ of \ its \ products$

### PRODUCTION DATA - JAN 15, 2015

Table 3. KNX frame timing

| Description                                                                                                                                            | Condition                                                                     | Symbol                    | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| Time between end of telegram<br>upload from host processor to<br>E981.03 and start of telegram<br>transmission on EIB bus<br>(in case of idle EIB bus) | bit TXDEL of<br>register<br>UART_CTRL = 0<br>L_Data or<br>L_PollData<br>frame | t <sub>tr,delay,var</sub> |     |     | 104 | μs   |

| Time between end of telegram upload from host processor to E981.03 and start of telegram transmission on EIB bus (in case of idle EIB bus)             | bit TXDEL of<br>register<br>UART_CTRL = 0<br>L_ExtData frame                  |                           |     |     | 250 | μs   |

| Wait time after BUSY acknowledge                                                                                                                       |                                                                               | t <sub>BUSY,rep</sub>     |     | 104 |     | μs   |

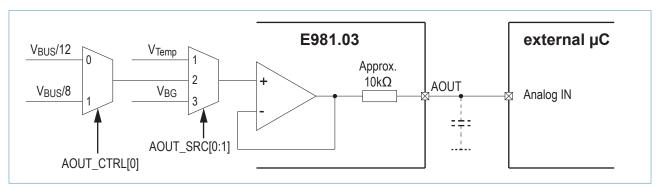

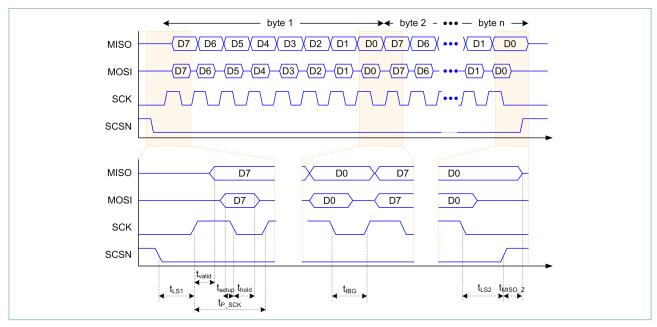

### **5.5 AOUT**

The pin AOUT is used to monitor several voltages. The source can be selected by a register value. The analog monitor signal is not filtered by the E981.03. Especially the scaled analog bus voltage is not the mean value of the bus voltage but follows the BUSP line immediately.

Between AOUT buffer and AOUT pin a series resistor of approximately 10 k is implemented in E981.03. It can be

used to realize a first order RC filter by connecting AOUT to an external capacitor  $C_{\rm ext}$ . Measurement of AOUT voltage needs to take the intern resistor value into account (high impedance measurement input use).

Measurement values are:

- Temperature voltage

- Band gap voltage <sup>1)</sup>

- Bus voltage

| VIO = 3.3 V | VBUS / 12 |

|-------------|-----------|

| VIO = 5 V   | VBUS / 8  |

other multiplexer configuration are invalid

1) The band gap voltage can be used to increase the precision of the ADC.

Figure 5. Analog Monitoring