### **MAX11410**

## 24-Bit Multi-Channel Low-Power 1.9ksps Delta-Sigma ADC with PGA

### **General Description**

The MAX11410 is a low-power, multi-channel, 24-bit delta-sigma ADC with features and specifications that are optimized for precision sensor measurement.

The input section includes a low-noise programmable gain amplifier (PGA) with very high input impedance and available gains from 1x to 128x to optimize the overall dynamic range. Input buffers provide isolation of the signal inputs from the switched-capacitor sampling network when the PGA is not in use, making the ADC easy to drive even with high-impedance sources.

Several integrated features simplify precision sensor applications. The programmable matched current sources provide excitation for resistive sensors. An additional current sink and current source aid in detecting broken sensor wires. The 10-channel input multiplexer provides the flexibility needed for complex, multi-sensor measurements. GPIOs reduce isolation components and ease control of switches or other circuitry.

When used in single-cycle mode, the digital filter settles within a single conversion cycle. The available FIR digital filter allows single-cycle settling in 16ms while providing more than 90dB simultaneous rejection of 50Hz and 60Hz line noise.

The integrated on-chip oscillator requires no external components. If needed, an external clock source may be used instead. Control registers and conversion data are accessed through the SPI-compatible serial interface.

### **Applications**

- Sensor Measurement

- Portable Instruments

- Resistive Bridge Measurement

#### **Benefits and Features**

- High Resolution And Low Noise For Signal Sources With Wide Dynamic Range

- · 24-Bit Resolution

- Programmable Gain Amplifier With 1, 2, 4, 8, 16, 32, 64, and 128 Gain Options

- 90dB Simultaneous 60Hz and 50Hz Power Line Rejection

- · 3ppm Typical INL with No Missing Codes

- Optimized Features For More Efficient System Design

- 10 Analog Inputs May be Used for Single-Ended/ Fully Differential in Any Combination

- Two Dedicated/One Shared Differential Voltage Reference Inputs

- · On-Demand Offset and Gain Self-Calibration

- Low Power for Efficient Systems

- · 2.7V to 3.6V Analog Supply Range

- 1.7V to 3.6V I/O Supply Range

- <1µA Sleep Mode</li>

- Standard SPI-Compatible Control Interface

- Selectable Internal/External Oscillator

- Operating Temperature Range from -40°C to +125°C

- Small 28-Pin 4mm x 4mm TQFN Package: Lead-Free & RoHS Compliant

Ordering Information appears at end of data sheet.

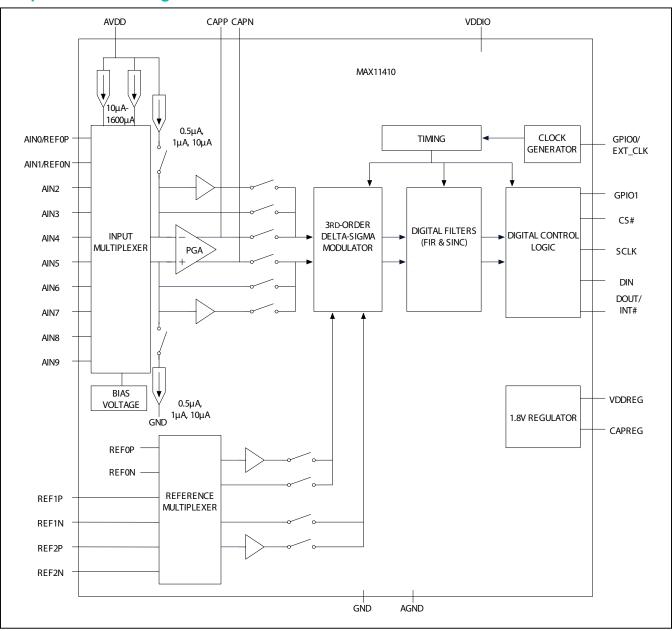

# **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                                          | 1  |

|--------------------------------------------------------------|----|

| Applications                                                 | 1  |

| Benefits and Features                                        | 1  |

| Simplified Block Diagram                                     | 2  |

| Absolute Maximum Ratings                                     | 7  |

| Package Thermal Characteristics                              | 7  |

| Electrical Characteristics                                   | 7  |

| Typical Operating Characteristics                            | 16 |

| Pin Configuration                                            | 19 |

| Pin Description                                              | 19 |

| Detailed Description                                         | 21 |

| Analog Inputs                                                | 21 |

| Signal Path Considerations                                   | 21 |

| Bypass (Direct Signal Path) Mode                             | 21 |

| Buffered Mode                                                | 21 |

| PGA Mode                                                     | 21 |

| Digital Gain                                                 | 22 |

| Noise Performance                                            | 23 |

| Analog Supply Current Comparison for Various Operating Modes | 26 |

| Reference Inputs                                             | 26 |

| Low-Power Considerations                                     | 26 |

| Modulator Duty Cycle Mode                                    | 26 |

| Sleep Mode                                                   | 26 |

| Circuit Settling Time                                        | 27 |

| Input Multiplexer                                            | 27 |

| PGA                                                          | 27 |

| Reference Multiplexer                                        | 27 |

| Excitation Current Source                                    | 27 |

| V <sub>BIAS</sub> Source                                     | 27 |

| Sensor Excitation Current Sources                            | 27 |

| Burnout Currents                                             | 28 |

| Calibration                                                  | 28 |

| Self-Calibration                                             | 28 |

| PGA Self-Calibration                                         | 29 |

| System Offset and Gain Calibration                           | 29 |

| Sensitivity of Calibration Coefficients                      |    |

| Example of Self-Calibration                                  | 29 |

# TABLE OF CONTENTS (CONTINUED)

| Example of PGA Gain Calibration            | 30 |

|--------------------------------------------|----|

| Example of System Offset Calibration       |    |

| GPIOs                                      |    |

| Low-Side Power Switch                      |    |

| Example of System Gain Calibration         |    |

| Conversion Data Formats                    |    |

| Digital Filter                             |    |

| Sequencer                                  |    |

| Sequencer Notes                            | 34 |

| Sequencer Example                          | 34 |

| SPI Interface                              |    |

| DOUT/INTB                                  |    |

| SPI Transactions                           |    |

| Register Address Byte                      |    |

| Register Map                               | 39 |

| 8-Bit Control RegistersPD (0x00)           |    |

| CONV_START (0x01)                          | 40 |

| SEQ_START (0x02)                           | 41 |

| CAL_START (0x03)                           | 41 |

| GP0_CTRL (0x04)                            | 42 |

| GP1_CTRL (0x05)                            |    |

| GP_CONV (0x06)                             |    |

| GP_SEQ_ADDR (0x07)                         |    |

| FILTER (0x08)                              |    |

| CTRL (0x09)                                |    |

| SOURCE (0x0A)                              |    |

| MUX_CTRL0 (0x0B)                           |    |

| MUX_CTRL1 (0x0C)                           |    |

| MUX_CTRL2 (0x0D)                           |    |

| PGA (0x0E)                                 |    |

| WAIT_EXT (0x0F)                            |    |

| WAIT_START (0x10)                          |    |

| 24-Bit Control, Data, and Status Registers |    |

| PART_ID (0x11)                             |    |

| SYSC_SEL (0x12)                            |    |

| SYS_OFF_A (0x13)                           |    |

| SYS_OFF_B (0x14)                           | 61 |

## **TABLE OF CONTENTS (CONTINUED)**

| SYS_GAIN_A (0x15)      |

|------------------------|

| SYS_GAIN_B (0x16)      |

| SELF_OFF (0x17)        |

| SELF_GAIN_1 (0x18)65   |

| SELF_GAIN_2 (0x19)     |

| SELF_GAIN_4 (0x1A)     |

| SELF_GAIN_8 (0x1B)     |

| SELF_GAIN_16 (0x1C)    |

| SELF_GAIN_32 (0x1D)    |

| SELF_GAIN_64 (0x1E)    |

| SELF_GAIN_128 (0x1F)69 |

| LTHRESH0 (0x20)        |

| LTHRESH1 (0x21)        |

| LTHRESH2 (0x22)        |

| LTHRESH3 (0x23)        |

| LTHRESH4 (0x24)        |

| LTHRESH5 (0x25)        |

| LTHRESH6 (0x26)        |

| LTHRESH7 (0x27)        |

| UTHRESH0 (0x28)        |

| UTHRESH1 (0x29)74      |

| UTHRESH2 (0x2A)        |

| UTHRESH3 (0x2B)        |

| UTHRESH4 (0x2C)        |

| UTHRESH5 (0x2D)        |

| UTHRESH6 (0x2E)        |

| UTHRESH7 (0x2F)        |

| DATA0 (0x30)           |

| DATA1 (0x31)           |

| DATA2 (0x32)           |

| DATA3 (0x33)79         |

| DATA4 (0x34)           |

| DATA5 (0x35)80         |

| DATA6 (0x36)80         |

| DATA7 (0x37)81         |

| Status (0x38)          |

| Status IF (0x39) 85    |

| TABLE OF CONTENTS (CONTINUED)                                                                                                                                                                                                                                                                                    |              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 16-bit Sequencer Registers                                                                                                                                                                                                                                                                                       | 86           |

| μC (0x3A, 0x3B, 0x3C, 0x3D, 0x3E, 0x3F, 0x40, 0x41, 0x42, 0x43, 0x44, 0x45, 0x46, 0x47, 0x48, 0x49, 0x4B, 0x4C, 0x4D, 0x4E, 0x4F, 0x50, 0x51, 0x52, 0x53, 0x54, 0x55, 0x56, 0x57, 0x58, 0x59, 0x5A, 0x05C, 0x5D, 0x5E, 0x5F, 0x60, 0x61, 0x62, 0x63, 0x64, 0x65, 0x66, 0x67, 0x68, 0x69, 0x6A, 0x6B, 0x6D, 0x6E) | x5B,<br>x6C, |

| μCADDR (0x6F)                                                                                                                                                                                                                                                                                                    |              |

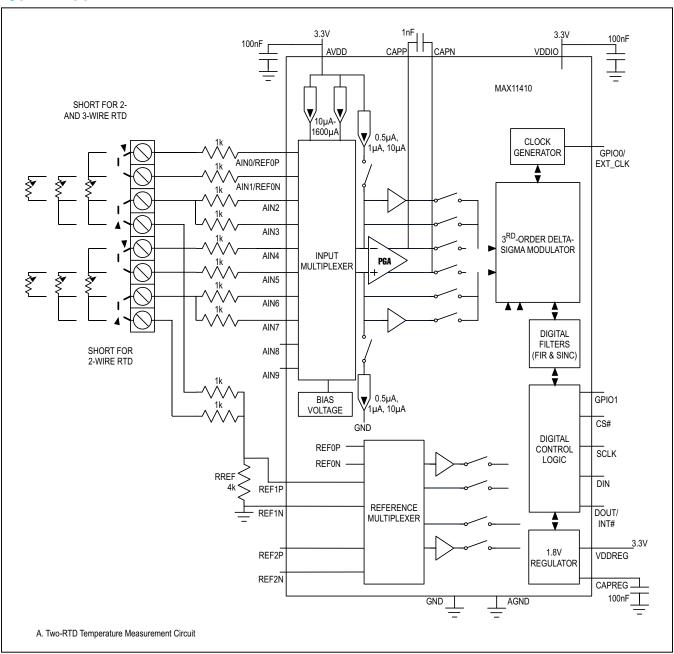

| Typical Application Circuits                                                                                                                                                                                                                                                                                     |              |

| Two-RTD Temperature Measurement Circuit (2, 3, and 4-Wire)                                                                                                                                                                                                                                                       |              |

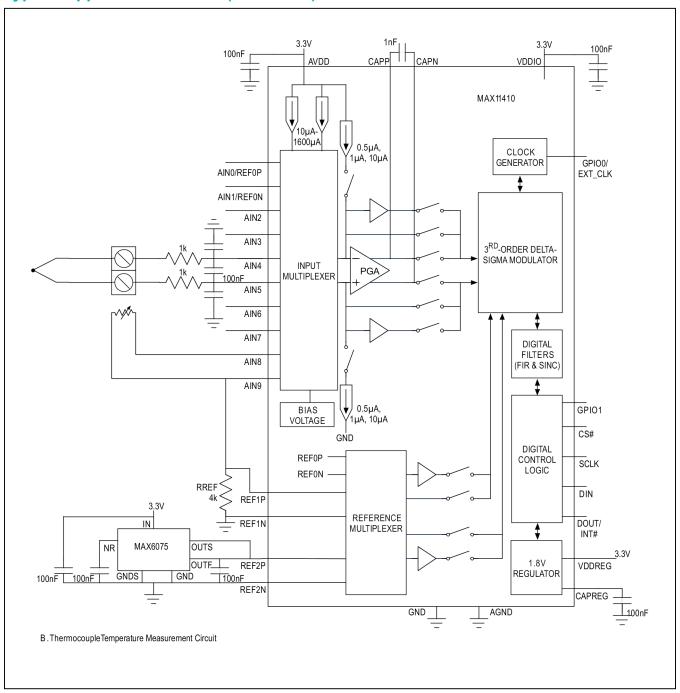

| Thermocouple Measurement Circuit.                                                                                                                                                                                                                                                                                |              |

| Ordering Information                                                                                                                                                                                                                                                                                             |              |

| Chip Information                                                                                                                                                                                                                                                                                                 |              |

| Package Information                                                                                                                                                                                                                                                                                              |              |

| Revision History                                                                                                                                                                                                                                                                                                 |              |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                   |              |

| Table 1. Input-Referred Noise(μVrms) with V <sub>REF</sub> = 2.5V, AV <sub>DD</sub> = 3.3V, and inputs shorted                                                                                                                                                                                                   | 23           |

| Table 2. Effective resolution with V <sub>REF</sub> = 2.5V, AV <sub>DD</sub> = 3.3V, and inputs shorted                                                                                                                                                                                                          | 24           |

| Table 3. Noise-Free Resolution with V <sub>REF</sub> = 2.5V, AV <sub>DD</sub> = 3.3V, and inputs shorted                                                                                                                                                                                                         | 25           |

| Table 4. Analog Supply Current Comparison for Various Operating Modes (typical values shown)                                                                                                                                                                                                                     | 26           |

| Table 5. Gain Calibration Codes                                                                                                                                                                                                                                                                                  |              |

| Table 6. Offset Calibration Codes                                                                                                                                                                                                                                                                                |              |

| Table 7a. Example of Self-Calibration                                                                                                                                                                                                                                                                            |              |

| Table 7b. Example of PGA Gain Calibration                                                                                                                                                                                                                                                                        |              |

| Table 7c. Example of System Offset Calibration                                                                                                                                                                                                                                                                   |              |

| Table 7d. Example of System Gain Calibration                                                                                                                                                                                                                                                                     |              |

| Table 8. Conversion Data Formats                                                                                                                                                                                                                                                                                 |              |

| Table 9a. LINEF = 00 Data Rate and Filter Rejection Settings                                                                                                                                                                                                                                                     |              |

| Table 9b. LINEF = 01 Data Rate and Filter Rejection Settings                                                                                                                                                                                                                                                     |              |

| Table 9c. LINEF = 10 Data Rate and Filter Rejection Settings                                                                                                                                                                                                                                                     |              |

| Table 9d. LINEF = 11 Data Rate and Filter Rejection Settings                                                                                                                                                                                                                                                     |              |

| Table 10. Populated Sequence Register Example                                                                                                                                                                                                                                                                    | 35           |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                  |              |

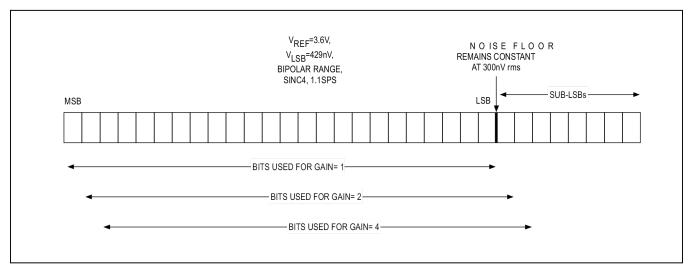

| Figure 1. Digital Programmable Gain Example                                                                                                                                                                                                                                                                      | 23           |

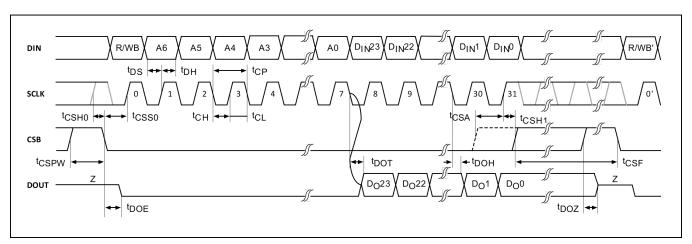

| Figure 2, SDI Timing Diogram                                                                                                                                                                                                                                                                                     | 20           |

### **Absolute Maximum Ratings**

| $AV_{DD}$ to GND (GND = AGND = DGND)0.3V to +3.6V        |

|----------------------------------------------------------|

| V <sub>DDIO</sub> to GND (GND = AGND = DGND)0.3V to 3.6V |

| AV <sub>DD</sub> to V <sub>DDIO</sub> 0.3V to 1.8V       |

| Analog Inputs (AIN, REF) to AGND                         |

| (GND = AGND = DGND)0.3V to AV <sub>DD</sub> + 0.3V       |

| CAPP, CAPN, V <sub>DDREG</sub> , CAPREG to GND           |

| (GND = AGND = DGND)0.3V to AV <sub>DD</sub> + 0.3V       |

| Digital Inputs and Outputs to GND                        |

| (GND = AGND = DGND)                                      |

| GPIO Inputs to GND (GND = AGND = DGND)                   |

| 0.3V to AV <sub>DD</sub> + 0.3V                          |

|                                                          |

| Maximum Current Into Any Pin                              | 50mA      |

|-----------------------------------------------------------|-----------|

| ESD Rating—II Pins                                        | 2kV       |

| Continuous Power Dissipation                              |           |

| (Single-Layer Board, T <sub>A</sub> = +70°C, derate 20.8) | 1667mW    |

| Continuous Power Dissipation                              |           |

| (Multilayer Board, T <sub>A</sub> = +70°C,                |           |

| derate 28.6mW/°C above +70°C)                             | 2286mW    |

| Operating Temperature Range40°C                           | to +125°C |

| Junction Temperature                                      |           |

| Storage Temperature Range40°C                             | to +150°C |

| Lead Temperature (soldering, 10 sec)                      | +300°C    |

| Soldering Temperature (reflow)                            | +260°C    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

#### Thermal Resistance, Single-Layer Board (TQFN) Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......48°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......3°C/W

#### Thermal Resistance, Four-Layer Board (TQFN)

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......35°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(AV_{DD}$  = +3.3V,  $V_{DDIO}$  = +1.8V,  $V_{REFP}$  -  $V_{REFN}$  =  $AV_{DD}$ ,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS               | MIN                                                           | TYP                         | MAX                                                           | UNITS |

|------------------------------|-----------------|--------------------------|---------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|-------|

| ANALOG INPUTS                |                 |                          |                                                               |                             |                                                               |       |

| Full-Scale Input Voltage     |                 |                          |                                                               | ±V <sub>REF</sub> /<br>Gain |                                                               |       |

| Absolute Input Voltage       |                 | Buffers disabled         | A <sub>GND</sub> -<br>30mV                                    |                             | AV <sub>DD</sub> +<br>30mV                                    | V     |

| Innut Voltage Dange          |                 | Unipolar                 | 0                                                             |                             | $V_{REF}$                                                     | V     |

| Input Voltage Range          |                 | Bipolar                  | -V <sub>REF</sub>                                             |                             | $V_{REF}$                                                     |       |

|                              |                 | AIN buffers/PGA disabled | A <sub>GND</sub>                                              |                             | $AV_{DD}$                                                     |       |

|                              |                 | Buffers enabled          | A <sub>GND</sub><br>+ 0.1                                     |                             | AV <sub>DD</sub><br>- 0.1                                     |       |

| Common Mode Voltage<br>Range | V <sub>СМ</sub> | PGA gain = 1 to 16       | A <sub>GND</sub><br>+ 0.1 +<br>(V <sub>IN</sub> )<br>(Gain)/2 |                             | AV <sub>DD</sub><br>- 0.1 -<br>(V <sub>IN</sub> )<br>(Gain)/2 | V     |

|                              |                 | PGA gain = 32 to 128     | A <sub>GND</sub> +<br>0.2 +<br>(V <sub>IN</sub> )<br>(Gain)/2 |                             | AV <sub>DD</sub> -<br>0.2<br>- (V <sub>IN</sub> )<br>(Gain)/2 |       |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                  | SYMBOL         | CONDITIONS                                      | MIN | TYP                                                             | MAX | UNITS |

|----------------------------|----------------|-------------------------------------------------|-----|-----------------------------------------------------------------|-----|-------|

|                            |                | Buffer disabled                                 |     | ±1                                                              |     | μA/V  |

| Differential Input Current |                | Buffer enabled                                  | -13 |                                                                 | +13 | 0     |

|                            |                | PGA enabled, Note 2                             | -1  |                                                                 | +1  | nA    |

|                            |                | Buffer disabled                                 |     | ±1                                                              |     | μA/V  |

| Abaaluta lagut Cumant      |                | Buffer enabled                                  | -65 |                                                                 | +65 |       |

| Absolute Input Current     |                | PGA enabled, -40°C to +85°C, Note 2             | -1  |                                                                 | +1  | nA    |

|                            |                | PGA enabled, -40°C to +125°C, Note 2            | -5  |                                                                 | +5  | 1     |

| Input Capacitance          |                | Bypass mode                                     |     | 10                                                              |     | pF    |

| Input Sampling Rate        | f <sub>s</sub> |                                                 |     | 246                                                             |     | kHz   |

| SYSTEM PERFORMANCI         | E              |                                                 |     |                                                                 |     | 1     |

| Resolution                 |                |                                                 |     | 24                                                              |     | bits  |

| Data Rate                  |                | 50/60Hz FIR filter,<br>single-cycle conversions |     | 1, 2, 4,<br>8, 16                                               |     |       |

|                            |                | 50Hz FIR filter,<br>single-cycle conversions    |     | 1.3, 2.5,<br>5, 10,<br>20, 35.6                                 |     |       |

|                            |                | 60Hz FIR filter,<br>single-cycle conversions    |     | 1.3, 2.5.<br>5, 10,<br>20, 36.5                                 |     |       |

|                            |                | SINC4 filter, single-cycle conversions          |     | 1, 2.5,<br>5, 10,<br>15, 30,<br>60, 120,<br>240,<br>480         |     |       |

|                            |                | SINC4 filter, continuous conversions            |     | 4, 10,<br>20, 40,<br>60, 120,<br>240,<br>480,<br>960,<br>1920   |     | sps   |

|                            |                | SINC4 filter, duty cycle conversions            |     | 0.25,<br>0.63,<br>1.25,<br>2.5, 5,<br>10, 15,<br>30, 60,<br>120 |     |       |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                                 | SYMBOL         | CONDITIONS                                                                                                                             | MIN    | TYP                                 | MAX    | UNITS             |

|-------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|--------|-------------------|

| Data Rate Tolerance                       |                | Determined by internal clock accuracy                                                                                                  | -6     |                                     | 6      | %                 |

|                                           |                | Differential input, reference buffer enabled, PGA = 1, tested @ 16sps, Note 4                                                          | -12    | +3                                  | +12    | ppm<br>FSR        |

| Integral Nonlinearity                     | INL            | Differential input, PGA = 2 - 16, Note 4                                                                                               |        | 6                                   |        |                   |

|                                           |                | Differential input, PGA = 32 - 64, Note 4                                                                                              |        | 11                                  |        | ppmFS             |

|                                           |                | Differential input, PGA = 128, Note 4                                                                                                  |        | 15                                  |        |                   |

| Offset Error                              |                | Referred to modulator input. After self and system calibration; V <sub>REFP</sub> - V <sub>REFN</sub> = 2.5V. Tested at 16sps. Note 5. | -25    | ±0.5                                | +25    | μV                |

| Offset Error Drift                        |                |                                                                                                                                        |        | 50                                  |        | nV/°C             |

| PGA Gain Settings                         |                |                                                                                                                                        |        | 1, 2,<br>4, 8,<br>16, 32,<br>64,128 |        |                   |

| Digital Gain Settings                     |                |                                                                                                                                        |        | 2, 4                                |        |                   |

| PGA Gain Error                            |                | No calibration, Note 3                                                                                                                 |        | ±0.1                                |        | %                 |

| F GA Gaill Elloi                          |                | Gain = 1, after calibration, Note 3                                                                                                    | -0.002 |                                     | +0.002 | 70                |

| PGA Gain Drift                            |                |                                                                                                                                        |        | 20                                  |        | ppm<br>μS/°C      |

| Input Noise                               | V <sub>n</sub> | FIR50/60Hz, 16.8sps, PGA = 128.<br>See Tables 1 and 4 for other conditions.                                                            |        | 188                                 |        | nV <sub>RMS</sub> |

| Noise-Free Resolution                     | NFR            | FIR50/60Hz, 16.8sps, PGA = 1.<br>See Table 3 for other conditions.                                                                     |        | 17.2                                |        | Bits              |

|                                           |                | 50Hz/60Hz FIR filter, 50Hz ±1%,<br>16sps conversion, Note 2                                                                            | 81.8   |                                     |        |                   |

| Normal Mode Rejection<br>(Internal Clock) |                | 50Hz/60Hz FIR filter, 60Hz ±1%,<br>16sps single-cycle conversion, Note 2                                                               | 94.4   |                                     |        |                   |

|                                           |                | 50Hz FIR filter, 50Hz ±1%,<br>35.6sps single-cycle conversion, Note 2                                                                  | 39.2   |                                     |        |                   |

|                                           | NMR            | 60Hz FIR filter, 60Hz ±1%,<br>35.6sps single-cycle conversion, Note 2                                                                  | 42.3   |                                     |        | dB                |

|                                           |                | SINC4 filter, 50Hz ±1%,<br>10sps single-cycle conversion, Note 2                                                                       | 55.1   |                                     |        |                   |

|                                           |                | SINC4 filter 60Hz ±1%,<br>10sps single-cycle conversion, Note 2                                                                        | 90.4   |                                     |        |                   |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                                 | SYMBOL                                                | CONDITIONS                                                             | MIN                       | TYP      | MAX                       | UNITS |

|-------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------|---------------------------|----------|---------------------------|-------|

|                                           |                                                       | 50 Hz/60Hz FIR filter, 50Hz or 60Hz ±1%, 16sps single-cycle conversion |                           | 96       |                           |       |

| Normal Mode Rejection<br>(External Clock) |                                                       | 50Hz FIR filter, 50Hz ±1%, 35.6sps single-cycle conversion             |                           | 45       |                           |       |

|                                           | NMR                                                   | 60Hz FIR filter, 60Hz ±1%, 35.6sps single-cycle conversion             |                           | 49       |                           | dB    |

|                                           | SINC4 filter, 50Hz ±1%, 10sps single-cycle conversion |                                                                        | 80                        |          |                           |       |

|                                           |                                                       | SINC4 filter, 60Hz ±1%, 10 SPS single-cycle conversion                 |                           | 95       |                           |       |

| Common-Mode                               | CMR                                                   | DC rejection, any PGA gain                                             | 90                        |          |                           | dB    |

| Rejection                                 | CMR60                                                 | 50/60Hz rejection, PGA enabled                                         | 100                       |          |                           |       |

| Power Supply Rejection                    | PSRRA                                                 |                                                                        | 70                        | 80       |                           | dB    |

| REFERENCE INPUTS                          |                                                       |                                                                        |                           |          |                           |       |

| Reference Voltage                         |                                                       | Reference buffer(s) disabled                                           | A <sub>GND</sub><br>- 30m |          | AV <sub>DD</sub><br>+ 30m | V     |

| Range                                     |                                                       | Reference buffer(s) enabled                                            | A <sub>GND</sub><br>+ 0.1 |          | AV <sub>DD</sub><br>- 0.1 |       |

| Reference Voltage Input                   |                                                       | V <sub>REF</sub> = V <sub>REFP</sub> - V <sub>REFN</sub>               | 0.75                      | 2.5      | AV <sub>DD</sub>          | V     |

| Defended to the control                   |                                                       | Reference buffer disabled                                              |                           | 2.1      |                           | μΑ/V  |

| Reference Input Current                   |                                                       | Reference buffer enabled                                               | -200                      | 61       | +200                      | nA    |

| Reference Input<br>Capacitance            |                                                       | Reference buffers disabled                                             |                           | 15       |                           | pF    |

| BURNOUT CURRENT SO                        | OURCES                                                |                                                                        |                           |          |                           |       |

| Current                                   |                                                       |                                                                        |                           | 0.5,1,10 |                           | μA    |

| Initial Tolerance                         |                                                       |                                                                        |                           | ±10      |                           | %     |

| Drift                                     |                                                       |                                                                        |                           | 0.1      |                           | %/°C  |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                                     | SYMBOL                     | CONDITIONS                                                                          | MIN | TYP                                                                                                                  | MAX                       | UNITS  |

|-----------------------------------------------|----------------------------|-------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|---------------------------|--------|

| MATCHED CURRENT SO                            | OURCES                     |                                                                                     |     |                                                                                                                      |                           |        |

| Matched Current Source<br>Outputs             |                            |                                                                                     |     | 10, 50,<br>75, 100,<br>125,<br>150,<br>175,<br>200,<br>225,<br>250,<br>300,<br>400,<br>600,<br>800,<br>1200,<br>1600 |                           | μА     |

| Current Source Output                         |                            | IDAC ≤ 250μA                                                                        | 0   |                                                                                                                      | AV <sub>DD</sub><br>- 0.7 | V      |

| Voltage Compliance                            | ge Compliance IDAC = 1.6mA | 0                                                                                   |     | AV <sub>DD</sub><br>- 1.2                                                                                            | V                         |        |

| Initial Tolerance                             |                            | T <sub>A</sub> = 25°C, Note 2                                                       | -5  | ±1                                                                                                                   | +5                        | %      |

| Temperature Drift                             |                            | Each IDAC                                                                           |     | 50                                                                                                                   |                           | ppm/°C |

| Current Matching                              |                            | Between IDACs                                                                       |     | ±0.1                                                                                                                 |                           | %      |

| Temperature Drift<br>Matching                 |                            | Between IDACs                                                                       |     | 10                                                                                                                   |                           | ppm/C  |

| Current Source Output<br>Noise                | I <sub>N</sub>             | Output current = 250µA. SINC4 filter, 60sps continuous. Noise is referred to input. |     | 0.47                                                                                                                 |                           | pA rms |

| V <sub>BIAS</sub> OUTPUTS                     |                            |                                                                                     |     |                                                                                                                      |                           |        |

| V <sub>BIAS</sub> Voltage                     |                            |                                                                                     |     | AV <sub>DD</sub> /2                                                                                                  |                           | V      |

| V <sub>BIAS</sub> Voltage Output<br>Impedance |                            |                                                                                     |     | 125K (active), 20K (passive), 125K (passive)                                                                         |                           | Ω      |

## **Electrical Characteristics (continued)**

$(AV_{DD} = +3.3V, V_{DDIO} = +1.8V, V_{REFP} - V_{REFN} = AV_{DD}, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A = +25^{\circ}C$  for typical specifications, unless otherwise noted, Note 1)

| PARAMETER                                                | SYMBOL | CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNITS   |

|----------------------------------------------------------|--------|-----------------------------------------------------------------------------------|------|------|------|---------|

| LDO                                                      |        |                                                                                   |      |      |      |         |

| LDO Output<br>Capacitance                                |        |                                                                                   | 100  |      |      | nF      |

| LDO Output Voltage                                       |        |                                                                                   | 1.62 | 1.8  | 1.98 | V       |

| System Timing                                            |        |                                                                                   |      |      |      |         |

| Power-On Wake-Up<br>Time                                 |        | From AV <sub>DD</sub> > V <sub>POR</sub>                                          |      | 240  |      | μs      |

| Sleep Wake-Up Time                                       |        |                                                                                   |      | 1.25 |      | ms      |

|                                                          |        | C <sub>FILTER</sub> = 0                                                           |      | 0.25 |      |         |

| PGA Power-Up Time                                        |        | C <sub>FILTER</sub> = 20nF                                                        |      | 2    |      | ms      |

|                                                          |        | C <sub>FILTER</sub> = 100nF                                                       |      | 10   |      |         |

|                                                          |        | After changing gain settings to Gain = 1.  C <sub>FILTER</sub> = 0.               |      | 0.25 |      |         |

| PGA Settling Time                                        |        | After changing gain settings to Gain = 1.  C <sub>FILTER</sub> = 100nF.           |      | 10   |      | ms<br>- |

|                                                          |        | After changing gain settings to Gain = 128.  C <sub>FILTER</sub> = 0.             |      | 2    |      |         |

| Input Multiplexer<br>Power-Up Time                       |        | Settled to 21 bits with 10pF load                                                 |      | 2    |      | μs      |

| Input Multiplexer<br>Channel-to-Channel<br>Settling Time |        | Settled to 21 bits with 2K external source resistor                               |      | 2    |      | μs      |

|                                                          |        | Active generator; settled within 1% of final value; $C_{LOAD} = 1\mu F$           |      | 10   |      |         |

| V <sub>BIAS</sub> Power-Up Time                          |        | 125K passive generator; settled within 1% of final value; C <sub>LOAD</sub> = 1µF |      | 575  |      | ms      |

|                                                          |        | 20K passive generator; settled within 1% of final value; C <sub>LOAD</sub> = 1μF  |      | 90   |      |         |

|                                                          | l l    | Active generator; settled within 1% of final value; $C_{LOAD} = 1\mu F$           |      | 10   |      | ms      |

| V <sub>BIAS</sub> Settling Time                          |        | 125K passive generator; settled within 1% of final value; C <sub>LOAD</sub> = 1µF |      | 605  |      |         |

|                                                          |        | 20K passive generator; settled within 1% of final value; C <sub>LOAD</sub> = 1μF  |      | 100  |      |         |

| Matched Current Source<br>Startup Time                   |        |                                                                                   |      | 110  |      | μs      |

| Matched Current Source<br>Settling Time                  |        |                                                                                   |      | 12.5 |      | μs      |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                              | SYMBOL            | CONDITIONS                                                                                                                                                            | MIN | TYP | MAX | UNITS |

|----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| POWER SPECIFICATION                    | S                 |                                                                                                                                                                       | •   |     |     |       |

| Analog Supply                          | AV <sub>DD</sub>  |                                                                                                                                                                       | 2.7 |     | 3.6 | V     |

| Interface Supply                       | V <sub>DDIO</sub> |                                                                                                                                                                       | 1.7 |     | 3.6 | V     |

|                                        |                   | Sleep mode                                                                                                                                                            |     | 0.5 | 3   |       |

|                                        |                   | Standby mode                                                                                                                                                          |     | 115 | 150 |       |

|                                        |                   | Bypass mode, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 60sps.                                       |     | 390 | 550 |       |

| AV <sub>DD</sub> Currents              |                   | Buffered mode, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 60sps.                                     |     | 425 | 600 | μΑ    |

| 7W DD Gallenie                         |                   | PGA enabled, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 60SPS. $T_A = -40$ °C to $105$ °C            |     |     | 700 | μ/ (  |

|                                        |                   | PGA enabled, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 60sps. $T_A = -40^{\circ}\text{C}$ to 125°C. |     | 520 | 750 |       |

| V <sub>DDIO</sub> Operating<br>Current |                   | All modes of operation                                                                                                                                                |     | 0.3 | 2   | μА    |

| V <sub>DDREG</sub> Current             |                   |                                                                                                                                                                       |     | 48  |     | μA    |

|                                        |                   | Bypass mode, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 15sps.                                       |     | 280 | 380 |       |

| AVDD Duty Cycle<br>Power Mode          |                   | Buffered mode, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 15sps.                                     |     | 300 | 400 | μΑ    |

|                                        |                   | PGA enabled, IDAC, $V_{BIAS}$ sources off, $AV_{DD} = V_{REF} = V_{IN} = 3.6V$ , SINC4 filter, continuous conversions at 15sps.                                       |     | 400 | 580 |       |

| SPI TIMING SPECIFICATI                 | IONS              |                                                                                                                                                                       |     |     |     |       |

| SCLK Frequency                         | f <sub>SCLK</sub> |                                                                                                                                                                       | 0   |     | 8   | MHz   |

| SCLK Period                            | tsclk             |                                                                                                                                                                       | 125 |     |     | ns    |

| SCLK Pulse-Width High                  | t <sub>CH</sub>   |                                                                                                                                                                       | 50  |     |     | ns    |

| SCLK Pulse-Width Low                   | t <sub>CL</sub>   |                                                                                                                                                                       | 50  |     |     | ns    |

## **Electrical Characteristics (continued)**

(AV<sub>DD</sub> = +3.3V, V<sub>DDIO</sub> = +1.8V, V<sub>REFP</sub> - V<sub>REFN</sub> = AV<sub>DD</sub>,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A$ =+25°C for typical specifications, unless otherwise noted, Note 1 )

| PARAMETER                           | SYMBOL            | CONDITIONS                                                  | MIN                        | TYP | MAX                        | UNITS |

|-------------------------------------|-------------------|-------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| CSB Fall to SCLK Fall<br>Setup Time | t <sub>CSS0</sub> | CSB falling edge to the 1st SCLK falling edge               | 40                         |     |                            | ns    |

| CSB Rise to SCLK Fall<br>Hold Time  | t <sub>CSH1</sub> | Applies to the last active SCLK falling edge                | 3                          |     |                            | ns    |

| CSB Rise to SCLK Fall               | <sup>t</sup> CSA  | Applies to last active SCLK falling edge, aborted sequence  | 12                         |     |                            | ns    |

| CSB Pulse-Width High                | t <sub>CSPW</sub> |                                                             | 40                         |     |                            | ns    |

| SCLK Fall to CS Fall                | t <sub>CSF</sub>  | Applies to the last active SCLK falling edge                | 100                        |     |                            | ns    |

| DIN to SCLK Rise Setup<br>Time      | t <sub>DS</sub>   |                                                             | 40                         |     |                            | ns    |

| DIN to SCLK Rise Hold<br>Time       | t <sub>DH</sub>   |                                                             | 2                          |     |                            | ns    |

| DOUT Propagation<br>Delay           | t <sub>DOT</sub>  | Delay from the falling clock edge to the transition on DOUT |                            |     | 40                         | ns    |

| DOUT Enable Time                    | t <sub>DOE</sub>  |                                                             | 0                          |     | 40                         | ns    |

| DOUT Disable Time                   | t <sub>DOZ</sub>  |                                                             |                            |     | 25                         | ns    |

| Bus Capacitance                     | C <sub>B</sub>    |                                                             |                            |     | 20                         | pF    |

| LOGIC INPUTS AND OUT                | TPUTS (NON-GP     | PIO)                                                        |                            |     |                            |       |

| Input Current                       |                   | Leakage current                                             |                            |     | ±1                         | uA    |

| Input Low Voltage                   | V <sub>IL</sub>   |                                                             |                            |     | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input High Voltage                  | $V_{IH}$          |                                                             | 0.7 x<br>V <sub>DDIO</sub> |     |                            | V     |

| Input Hysteresis                    | V <sub>HYS</sub>  |                                                             |                            | 200 |                            | mV    |

| Input Capacitance                   |                   |                                                             |                            | 5   |                            | pF    |

| Output Low Level                    | V <sub>OL</sub>   | I <sub>OL</sub> = 1mA, V <sub>DDIO</sub> = 1.8V and 3.6V    |                            |     | 0.1 x<br>V <sub>DDIO</sub> | V     |

| Output High Level                   | V <sub>OH</sub>   | $I_{OL}$ = 1mA, $V_{DDIO}$ = 1.8V and 3.6V                  | 0.9 x<br>V <sub>DDIO</sub> |     |                            | V     |

| High-Z Leakage Current              |                   | Note 2                                                      | -100                       |     | +100                       | nA    |

| High-Z Output<br>Capacitance        |                   |                                                             |                            | 9   |                            | pF    |

### **Electrical Characteristics (continued)**

$(AV_{DD} = +3.3V, V_{DDIO} = +1.8V, V_{REFP} - V_{REFN} = AV_{DD}, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.,  $T_A = +25$ °C for typical specifications, unless otherwise noted, Note 1)

| PARAMETER                           | SYMBOL           | CONDITIONS                                              | MIN                        | TYP    | MAX                        | UNITS |

|-------------------------------------|------------------|---------------------------------------------------------|----------------------------|--------|----------------------------|-------|

| GENERAL PURPOSE IN                  | PUT AND OUTP     | UT (GPIO)                                               |                            |        |                            |       |

| Input Current                       |                  | Leakage current                                         |                            |        | ±1                         | μA    |

| Input Low Voltage                   | V <sub>IL</sub>  |                                                         |                            |        | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input High Voltage                  | V <sub>IH</sub>  |                                                         | 0.7 x<br>V <sub>DDIO</sub> |        |                            | V     |

| Input Hysteresis                    | V <sub>HYS</sub> |                                                         |                            | 200    |                            | mV    |

| Output Low Level                    | V <sub>OL</sub>  | I <sub>OL</sub> = 1mA, A <sub>VDD</sub> = 2.7V and 3.6V |                            |        | 0.1 x<br>AV <sub>DD</sub>  | V     |

| Output High Level                   | V <sub>OH</sub>  | I <sub>OL</sub> = 1mA, AV <sub>DD</sub> = 2.7V and 3.6V | 0.9 x<br>AV <sub>DD</sub>  |        |                            | V     |

| Low-Side Power Switch<br>Current    |                  | GPIO output voltage = 1V                                | 25                         |        |                            | mA    |

| Low-Side Power Switch Impedance     |                  | GPIO output voltage = 1V                                |                            |        | 35                         | Ω     |

| Internal Clock Output Frequency     |                  |                                                         | 2.3347                     | 2.4576 | 2.5805                     | MHz   |

| Internal Clock Output<br>Duty Cycle |                  |                                                         | 40                         |        | 60                         | %     |

| External Clock Input Frequency      |                  |                                                         |                            | 2.4576 |                            | MHz   |

| External Clock Input<br>Duty Cycle  |                  |                                                         | 30                         |        | 70                         | %     |

- Note 1: Limits are 100% production tested at  $T_A$  = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

- Note 2: These specifications are not fully tested and are guaranteed by design and/or characterization.

- Note 3: Gain error does not include zero-scale errors. It is calculated as (full-scale error offset error). After calibration, gain error is on the order of the noise.

- Note 4: ppmFS is parts per million of full scale.

- Note 5: After calibration, the offset voltage is on the order of the noise.

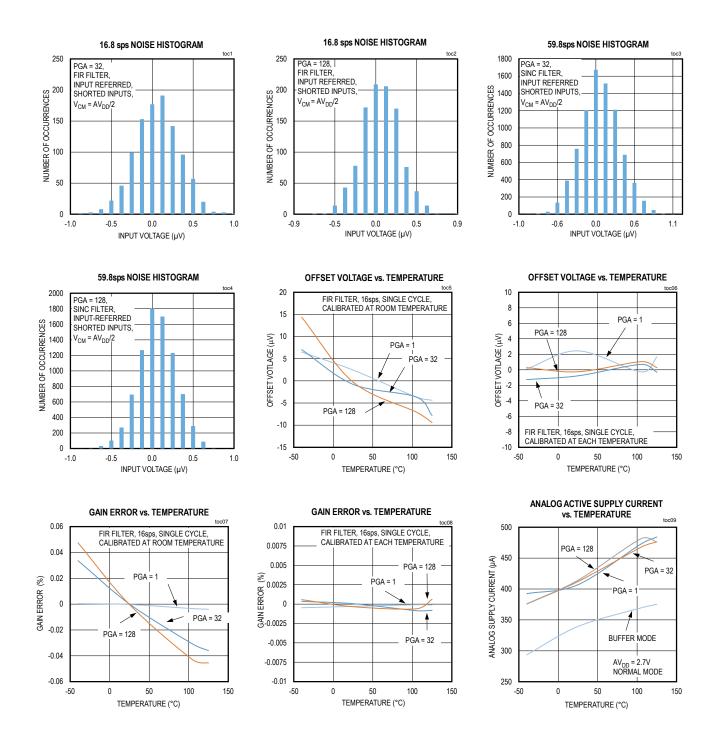

### **Typical Operating Characteristics**

$(V_{AVDD} = 3.3V, V_{REF} = 2.5V, Internal clock, T_A = 25$ °C unless otherwise noted.)

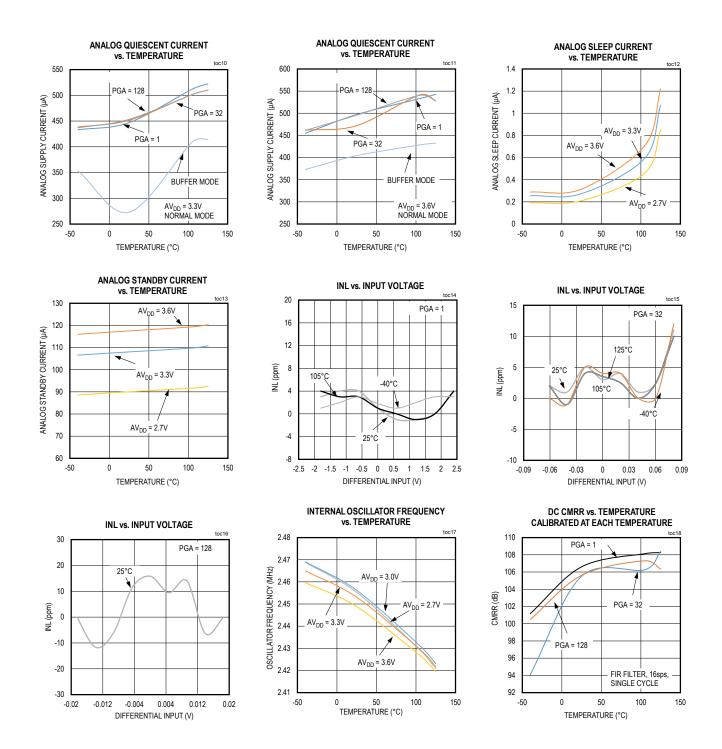

# Typical Operating Characteristics (continued) (V<sub>AVDD</sub> = 3.3V, V<sub>REF</sub> = 2.5V, Internal clock, T<sub>A</sub> = 25°C unless otherwise noted.)

Maxim Integrated | 17 www.maximintegrated.com

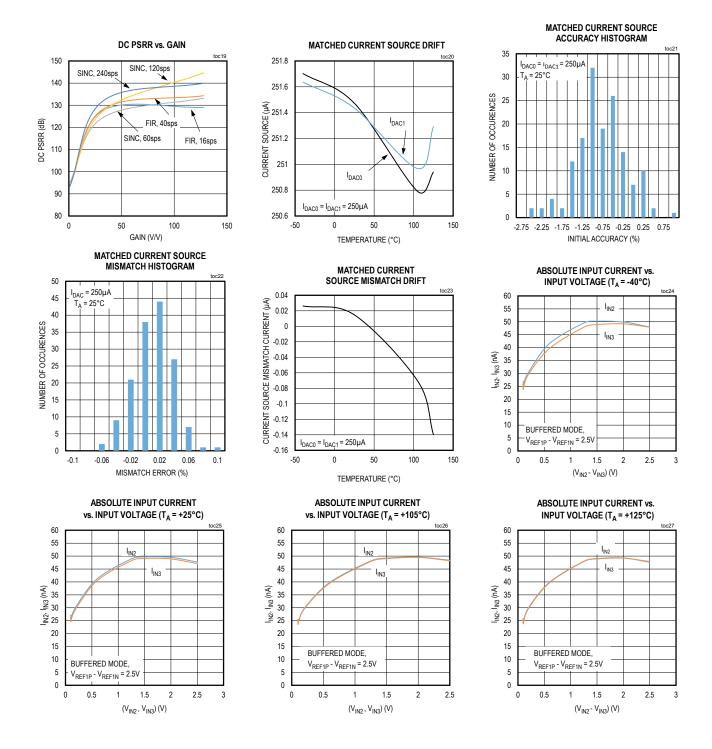

# Typical Operating Characteristics (continued) (V<sub>AVDD</sub> = 3.3V, V<sub>REF</sub> = 2.5V, Internal clock, T<sub>A</sub> = 25°C unless otherwise noted.)

Maxim Integrated | 18 www.maximintegrated.com

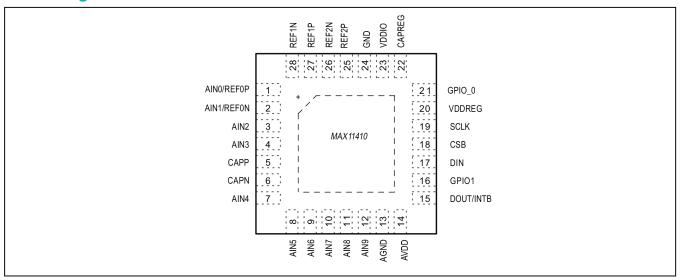

# **Pin Configuration**

# **Pin Description**

| PIN      | NAME       | FUNCTION                                                                                                                                                                                                                                                                        | DEE CUDDLY       | TVDE         |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|

| MAX11410 | NAME       | FUNCTION                                                                                                                                                                                                                                                                        | REF SUPPLY       | TYPE         |

| 1        | AIN0/REF0P | Channel 0 Analog Input/Positive Differential Reference 0 Input. When used as an analog input, may serve as either the positive or negative differential input. May also serve as current source output. When used as a reference input, REF0P must be more positive than REF0N. | AV <sub>DD</sub> | Analog Input |

| 2        | AIN1/REF0N | Channel 1 Input/Negative Differential Reference 0 Input. When used as an analog input, may serve as either the positive or negative differential input. May also serve as current source output. When used as a reference input, REF0P must be more positive than REF0N.        | AV <sub>DD</sub> | Analog Input |

| 3        | AIN2       | Channel 2 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                      | AV <sub>DD</sub> | Analog Input |

| 4        | AIN3       | Channel 3 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                      | AV <sub>DD</sub> | Analog Input |

| 5        | CAPP       | PGA Output. Connect 1nF capacitor across CAPP and CAPN.                                                                                                                                                                                                                         | AV <sub>DD</sub> | Output       |

| 6        | CAPN       | PGA output. Connect 1nF capacitor across CAPP and CAPN                                                                                                                                                                                                                          | AV <sub>DD</sub> | Output       |

| 7        | AIN4       | Channel 4 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                      | AV <sub>DD</sub> | Analog Input |

| 8        | AIN5       | Channel 5 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                      | AV <sub>DD</sub> | Analog Input |

| 9        | AIN6       | Channel 6 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                      | AV <sub>DD</sub> | Analog Input |

# **Pin Description (continued)**

| PIN MAX11410 | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                   | REF SUPPLY        | TYPE           |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|

| 10           | AIN7      | Channel 7 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                                                                                                                                 | AV <sub>DD</sub>  | Analog Input   |

| 11           | AIN8      | Channel 8 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                                                                                                                                 | AV <sub>DD</sub>  | Analog Input   |

| 12           | AIN9      | Channel 9 Input. May serve as either the positive or negative differential input. May also serve as current source output.                                                                                                                                                                                                                                                                 | AV <sub>DD</sub>  | Analog Input   |

| 13           | AGND      | Analog Ground Voltage for AV <sub>DD</sub> Supply. Connect AGND and GND together.                                                                                                                                                                                                                                                                                                          | N/A               | Ground         |

| 14           | AVDD      | Analog Supply Voltage, +2.7V to +3.6V with respect to AGND.                                                                                                                                                                                                                                                                                                                                | AV <sub>DD</sub>  | Power          |

| 15           | DOUT/INTB | This pin serves a dual function. Serial Data Output: the device will drive this pin in response to a serial clock at SCLK, when data is read from the internal registers. In addition to the serial data output function, the DOUT/INTB pin also indicates an enabled interrupt condition has occurred when the pin is asserted low. To view the interrupt state on DOUT/INTB, enable CSB. | V <sub>DDIO</sub> | Digital Output |

| 16           | GPIO1     | Register-Controlled, General-Purpose Input/Output.                                                                                                                                                                                                                                                                                                                                         | AV <sub>DD</sub>  | Digital I/O    |

| 17           | DIN       | Serial Data Input. Data present at DIN is shifted in to the part's internal registers in response to a serial clock at SCLK, either when the part is accessed for an internal register write or for a command operation.                                                                                                                                                                   | V <sub>DDIO</sub> | Digital Input  |

| 18           | CSB       | Chip Select Bar. Active-Low Logic Input. Use CSB to select the IC for access through the serial interface. CSB is used for frame synchronization for communications when SCLK is continuous. CSB transitioning from low to high is used to reset the SPI interface.                                                                                                                        | V <sub>DDIO</sub> | Digital Input  |

| 19           | SCLK      | Serial Clock. Logic Input. Apply an external serial clock to this input to issue commands to or access data.                                                                                                                                                                                                                                                                               | V <sub>DDIO</sub> | Digital Input  |

| 20           | VDDREG    | Digital Regulator Supply, Connect to AVDD.                                                                                                                                                                                                                                                                                                                                                 | AV <sub>DD</sub>  | Power          |

| 21           | GPIO0     | Register Controlled General Purpose Input/Output and External Clock Signal Input. When external clock mode is selected (EXTCLK = 1), provide a 2.4576MHz clock signal at CLK. Other frequencies can be used, but the data rate and digital filter notch frequencies scale accordingly.                                                                                                     | AV <sub>DD</sub>  | Digital I/O    |

| 22           | CAPREG    | Digital Regulator Output. Connect a 100nF capacitor from CAPREG to AGND.                                                                                                                                                                                                                                                                                                                   | AV <sub>DD</sub>  | Power          |

| 23           | VDDIO     | Digital Interface Supply (+1.8V to +3.6V).                                                                                                                                                                                                                                                                                                                                                 | V <sub>DDIO</sub> | Power          |

| 24           | GND       | Ground Reference for V <sub>DDIO</sub> . Connect to AGND.                                                                                                                                                                                                                                                                                                                                  | N/A               | Ground         |

| 25           | REF2P     | Positive Differential Reference 2 Input. REF2P must be more positive than REF2N.                                                                                                                                                                                                                                                                                                           | AV <sub>DD</sub>  | Analog Input   |

| 26           | REF2N     | Negative Differential Reference 2 Input. REF2P must be more positive than REF2N.                                                                                                                                                                                                                                                                                                           | AV <sub>DD</sub>  | Analog Input   |