# Ambient Light Sensor with I<sup>2</sup>C Interface and Dark Current Compensation

#### Description

The NOA1305 ambient light sensor (ALS) is designed for handheld applications and integrates a 16-bit ADC, a 2-wire I<sup>2</sup>C digital interface, internal clock oscillator and a power down mode. The built in dynamic dark current compensation and precision calibration capability coupled with excellent IR and 50/60 Hz flicker rejection enables highly accurate measurements from very low light levels to full sunlight. The device can support simple count equals lux readings in interrupt-driven or polling modes. The NOA1305 employs proprietary CMOS image sensing technology from ON Semiconductor to provide large signal to noise ratio (SNR) and wide dynamic range (DR) over the entire operating temperature range. The optical filter used with this chip provides a light response similar to that of the human eye.

### Features

- Senses Ambient Light and Provides an Output Count Proportional to the Ambient Light Intensity

- Photopic Spectral Response

- Dynamic Dark Current Compensation

- IR Rejection Eliminates Need for Additional IR Photodiode

- Less than 120 µA Active Power Consumption in Normal Operation

- Less than 2 µA Power Dissipation in Power Down Mode

- Interrupt Signal Notifies Host of Significant Intensity Changes

- Wide Operating Voltage Range (2.4 V to 3.6 V)

- Wide Operating Temperature Range (-40°C to 85°C)

- Linear Response Over the Full Operating Range

- Senses Intensity of Ambient Light from 0.165 Lux to Over 100K Lux

- 8 Selectable Integration Times Ranging from 6.25 ms to 800 ms

- No External Components Required

- Built-in 16-bit ADC

- I<sup>2</sup>C Serial Communication Port Supports Standard and Fast Modes

- Metal Mask Programmable I<sup>2</sup>C Slave Address Option Available

- These Devices are Pb-Free and are RoHS Compliant

#### Applications

- Saves Display Power In Applications Such As:

- Cell Phones, PDAs, MP3 Players, GPS

- Cameras, Video Recorders

- · Mobile Devices with Displays or Backlit Keypads

# **ON Semiconductor®**

http://onsemi.com

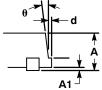

CU SUFFIX CASE 505AD

#### **ORDERING INFORMATION**

| Device            | Package             | Shipping <sup>†</sup> |  |  |  |  |  |

|-------------------|---------------------|-----------------------|--|--|--|--|--|

| NOA1305CUTAG      | CUDFN6<br>(Pb-Free) | 2500 / Tape &<br>Reel |  |  |  |  |  |

| Temperature Range |                     |                       |  |  |  |  |  |

| −40°C to 85°C     |                     |                       |  |  |  |  |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

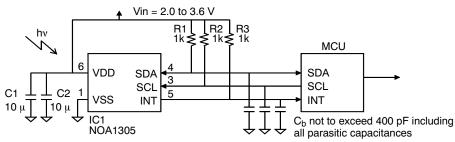

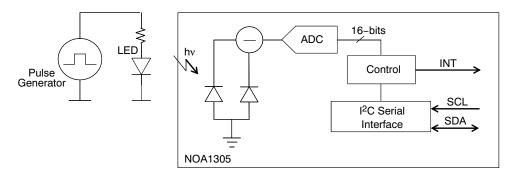

Figure 1. Typical Application Circuit

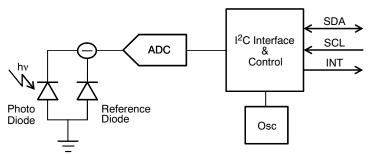

Figure 2. Simplified Block Diagram

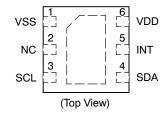

#### **Table 1. PIN FUNCTION DESCRIPTION**

| Pin | Pin Name | Description                                                                                                                                  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VSS      | Ground pin.                                                                                                                                  |

| 2   | NC       | No connection.                                                                                                                               |

| 3   | SCL      | External I <sup>2</sup> C clock supplied by the I <sup>2</sup> C master. Requires a 1 k $\Omega$ pull–up resistor.                           |

| 4   | SDA      | Bi–directional data signal for communications between this device and the I <sup>2</sup> C master. Requires a 1 k $\Omega$ pull–up resistor. |

| 5   | INT      | Interrupt request to the host. Programmable active state, open-drain output and requires an external 1 $k\Omega$ pull-up resistor.           |

| 6   | VDD      | Power pin.                                                                                                                                   |

#### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                        | Symbol              | Value                                | Unit |

|-----------------------------------------------|---------------------|--------------------------------------|------|

| Input power supply                            | VDD                 | 4.0                                  | V    |

| Input voltage range                           | V <sub>in</sub>     | -0.3 to VDD + 0.2                    | V    |

| Output voltage range                          | V <sub>out</sub>    | -0.3 to VDD + 0.2                    | V    |

| Maximum Junction Temperature                  | T <sub>J(max)</sub> | 85                                   | °C   |

| Storage Temperature                           | T <sub>STG</sub>    | -40 to 85                            | °C   |

| ESD Capability, Human Body Model (Note 1)     | ESD <sub>HBM</sub>  | 2                                    | kV   |

| ESD Capability, Charged Device Model (Note 1) | ESD <sub>CDM</sub>  | 750 (corner pins), 500 (center pins) | V    |

| ESD Capability, Machine Model (Note 1)        | ESD <sub>MM</sub>   | 200                                  | V    |

| Moisture Sensitivity Level                    | MSL                 | 5                                    | -    |

| Lead Temperature Soldering (Note 2)           | T <sub>SLD</sub>    | 260                                  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per EIA/JESD22-A114

ESD Charged Device Model tested per ESD-STM5.3.1-1999

ESD Machine Model tested per EIA/JESD22-A115

Latchup Current Maximum Rating: < 100 mA per JEDEC standard: JESD78

2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### **Table 3. OPERATING RANGES**

|                                                                                                              |                    | Standard Mode |           | Fast Mode            |           |      |

|--------------------------------------------------------------------------------------------------------------|--------------------|---------------|-----------|----------------------|-----------|------|

| Rating                                                                                                       | Symbol             | Min           | Max       | Min                  | Max       | Unit |

| Power supply voltage                                                                                         | VDD                | 2.4           | 3.6       | 2.4                  | 3.6       | V    |

| Power supply current                                                                                         | I <sub>DD</sub>    |               | 120       |                      | 120       | μΑ   |

| Quiescent supply current (Note 3)                                                                            | I <sub>DD_qe</sub> |               | 2.0       |                      | 2.0       | μΑ   |

| Low level input voltage (VDD related input levels)                                                           | V <sub>IL</sub>    | -0.5          | 0.3 VDD   | -0.5                 | 0.3 VDD   | V    |

| High level input voltage (VDD related input levels) (Note 4)                                                 | VIH                | 0.7 VDD       | VDD + 0.5 | 0.7 VDD              | VDD + 0.5 | V    |

| Hysteresis of Schmitt trigger inputs (VDD > 2 V)                                                             |                    | N/A           | N/A       | 0.05 VDD             | -         | V    |

| Low level output voltage (open drain) at 3 mA sink current (VDD > 2 V)                                       | V <sub>OL</sub>    | 0             | 0.4       | 0                    | 0.4       | V    |

| Output low current (V <sub>OI</sub> =0.4 V)                                                                  | I <sub>OL</sub>    | 3             | N/A       | 3                    | N/A       | mA   |

| Output low current (V <sub>OI</sub> =0.6 V)                                                                  |                    | N/A           | N/A       | 6                    | N/A       | mA   |

| Output fall time from $V_{IHmin}$ to $V_{ILmax}$ with a bus capacitance, $C_b$ from 10 pF to 400 pF (Note 4) | t <sub>of</sub>    | -             | 250       | 20+0.1C <sub>b</sub> | 250       | ns   |

| Pulse width of spikes which must be suppressed by the input filter                                           | t <sub>SP</sub>    | N/A           | N/A       | 0                    | 50        | ns   |

| Input current of IO pin with an input voltage between 0.1<br>VDD and 0.9 VDD                                 | I                  | -10           | 10        | -10                  | 10        | μΑ   |

| Capacitance on IO pin                                                                                        | CI                 | _             | 10        | -                    | 10        | pF   |

| Operating free-air temperature range                                                                         |                    | -40           | 85        | -40                  | 85        | °C   |

3. Current dissipation when a software Power Down command is sent to the device.

4. Cb = capacitance of one bus line, maximum value of which including all parasitic capacitances should be less than 400 pF.

#### **Table 4. ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified, these specifications apply over VDD = 3.3 V,  $-40^{\circ}C < T_A < 85^{\circ}C$ ) (Note 5)

|                                                                                       |                       | Standard Mode |      | Fast M                 | Fast Mode |      |

|---------------------------------------------------------------------------------------|-----------------------|---------------|------|------------------------|-----------|------|

| Parameter                                                                             | Symbol                | Min           | Max  | Min                    | Max       | Unit |

| SCL clock frequency                                                                   | f <sub>SCL</sub>      | 0             | 100  | 0                      | 400       | kHz  |

| Hold time for START condition. After this period, the first clock pulse is generated. | <sup>t</sup> hd;sta   | 4.0           | -    | 0.6                    | _         | μS   |

| Low period of SCL clock                                                               | t <sub>LOW</sub>      | 4.7           |      | 1.3                    |           | μS   |

| High period of SCL clock                                                              | t <sub>HIGH</sub>     | 4.0           |      | 0.6                    |           | μS   |

| Set-up time for a repeated START condition                                            | t <sub>SU;STA</sub>   | 4.7           | -    | 0.6                    | _         | μS   |

| Data hold time for I <sup>2</sup> C-bus devices                                       | t <sub>HD;DAT_d</sub> | 0             | 3.45 | 0                      | 0.9       | μS   |

| Data set-up time                                                                      | t <sub>SU;DAT</sub>   | 250           | -    | 100                    | _         | nS   |

| Rise time of both SDA and SCL (Note 6)                                                | t <sub>r</sub>        | -             | 1000 | 20 + 0.1C <sub>b</sub> | 300       | nS   |

| Fall time of both SDA and SCL (Note 6)                                                | t <sub>f</sub>        | -             | 300  | 20 + 0.1C <sub>b</sub> | 300       | nS   |

| Set-up time for STOP condition                                                        | t <sub>SU;STO</sub>   | 4.0           | -    | 0.6                    | _         | μS   |

| Bus free time between STOP and START condition                                        |                       | 4.7           | _    | 1.3                    | _         | μS   |

| Capacitive load for each bus line                                                     | Cb                    | -             | 400  | -                      | 400       | pF   |

| Noise margin at the low level for each connected device (including hysteresis)        | V <sub>nL</sub>       | 0.1 VDD       | -    | 0.1 VDD                | _         | V    |

| Noise margin at the high level for each connected device (including hysteresis)       | V <sub>nH</sub>       | 0.2 VDD       | -    | 0.2 VDD                | _         | V    |

| Parameter                                                                             | Symbol                | Тур           |      | Ту                     | Тур       |      |

| Internal Oscillator Frequency                                                         | f <sub>osc</sub>      | 1             |      | 1                      |           | MHz  |

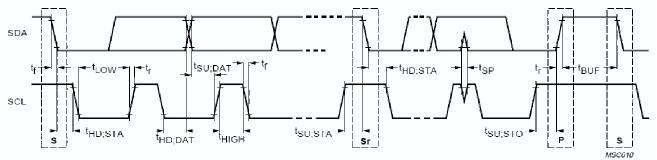

5. Refer to Figure 3 for more information on AC characteristics 6. The rise time and fall time are measured with a pull–up resistor  $R_p = 1 k\Omega$  and  $C_b$  of 400 pF (including all parasitic capacitances).

Table 5. OPTICAL CHARACTERISTICS(Unless otherwise specified, these specifications are for VDD = 3.3 V,  $T_A = 25^{\circ}C$ ,  $T_{INT} = 200 \text{ ms}$ )

| Parameter                | Test Conditions                                   | Symbol              | Min | Тур  | Max | Unit   |

|--------------------------|---------------------------------------------------|---------------------|-----|------|-----|--------|

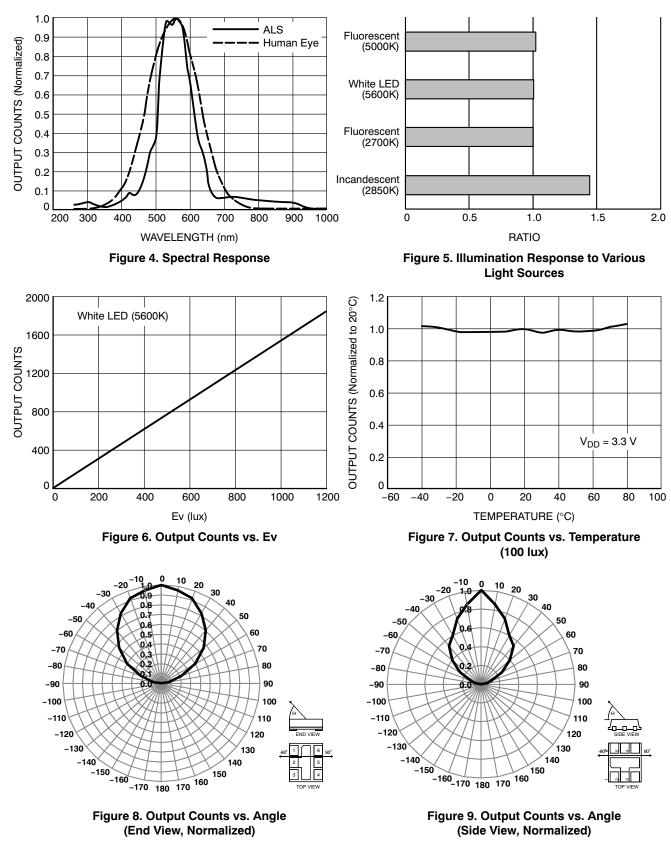

| Irradiance responsivity  | λp (see Figure 5)                                 | R <sub>e</sub>      |     | 545  |     | nM     |

| Illuminance responsivity | White LED Source:<br>Ev = 100 lux (see Figure 6)  | R <sub>vi100</sub>  |     | 154  |     | Counts |

|                          | White LED source:<br>Ev = 1000 lux (see Figure 6) | R <sub>vi1000</sub> |     | 1543 |     |        |

| Dark responsivity        | Ev = 0 lux (see Figure 6)                         | I <sub>DARK</sub>   |     | 0    |     | Counts |

Figure 3. AC Characteristics

#### **DESCRIPTION OF OPERATION**

#### **Ambient Light Sensor Architecture**

The NOA1305 employs a sensitive photo diode fabricated in ON Semiconductor's standard CMOS process technology. The major components of this sensor are as shown in Figure 2. The photons which are to be detected pass through an ON Semiconductor proprietary color filter limiting extraneous photons and thus performing as a band pass filter on the incident wave front. The filter only transmits photons in the visible spectrum which are primarily detected by the human eye. The photo response of this sensor is as shown in Figure 5.

The ambient light signal detected by the photo diode is converted to digital signal using a variable slope integrating ADC with a resolution of 16–bits, unsigned. The ADC value is provided to the control block connected to the  $I^2C$  interface block.

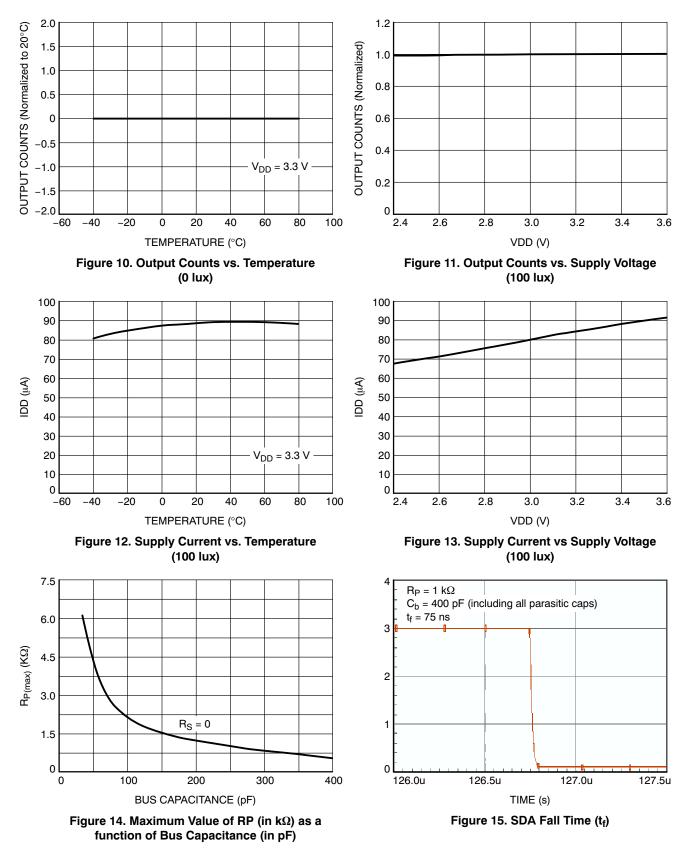

Equation 1 shows the relationship of output counts  $C_{nt}$  as a function of integration constant  $I_k$ , integration time  $T_{int}$  (in seconds) and the intensity of the ambient light,  $I_L$ (in lux), at room temperature (25°C).

$$I_{L} = C_{nt} / (I_{k} \times T_{int})$$

(eq. 1)

Where:

$I_k \approx 7.7$  (for White LED Source)

For example let:

$C_{nt} = 1000$

$T_{int} = 200 \text{ mS}$

Intensity of ambient light, I<sub>L</sub>(in lux):

$$I_{L} = 1000/(7.7 \times 200 \text{ mS})$$

(eq. 2)

$I_{L} = 649 lux$

#### **Modes of Operation**

The NOA1305 can be placed in any of the following modes of operation by programming registers over the  $I^2C$  bus:

- 1. Interrupt driven mode

- 2. Polling mode

- 3. Power-down mode

In the interrupt driven mode, once the NOA1305 is configured, no  $I^2C$  activity is necessary until the ambient light intensity goes above the value programmed in the interrupt threshold register. When this occurs, the device signals an interrupt on the INT pin. Then it is up to the  $I^2C$ master host to read the ALS count from the device.

In polling mode, interrupts are typically disabled, but the NOA1305 continuously takes measurements and the  $I^2C$  master host reads out the most recent count whenever it desires to do so, typically in a timed repeat loop.

In power-down mode, the NOA1305 stops taking ambient light measurements and powers down most of the internal circuitry and the INT pin is deactivated. Power is maintained to preserve the register values (static memory) and a portion of the I<sup>2</sup>C remains active to monitor for a power-on command to the NOA1305.

#### I<sup>2</sup>C Interface

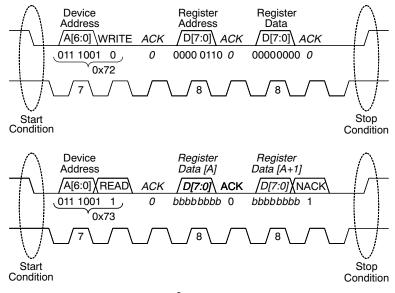

The NOA1305 acts as an I<sup>2</sup>C slave device and supports single register read and write operations, in addition to block read and block write operations. All data transactions on the bus are 8 bits long. Each data byte transmitted is followed by an acknowledge bit. Data is transmitted with the MSB first.

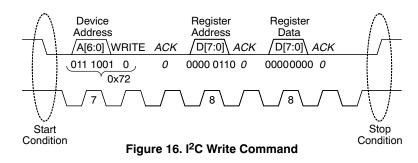

Figure 16 shows an I<sup>2</sup>C write operation. Write transactions begin with the master sending an I<sup>2</sup>C start sequence followed by the seven bit slave address (NOA1305 = 0x39) and the write(0) command bit. The NOA1305 will acknowledge this byte transfer with an appropriate ACK. Next the master will send the 8 bit register address to be written to. Again the NOA1305 will acknowledge reception with an ACK. Finally, the master will begin sending 8 bit data segment(s) to be written to the NOA1305 register bank. The NOA1305 will send an ACK after each byte and increment the address pointer by one in preparation for the next transfer. Write transactions are terminated with either an I<sup>2</sup>C STOP or with another I I<sup>2</sup>C START (repeated START).

Figure 17 shows the most basic  $I^2C$  read command sequence sent by the master to the slave device. The sequence consists of a complete  $I^2C$  write command which sets the address pointer in preparation for the  $I^2C$  read command since the read command itself does not include a register address. When reading from a read only data register in the NOA1305 it is acceptable to write a 0 to the register in order to update the address pointer, but the 0 does not actually over-write the value in the data register.

Figure 17. I<sup>2</sup>C Read Command

Once the  $I^2C$  write command is completed, the master sends an  $I^2C$  start sequence followed by the seven bit slave address (NOA1305 = 0x39) and the read (1) command bit. The NOA1305 will acknowledge this byte transfer with an appropriate ACK. The NOA1305 will then begin shifting out data from the register just addressed. If the master wishes to receive more data (next register address), it will ACK the slave at the end of the 8 bit data transmission, and the slave will respond by sending the next byte, and so on. To signal the end of the read transaction, the master will send a NACK bit at the end of a transmission followed by an  $I^2C$  STOP.

#### Rise and Fall Time of SDA (Output)

Proper operation of the  $I^2C$  bus depends on keeping the bus capacitance low and selecting suitable pull–up resistor values. Figure 15 shows the fall time on SDA in output mode under maximum load conditions. The measurement set–up is shown in Figure 18. Figure 14 shows the maximum value of the pull–up resistor (R<sub>P</sub>) as a function of the  $I^2C$  data bus capacitance.

Figure 18. Measurement Set-up

# NOA1305 Data Registers

NOA1305 operation is observed and controlled by internal data registers read from and written to via the external I<sup>2</sup>C interface. Registers are listed in Table 6. Default values are set on initial power up.

| Address | Register         | Туре | Value (binary) | Description                                                                  | Default (binary) |  |

|---------|------------------|------|----------------|------------------------------------------------------------------------------|------------------|--|

| 0x00    | POWER_CONTROL    | RW   | 0000 0000      | Power Down                                                                   | 0000 1000        |  |

|         |                  |      | 0000 1000      | Power On                                                                     |                  |  |

|         |                  |      | 0000 1001      | Test Mode 1 (reserved)                                                       |                  |  |

|         |                  |      | 0000 1010      | Test Mode 2 (fixed output 0x5555)                                            |                  |  |

|         |                  |      | 0000 1011      | Test Mode 3 (fixed output 0xAAAA)                                            |                  |  |

| 0x01    | RESET            | RW   | 0001 0000      | Reset ALS data. Resets to 0000                                               | 0000 0000        |  |

| 0x02    | INTEGRATION_TIME | RW   | 0000 0000      | 800 ms continuous measurement                                                | 0000 0010        |  |

|         |                  |      | 0000 0001      | 400 ms continuous measurement                                                |                  |  |

|         |                  |      | 0000 0010      | 200 ms continuous measurement                                                |                  |  |

|         |                  |      | 0000 0011      | 100 ms continuous measurement                                                |                  |  |

|         |                  |      | 0000 0100      | 50 ms continuous measurement                                                 |                  |  |

|         |                  |      | 0000 0101      | 25 ms continuous measurement                                                 |                  |  |

|         |                  |      | 0000 0110      | 12.5 ms continuous measurement                                               |                  |  |

|         |                  |      | 0000 0111      | 6.25 ms continuous measurement                                               |                  |  |

| 0x03    | INT_SELECT       | RW   | 0000 0001      | $L \rightarrow H$                                                            | 0000 0011        |  |

|         |                  |      | 0000 0010      | $H \rightarrow L$                                                            |                  |  |

|         |                  |      | 0000 0011      | Inactive, always H                                                           |                  |  |

| 0x04    | INT_THRESH_LSB   | RW   | XXXX XXXX      | Interrupt threshold, least significant bits                                  | 0000 0000        |  |

| 0x05    | INT_THRESH_MSB   | RW   | XXXX XXXX      | Interrupt threshold, most significant bits                                   | 0000 1000        |  |

| 0x06    | ALS_DATA_LSB     | R    | XXXX XXXX      | ALS measurement data, least significant bits                                 | 0000 0000        |  |

| 0x07    | ALS_DATA_MSB     | R    | XXXX XXXX      | ALS measurement data, most significant bits 0000                             |                  |  |

| 0x08    | DEVICE_ID_LSB    | R    | 0001 1001      | Device ID value, least significant bits 0001 1<br>(1305 decimal, 0x0519 hex) |                  |  |

| 0x09    | DEVICE_ID_MSB    | R    | 0000 0101      | Device ID value, most significant bits<br>(1305 decimal, 0x0519 hex)         | 0000 0101        |  |

7. Writing a value other than those specified for registers 0x00, 0x01, 0x02, 0x03 will cause the specified default value to be written instead.

#### POWER\_CONTROL Register (0x00)

The POWER\_CONTROL register is used to power the device up and down via software control. By default this device powers up in the power ON mode. To reduce power consumption, the NOA1305 can be powered down at any time by writing 0x00 to this register.

To power up the device, use the following write command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x00 for the POWER\_CONTROL register address

- 4. Issue 0x08 to put the device in the power on state

- 5. Issue Stop command

After applying power to the device or after issuing a power-on command, stable ALS\_DATA and INT signal may not be available for the first three integration times. For example with a default of 200 ms integration time, the  $I^2C$  master should wait at least 600 ms before accessing this device.

To power down the device, use the following write command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x00 for the POWER\_CONTROL register address

- 4. Issue 0x00 to put the device in the power down state

- 5. Issue Stop command

After issuing a power-on command, the  $I^2C$  master should wait at least 1.5 ms before accessing this device.

The data registers are set to their default values when power is first applied to the device. However the power-down and power-on commands do not affect the values of the data registers.

The test modes provide a useful debugging mode as they cause the device to output known values in place of the ALS\_DATA values.

## **RESET Register (0x01)**

Software reset is controlled by this register. Setting this register followed by an I2C\_STOP sequence will immediately reset the NOA1305 to the startup standby state and clear the ALS\_DATA register. However the values of the other data registers are not affected.

To reset the device, use the following write command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x01 for the RESET register address

- 4. Issue 0x10 to reset the device

- 5. Issue Stop command

After issuing a reset command, the device will reset the RESET register to 0x00.

#### INTEGRATION\_TIME Register (0x02)

The INTEGRATION\_TIME register controls the integration time of the ambient light sensor which directly affects the sensitivity.

To set the integration time, use the following write command sequence:

- 1. Issue Start command

- 2. Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x02 for the INTEGRATION\_TIME register address

- 4. Issue 0x02 to set the integration time to 200 ms (for example)

- 5. Issue Stop command

## INT\_SELECT Register (0x03)

The INT\_SELECT register controls the polarity of the interrupt pin INT and enables or disables interrupts on that pin.

To specify low to high transitions on INT to signal an interrupt, use the following write command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x03 for the INT\_SELECT register address

- 4. Issue 0x01 to specify low to high signaling on INT

- 5. Issue Stop command

To specify low to high transitions on INT to signal an interrupt, use the following write command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x03 for the INT\_SELECT register address

- 4. Issue 0x02 to specify high to low signaling on INT

- 5. Issue Stop command

Disabling interrupts causes the INT pin to be held in the open-drain or high state. To disable interrupts completely on the INT pin, use the following write command sequence:

- 1. Issue Start command

- 2. Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x03 for the INT\_SELECT register address

- 4. Issue 0x03 to disable interrupts on INT

- 5. Issue Stop command

# INT\_THRESH\_LSB and INT\_THRES\_MSB Registers (0x04, 0x05)

The INT\_THRESH register specifies an ambient light threshold value for signaling interrupts on the INT pin. The INT\_THRESH register is 16-bits wide to match the 16-bit ALS\_DATA register and is accessed over the I<sup>2</sup>C bus as two 8-bit registers for the least and most significant bits (LSB and MSB). On any measurement cycle where the ALS\_DATA intensity count exceeds the INT\_THRESH value, the INT pin will become active and will remain active until a measurement cycle where the count is less than or equal to the threshold (and provided the INT pin is enabled, see INT\_SELECT register).

Changing the INT\_THRESH register value can cause the INT pin to change immediately if the ALS\_DATA to INT THRESH comparison changes.

Powering down the device will cause the INT pin to become inactive.

To program a value into the INT\_THRESH register, use the following write command sequence:

- 1. Issue Start command

- 2. Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write–bit 0)

- 3. Issue 0x04 for the INT\_THRES\_LSB register address

- 4. Issue the 8–bit LSB value

- 5. Issue Stop command

- 6. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 8. Issue 0x05 for the INT\_THRES\_MSB register address

- 9. Issue the 8-bit MSB value

- 10. Issue Stop command

After a power-down and power-on sequence, wait at least three integration times for the data to stabilize, before accessing any ALS\_DATA values from NOA1305.

# ALS\_DATA\_LSB and ALS\_DATA\_MSB Registers (0x06, 0x07)

The ALS\_DATA register holds the ambient light intensity count from the most recent measurement. The ALS\_DATA register is 16-bits wide and is accessed from the I<sup>2</sup>C bus as two 8-bit registers for the least and most significant bits (LSB and MSB).

To read the ALS\_DATA register, use the following read command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x06 for the INT\_DATA\_LSB register address

- 4. Issue Start command

- 5. Issue 0x73 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by read-bit 1)

- 6. Read the ALS\_DATA\_LSB byte

- 7. Read the ALS DATA MSB byte

- 8. Issue Stop command

# DEVICE\_ID\_LSB and DEVICE\_ID\_MSB Registers (0x08, 0x09)

The DEVICE\_ID register is a pre-programmed register that describes the device. For the NOA1305, the register holds the decimal value of 1305 (0x0519). The DEVICE\_ID register is 16-bits wide and is accessed from the I<sup>2</sup>C bus as two 8-bit registers for the least and most significant bits (LSB and MSB).

To read the DEVICE\_ID register, use the following read command sequence:

- 1. Issue Start command

- Issue 0x72 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by write-bit 0)

- 3. Issue 0x08 for the DEVICE\_ID\_LSB register address

- 4. Issue Start command

- 5. Issue 0x73 (lower seven bits of I<sup>2</sup>C slave address 0x39 followed by read-bit 1)

- 6. Read the DEVICE ID LSB byte

- 7. Read the DEVICE ID MSB byte

- 8. Issue Stop command

#### **Example Programming Sequence**

The following pseudo code configures the NOA1305 ambient light sensor and then runs it in an interrupt driven mode. When the controller receives an interrupt, it reads the ALS\_Data from the device, sets a flag and then waits for the main polling loop to respond to the ambient light change.

```

external subroutine I2C Read Byte (I2C Address, Data Address);

external subroutine I2C Read Block (I2C Address, Data Start Address, Count, Memory Map);

external subroutine I2C Write Byte (I2C Address, Data Address, Data);

external subroutine I2C Write Block (I2C Address, Data Start Address, Count, Memory Map);

subroutine Initialize ALS () {

MemBuf[0x00] = 0x08; // POWER CONTROL assert Power On

MemBuf[0x01] = 0x10; // RESET assert reset

// INTEGRATION TIME select 200ms

MemBuf[0x02] = 0x02;

MemBuf[0x03] = 0x01;

// INT SELECT select Low to High

// INT THRESH LSB

MemBuf[0x04] = 0xFF;

MemBuf[0x05] = 0x8F;

// INT THRESH MSB

I2C_Write_Block (I2CAddr, 0x00, 6, MemBuf);

}

subroutine I2C_Interupt_Handler () {

// Retrieve and store the ALS data

ALS Data LSB = I2C_Read_Byte (I2CAddr, 0x06);

ALS Data MSB = I2C Read Byte (I2CAddr, 0x07);

NewALS = 0 \times 01;

}

subroutine main loop () {

I2CAddr = 0x39;

NewALS = 0 \times 00;

Initialize_ALS ();

loop {

// Do some other polling operations

if (NewALS == 0x01) {

NewALS = 0 \times 00;

// Do some operations with ALS Data

}

}

}

```

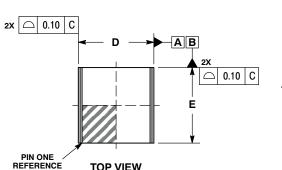

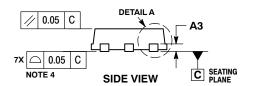

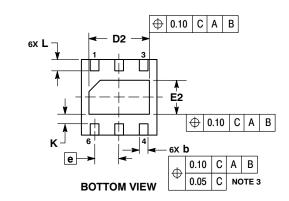

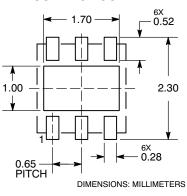

#### PACKAGE DIMENSIONS

#### CUDFN6, 2x2 CASE 505AD-01 ISSUE B

**END VIEW**

NOTES 1. DIMENSIONING AND TOLERANCING PER ASME

- V14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM 3

- THE TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED PAD AS

| WELL AS THE TERMINALS. |             |       |  |  |  |  |

|------------------------|-------------|-------|--|--|--|--|

|                        | MILLIMETERS |       |  |  |  |  |

| DIM                    | MIN         | MAX   |  |  |  |  |

| Α                      | 0.55        | 0.65  |  |  |  |  |

| A1                     | 0.00        | 0.05  |  |  |  |  |

| A3                     | 0.20 REF    |       |  |  |  |  |

| b                      | 0.18 0.28   |       |  |  |  |  |

| D                      | 2.00 BSC    |       |  |  |  |  |

| D2                     | 1.50        | 1.70  |  |  |  |  |

| d                      |             | 0.10  |  |  |  |  |

| E                      | 2.00        | ) BSC |  |  |  |  |

| E2                     | 0.80        | 1.00  |  |  |  |  |

| е                      | 0.65        | BSC   |  |  |  |  |

| K                      | 0.20        |       |  |  |  |  |

| L                      | 0.25        | 0.35  |  |  |  |  |

| θ                      | 4°          | 10°   |  |  |  |  |

MOUNTING FOOTPRINT

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without particular purpose, nor loss of LEC existing any including ansing out of the application of use of any product of including window in SCILLC data sheets and/or specifications can and or vary in different applications and a analytical parameters which may be provided in SCILLC data sheets and/or specifications can and or vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC data sheets and/or specifications can and or vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC groducts are not designed, intended, or authorized for use as components in systems intended for surgical implant into the applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exponses, and reasonable attorney fees arising out of, directly or indirectly, and claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative