# 3 Gbps, 2 differential-pair channel eSATA signal re-driver

**Datasheet - production data**

#### **Features**

- Supports eSATA data rate of 1.5 Gbps and 3 Gbps

- Supports complete eSATA bus of two 2-wire differential-pair channels

- Squelch detector for validity of input differential signal

- Single operating supply (V<sub>CC</sub>) range of 3.3 V ± 10%

- Low power mode

- 100 Ω CML I/Os

- eSATA hot plug capable

- Low capacitance on all channels

- 1-bit input equalizer regenerates the receiver attenuated signal

- 1-bit adjustable pre-emphasis and driver to drive the transmitter outputs over long PCB track lengths

- Low output skew and jitter

- Low ground bounce

- Available in QFN20 (4 x 4 mm) package footprint with flow-through pinout

- 0 °C to 85 °C operating temperature range

Table 1. Device summary

| Order code  | Package          | Packing       |  |

|-------------|------------------|---------------|--|

| STA1102RUTR | QFN20 (4 x 4 mm) | Tape and reel |  |

Contents STA1102R

## **Contents**

| 1    | Desc   | cription                      | . 3 |

|------|--------|-------------------------------|-----|

| 2    | Bloc   | k diagram                     | . 4 |

| 3    | Fund   | ctional description           | . 7 |

|      | 3.1    | Equalizer                     | . 7 |

|      | 3.2    | Pre-emphasis                  | . 7 |

|      | 3.3    | Input termination             | . 8 |

|      | 3.4    | Low power modes               | . 8 |

|      |        | 3.4.1 Hardware low power mode | . 8 |

|      |        | 3.4.1 Hardware low power mode | . 8 |

|      | 3.5    | Squelch detector              | . 8 |

| 4    | Appl   | lication diagram              | . 9 |

| 5    |        | olute maximum ratings         |     |

| 6    |        | mal data                      |     |

| 7    | Reco   | ommended operating conditions | 11  |

|      | Electi | rical characteristics         | 11  |

| 8    | Pack   | age information               | 14  |

| 9.50 | Revi   | sion history                  | 17  |

STA1102R Description

### 1 Description

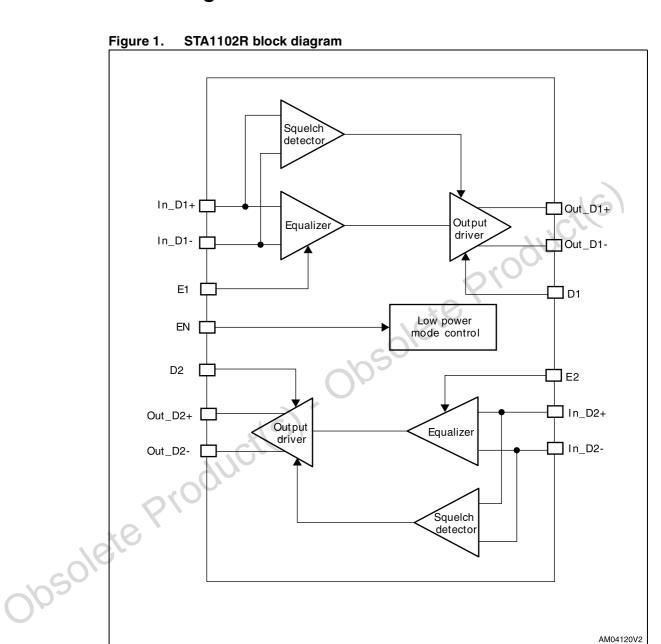

The STA1102R device is a serial data signal re-driver. It integrates two differential-pair channels suitable for eSATA signals up to a 3 Gbps data rate, in compliance with the SATA rev 2.6 specification.

An input detector is available at each channel, which constantly monitors the input signal level for output squelch functionality. If the detected differential input is below a defined threshold, the output is biased to the common mode voltage.

High-speed data paths and the flow-through pinout minimize internal device jitter and simplify board layout. The integrated input equalizer improves signal integrity at the receiver due to effects from lossy cables. A 1-bit adjustable pre-emphasis is also integrated to drive the transmitter outputs over long PCB track lengths.

The device can be set to a low-power mode by disabling the output current drivers through the EN pin.

Block diagram STA1102R

## 2 Block diagram

STA1102R Block diagram

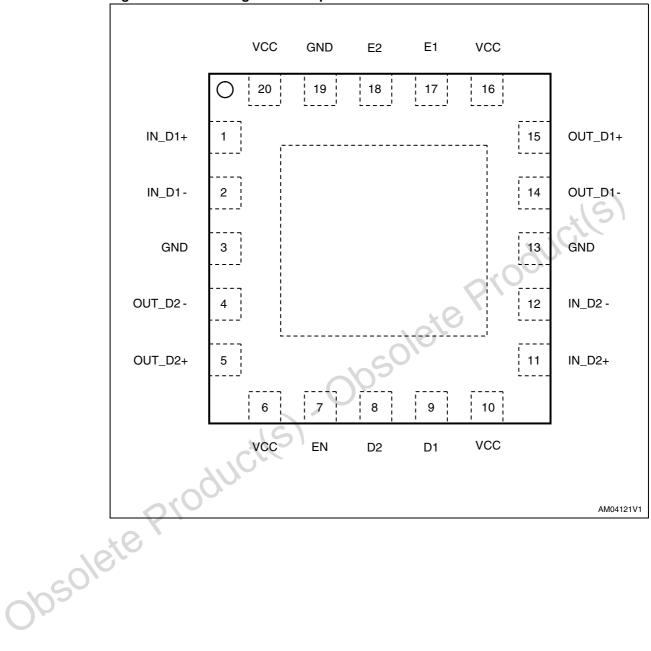

Figure 2. Pin configuration - top view

Block diagram STA1102R

Table 2. Pin description

| Pin number | Pin name | Туре   | Function                                                                                                                      |

|------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 1          | IN_D1+   | Input  | IN_D1+ makes a differential pair with IN_D1-                                                                                  |

| 2          | IN_D1-   | Input  | IN_D1- makes a differential pair with IN_D1+                                                                                  |

| 3          | GND      | Power  | Ground                                                                                                                        |

| 4          | OUT_D2-  | Output | OUT_D2- makes a differential pair with OUT_D2+                                                                                |

| 5          | OUT_D2+  | Output | OUT_D2+ makes a differential pair with OUT_D2-                                                                                |

| 6          | VCC      | Power  | 3.3 V DC supply                                                                                                               |

| 7          | EN       | Input  | Output driver enable pin; when low, device enters low power mode (internal 360 k $\Omega$ pull-up resistor to V $_{\rm CC}$ ) |

| 8          | D2       | Input  | Channel 2 pre-emphasis selection (internal 360 k $\Omega$ pull-down resistor to GND)                                          |

| 9          | D1       | Input  | Channel 1 pre-emphasis selection (internal 360 k $\Omega$ pull-down resistor to GND)                                          |

| 10         | VCC      | Power  | 3.3 V DC supply                                                                                                               |

| 11         | IN_D2+   | Input  | IN_D2+ makes a differential pair with IN_D2-                                                                                  |

| 12         | IN_D2-   | Input  | IN_D2- makes a differential pair with IN_D2+                                                                                  |

| 13         | GND      | Power  | Ground                                                                                                                        |

| 14         | OUT_D1-  | Output | OUT_D1- makes a differential pair with OUT_D1+                                                                                |

| 15         | OUT_D1+  | Output | OUT_D1+ makes a differential pair with OUT_D1-                                                                                |

| 16         | VCC      | Power  | 3.3 V DC supply                                                                                                               |

| 17         | E1       | Input  | Channel 1, input equalization selection (internal 360 $k\Omega$ pull down resistor to GND)                                    |

| 18         | E2       | Input  | Channel 2, input equalization selection (internal 360 k $\Omega$ pull down resistor to GND)                                   |

| 19         | GND      | Power  | Ground                                                                                                                        |

| 20         | vcc      | Power  | 3.3 V DC supply                                                                                                               |

## 3 Functional description

### 3.1 Equalizer

The adjustable input equalizer reduces system jitter and attenuation from long or lossy cables. Shaping is performed by the gain stage of the equalizer to compensate the signal.

Table 3. Input equalizer truth table

| EN | E1 | E2 | Function                                                           |

|----|----|----|--------------------------------------------------------------------|

| 0  | х  | х  | Low power mode: input stage disabled for minimum power consumption |

| 1  | 0  | 0  | Normal operation mode:<br>both CH1 and CH2 7dB EQ                  |

| 1  | 0  | 1  | Normal operation mode:<br>CH1 7dB EQ; CH2 9dB EQ                   |

| 1  | 1  | 0  | Normal operation mode:<br>CH1 9dB EQ; CH2 7dB EQ                   |

| 1  | 1  | 1  | Normal operation mode:<br>both CH1 and CH2 9dB EQ                  |

Note: 9 dB EQ is useful for signal recovery over long PCB track, e.g. 10" FR4.

# 3.2 Pre-emphasis

The STA1102R provides at each output a differential pair of 1-bit programmable preemphasis to compensate for losses across long PCB tracks and interconnects after the redriver output. Below, the truth table of the pre-emphasis control is shown:

Table 4. Pre-emphasis truth table

| EN | D1 | D2 | Functions                                                                |

|----|----|----|--------------------------------------------------------------------------|

| 0  | х  | х  | Low power mode:<br>output driver disabled; output driven to HiZ          |

| 1  | 0  | 0  | Normal operation mode:<br>both CH1 and CH2 0 dB pre-emphasis             |

| 1  | 0  | 1  | Normal operation mode:<br>CH1 0 dB pre-emphasis; CH2 2.5 dB pre-emphasis |

| 1  | 1  | 0  | Normal operation mode:<br>CH1 2.5 dB pre-emphasis; CH2 0 dB pre-emphasis |

| 1  | 1  | 1  | Normal operation mode:<br>both CH1 and CH2 2.5 dB pre-emphasis           |

### 3.3 Input termination

The STA1102R integrates precise 50  $\Omega\pm10\%$  termination resistors, pulled up to  $V_{Cm}$ , on all its differential input channels. External terminations are not required. This gives improved performance and also minimizes the PCB board space. These on-chip termination resistors should match the differential characteristic impedance of the transmission line.

### 3.4 Low power modes

There are 2 types of low power modes in the STA1102R: hardware low and auto low power modes.

#### 3.4.1 Hardware low power mode

The EN input activates a hardware low power mode. There is an internal pull-up resistor to maintain the EN in the default (HIGH) state. When this low power mode is activated (EN = L), all input and output buffers and internal bias circuitry are powered off and disabled. Outputs are driven to HiZ in low power mode. There is a delay associated with entering (max.  $2 \mu s$ ) and exiting (max.  $20 \mu s$ ) this hardware low power mode.

### 3.4.2 Auto low power mode

The auto low power mode is activated when differential voltage at either or both of the channels is < 50 mV for more than 3  $\mu$ s. During this low power mode, output of the associated channel is driven to  $V_{cm}$  and the selective circuit block is disabled to lower power consumption. The delay associated with exiting the auto low power mode is 50 ns max.

### 3.5 Squelch detector

A squelch detector is integrated on the input of each of the 2 data paths. The squelch detector is a high-speed amplitude comparator that is turned on when EN = H. The differential input signal is monitored by the detector. When the differential input is detected to be less than or equal to 50 mV, the input signal is considered an invalid signal and is not passed to the output. When this happens, the corresponding output is biased to  $V_{CM}$ . When the differential input is greater than or equal to 150 mV, the input signal is considered valid signal and is passed to the output.

The integration of the squelch detector helps the system to prevent responding to noises. As such, it enables the device to fully support OOB signaling.

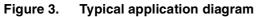

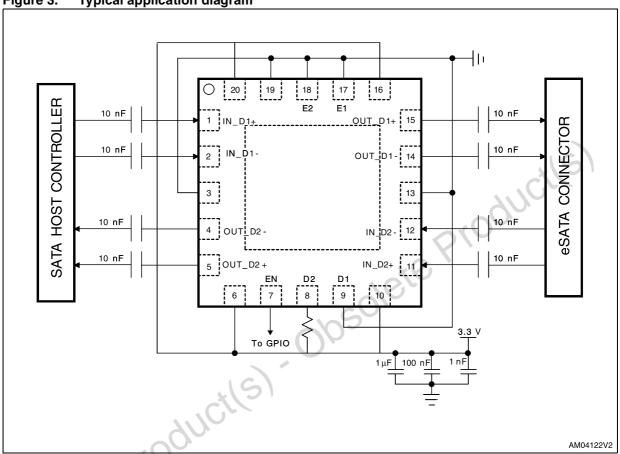

## 4 Application diagram

Note: Typical circuit above is shown with CHI1 Pre-Emp of 0 dB, EQ of 7 dB; CH2 Pre-Emp of 2.5 dB, EQ of 7 dB.

#### **Absolute maximum ratings** 5

Absolute maximum ratings are those values above which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

Table 5. **Absolute maximum ratings**

| Symbol           | Parame                                                    | eter                                    | Value         | Unit |  |  |  |

|------------------|-----------------------------------------------------------|-----------------------------------------|---------------|------|--|--|--|

| V <sub>CC</sub>  | Supply voltage to ground                                  |                                         | -0.5 to + 4.0 | V    |  |  |  |

| V                | Differential pair IOs voltage range                       | -0.5 to + 4.0                           | ٧             |      |  |  |  |

| V <sub>I</sub>   | Control IOs voltage range                                 |                                         | -0.5 to + 4.0 | V    |  |  |  |

| T <sub>STG</sub> | Storage temperature                                       | -65 to + 150                            | °C            |      |  |  |  |

| V <sub>ESD</sub> | Electrostatic discharge voltage (human body model JESD22- | Differential input and output data pins | ±12           | kV   |  |  |  |

|                  | A114C.01)                                                 | All other pins                          | ±8            |      |  |  |  |

| Thermal data     |                                                           |                                         |               |      |  |  |  |

#### Thermal data 6

QFN20 package thermal data Table 6.

|      | Symbol        | Parameter                              | QFN20 | Unit |

|------|---------------|----------------------------------------|-------|------|

|      | $\theta_{JA}$ | Thermal coefficient (junction-ambient) | 45    | °C/Ω |

| 76   | refe          | o rodio.                               |       |      |

| Opso |               |                                        |       |      |

577 10/18 Doc ID 16470 Rev 5

# 7 Recommended operating conditions

Table 7. Recommended operating conditions

| Symbol          | Parameter                     | Test conditions | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------|-----------------|------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | -               | 3.0  | 3.3  | 3.6  | V    |

| T <sub>A</sub>  | Operating ambient temperature | -               | 0    | -    | 85   | °C   |

| C <sub>C</sub>  | Coupling capacitor            | -               | -    | 12   | -    | nF   |

| $D_R$           | Data rate                     | -               | 1    | -    | 3.0  | Gbps |

### **Electrical characteristics**

( $T_A$  = 0 to 85 °C,  $V_{CC}$  = 3.0 V to 3.6 V unless otherwise specified).

Table 8. DC electrical characteristic

| Symbol                           | Parameter                   | Test conditions                                                                  | Min. | Тур. | Max. | Unit      |  |

|----------------------------------|-----------------------------|----------------------------------------------------------------------------------|------|------|------|-----------|--|

| General pa                       | rameter characteristics     | 18/6                                                                             |      |      |      |           |  |

| I <sub>CC_standby</sub>          | Standby mode supply current | EN = L                                                                           | -    | -    | 300  | μΑ        |  |

| I <sub>CC_active</sub>           | Active mode supply current  | V <sub>DIFF_RX</sub> = 700 mV, K28.5<br>pattern running at 3 Gbps<br>D1 = D2 = H | -    | -    | 80   | mA        |  |

| I <sub>CC_squelch</sub>          | i Cil                       | $V_{DIFF\_RX} \le V_{TH}$ , EN = H<br>D1= D2 = H                                 | -    | -    | 45   | mA        |  |

| T <sub>PD</sub>                  | Data propagation delay      | -                                                                                | -    | -    | 400  | ps        |  |

| T <sub>DIS</sub>                 | Device disable time         | EN = H to L                                                                      | -    | -    | 2    | μs        |  |

| T <sub>EN</sub>                  | Device enable time          | EN = L to H                                                                      | -    | -    | 20   | μs        |  |

| Control log                      | gic characteristics         |                                                                                  |      |      |      |           |  |

| V <sub>IH</sub>                  | Input logic high voltage    | -                                                                                | 1.4  | -    | -    | V         |  |

| V <sub>IL</sub>                  | Input logic low voltage     | -                                                                                | -    | -    | 0.5  | V         |  |

| I <sub>IH</sub>                  | Input logic high current    | -                                                                                | -15  | -    | 15   | μΑ        |  |

| I <sub>IL</sub>                  | Input logic low current     | -                                                                                | -15  | -    | 15   | μΑ        |  |

| Squelch detector characteristics |                             |                                                                                  |      |      |      |           |  |

| V <sub>TH</sub>                  | Squelch threshold voltage   | -                                                                                | 50   | -    | 150  | $mV_{pp}$ |  |

| T <sub>ENTER</sub>               | Squelch mode enter          | -                                                                                | -    | -    | 5    | ns        |  |

| T <sub>EXIT</sub>                | Squelch mode exit           | -                                                                                | -    | -    | 5    | ns        |  |

577

Table 8. DC electrical characteristic (continued)

| Symbol                            | Parameter                               | Test conditions           | Min. | Тур.     | Max. | Unit      |  |

|-----------------------------------|-----------------------------------------|---------------------------|------|----------|------|-----------|--|

| AC/DC specifications for receiver |                                         |                           |      |          |      |           |  |

| V <sub>DIFF_RX</sub>              | Differential input peak-to-peak voltage | D <sub>R</sub> = 3.0 Gbps | 200  | -        | 1600 | $mV_{pp}$ |  |

| V <sub>CM_RX</sub>                | Common mode voltage                     | -                         | -    | 0        | -    | V         |  |

| Z <sub>DIFF_RX</sub>              | Differential input impedance            | -                         | 85   | 100      | 115  | Ω         |  |

| Z <sub>SE_RX</sub>                | Single-ended input impedance            | -                         | 40   | -        | -    | Ω         |  |

|                                   |                                         | f = 100 MHz to 300 MHz    | 18   | -        | -    | dB        |  |

|                                   |                                         | f = 300 MHz to 600 MHz    | 14   | -        | i G  | dB        |  |

| RL <sub>DIFF_RX</sub>             | Differential input return loss          | f = 600 MHz to 1200 MHz   | 10   | -        |      | dB        |  |

|                                   |                                         | f = 1.2 GHz to 2.4 GHz    | 8    | 71),     | ٠.   | dB        |  |

|                                   |                                         | f = 2.4 GHz to 3.0 GHz    | 3    | <u> </u> | -    | dB        |  |

Table 9. AC electrical characteristic

| Table 5.              | AC electrical characteristic     | 10                                   |      |      | 1    |           |

|-----------------------|----------------------------------|--------------------------------------|------|------|------|-----------|

| Symbol                | Parameter                        | Test conditions                      | Min. | Тур. | Max. | Unit      |

|                       |                                  | f = 100 MHz to 300 MHz               | 5    | -    | -    | dB        |

|                       |                                  | f = 300 MHz to 600 MHz               | 5    | -    | -    | dB        |

| RL <sub>CM_RX</sub>   | Common mode input return loss    | f = 600 MHz to 1200 MHz              | 2    | -    | -    | dB        |

|                       | (                                | f = 1.2 GHz to 2.4 GHz               | 1    | -    | -    | dB        |

|                       | , cil                            | f = 2.4 GHz to 3.0 GHz               | 1    | -    | -    | dB        |

| T <sub>R/F_RX</sub>   | Input rise/fall time             | 20% to 80%                           | 67   | -    | 136  | ps        |

| T <sub>Skew_RX</sub>  | Input differential skew          | Mid-point of RX+ to mid-point of RX- | -    | -    | 50   | ps        |

| AC/DC spe             | cifications for transmitter      |                                      |      |      |      |           |

| V <b>A</b>            | Differential output peak-to-peak | f = 1.5 GHz; D1/D2 = L               | 400  | -    | 600  | $mV_{pp}$ |

| $V_{DIFF\_TX}$        | voltage                          | f = 1.5 GHz; D1/D2 = H               | 600  | -    | 800  | $mV_{pp}$ |

| V <sub>CM_TX</sub>    | Common mode voltage              | -                                    | -    | 2.1  | -    | V         |

| $Z_{DIFF\_TX}$        | Differential output impedance    | -                                    | 85   | 100  | 115  | Ω         |

| Z <sub>SE_TX</sub>    | Single-ended output impedance    | -                                    | 40   | -    | -    | Ω         |

|                       |                                  | f = 100 MHz to 300 MHz               | 14   | -    | -    | dB        |

|                       |                                  | f = 300 MHz to 600 MHz               | 8    | -    | -    | dB        |

| RL <sub>DIFF_TX</sub> | Differential output return loss  | f = 600 MHz to 1200 MHz              | 6    | -    | -    | dB        |

|                       |                                  | f = 1.2 GHz to 2.4 GHz               | 6    | -    | -    | dB        |

|                       |                                  | f = 2.4 GHz to 3.0 GHz               | 3    | -    | -    | dB        |

|                       |                                  |                                      |      |      |      |           |

Table 9. AC electrical characteristic (continued)

| Symbol                                             | Parameter                | Test conditions                        | Min. | Тур. | Max. | Unit              |

|----------------------------------------------------|--------------------------|----------------------------------------|------|------|------|-------------------|

|                                                    |                          | f = 100 MHz to 300 MHz                 | 5    | -    | -    | dB                |

| RL <sub>CM_TX</sub> Common mode output return loss |                          | f = 300 MHz to 600 MHz                 | 5    | -    | -    | dB                |

|                                                    | f = 600 MHz to 1200 MHz  | 2                                      | -    | -    | dB   |                   |

|                                                    |                          | f = 1.2 GHz to 2.4 GHz                 | 1    | -    | -    | dB                |

|                                                    |                          | f = 2.4 GHz to 3.0 GHz                 | 1    | -    | -    | dB                |

| T <sub>R/F_TX</sub>                                | Output rise/fall time    | 20% to 80%                             | 67   | -    | 136  | ps                |

| T <sub>Skew_TX</sub>                               | Output differential skew | Mid-point of RX+ to mid-point of RX-   | ı    | -    | 20   | ps                |

| $TJ_TX$                                            | Total jitter             | D <sub>R</sub> = 3 Gbps; K28.5 pattern | i    | 0.2  | 0.3  | UI <sub>pp</sub>  |

| $DJ_TX$                                            | Deterministic jitter     | D <sub>R</sub> = 3 Gbps; K28.5 pattern | ı    | 0.13 | 0.2  | UI <sub>pp</sub>  |

| $RJ_{TX}$                                          | Random jitter            | D <sub>R</sub> = 3 Gbps; K28.7 pattern | -    | 2.0  | 2.15 | ps <sub>rms</sub> |

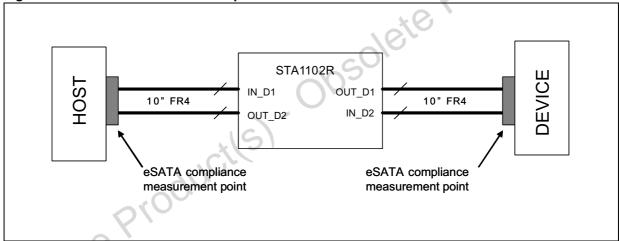

Figure 4. Jitter measurement setup

Package information STA1102R

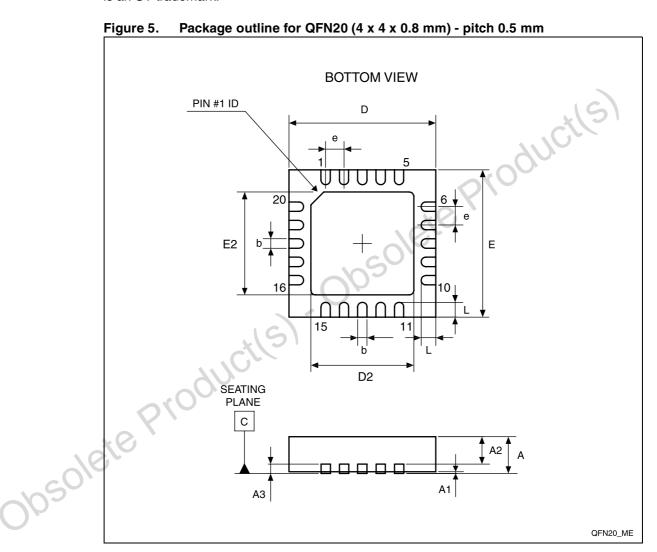

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

STA1102R Package information

Table 10. STA1102RUTR - mechanical data for QFN20 (4 x 4 x 0.8 mm) - pitch 0.5 mm

| - pitch 0.5 min |                            |           |      |  |  |  |

|-----------------|----------------------------|-----------|------|--|--|--|

|                 | Dimensions  Millimeters    |           |      |  |  |  |

| Symbol          |                            |           |      |  |  |  |

|                 | Min.                       | Тур.      | Max. |  |  |  |

| A               | 0.70                       | 0.75      | 0.80 |  |  |  |

| A1              | -                          | 0.02      | -    |  |  |  |

| A2              | -                          | 0.65      | -    |  |  |  |

| A3              | -                          | 0.20      | -    |  |  |  |

| b               | 0.18                       | 0.25      | 0.30 |  |  |  |

| D               | 3.85                       | 4.00      | 4.15 |  |  |  |

| D2              | See exposed pad variations |           |      |  |  |  |

| E               | 3.85                       | 4.00      | 4.15 |  |  |  |

| E2              | See exposed pad variations |           |      |  |  |  |

| е               | 0.45                       | 0.50 0.55 |      |  |  |  |

| L               | 0.45                       | 0.55      | 0.65 |  |  |  |

Table 11. STA1102RUTR - exposed pad variations

|                 | Variation | D2        |      | E2   |      |      |  |

|-----------------|-----------|-----------|------|------|------|------|--|

|                 | variation | Min. Typ. | Max. | Min. | Тур. | Max. |  |

|                 | А         | 2.00 2.10 | 2.20 | 2.00 | 2.10 | 2.20 |  |

| Obsoleite Prool |           |           |      |      |      |      |  |

Package information STA1102R

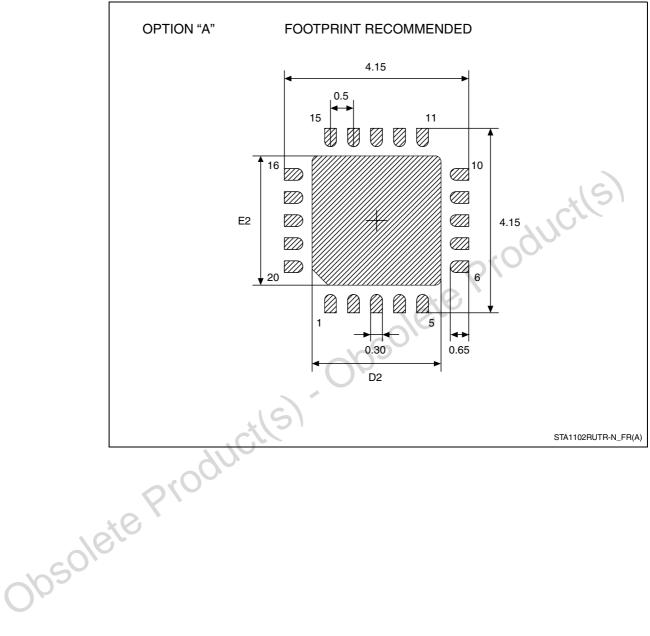

Figure 6. STA1102RUTR - footprint recommendation for QFN20 (4 x 4 x 0.8 mm) - pitch 0.5 mm

16/18 Doc ID 16470 Rev 5

STA1102R Revision history

# 9 Revision history

Table 12. Document revision history

| Date                                                                                                         | Revision | Changes                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 19-Oct-2009                                                                                                  | 1        | Initial release.                                                                                                                                                                                                                                                                                       |  |  |  |

| 08-Jan-2010                                                                                                  | 2        | Updated: Figure 1, Figure 2, Table 2, Section 2.1, Section Figure 3. and Table 5.                                                                                                                                                                                                                      |  |  |  |

| 12-Mar-2010                                                                                                  | 3        | Updated package information. Replaced D1 with D2 and D0 with D1.                                                                                                                                                                                                                                       |  |  |  |

| 04-Feb-2011                                                                                                  | 4        | Document reformatted, added <i>Contents</i> , updated <i>Table 5</i> , corrected typo in <i>Figure 1</i> , <i>Table 2</i> , <i>Table 3</i> , <i>Section 3.2</i> , <i>Section 3.4.1</i> , <i>Section 3.5</i> , <i>Figure 3</i> , <i>Figure 5</i> , <i>Figure 6</i> , <i>Table 8</i> , <i>Table 11</i> . |  |  |  |

| 31-Jan-2013                                                                                                  | 5        | Updated temperature in <i>Features</i> (replaced -40 by 0). Minor corrections throughout document.                                                                                                                                                                                                     |  |  |  |

| 31-Jan-2013 5 Updated temperature in **Peatures* (replaced -40 by 0). Minor corrections throughout document. |          |                                                                                                                                                                                                                                                                                                        |  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

18/18 Doc ID 16470 Rev 5