# Sup*IR*Buck™

## **USER GUIDE FOR IRDC3473 EVALUATION BOARD**

### **DESCRIPTION**

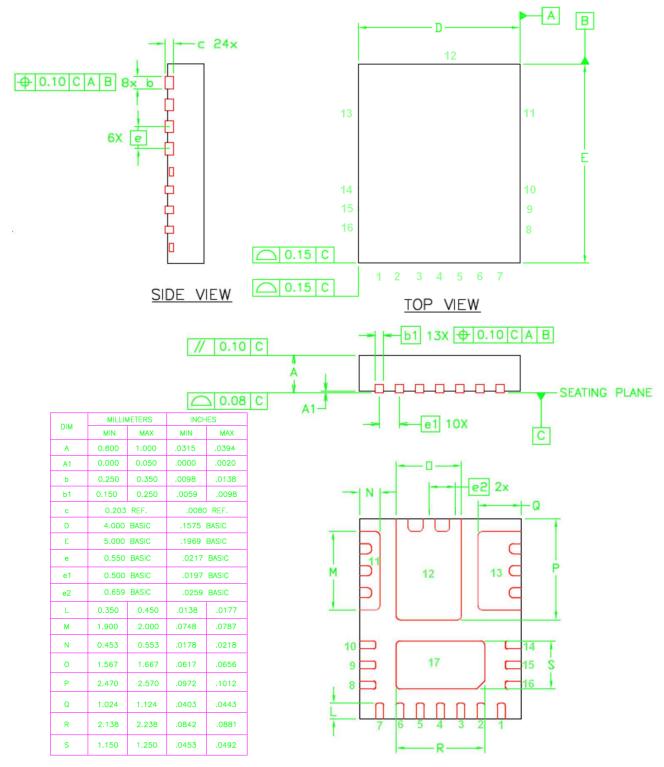

The IR3473 SupIRBuck™ is an easy-to-use, fully integrated and highly efficient DC/DC voltage regulator. The onboard constant on time hysteretic controller and MOSFETs make IR3473 a space-efficient solution that delivers up to 6A of precisely controlled output voltage. IR3473 is housed in a 4mmx5mm QFN package.

Key features offered by IR3473 include: programmable switching frequency, soft start, temperature compensated over current protection, and thermal shutdown allowing a very flexible solution suitable for many different applications and an ideal choice for battery powered applications.

Additional features include pre-bias startup, a very precise 0.5V reference, forced continuous conduction mode option, over/under voltage protection, power good output, and enable input with voltage monitoring capability.

This user guide contains the schematic, bill of materials, and operating instructions of the IRDC3473 evaluation board. Detailed product specifications, application information and performance curves at different operating conditions are available in the IR3473 data sheet.

### **BOARD FEATURES**

- V<sub>IN</sub> = +12V

- V<sub>CC</sub> = +5V

- V<sub>OUT</sub> = +1.05V

- I<sub>OUT</sub> = 0 to 6A

- F<sub>S</sub> = 300kHz @ CCM

- L = 2.2µH

- $C_{IN} = 22\mu F$  (ceramic 1210) +  $68\mu F$  (electrolytic)

- $C_{OUT} = 47 \mu F$  (ceramic 0805) + 150  $\mu F$  (POSCAP)

#### CONNECTIONS and OPERATING INSTRUCTIONS

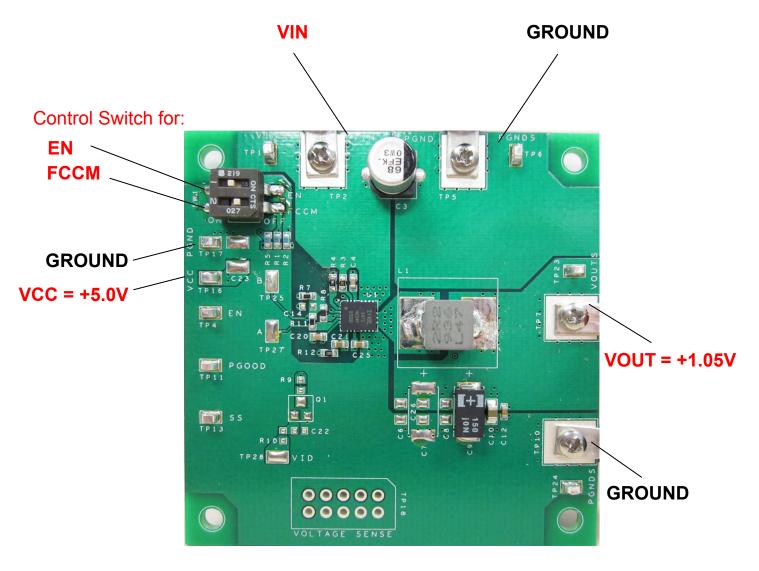

An input supply in the range of 8 to 19V should be connected from VIN to PGND. A maximum load of 6A may be connected to  $V_{\text{OUT}}$  and PGND. The connection diagram is shown in Fig. 1, and the inputs and outputs of the board are listed in Table 1.

IRDC3473 has two input supplies, one for biasing (VCC) and the other for input voltage (VIN). Separate supplies should be applied to these inputs. VCC input should be a well regulated 4.5V to 5.5V supply connected to VCC and PGND. Enable (EN) is controlled by the first switch of SW1, and FCCM option can be selected by the second switch of SW1. Toggle the switch to the ON position (marked by a solid square) to enable switching or to select FCCM. The absolute maximum voltage of the external signal applied to EN (TP4) and FCCM is +8V.

Connection Signal Name VIN (TP2) VIN PGND (TP5) Ground for VIN VCC (TP16) VCC Input PGND (TP17) Ground for VCC Input VOUT (TP7) V<sub>OUT</sub> (+1.05V) PGND (TP10) Ground for V<sub>OUT</sub> EN (TP4) **Enable Input**

**Table 1. Connections**

### LAYOUT

The PCB is a 4-layer board. All layers are 1 oz. copper. IR3473 and other components are mounted on the top and bottom layers of the board.

The power supply decoupling capacitors, bootstrap capacitor and feedback components are located close to IR3473. To improve efficiency, the circuit board is designed to minimize the length of the onboard power ground current path.

## **CONNECTION DIAGRAM**

Fig. 1: Connection Diagram of IRDC3473 Evaluation Board

## **PCB Board Layout**

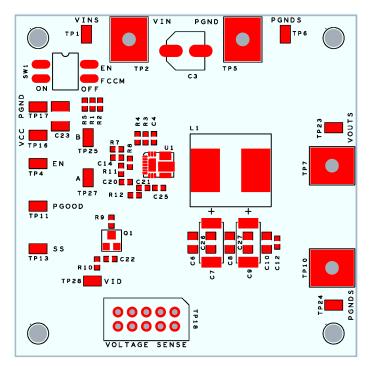

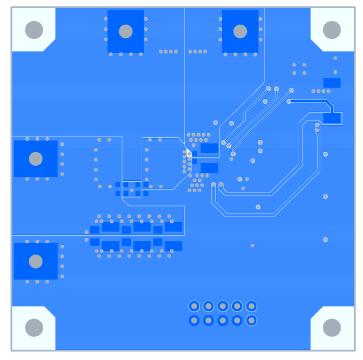

Fig. 2: Board Layout, Top Components

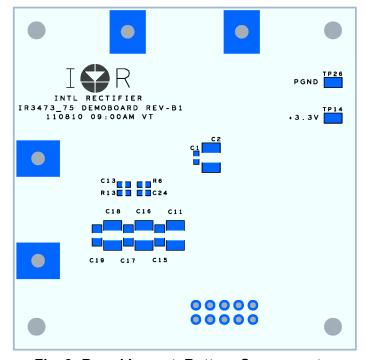

Fig. 3: Board Layout, Bottom Components

## **PCB Board Layout**

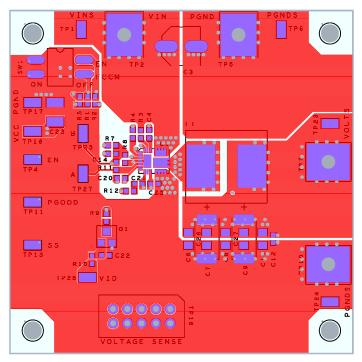

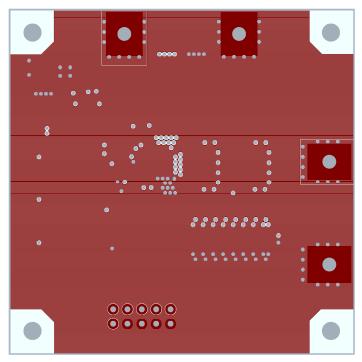

Fig. 4: Board Layout, Top Layer

Fig. 5: Board Layout, Bottom Layer

## **PCB Board Layout**

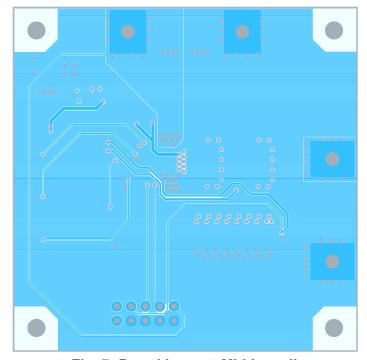

Fig. 6: Board Layout, Mid-layer I

Fig. 7: Board Layout, Mid-layer II

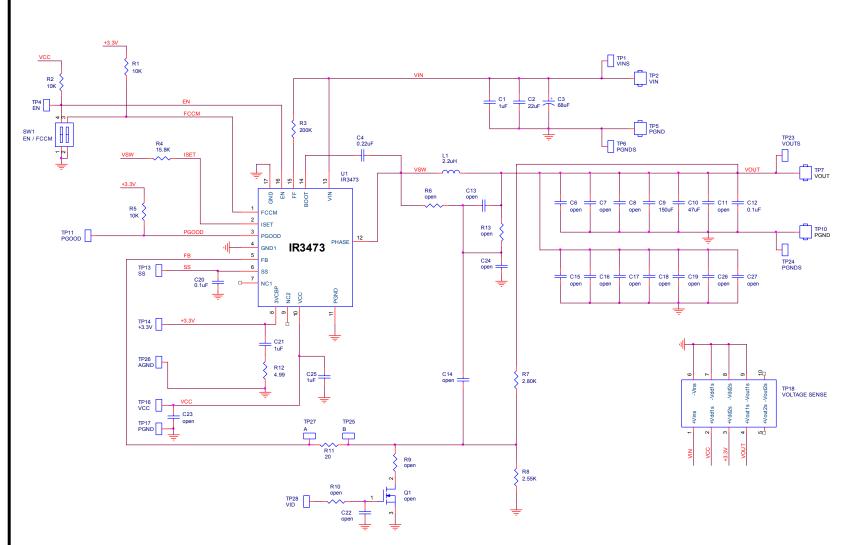

Fig. 8: Schematic of the IRDC3473 Evaluation Board

## **Bill of Materials**

| QTY | REF DESIGNATOR | VALUE   | DESCRIPTION                                         | MANUFACTURER   | PART NUMBER        |

|-----|----------------|---------|-----------------------------------------------------|----------------|--------------------|

| 3   | C1, C21, C25   | 1.00uF  | capacitor, X7R, 1.00uF, 25V, 0.1, 0603              | Murata         | GRM188R71E105KA12D |

| 1   | C10            | 47uF    | capacitor, 47uF, 6.3V, 805                          | TDK            | C2012X5R0J476M     |

| 2   | C12, C20       | 0.100uF | capacitor, X7R, 0.100uF, 25V, 0.1, 603              | TDK            | C1608X7R1E104K     |

| 1   | C2             | 22.0uF  | capacitor, X5R, 22.0uF, 16V, 20%, 1206              | Taiyo Yuden    | EMK316BJ226ML-T    |

| 1   | C3             | 68uF    | capacitor, electrolytic, 68uF, 25V, 0.2, SMD        | Panasonic      | EEV-FK1E680P       |

| 1   | C4             | 0.22uF  | capacitor, X5R, 0.22uF, 10V, 0.1, 0603              | TDK            | C1608X5R1A224K     |

| 1   | C9             | 150uF   | capacitor, tantalum polymer, 150uF, 6.3V, 20%, 7343 | Sanyo          | 6TPC150M           |

| 1   | L1             | 2.2uH   | inductor, ferrite, 2.2uH, 8.0A, 11.2mOhm, SMT       | Cyntec         | PCMB065T-2R2MS     |

| 1   | R4             | 15.8K   | resistor, thick film, 15.8K, 1/10W, 0.01, 603       | KOA            | RK73H1JLTD1582F    |

| 3   | R1, R2, R5     | 10.0K   | resistor, thick film, 10.0K, 1/10W, 0.01, 0603      | KOA            | RK73H1J1002F       |

| 1   | R11            | 20      | resistor, thick film, 20, 1/10W, 0.01, 603          | KOA            | RK73H1JLTD20R0F    |

| 1   | R12            | 4.99    | resistor, thick film, 4.99, 1/8W, 0.01, 603         | KOA            | RK73H1J4R99F       |

| 1   | R3             | 200K    | resistor, thick film, 200K, 1/10W, 0.01, 603        | KOA            | RK73H1JLTD2003F    |

| 1   | R7             | 2.80K   | resistor, thick film, 2.80K, 1/10W, 0.01, 603       | KOA            | RK73H1JLTD2801F    |

| 1   | R8             | 2.55K   | resistor, thick film, 2.55K, 1/10W, 0.01, 0603      | KOA            | RK73H1J2551F       |

| 1   | SW1            | SPST    | switch, DIP, SPST, 2 position, SMT                  | C&K Components | SD02H0SK           |

| 1   | U1             | IR3473  | 4mm X 5mm QFN                                       | IRF            | IR3473MTRPBF       |

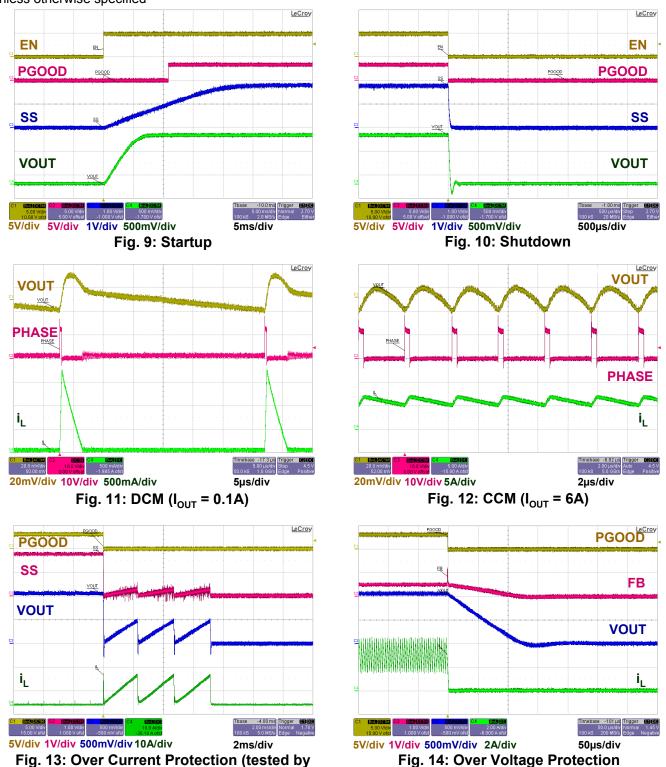

## **TYPICAL OPERATING WAVEFORMS**

Tested with demoboard shown in Fig. 8, VIN = 12V, VCC = 5V, VOUT = 1.05V, Fs = 300kHz,  $T_A = 25^{\circ}C$ , no airflow, unless otherwise specified

(tested by shorting FB to VOUT)

shorting VOUT to PGND)

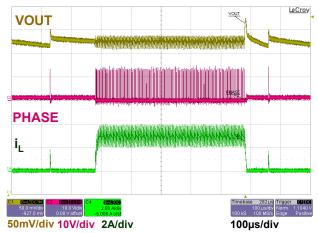

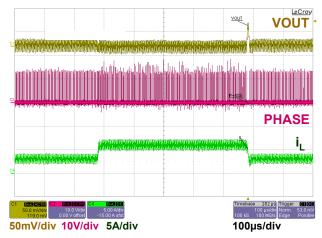

## **TYPICAL OPERATING WAVEFORMS**

Tested with demoboard shown in Fig. 8, VIN = 12V, VCC = 5V, VOUT = 1.05V, Fs = 300kHz,  $T_A = 25^{\circ}C$ , no airflow, unless otherwise specified

Fig. 15: Load Transient 0-3A

Fig. 16: Load Transient 3-6A

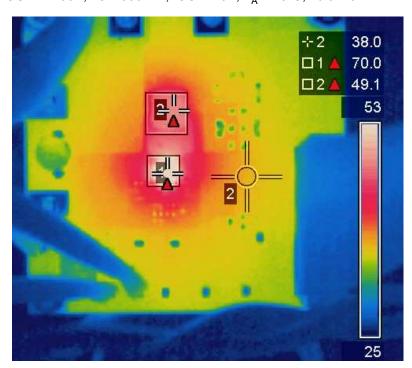

### **TYPICAL PERFORMANCE**

VIN = 12V, VCC = 5V, VOUT = 1.05V, Fs = 300kHz, IOUT = 6A,  $T_A = 25$ °C, no airflow

Fig. 17: Thermal Image (IR3473: 70°C, Inductor: 49°C, PCB: 38°C)

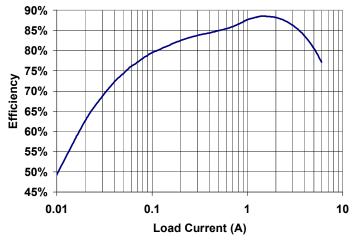

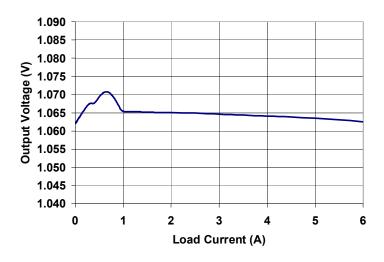

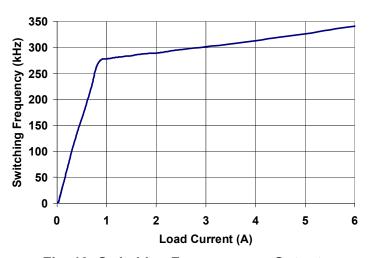

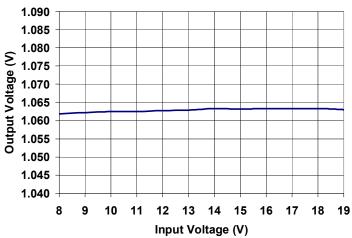

## **TYPICAL OPERATING DATA**

VIN = 12V, VCC = 5V, VOUT = 1.05V, Fs = 300kHz, IOUT = 0  $\sim$  6A, T<sub>A</sub> = 25°C, no airflow, unless otherwise specified

Fig. 18: Efficiency vs. Output Current

Fig. 20: Load Regulation

Fig. 19: Switching Frequency vs. Output Current

Fig. 21: Line Regulation at 6A Load

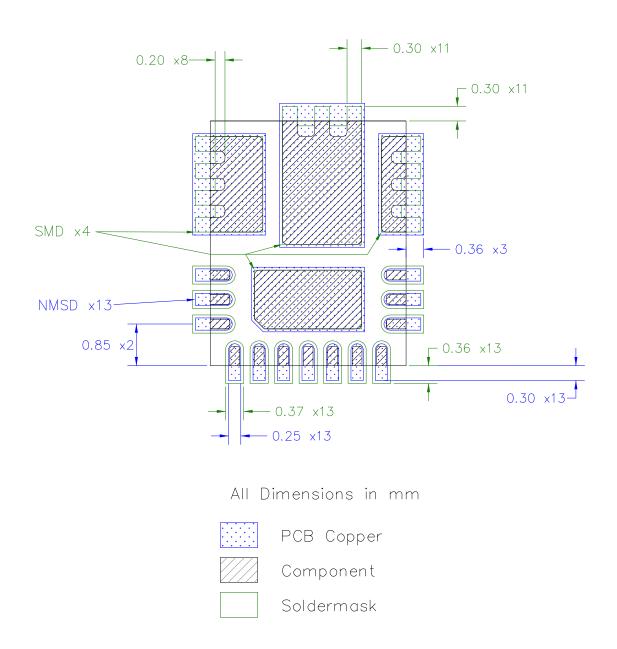

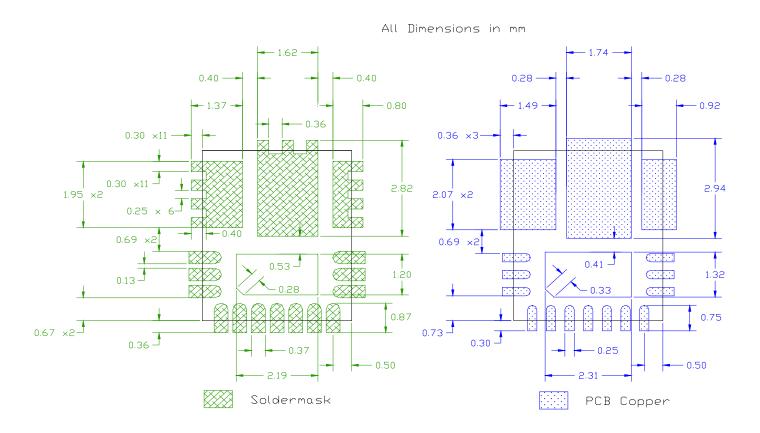

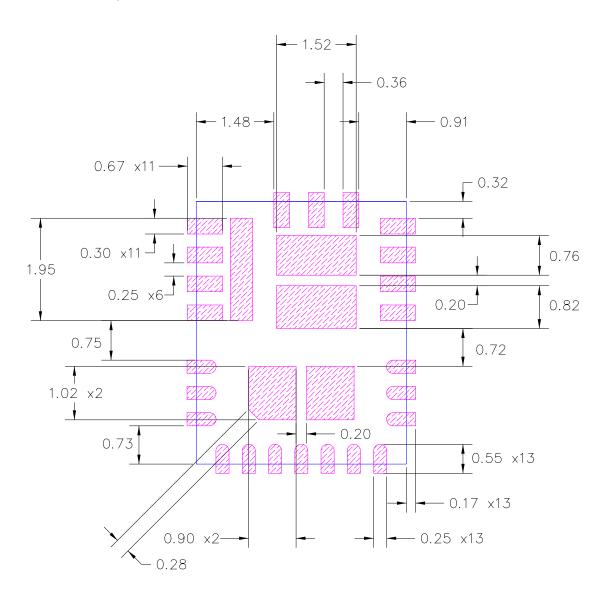

### **PCB Metal and Components Placement**

Lead lands (the 13 IC pins) width should be equal to nominal part lead width. The minimum lead to lead spacing should be  $\geq 0.2$ mm to minimize shorting.

Lead land length should be equal to maximum part lead length + 0.3 mm outboard extension. The outboard extension ensures a large toe fillet that can be easily inspected.

Pad lands (the 4 big pads) length and width should be equal to maximum part pad length and width. However, the minimum metal to metal spacing should be no less than 0.17mm for 2 oz. Copper, or no less than 0.1mm for 1 oz. Copper, or no less than 0.23mm for 3 oz. Copper.

### **Solder Resist**

It is recommended that the lead lands are Non Solder Mask Defined (NSMD). The solder resist should be pulled away from the metal lead lands by a minimum of 0.025mm to ensure NSMD pads.

The land pad should be Solder Mask Defined (SMD), with a minimum overlap of the solder resist onto the copper of 0.05mm to accommodate solder resist misalignment.

Ensure that the solder resist in between the lead lands and the pad land is  $\geq 0.15$ mm due to the high aspect ratio of the solder resist strip separating the lead lands from the pad land.

### **Stencil Design**

The Stencil apertures for the lead lands should be approximately 80% of the area of the lead lads. Reducing the amount of solder deposited will minimize the occurrences of lead shorts. If too much solder is deposited on the center pad, the part will float and the lead lands will open.

The maximum length and width of the land pad stencil aperture should be equal to the solder resist opening minus an annular 0.2mm pull back in order to decrease the risk of shorting the center land to the lead lands when the part is pushed into the solder paste.

Stencil Aperture

All Dimensions in mm

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information

Data and specifications subject to change without notice. 02/2011