# SEMICONDUCTOR TECHNICAL DATA

# **KIC6971F/MF**

**Analog CMOS Integrated Circuits**

#### 1.5A 2-Channel Current Limited Power Switch

The KIC6971F/MF is integrated power switches optimized for USB and other hot-swap applications.

The family of devices complies with USB 2.0 and is available with high polarity of Enable input. They offer current and thermal limiting and short circuit protection as well as controlled rise time and under-voltage lockout functionality.

#### **Features**

- ☐ Single USB Port Power Switches with discharge

- $\square$  Operating input voltage range 2.7V to 5.5V

- □Up to 1.5A Maximum Load Current

- □ Internal Short Circuit Current Limiting(2.1A)

- ☐ Reverse Current Blocking

- □ Fault report with blanking time(7ms)

- □90mΩ Power MOSFET

#### Maximum Ratings (Ta=25 °C)

| CHARACTERISTIC                            | SYMBOL           | RATING    | UNIT       |  |

|-------------------------------------------|------------------|-----------|------------|--|

| Input Voltage                             | V <sub>IN</sub>  | 6.5       | V          |  |

| Output Voltage                            | V <sub>OUT</sub> | 6.5       | V          |  |

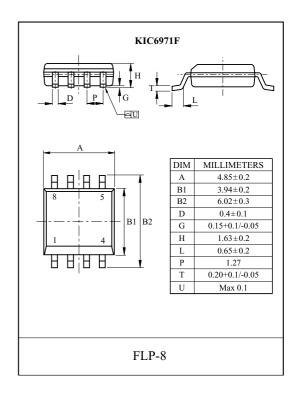

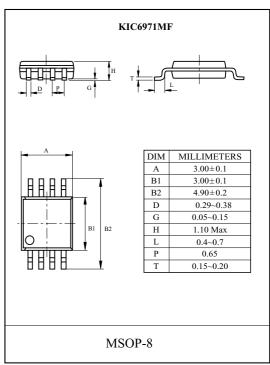

| Thermal Resistance<br>Junction-to-Ambient | FLP              | 129       | ℃/W        |  |

|                                           | MSOP             | 132       |            |  |

| Operating Junction Temperature            | Tj               | -40~125   | $^{\circ}$ |  |

| Storage Temperature                       | $T_{stg}$        | -55 ~ 150 |            |  |

Note) Device mounted on FR-4 substrate 2Layer PCB.

#### **Recommended Operating Conditions**

| CHARACTERISTIC | SYMBOL           | MIN | MAX | UNIT |

|----------------|------------------|-----|-----|------|

| Input Voltage  | V <sub>IN</sub>  | 2.7 | 5.5 | V    |

| Output Current | I <sub>OUT</sub> | 0   | 1.5 | A    |

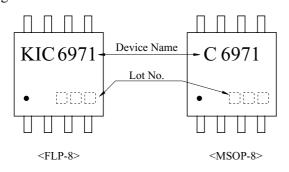

#### Marking

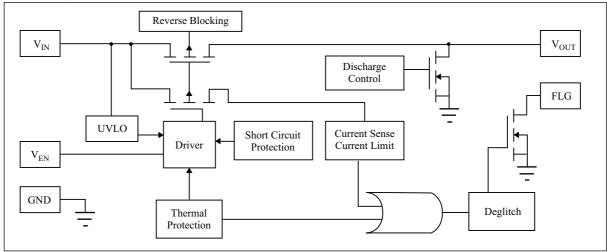

#### **Block Diagram**

The two current limit power switchs are the same function and Each channel is as below.

#### **Pin Descriptions**

| Pin Name            | Pin Number | Descriptions                                                          |  |

|---------------------|------------|-----------------------------------------------------------------------|--|

| GND                 | 1          | Ground                                                                |  |

| $V_{ m IN}$         | 2          | Voltage input pin                                                     |  |

| V <sub>EN1</sub>    | 3          | S/W 1 Enable input (active high)                                      |  |

| V <sub>EN2</sub>    | 4          | S/W 2 Enable input (active high)                                      |  |

| $V_{\mathrm{FLG2}}$ | 5          | S/W 2 Over-current and over-temperature fault report pin (Open drain) |  |

| V <sub>OUT1</sub>   | 6          | S/W 2 Voltage output pin                                              |  |

| $V_{\mathrm{OUT2}}$ | 7          | S/W 1 Voltage output pin                                              |  |

| V <sub>FLG1</sub>   | 8          | S/W 1 Over-current and over temperature fault report pin (Open drain) |  |

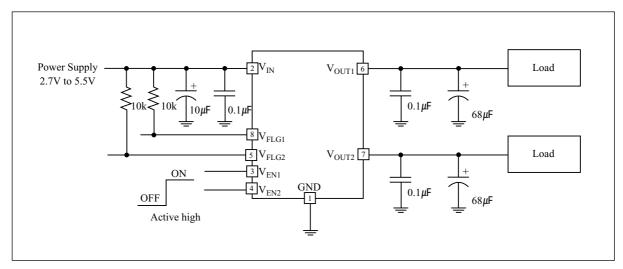

#### **Typical Application Circuit**

# $\textbf{ELECTRICAL CHARACTERISTICS} \ (V_{IN} = 5V, \ Ta = 25\,^{\circ}\text{C} \ , \ Unless \ otherwise \ stated)$

| CHARACTERISTIC                     | Symbol              | Test Conditions                                                                          | Min | Тур  | Max | Units              |

|------------------------------------|---------------------|------------------------------------------------------------------------------------------|-----|------|-----|--------------------|

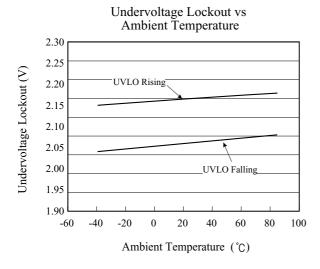

| Input UVLO                         | V                   |                                                                                          | 2.0 | 2.2  | 2.4 | V                  |

| Hysteresis                         | $V_{UVLO}$          |                                                                                          | 50  | 100  | 150 | mV                 |

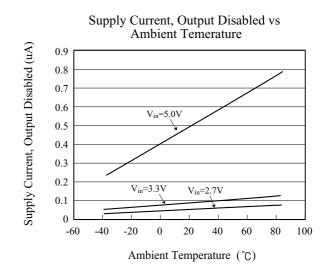

| Input Shutdown Current             | $I_{SHDN}$          | Disabled, I <sub>OUT</sub> = 0                                                           | 0.2 | 0.5  | 1   | μA                 |

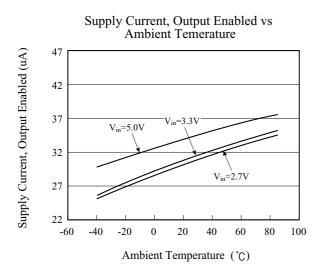

| Input Quiescent Current            | $I_Q$               | Enabled, I <sub>OUT</sub> = 0                                                            | 20  | 45   | 70  | μA                 |

| Input Leakage Current              | $I_{LEAK}$          | Disabled, V <sub>OUT</sub> grounded                                                      | -   | 0.1  | 1   | μA                 |

| Reverse Leakage Current            | $I_{REV}$           | Disabled, $V_{IN} = 0V$ , $V_{OUT} = 5V$ , $I_{REV}$ at $V_{IN}$                         | -   | 0.1  | 1   | μA                 |

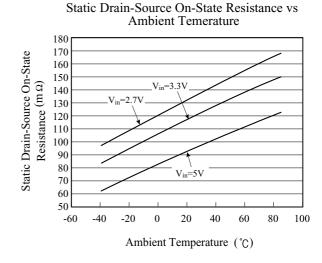

| Switch on-resistance               | $R_{DS(ON)}$        | $V_{IN} = 5V$ , $I_{OUT} = 1.5A$ , $TA = 25$ °C                                          | 70  | 90   | 115 | $\mathbf{m}\Omega$ |

| Switch on-resistance               | K <sub>DS(ON)</sub> | $V_{IN} = 5V$ , $I_{OUT} = 1.5A$ , $-40 ^{\circ}\text{C} \le TA \le 85 ^{\circ}\text{C}$ | -   | -    | 140 | mΩ                 |

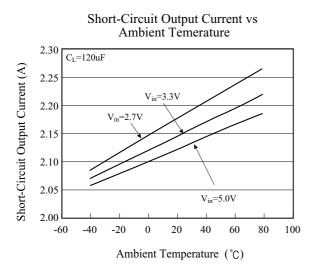

| Short-Circuit Current Limit        | $I_{LIMIT}$         | $V_{IN} = 5V, V_{OUT} = 4V, C_L = 120 \mu F, -40 \degree C \Box TA \Box 85 \degree C$    | 1.6 | 2.1  | 2.6 | A                  |

| Current limiting trigger threshold | $I_{Trig}$          | Output Current Slew rate(<100A/s), C <sub>L</sub> =120µF                                 | -   | 2.6  | -   | A                  |

| EN Input Logic Low Voltagve        | $V_{IL}$            | V <sub>IN</sub> = 2.7V to 5.5V                                                           | -   | -    | 0.8 | V                  |

| EN Input Logic High Voltagve       | $V_{\mathrm{IH}}$   | V <sub>IN</sub> = 2.7V to 5.5V                                                           | 2   | -    | -   | V                  |

| EN Input leakage                   | I <sub>SINK</sub>   | V <sub>EN</sub> =5V                                                                      | -   | -    | 1   | μA                 |

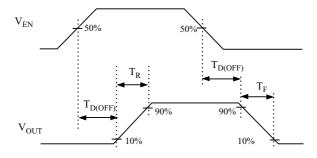

| Output turn-on delay time          | T <sub>D(on)</sub>  | $C_L=1\mu F$ , Rload= $10\Omega$                                                         | -   | 0.05 | 0.1 | ms                 |

| Output turn-off delay time         | $T_{D(off)}$        | $C_L=1\mu F$ , Rload= $10\Omega$                                                         | -   | 0.05 | 0.1 | ms                 |

| Output turn-on rise time           | $T_R$               | $C_L=1\mu F$ , Rload= $10\Omega$                                                         | -   | 0.6  | 1.5 | ms                 |

| Output turn-on fall time           | $T_{\mathrm{F}}$    | $C_L=1\mu F$ , Rload= $10\Omega$                                                         | -   | 0.2  | 0.4 | ms                 |

| Discharge time                     | $T_{ m DIS}$        | $C_L$ =120 $\mu$ F, Rload=10 $\Omega$<br>disabled to $V_{OUT} < 0.5V$                    | 1   | 3    | 6   | ms                 |

| FLG blanking time                  | $T_{Blank}$         | $C_{IN} = 10 \mu F, C_L = 22 \mu F$                                                      | 4   | 7    | 15  | ms                 |

| Thermal Shutdown Threshold         | $T_{SHDN}$          | Enabled, Rload = 1kΩ                                                                     | 130 | 150  | 170 | $^{\circ}$         |

| Thermal Shutdown Hysteresis        | $T_{HYS}$           | Disabled, V <sub>OUT</sub> grounded                                                      | -   | 25   | -   | $^{\circ}$         |

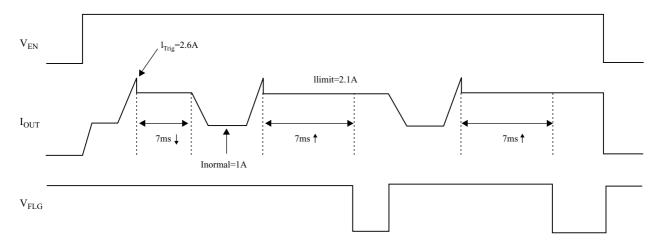

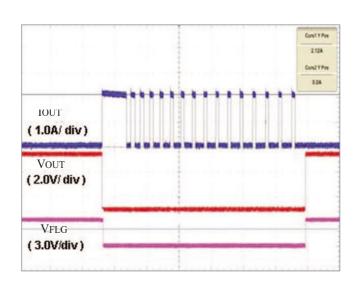

[Figure 1. Over Current Protection on Power Switch]

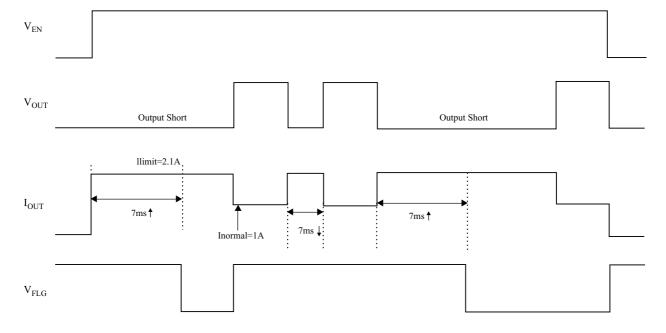

[Figure 2. Short Circuit Protection on Power Switch]

[Figure 3. delay Time]

# [Over Load]

# IOUT (1.0A/div) VOUT (2.0V/div) VFLG (3.0V/div)

200ms/div

#### [Short Circuit]

200ms/div

#### **\* FLG Response Condition**

|               | Condition                           | FLG      | Remark |

|---------------|-------------------------------------|----------|--------|

| Over - Load   | $V_{IN}$ - $V_{OUT}$ $\square 1.0V$ | Active L |        |

| Short Circuit | $V_{OUT} = 0$                       | Active L |        |

#### Typical Characteristics (Continued)

#### **Functional Description**

#### 1. Over-current and Short Circuit Protection

An internal sensing FET is employed to check for over-current conditions. Unlike current-sense resistors, sense FETs do not increase the series resistance of the current path. When an over-current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Complete shutdown occurs only if the fault stays long enough to activate thermal limiting.

#### 2. Thermal Protection

Thermal protection prevents the IC from damage when the die temperature exceeds safe margins. This mainly occurs when heavy-overload or short-circuit faults are present for extended periods of time. The KIC6981F/MF implements a thermal sensing to monitor the operating junction temperature of the power distribution switch. Once the die temperature rises to approximately 150°C, the Thermal protection feature gets activated as follows: The internal thermal sense circuitry turns the power switch off and the FLG output is asserted thus preventing the power switch from damage. Hysteresis in the thermal sense circuit allows the device to cool down to approximately 25°C before the output is turned back on. This built-in thermal hysteresis feature is an excellent feature, as it avoids undesirable oscillations of the thermal protection circuit. The switch continues to cycle in this manner until the load fault is removed, resulting in a pulsed output. The FLG open-drain output is asserted when an over-current occurs with 7-ms deglitch.

#### 3. Under-Voltage Lockout (UVLO)

Under-voltage lockout function (UVLO) guarantees that the internal power switch is initially off during start-up. The UVLO functions only when the switch is enabled. Even if the switch is enabled, the switch is not turned ON until the power supply has reached at least 2.2V. Whenever the input voltage falls below approximately 2.2V, the power switch is turned off. This facilitates the design of hot-insertion systems where it is not possible to turn off the power switch before input power is removed.

#### 4. Reverse Current Protection

In a normal MOSFET switch, current can flow in reverse direction (from the output side to the input side) when the output side voltage is higher than the input side, even when the switch is turned off. A reverse-current blocking feature is implemented in the KIC6981F/MF to prevent such back currents. This circuit is activated by the difference between the output voltage and the input voltage. When the switch is disabled, this feature blocks reverse current flow from the output back to the input.

#### 5. Discharge Function

When enable is de-asserted, the discharge function is active. The output capacitor is discharged through an internal NMOS that has a discharge resistance of  $100\Omega$ . Hence, the output voltage drops down to zero. The time taken for discharge is dependent on the RC time constant of the resistance and the output capacitor.

#### 6. FLG Response

The FLG open-drain output goes active low for any of the two conditions: Over-Current or Over-Temperature. The time from when a fault condition is encountered to when the FLG output goes low is 7-ms (TYP). The FLG output remains low until both over-current and over-temperature conditions are removed. Connecting a heavy capacitive load to the output of the device can cause a momentary Over-current condition, which does not trigger the FLG due to the 7-ms deglitch timeout. The KIC6981F/MF is designed to eliminate erroneous Over-current reporting without the need for external components, such as an RC delay network.

#### **Applications Information**

#### 1. Supply Filtering

A 0.01 uF to  $0.1 \mu F$  bypass capacitor from IN to GND, located near the KIC6981F/MF, is strongly recommended to control supply transients. Without a bypass capacitor, an output short may cause sufficient ringing on the input (from supply lead inductance) to damage internal control circuitry. Input transients must not exceed the absolute maximum supply voltage (VIN max = 6.5 V) even for a short duration.

#### 2.EN, the Enable Input

EN must be driven logic high for a clearly defined input. Floating the input may cause unpredictable operation. EN should not be allowed to go negative with respect to GND.