# **Brief Description**

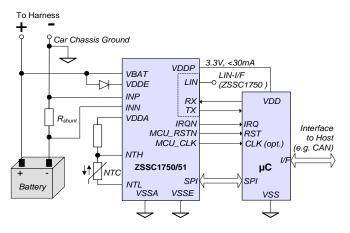

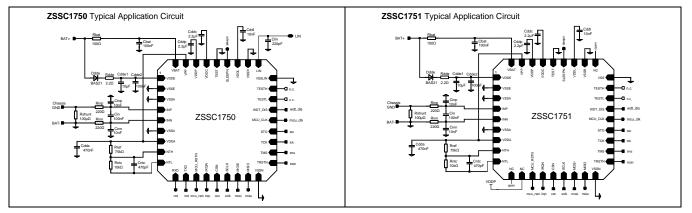

The ZSSC1750 and ZSSC1751 are System Basis Chips (SBCs) with a dual-channel ADC for battery sensing/management in automotive, industrial, and medical systems. The ZSSC1750 and ZSSC1751 feature an SPI interface; in addition, the ZSSC1750 has an integrated LIN 2.1 transceiver.

One of the two input channels measures the battery current  $I_{BAT}$  via the voltage drop at the external shunt resistor. The second channel measures the battery voltage  $V_{BAT}$  and the temperature.

By simultaneously measuring  $V_{BAT}$  and  $I_{BAT}$ , it is possible to determine dynamically the internal resistance of the battery, Rdi, which is correlated with the state-of-health (SOH) of the battery. By integrating  $I_{BAT}$ , it is possible to determine the stateof-charge (SOC) and the state-of-function (SOF) of the battery.

During Sleep Mode, the system makes periodic measurements to monitor the discharge of the battery. Measurement cycles are controlled by user software and include various wake-up conditions. The ZSSC1750/51 is optimized for ultra-low power consumption drawing only 60µA or less in this mode.

## Features

- Two high-precision 24-bit sigma-delta ADCs (18-bit with no missing codes); sample rate: 1Hz to 16kHz

- On-chip voltage reference (5ppm/K typical)

- Current channel

- I<sub>BAT</sub> offset error: ≤ 10mA

- I<sub>BAT</sub> resolution: ≤ 1mA

- Programmable gain: 4 to 512

- Max. differential input stage input range: ±300mV

- Voltage channel

- Input range: 4 to 28.8V

- Voltage accuracy: ±60ppm FSR\* = 1.73mV

- Temperature channel

- External temperature sensor (NTC)

- Factory-calibrated internal temp. sensor: ±2°C

- LIN 2.1/SAE J2602-1 transceiver (ZSSC1750 only)

- Typical current consumption

- Normal Mode: 12mA

- Sleep Mode: ≤ 60µA

# **Benefits**

- Integrated, precision measurement solution for accurate prediction of battery state of health (SOH), state of charge (SOC), or state of function (SOF)

- Robust power-on-reset (POR) concept for harsh automotive environments

- On-chip precision oscillator accuracy: ±1%

- On-chip low-power oscillator

- Only a few external components needed

- Easy communication via SPI interface

- Power supply, interrupt, and reset signals for external microcontroller

- Watchdog timer with dedicated oscillator

- Industry's smallest footprint allows minimal module size and cost

- AEC-Q100 qualified solution

# **Available Support**

- Evaluation Kit

- Application Notes

## **Physical Characteristics**

- Operation temperature up to -40°C to +125°C

- Supply voltage: 4.2 to 18V

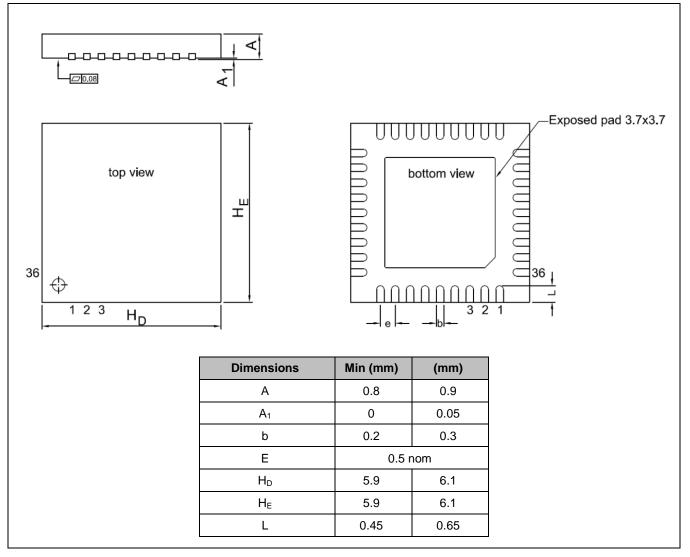

- Small footprint package: PQFN36 6x6 mm

- \* FSR = full-scale range.

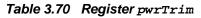

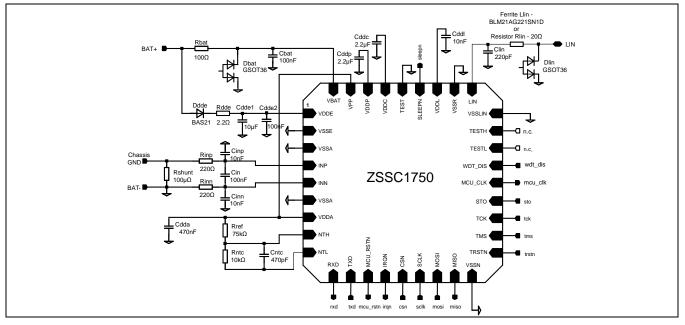

#### Basic ZSSC1750/51 Application Circuit

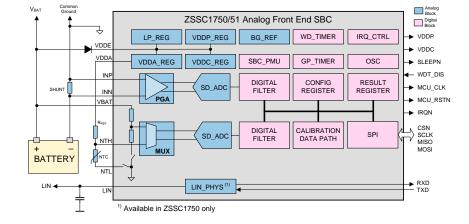

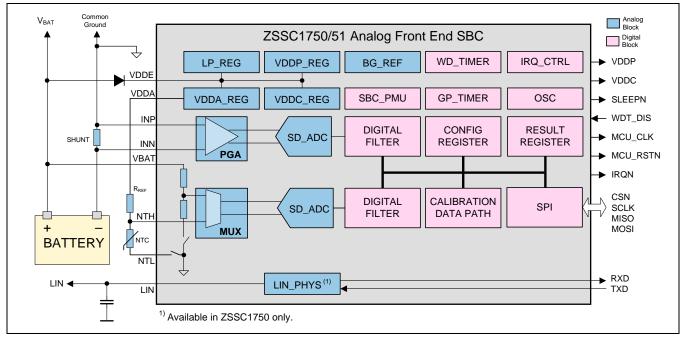

### ZSSC1750/51 Block Diagram

#### Applications

- Intelligent battery monitoring in automotive applications; start/stop systems, e-bikes, scooters, and e-carts

- Battery monitoring in Industrial, medical and photovoltaic applications;

- High precision data acquisition

#### **Ordering Information**

| Product Sales Code | Description                                                                                                                                                                                   | Package             |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| ZSSC1750EA3R       | ZSSC1750 Battery Sensing SBC—Temperature Range: -40°C to 125°C                                                                                                                                | PQFN36 6x6 mm, reel |  |  |

| ZSSC1751EA3R       | ZSSC1751 Battery Sensing SBC—Temperature Range: -40°C to 125°C                                                                                                                                | PQFN36 6x6 mm, reel |  |  |

| ZSSC1750KIT V1.1   | 7.1 ZSSC1750/51 Evaluation Kit: modular evaluation and development board for ZSSC1750/51, 3 IC samples, and USB cable (software and documentation can be downloaded from <u>www.IDT.com</u> ) |                     |  |  |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com

Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

#### Tech Support

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <u>www.idt.com/go/glossary</u>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

# Contents

| 1 | IC ( | Char   | acteristics                                                                  | 8    |

|---|------|--------|------------------------------------------------------------------------------|------|

|   | 1.1  | Abs    | olute Maximum Ratings                                                        | 8    |

|   | 1.2  | Rec    | commended Operating Conditions                                               | 9    |

|   | 1.3  | Eleo   | ctrical Parameters                                                           | . 10 |

|   | 1.4  | Tim    | ing Parameters                                                               | . 18 |

| 2 | Cire | cuit E | Description                                                                  | . 21 |

|   | 2.1  | Ove    | erview                                                                       | . 21 |

|   | 2.2  | SBC    | C-to-MCU Interface Pins                                                      | . 22 |

|   | 2.2  | 2.1    | Digital I/Os                                                                 | . 23 |

|   | 2.2  | 2.2    | External Microcontroller (MCU) Supply Pins                                   | . 23 |

|   | 2.2  | 2.3    | SLEEPN Power State Indicator Pin                                             | . 23 |

|   | 2.3  | Sys    | tem Power States                                                             | . 24 |

|   | 2.3  | 3.1    | Full Power State (FP)                                                        | . 24 |

|   | 2.3  | 3.2    | Low Power State (LP)                                                         |      |

|   | 2.3  | 3.3    | Ultra Low Power State (ULP)                                                  | . 25 |

|   | 2.3  | 3.4    | OFF Power State                                                              | . 25 |

| 3 | ZS   | SC17   | 750/51 Functional Block Descriptions                                         | . 26 |

|   | 3.1  | Ser    | ial Peripheral Interface (SPI Slave)                                         | . 26 |

|   | 3.1  | 1.1    | SPI Protocol                                                                 | . 26 |

|   | 3.2  | SBC    | C Register Map (RESULT REGISTER Block and CONFIG REGISTER Block)             | . 28 |

|   | 3.3  | ZSS    | SC1750/51 Clock and Reset Logic                                              | . 33 |

|   | 3.3  | 3.1    | Clock Sources                                                                |      |

|   | 3.3  | 3.2    | Trimming the Low-Power Oscillator                                            | . 34 |

|   | 3.3  | 3.3    | Clock Trimming and Configuration Registers                                   | . 35 |

|   | 3.3  |        | Resets                                                                       |      |

|   | 3.4  | SBC    | C Watchdog Timer (WD_TIMER Block)                                            | . 39 |

|   | 3.4  | 4.1    | Watchdog Registers                                                           |      |

|   | 3.5  | SBC    | C Sleep Timer (GP_TIMER Block)                                               | . 43 |

|   | 3.5  |        | Sleep Timer Registers                                                        |      |

|   | 3.6  |        | C Interrupt Controller (IRQ_CTRL Block)                                      |      |

|   | 3.7  | SBC    | C Power Management Unit (SBC_PMU Block)                                      |      |

|   | 3.7  | 7.1    | FP State                                                                     |      |

|   | 3.7  | 7.2    | LP and ULP States                                                            |      |

|   | 3.7  | 7.3    | OFF State                                                                    |      |

|   | 3.7  |        | Registers for Power Configuration and the Discreet Current Measurement Count |      |

|   | 3.8  |        | SC1750/51 ADC Unit                                                           |      |

|   | 3.8  |        | ADC Clocks                                                                   |      |

|   | 3.8  |        | ADC Data Path                                                                |      |

|   | 3.8  |        | ADC Operating Modes and Result Registers                                     |      |

|   | 3.8  | 3.4    | ADC Control and Conversion Timing                                            | . 86 |

| 3.8.5     | Diagnostic Features                            |  |

|-----------|------------------------------------------------|--|

| 3.8.6     | Digital Features                               |  |

| 3.9 SE    | C LIN Support Logic (for ZSSC1750 only)        |  |

| 3.9.1     | LIN Wakeup Detection                           |  |

| 3.9.2     | TXD Timeout Detection                          |  |

| 3.9.3     | LIN Short Detection                            |  |

| 3.9.4     | LIN Testing                                    |  |

| 3.10 ZS   | SC1750/51 OTP (CONFIG REGISTER)                |  |

| 3.11 Mi   | scellaneous Registers                          |  |

| 3.12 Vo   | Itage Regulators                               |  |

| 3.12.1    | VDDE                                           |  |

| 3.12.2    | VBAT                                           |  |

| 3.12.3    | VDDA                                           |  |

| 3.12.4    | VDDL                                           |  |

| 3.12.5    | VDDP                                           |  |

| 3.12.6    | VDDC                                           |  |

| 4 ESD /   | EMC                                            |  |

| 4.1 Ele   | ectrostatic Discharge                          |  |

| 4.2 Po    | wer System Ripple Factor                       |  |

| 4.3 Ap    | plication Circuit Examples for EMC Conformance |  |

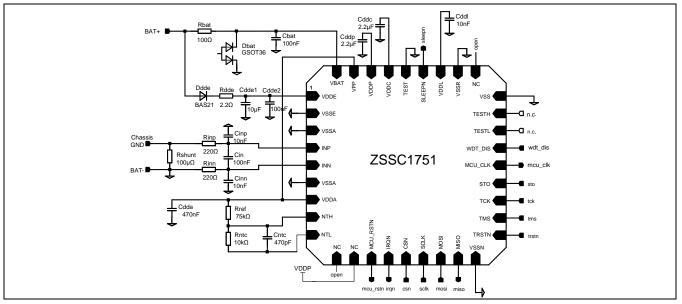

| 5 Pin Co  | nfiguration and Package                        |  |

| 6 Orderir | ng Information                                 |  |

| 7 Relate  | d Documents                                    |  |

| 8 Glossa  | ry                                             |  |

| 9 Docum   | ent Revision History                           |  |

# List of Figures

| Figure 1.1 | Measurement Method for Determining VDDP Pin Current Capability | 17 |

|------------|----------------------------------------------------------------|----|

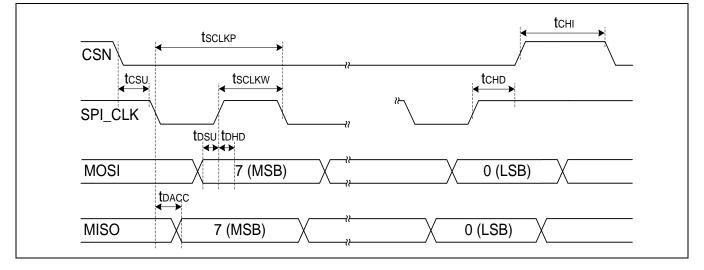

| Figure 1.2 | SPI Protocol Timing                                            | 19 |

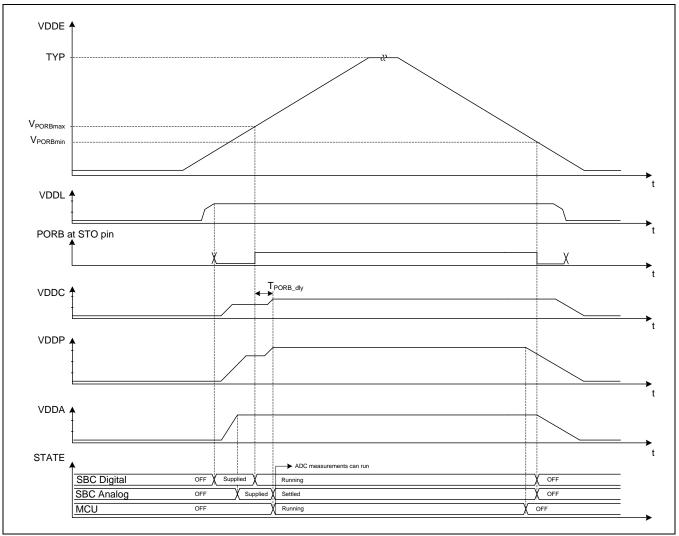

| Figure 1.3 | ZSSC1750/51 Power-Up and Power-Down Sequence                   | 20 |

| Figure 2.1 | Functional Block Diagram                                       | 21 |

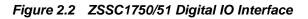

| Figure 2.2 | ZSSC1750/51 Digital IO Interface                               | 22 |

| Figure 2.3 | ZSSC1750/51 Power States                                       | 24 |

| Figure 3.1 | Read and Write Burst Access to the SBC                         | 27 |

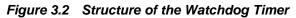

| Figure 3.2 | Structure of the Watchdog Timer                                | 39 |

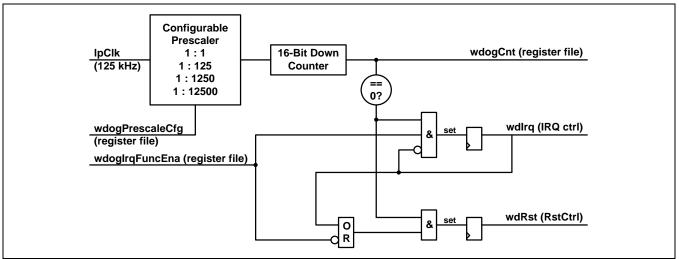

| Figure 3.3 | Structure of the Sleep Timer                                   | 43 |

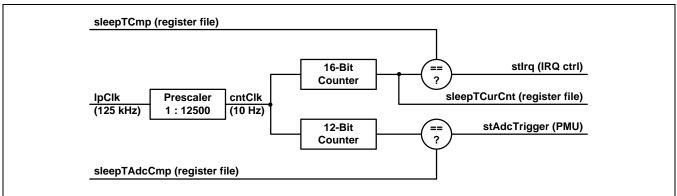

| Figure 3.4 | Generation of Interrupt and Wake-up                            | 46 |

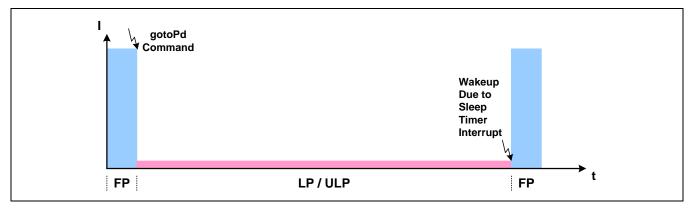

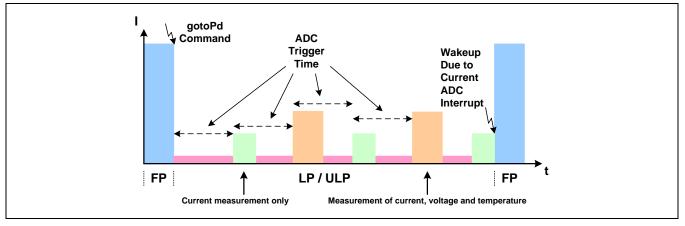

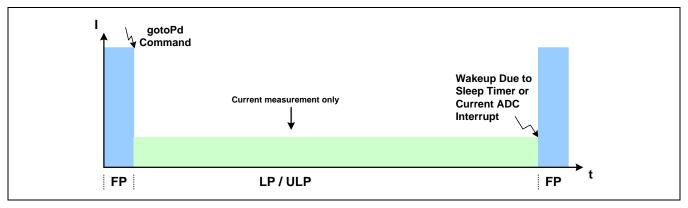

| Figure 3.5 | LP/ULP State without any Measurements                          | 52 |

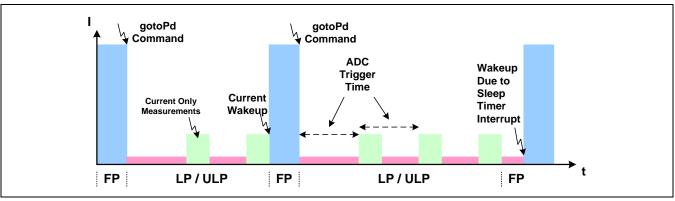

| Figure 3.6 | LP/ULP State Performing Only Current Measurements              | 54 |

# () IDT.

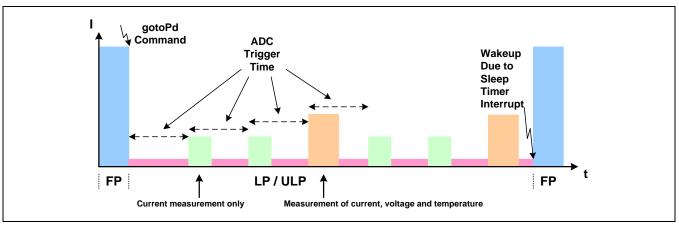

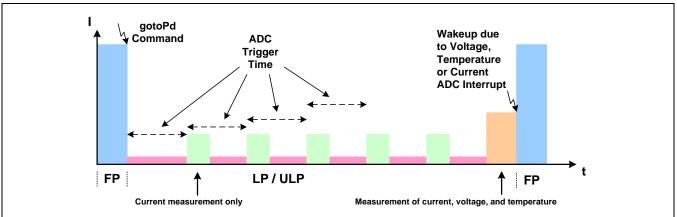

| Figure 3.7  | LP/ULP State Performing Current, Voltage, and Temperature Measurements<br>with discCvtCnt == 2                                            | FC  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

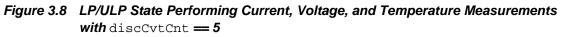

| Figure 3.8  | LP/ULP State Performing Current, Voltage, and Temperature Measurements                                                                    | 50  |

| Figure 3.6  | with discCvtCnt == 5                                                                                                                      | 56  |

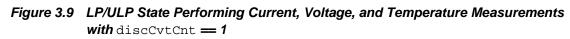

| Figure 3.9  | LP/ULP State Performing Current, Voltage, and Temperature Measurements                                                                    |     |

| 3           | with discCvtCnt == 1                                                                                                                      | 57  |

| Figure 3.10 | LP/ULP State Performing Continuous Current-Only Measurements                                                                              | 58  |

| Figure 3.11 | Performing Continuous Current and Voltage Measurements during LP/ULP State                                                                | 60  |

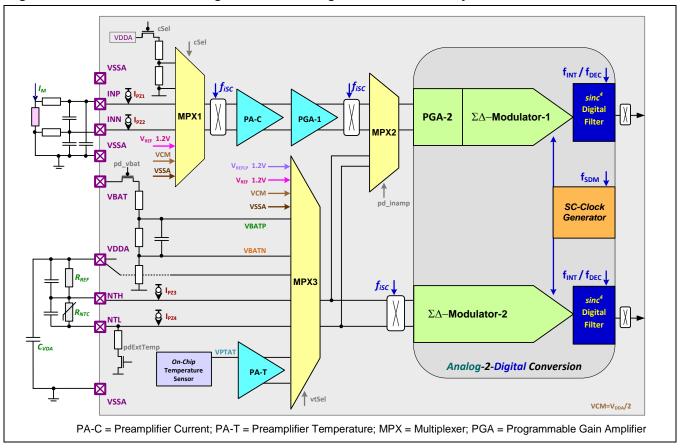

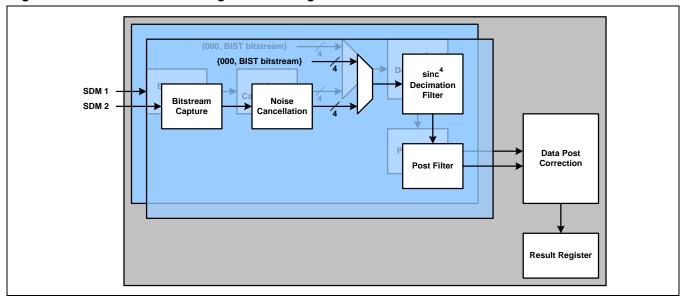

| Figure 3.12 | Functional Block Diagram of the Analog Measurement Subsystem                                                                              | 64  |

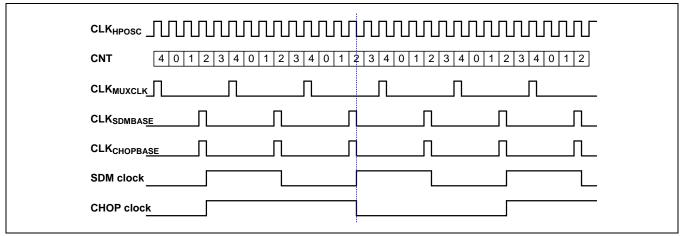

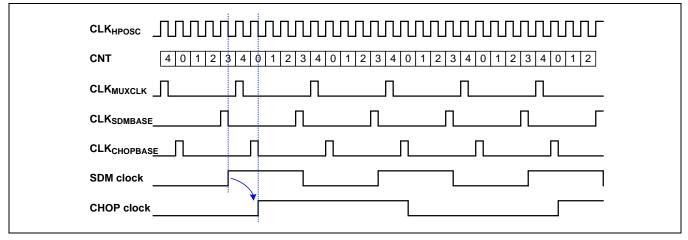

| Figure 3.13 | <pre>FP ADC Clocking Scheme for sdmPos = sdmPos2 = 2; sdmClkDivFp = 1;<br/>sdmChopClkDiv = 0</pre>                                        | 66  |

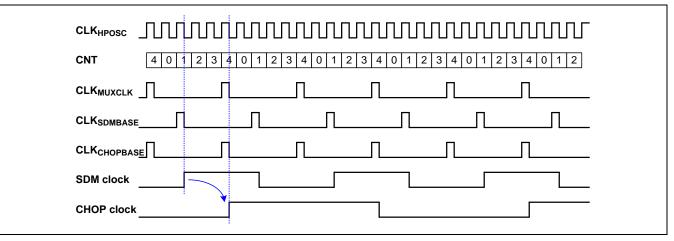

| Figure 3.14 | FP ADC Clocking for sdmPos = 1 and sdmPos2 = 4; sdmClkDivFp = 1; sdmChopClkDiv = 0.                                                       | 66  |

| Figure 3.15 | FP ADC Clocking for sdmPos = 3 and sdmPos2 = 0; sdmClkDivFp = 1; sdmChopClkDiv = 0.                                                       | 67  |

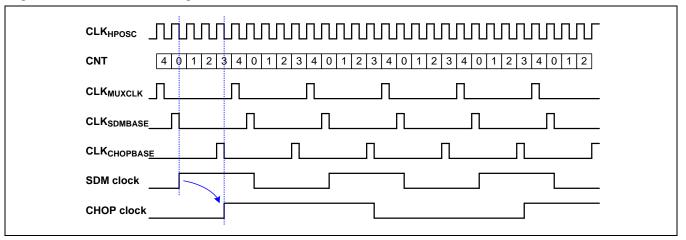

| -           | FP ADC Clocking for sdmPos = 0 and sdmPos2 = 3; sdmClkDivFp = 1; sdmChopClkDiv = 0.                                                       |     |

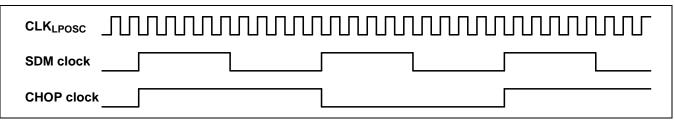

| -           | LP/ULP ADC Clocking Scheme; sdmClkDivLp = 5; sdmChopClkDiv = 0                                                                            |     |

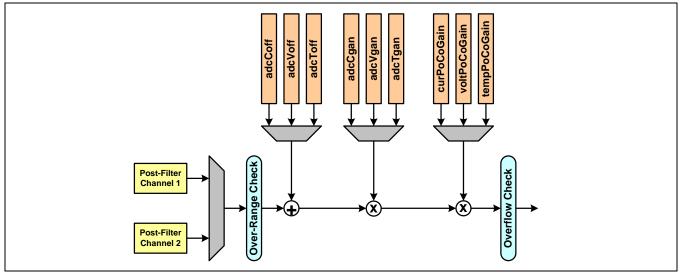

| -           | Functional Block Diagram of the Digital ADC Data Path                                                                                     |     |

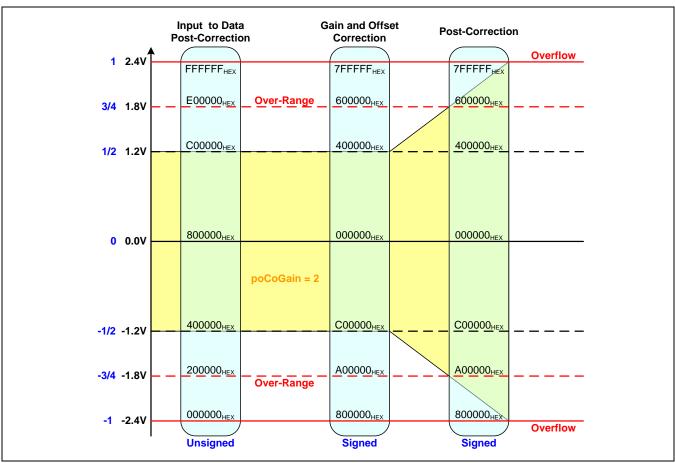

| -           | Data Post Correction                                                                                                                      |     |

| Figure 3.20 | Data Representation through Data Post Correction including Over-Range and Overflow Levels.                                                | 71  |

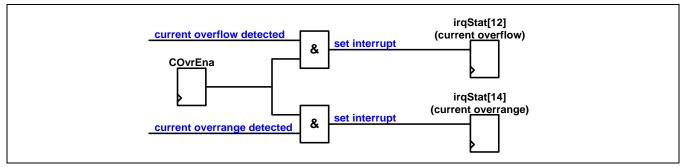

| Figure 3.21 | Common Enable for the "set overrange" and "set overflow" Interrupt Strobes for Current                                                    | 72  |

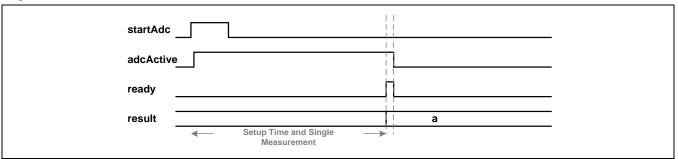

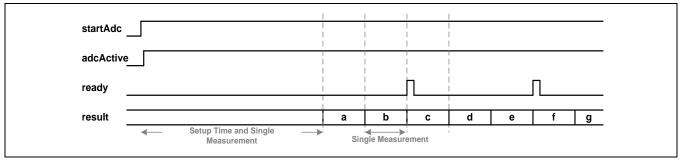

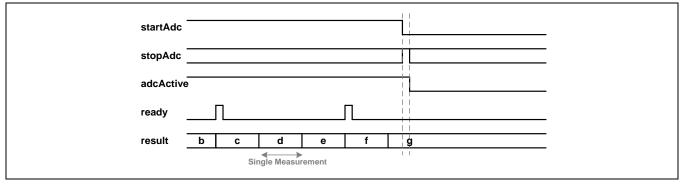

| Figure 3.22 | Individual SRCS                                                                                                                           | 87  |

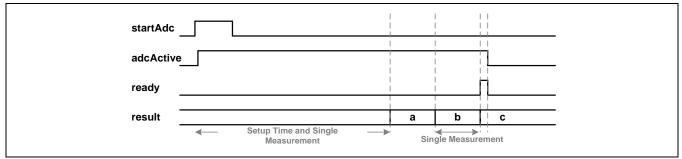

| Figure 3.23 | Individual MRCS (Example for Result Counter of 3)                                                                                         | 87  |

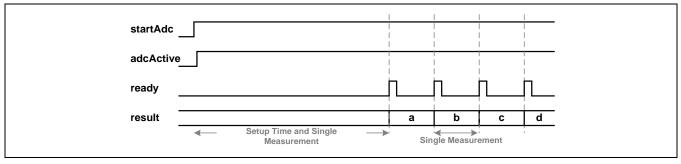

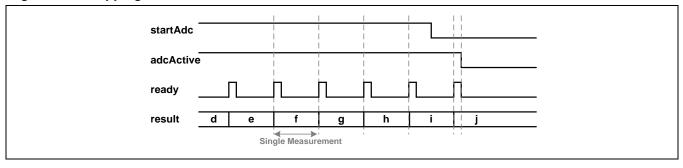

| Figure 3.24 | Continuous SRCS                                                                                                                           | 88  |

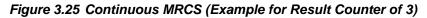

|             | Continuous MRCS (Example for Result Counter of 3)                                                                                         |     |

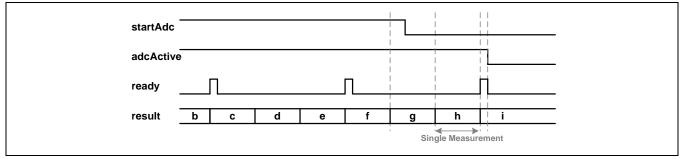

| Figure 3.26 | Stopping Continuous SRCS                                                                                                                  |     |

| Figure 3.27 |                                                                                                                                           |     |

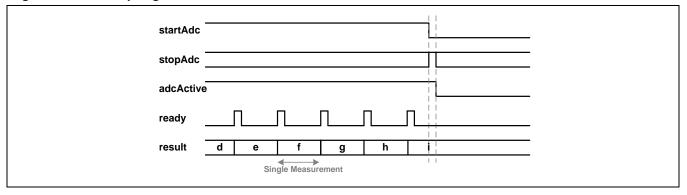

| Figure 3.28 | Interrupting a Continuous SRCS                                                                                                            |     |

| Figure 3.29 |                                                                                                                                           |     |

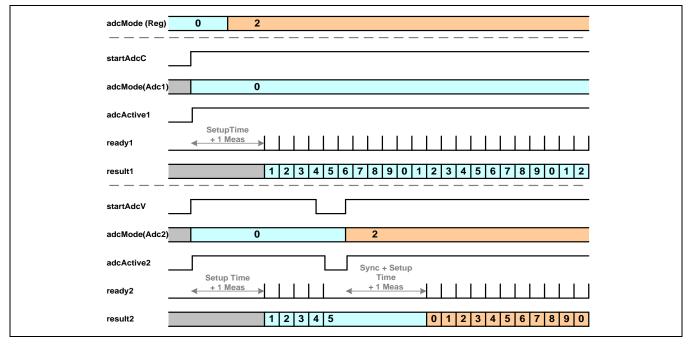

| -           | Signal Behavior of adcMode                                                                                                                | 91  |

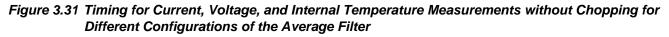

| Figure 3.31 | Timing for Current, Voltage, and Internal Temperature Measurements without Chopping for<br>Different Configurations of the Average Filter | 93  |

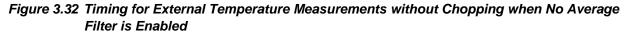

| Figure 3.32 | Timing for External Temperature Measurements without Chopping when No Average Filter is Enabled                                           | 94  |

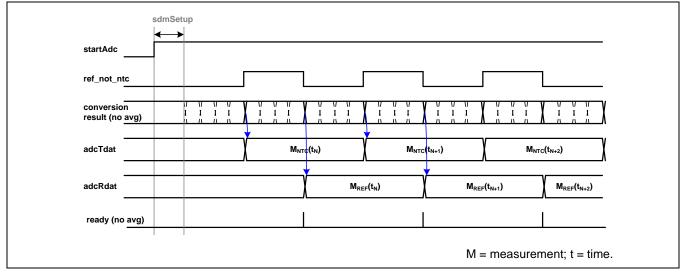

| Figure 3.33 | Timing for Current, Voltage, and Internal Temperature Measurements using Chopping                                                         | 95  |

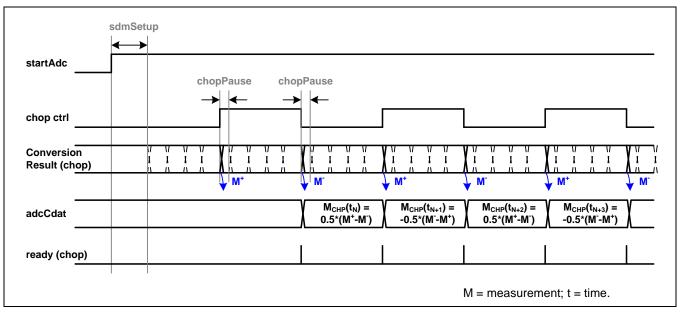

| Figure 3.34 | Timing for External Temperature Measurements using Chopping                                                                               | 96  |

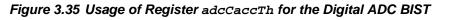

| Figure 3.35 | Usage of Register adcCaccTh for the Digital ADC BIST                                                                                      | 98  |

| Figure 3.36 | Bit Stream of ADC Interface Test at STO Pad                                                                                               | 99  |

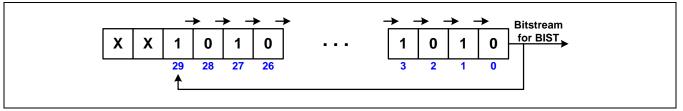

| Figure 3.37 | Protection Logic of the LIN TXD Line                                                                                                      | 100 |

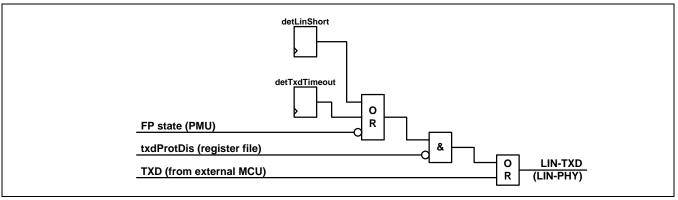

| Figure 3.38 | Waveform Showing the Gating Principle for Non-zero Values of linShortDelay                                                                | 101 |

| Figure 4.1  | Optional External Components for ZSSC1750                                                                                                 | 111 |

| Figure 4.2  | Optional External Components for ZSSC1751                                                                                                 | 111 |

| Figure 5.1  | ZSSC1750/51 PQFN36 6x6mm Package Pin-out (Top View)                                                                                       |     |

| Figure 5.2  | Package Drawing of the ZSSC1750/51                                                                                                        | 114 |

# List of Tables

| Table 1.1  | Absolute Maximum Ratings (referenced to VSSE)                                        | 8    |

|------------|--------------------------------------------------------------------------------------|------|

| Table 1.2  | Operating Conditions                                                                 | 9    |

| Table 1.3  | Electrical Specifications                                                            | . 10 |

| Table 1.4  | Timing Parameters                                                                    | . 18 |

| Table 3.1  | SBC Register Map                                                                     | . 28 |

| Table 3.2  | Register irefOsc                                                                     | . 35 |

| Table 3.3  | Register irefLpOsc                                                                   | . 35 |

| Table 3.4  | Register IpOscTrim                                                                   | . 36 |

| Table 3.5  | Register lpOscTrimCnt                                                                | . 36 |

| Table 3.6  | Register swRst                                                                       | . 38 |

| Table 3.7  | Register cmdExe                                                                      | . 38 |

| Table 3.8  | Register funcDis                                                                     | . 39 |

| Table 3.9  | Resolution and Maximum Timeout for Prescaler Configurations                          | . 40 |

| Table 3.10 | Register wdogPresetVal                                                               | . 41 |

| Table 3.11 | Register wdogCnt                                                                     | . 41 |

| Table 3.12 | Register wdogCfg                                                                     | . 42 |

| Table 3.13 | Register sleepTAdcCmp                                                                | . 44 |

| Table 3.14 | Register sleepTCmp                                                                   | . 45 |

| Table 3.15 | Register sleepTCurCnt                                                                | . 45 |

| Table 3.16 | Register irqStat                                                                     | . 48 |

| Table 3.17 | Register irqEna                                                                      | . 48 |

| Table 3.18 | Register pwrCfgFp                                                                    | . 61 |

| Table 3.19 | Register pwrCfgLp                                                                    | . 62 |

| Table 3.20 | Register gotoPd                                                                      | . 63 |

| Table 3.21 | Register discCvtCnt                                                                  | . 63 |

| Table 3.22 | Value for sdmPos2 Depending on sdmPos and Desired Clock Delay from SDM to Chop Clock |      |

| Table 3.23 | Register sdmClkCfgLp                                                                 | . 68 |

| Table 3.24 | Register sdmClkCfgFp                                                                 | . 68 |

| Table 3.25 | Register adcCoff                                                                     | . 72 |

| Table 3.26 | Register adcCgan                                                                     | . 72 |

| Table 3.27 | Register adcVoff                                                                     | . 72 |

| Table 3.28 | Register adcVgan                                                                     | . 73 |

| Table 3.29 | Register adcToff                                                                     | . 73 |

| Table 3.30 | Register adcTgan                                                                     | . 73 |

| Table 3.31 | Register adcPoCoGain                                                                 |      |

| Table 3.32 | Register adcCdat                                                                     |      |

| Table 3.33 | Register adcVdat                                                                     | . 75 |

| Table 3.34 | Register adcTdat                                                                     | . 75 |

| Table 3.35 | Register adcRdat                            | 75  |

|------------|---------------------------------------------|-----|

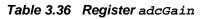

| Table 3.36 | Register adcGain                            | 76  |

| Table 3.37 | Register adcCrcl                            | 77  |

| Table 3.38 | Register adcCrcv                            | 77  |

| Table 3.39 | Register adcVrcl                            | 77  |

| Table 3.40 | Register adcVrcv                            | 77  |

| Table 3.41 | Register adcCrth                            | 79  |

| Table 3.42 | Register adcCtcl                            | 79  |

| Table 3.43 | Register adcCtcv                            | 79  |

| Table 3.44 | Register adcCaccTh                          | 80  |

| Table 3.45 | Register adcCaccu                           | 80  |

| Table 3.46 | Register adcVTh                             | 81  |

| Table 3.47 | Register adcVaccu                           | 81  |

| Table 3.48 | Register adcCmax                            | 82  |

| Table 3.49 | Register adcCmin                            | 82  |

| Table 3.50 | Register adcVmax                            | 82  |

| Table 3.51 | Register adcVmin                            | 82  |

| Table 3.52 | Register adcTmax                            | 83  |

| Table 3.53 | Register adcTmin                            | 83  |

| Table 3.54 | Register adcAcmp                            | 84  |

| Table 3.55 | Register adcGomd                            | 85  |

| Table 3.56 | Register adcSamp                            | 85  |

| Table 3.57 | adcMode Settings                            | 86  |

| Table 3.58 | Register adcCtrl                            | 92  |

| Table 3.59 | Register adcChan                            | 97  |

| Table 3.60 | Example Results of BIST                     | 98  |

| Table 3.61 | Register adcDiag                            | 99  |

| Table 3.62 | Register currentSrcEna                      | 99  |

| Table 3.63 | ZSSC1750 Register linCfg                    | 102 |

| Table 3.64 | ZSSC1750 Register linShortFilter            | 103 |

| Table 3.65 | ZSSC1750 Register linShortDelay             | 103 |

| Table 3.66 | ZSSC1750 Register linWuDelay                | 103 |

| Table 3.67 | OTP Memory Map                              | 104 |

| Table 3.68 | Register pullResEna                         | 106 |

| Table 3.69 | Register versionCode                        | 106 |

| Table 3.70 | Register pwrTrim                            | 107 |

| Table 3.71 | Register ibiasLinTrim                       | 107 |

| Table 4.1  | ESD Protection According to AEC-Q100 Rev. G | 110 |

| Table 5.1  | ZSSC1750/51 Pins Description                | 112 |

# **1** IC Characteristics

The absolute maximum ratings are stress ratings only. The ZSSC1750/51 might not function or be operable above the recommended operating conditions. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the "Absolute Maximum Ratings."

# 1.1 Absolute Maximum Ratings

| No      | Parameter                      | Symbol            | Conditions          | Min                   | Max                   | Unit |

|---------|--------------------------------|-------------------|---------------------|-----------------------|-----------------------|------|

| 1.1.1.  | External power supply          | V <sub>DDE</sub>  |                     | $V_{SSE}$ -0.3        | 40                    | V    |

| 1.1.2.  | Current sensing, INP pin       | V <sub>INP</sub>  |                     | V <sub>SSE</sub> -0.3 | V <sub>DDA</sub> +0.3 | V    |

| 1.1.3.  | Current sensing, INN pin       | V <sub>INN</sub>  |                     | V <sub>SSE</sub> -0.3 | V <sub>DDA</sub> +0.3 | V    |

| 1.1.4.  | Voltage sensing, VBAT pin      | V <sub>VBAT</sub> |                     | -18                   | 33                    | V    |

| 1.1.5.  | Voltage sensing, VBAT pin      | V <sub>VBAT</sub> | 1h over<br>lifetime | -18                   | 40                    | V    |

| 1.1.6.  | Temperature sensing, NTH pin   | V <sub>NTH</sub>  |                     | V <sub>SSE</sub> -0.3 | V <sub>DDA</sub> +0.3 | V    |

| 1.1.7.  | Temperature sensing, NTL pin   | V <sub>NTL</sub>  |                     | V <sub>SSE</sub> -0.3 | V <sub>DDA</sub> +0.3 | V    |

| 1.1.8.  | LIN bus interface, LIN pin     | V <sub>LIN</sub>  |                     | -16                   | 33                    | V    |

| 1.1.9.  | LIN bus interface, LIN pin     | V <sub>LIN</sub>  | 1h over<br>lifetime | -16                   | 40                    | V    |

| 1.1.10. | Digital IO pins                | V <sub>IO</sub>   |                     | V <sub>SSE</sub> -0.3 | V <sub>DDP</sub> +0.3 | V    |

| 1.1.11. | Ambient temperature under bias | T <sub>AMB</sub>  |                     |                       | 125                   | °C   |

| 1.1.12. | Junction temperature           | Tj                |                     |                       | 135                   | °C   |

| 1.1.13. | Storage temperature            | T <sub>STOR</sub> |                     | -50                   | 125                   | °C   |

Table 1.1 Absolute Maximum Ratings (referenced to VSSE)

# 1.2 Recommended Operating Conditions

# Table 1.2Operating Conditions

| No.    | Parameter                                                                                                                                                                                                                 | Symbol                | Conditions                                                                                                     | Min                  | Тур. | Max                  | Unit |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|------|

| 1.2.1  | Operating temperature range                                                                                                                                                                                               | Т <sub>АМВ</sub>      | MB Ambient temperature;<br>RTH <sub>JA</sub> =27K/W                                                            |                      |      | 115                  | °C   |

| 1.2.2  | Extended temperature range                                                                                                                                                                                                | $T_{AMB}_Ext$         | AMB_Ext Ambient temperature;<br>reduced accuracies                                                             |                      |      | 125                  | °C   |

| 1.2.3  | Supply voltage at BAT+ terminal <sup>1)</sup> for normal operation                                                                                                                                                        | V <sub>BAT+</sub>     |                                                                                                                | 6                    | 13   | 18                   | V    |

| 1.2.4  | <ul> <li>Minimum supply voltage at VDDE pin:</li> <li>a) When BAT+ &lt; 6V, i.e. operation with low battery</li> <li>b) When V<sub>BAT</sub> = V<sub>DDE</sub>, i.e. without using Ddde and Rdde <sup>1)</sup></li> </ul> | $V_{\text{DDE}\_low}$ | Normal accuracy for<br>current and temperature<br>measurements<br>Reduced accuracy for<br>voltage measurements | 4.8                  |      |                      | V    |

|        |                                                                                                                                                                                                                           |                       | Reduced accuracy for all measurements                                                                          | 4.2                  |      |                      |      |

| 1.2.5  | Digital input voltage LOW                                                                                                                                                                                                 | VIL                   |                                                                                                                | 0                    |      | 0.3*V <sub>DDP</sub> | V    |

| 1.2.6  | Digital input voltage HIGH                                                                                                                                                                                                | V <sub>IH</sub>       |                                                                                                                | 0.7*V <sub>DDP</sub> |      | V <sub>DDP</sub>     | V    |

| 1) See | application diagram on page 2.                                                                                                                                                                                            |                       |                                                                                                                |                      |      |                      |      |

<sup>© 2016</sup> Integrated Device Technology, Inc.

# **1.3 Electrical Parameters**

Note: See important notes at the end of the following table. See section 3.7 for definitions of the ULP and OFF power states.

| Table 1.3 | <b>Electrical Specifications</b> |

|-----------|----------------------------------|

|           |                                  |

| No.     | Parameter                                                                                                        | Symbol                | Conditions                                     | Min  | Тур. | Max  | Unit |

|---------|------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|------|------|------|------|

| Supply  |                                                                                                                  |                       |                                                |      |      | •    |      |

| 1.3.1.  | Average supply current at VDDE                                                                                   | I <sub>DDE_avg</sub>  | Normal Mode<br>(FP State,<br>both ADCs on)     | 10   | 12   | 14   | mA   |

| 1.3.2.  | Average power dissipation                                                                                        | $P_{DDE\_avg}$        | Normal Mode,<br>V <sub>DDE</sub> =13V          | 130  | 156  | 182  | mW   |

| 1.3.3.  | Current at VDDE in Sleep Mode<br>(ULP State with no<br>measurement)                                              | I <sub>DDE_sip</sub>  | T <sub>AMB</sub> = room<br>temperature<br>(RT) |      | 55   |      | μA   |

|         |                                                                                                                  |                       | $T_{AMB} = 115^{\circ}C$                       |      | 100  |      | μA   |

| 1.3.4.  | Average current at VDDE in<br>Comparator Mode<br>(ULP State with wake-up interval<br>= 30s and current ADC only) | I <sub>DDE_cmp</sub>  | T <sub>AMB</sub> = RT                          |      | 160  |      | μΑ   |

| 1.3.5.  | Average current at VDDE in OFF<br>State (no measurements)                                                        | I <sub>DDE_off</sub>  | T <sub>AMB</sub> = RT                          |      | 50   |      | μA   |

| 1.3.6.  | Internal analog power supply voltage, VDDA pin                                                                   | $V_{DDA}$             |                                                | 2.4  | 2.5  | 2.6  | V    |

| 1.3.7.  | Internal digital power supply voltage, VDDL pin                                                                  | $V_{DDL}$             |                                                | 1.62 | 1.8  | 1.98 | V    |

| Externa | al Microcontroller (MCU) Supply                                                                                  |                       |                                                |      |      |      |      |

| 1.3.8.  | External microcontroller core                                                                                    | V <sub>DDC</sub>      | Default                                        | 1.62 | 1.8  | 1.98 | V    |

|         | power supply voltage, VDDC pin                                                                                   |                       | Configuration<br>option (see<br>section 2.2)   | 1.08 | 1.2  | 1.32 | V    |

| 1.3.9.  | External microcontroller power                                                                                   | V <sub>DDP</sub>      | Default                                        | 2.97 | 3.3  | 3.63 | V    |

|         | supply voltage (periphery), VDDP pin                                                                             |                       | Configuration<br>option (see<br>section 2.2)   | 2.25 | 2.5  | 2.75 | V    |

| 1.3.10. | Output current of VDDP regulator                                                                                 | I <sub>VDDP_OUT</sub> |                                                | -    | -    | 40   | mA   |

<sup>© 2016</sup> Integrated Device Technology, Inc.

| No.       | Parameter                             | Symbol                      | Conditions                            | Min  | Тур. | Max  | Unit         |

|-----------|---------------------------------------|-----------------------------|---------------------------------------|------|------|------|--------------|

| 1.3.11.   | Output current capability of VDDP pin | I <sub>VDDP</sub>           | See Figure 1.1 for test circuit       | -    | -    | 30   | mA           |

| 1.3.12.   | Output current of VDDC regulator      | I <sub>VDDC_OUT</sub>       |                                       |      |      | 40   | mA           |

| 1.3.13.   | Output current capability of VDDC pin | I <sub>VDDC</sub>           |                                       |      |      | 40   | mA           |

| Digital I | O Pins Parameters (VDDP = 3.3V)       |                             |                                       |      |      |      |              |

| 1.3.14.   | Input low-to-high threshold voltage   | $V_{\text{LH}_{\text{th}}}$ |                                       | 55   | 60   | 65   | % of<br>VDDP |

| 1.3.15.   | Input high-to-low threshold voltage   | $V_{\text{HL}\_\text{th}}$  |                                       | 35   | 40   | 45   | % of<br>VDDP |

| 1.3.16.   | Internal pull-down resistor           | $R_{\text{PULL}_{down}}$    | Vpin = VDDP                           | 70   | 190  | 310  | kΩ           |

| 1.3.17.   | Leakage current                       | I <sub>LEAK_I/O</sub>       |                                       | -    | -    | 1    | μA           |

| 1.3.18.   | Output low level                      | V <sub>OL</sub>             | $I_{OUT} = I_{_{_{_{_{_{_{_{}}}}}}}}$ | -    | -    | 20   | % of<br>VDDP |

| 1.3.19.   | Output high level                     | V <sub>OH</sub>             | $I_{OUT} = I_{I/O}$                   | 80   | -    | -    | % of<br>VDDP |

| 1.3.20.   | Output low level of SLEEPN pin        | $V_{L_{SLEEPN}}$            | $I_{SLEEPN} = 0.1 \text{mA}$          | -    | -    | 0.40 | V            |

| 1.3.21.   | Output high level of SLEEPN pin       | $V_{H\_SLEEPN}$             | $I_{SLEEPN} = 0.1 \text{mA}$          | 1.40 | -    | -    | V            |

| 1.3.22.   |                                       | I                           | MCU_CLK pin                           | -    | -    | 3.0  | mA           |

| 1.3.23.   | Pin output current <sup>1)</sup>      | I_ <sub>!/O</sub>           | All other IOs                         | -    | -    | 1.5  | mA           |

| 1.3.24.   |                                       | I <sub>SLEEPN</sub>         | SLEEPN pin                            | -    | -    | 0.1  | mA           |

| 1.3.25.   | Pin capacitance <sup>1)</sup>         | C_I/O                       |                                       | 4.5  | 5.5  | 6.5  | pF           |

| Current   | Channel                               |                             |                                       |      |      |      |              |

| 1.3.26.   | Input signal range 1)                 | Range <sub>c</sub>          | Gain = 4                              | -300 |      | 300  | mV           |

|           |                                       |                             | Gain = 8                              | -150 |      | 150  | mV           |

|           |                                       |                             | Gain = 16                             | -75  |      | 75   | mV           |

|           |                                       |                             | Gain = 32                             | -38  |      | 38   | mV           |

|           |                                       |                             | Gain = 64                             | -19  |      | 19   | mV           |

|           |                                       |                             | Gain = 128                            | -9.5 |      | 9.5  | mV           |

|           |                                       |                             | Gain = 256                            | -4.7 |      | 4.7  | mV           |

|           |                                       |                             | Gain = 512                            | -2.3 |      | 2.3  | mV           |

| 1.3.27.   | Input leakage current 1)              | I <sub>LEAK_C</sub>         | $T_{AMB} = 25^{\circ}C$               | -3   |      | +3   | nA           |

| No.     | Parameter                                                                       | Symbol                      | Conditions                                               | Min  | Тур. | Max   | Unit                        |

|---------|---------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------|------|------|-------|-----------------------------|

| 1.3.28. | Input offset current <sup>1)</sup>                                              | I <sub>OFFSET_C</sub>       | For input signal<br>< 10mV                               |      | 0.5  | 1.5   | nA                          |

| 1.3.29. | Conversion rate <sup>1), 2)</sup>                                               | Rate <sub>c</sub>           | Programmable                                             | 1    |      | 16000 | Hz                          |

| 1.3.30. | Oversampling ratio (OSR) <sup>1)</sup><br>(Sinc <sup>4</sup> decimation filter) | OSR <sub>C</sub>            | Programmable                                             | 32   |      | 256   |                             |

| 1.3.31. | No missing codes <sup>1)</sup>                                                  | NMC <sub>c</sub>            |                                                          | 18   |      |       | Bits                        |

| 1.3.32. | Integral nonlinearity <sup>1), 3)</sup>                                         | INL                         | Maximum input range                                      |      | ±10  | ±60   | ppm of<br>FSR <sup>4)</sup> |

| 1.3.33. | PGA gain range <sup>1)</sup>                                                    | A <sub>PGA</sub>            |                                                          | 4    |      | 512   |                             |

| 1.3.34. | Total gain error <sup>1)</sup>                                                  | err <sub>PGA_C</sub>        |                                                          | -1   |      | 1     | %                           |

| 1.3.35. | Gain drift <sup>1)</sup>                                                        | err_drift <sub>PGA_C</sub>  |                                                          |      | ±3   |       | ppm/ <sup>°</sup> C         |

| 1.3.36. | Offset error after calibration <sup>1)</sup>                                    | V <sub>OFFSET_C</sub>       | Normal Mode<br>chop on,<br>external short<br>(VSSA)      | -2   |      | 2     | μV                          |

|         |                                                                                 |                             | Low-Power<br>State, chop on,<br>external short<br>(VSSA) | -0.6 |      | +0.6  | μV                          |

| 1.3.37. | Offset error drift <sup>1)</sup>                                                | V <sub>OFFSET_DRIFT_C</sub> | Chop on                                                  |      | ±20  |       | nV/⁰C                       |

|         |                                                                                 |                             | Chop off                                                 |      | ±80  |       | nV/ºC                       |

| 1.3.38. | Output noise with chop on <sup>1)</sup>                                         | V <sub>NOISE_C</sub>        | Gain = 512,<br>conversion rate<br>= 10Hz                 |      | 1.1  |       | μV <sup>RMS</sup>           |

|         |                                                                                 |                             | Gain = 512,<br>conversion rate<br>= 1kHz                 |      | 1.1  |       | μV <sup>RMS</sup>           |

|         |                                                                                 |                             | Gain = 32,<br>conversion rate<br>= 1kHz                  |      | 3    |       | μV <sup>RMS</sup>           |

|         |                                                                                 |                             | Gain = 4,<br>conversion rate<br>= 1kHz                   |      | 11   |       | μV <sup>RMS</sup>           |

| No.     | Parameter                                                                 | Symbol                               | Conditions                                               | Min   | Тур. | Max   | Unit                        |

|---------|---------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|-------|------|-------|-----------------------------|

| 1.3.39. | Current offset <sup>1)</sup>                                              | I <sub>BAT_offset</sub>              | Chop on,<br>gain = 512,<br>$R_{shunt} = 100 \mu \Omega$  |       |      | 10    | mA                          |

| 1.3.40. | Resolution <sup>1)</sup>                                                  | I <sub>RES</sub>                     | Chop on,<br>gain = 512,<br>$R_{shunt}$ = 100 $\mu\Omega$ | 1     |      |       | mA                          |

| Voltage | Channel                                                                   |                                      |                                                          |       |      |       |                             |

| 1.3.41. | Input signal range (at VBAT pin) <sup>1)</sup>                            | Range <sub>v</sub>                   | Resistive<br>divider (1:24)                              | 0     |      | 28.8  | V                           |

| 1.3.42. | Input measurement range 1)                                                | Range <sub>meas_V</sub>              | Resistive<br>divider (1:24)                              | 3.6   |      | 28.8  | V                           |

| 1.3.43. | Input valid range for ADC <sup>1)</sup>                                   | Range <sub>ADC_V</sub>               | Resistive<br>divider (1:24)                              | 0.15  |      | 1.2   | V                           |

| 1.3.44. | Voltage resistive divider ratio <sup>1)</sup>                             | Ratio <sub>v</sub>                   |                                                          |       | 24   |       |                             |

| 1.3.45. | Resistor divider mismatch drift <sup>1)</sup>                             | Ratio_mis <sub>drift_v</sub>         |                                                          |       | ±3   |       | ppm/°C                      |

| 1.3.46. | Conversion rate <sup>1), 2)</sup>                                         | Ratev                                | Programmable                                             | 1     |      | 16000 | Hz                          |

| 1.3.47. | Oversampling ratio<br>(Sinc <sup>4</sup> decimation filter) <sup>1)</sup> | OSR <sub>v</sub>                     | Programmable                                             | 32    |      | 256   |                             |

| 1.3.48. | No missing codes <sup>1)</sup>                                            | NMC <sub>V</sub>                     |                                                          | 18    |      |       | Bits                        |

| 1.3.49. | Integral nonlinearity <sup>1), 3)</sup>                                   | $INL_{V}$                            | Maximum input range                                      |       | ±10  | ±60   | ppm of<br>FSR <sup>4)</sup> |

| 1.3.50. | Total gain error <sup>1)</sup><br>(includes resistor divider<br>mismatch) | err <sub>PGA_V</sub>                 |                                                          | -0.25 |      | 0.25  | %                           |

| 1.3.51. | Gain drift <sup>1)</sup>                                                  | err_drift <sub>PGA_V</sub>           |                                                          |       | ±3   |       | ppm/°C                      |

| 1.3.52. | Offset error after calibration:<br>Normal Mode <sup>1)</sup>              | V <sub>OFFSET_V</sub>                | Chop on<br>external short<br>(1.25V)                     |       | 200  |       | μV                          |

|         |                                                                           |                                      | Chop off<br>external short<br>(1.25V)                    |       | 1    |       | mV                          |

| 1.3.53. | Offset error drift <sup>1)</sup>                                          | $V_{\text{OFFSET}\_\text{DRIFT}\_V}$ | Chop on                                                  |       | ±10  |       | µV/°C                       |

|         |                                                                           |                                      | Chop off                                                 |       | ±20  |       | µV/°C                       |

| No.     | Parameter                                                                 | Symbol                      | Conditions                                             | Min     | Тур.    | Max   | Unit              |

|---------|---------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------|---------|---------|-------|-------------------|

| 1.3.54. | Output noise <sup>1)</sup>                                                | V <sub>NOISE_V</sub>        | Chop on<br>gain = 1,<br>conversion rate<br>=10Hz       |         | 30      | 50    | μV <sup>RMS</sup> |

|         |                                                                           |                             | Chop on<br>gain = 1,<br>conversion rate<br>= 1kHz      |         | 1       |       | $\mu V^{RMS}$     |

| Temper  | ature Channel (External NTC/Refe                                          | erence Resisto              | r and Internal Ter                                     | nperatu | re Sens | or)   |                   |

| 1.3.55. | Voltage drop over NTC resistor <sup>1)</sup>                              | V <sub>NTC</sub>            |                                                        | 0       |         | 1.2   | V                 |

| 1.3.56. | Voltage drop over reference resistor 1)                                   | V <sub>REF_Res</sub>        | V <sub>REF_Res</sub>                                   |         |         | 1.2   | V                 |

| 1.3.57. | Conversion rate <sup>1)</sup>                                             | Rate⊤                       | Programmable                                           | 1       |         | 16000 | Hz                |

| 1.3.58. | Oversampling ratio<br>(Sinc <sup>4</sup> decimation filter) <sup>1)</sup> | OSR⊤                        | Programmable                                           | 32      |         | 256   |                   |

| 1.3.59. | Integral nonlinearity <sup>1), 3)</sup>                                   | INL <sub>T</sub>            | Maximum input range                                    |         | ±10     | ±60   | ppm<br>of FSR     |

| 1.3.60. | No missing codes <sup>1)</sup>                                            | NMC <sub>T</sub>            |                                                        | 16      |         |       | Bit               |

| 1.3.61. | Offset error after ZSSC1750/51 calibration <sup>1)</sup>                  | V <sub>OFFSET_T</sub>       | Normal Mode,<br>chop on,<br>external short<br>(1.25V)  | -100    |         | 100   | μV                |

|         |                                                                           |                             | Normal Mode,<br>chop off,<br>external short<br>(1.25V) | -2      |         | 2     | mV                |

| 1.3.62. | Offset error drift <sup>1)</sup>                                          | V <sub>OFFSET_DRIFT_T</sub> | Chop on                                                |         | ±10     |       | µV/⁰C             |

|         |                                                                           |                             | Chop off                                               |         | ±20     |       | µV/⁰C             |

| 1.3.63. | Output noise <sup>1)</sup>                                                | V <sub>NOISE_T</sub>        | Chop on,<br>gain = 1,<br>conversion<br>rate =500Hz     |         |         | 50    | $\mu V^{RMS}$     |

| 1.3.64. | Resistor to ground at pin NTL <sup>1)</sup>                               | GND <sub>RES</sub>          |                                                        |         | 50      |       | kΩ                |

| 1.3.65. | Internal temperature sensor resolution <sup>1)</sup>                      | RES <sub>ITS</sub>          |                                                        | -       | 1/32    | -     | °C/LSB            |

| 1.3.66. | Linearity error of internal temperature sensor <sup>1)</sup>              | LE <sub>ITS</sub>           |                                                        | -       | ±2      | -     | °C                |

<sup>© 2016</sup> Integrated Device Technology, Inc.

| No.      | Parameter                                                        | Symbol                                        | Conditions               | Min  | Тур. | Max  | Unit  |   |

|----------|------------------------------------------------------------------|-----------------------------------------------|--------------------------|------|------|------|-------|---|

| Power-o  | on Reset (POR)                                                   |                                               |                          |      |      |      | •     |   |

| 1.3.67.  | Power-on reset threshold                                         | V <sub>PORB</sub>                             | At V <sub>DDE</sub>      | 2.75 | 3.0  | 3.6  | V     |   |

| 1.3.68.  | Power-on-reset hysteresis                                        | Hyst <sub>PORB</sub>                          | At V <sub>DDE</sub>      |      | 300  |      | mV    |   |

| 1.3.69.  | Low-voltage flag                                                 | low_voltage                                   | At V <sub>DDE</sub>      | 1.8  | 2.0  | 2.3  | V     |   |

| 1.3.70.  | $V_{DDP}$ high <sup>1)</sup><br>(for VDDP = 3.3V configuration)  | vddp_high                                     | At V <sub>DDE</sub>      | 3.9  | 4.05 | 4.2  | V     |   |

| 1.3.71.  | V <sub>DDP</sub> high hysteresis <sup>1)</sup>                   | Hyst <sub>VDDP_high</sub> At V <sub>DDE</sub> |                          |      | 400  |      | mV    |   |

| Low-Po   | wer Voltage Reference                                            |                                               |                          |      |      |      |       |   |

| 1.3.72.  | Reference bandgap voltage:<br>low-power                          | V <sub>BGL</sub>                              | V <sub>BGL</sub>         |      |      | 1.32 | V     |   |

| 1.3.73.  | Accuracy<br>(including temperature drift)                        |                                               |                          |      |      | 3    | %     |   |

| 1.3.74.  | Temperature coefficient 1)                                       | TC <sub>VBGL</sub>                            |                          |      | 50   |      | ppm/K |   |

| Low-Po   | wer (LP) Oscillator                                              |                                               |                          |      |      |      |       |   |

| 1.3.75.  | Frequency                                                        | f <sub>LPO</sub>                              |                          |      | 125  |      | kHz   |   |

| 1.3.76.  | Accuracy (including temperature drift) <sup>1)</sup>             |                                               |                          |      | -3   |      | 3     | % |

| High-Pr  | ecision Voltage Reference                                        |                                               |                          |      |      |      | •     |   |

| 1.3.77.  | Reference bandgap voltage:<br>high-precision                     | V <sub>BGH</sub>                              | Uncalibrated             | 1.16 |      | 1.32 | V     |   |

| 1.3.78.  | Temperature coefficient 1)                                       | TC <sub>VBGH</sub>                            | Calibrated               | -20  | ±5   | +20  | ppm/K |   |

| High-Pr  | ecision (HP) Oscillator                                          |                                               |                          |      |      | •    |       |   |

| 1.3.79.  | Frequency                                                        | f <sub>HPO</sub>                              |                          |      | 20   |      | MHz   |   |

| 1.3.80.  | Accuracy<br>(including temperature drift) <sup>1)</sup>          |                                               |                          | -1   |      | 1    | %     |   |

| LIN Inte | rface                                                            |                                               |                          |      |      | •    |       |   |

| 1.3.81.  | Current limitation for driver dominant state <sup>1)</sup>       | I <sub>BUS_LIM</sub>                          | LIN spec 2.1<br>Param 12 | 40   |      | 200  | mA    |   |

| 1.3.82.  | Input leakage current, dominant state, driver off <sup>1)</sup>  | I <sub>BUS_PAS_dom</sub>                      | LIN spec 2.1<br>Param 13 | -1   |      |      | mA    |   |

| 1.3.83.  | Input leakage current, recessive state, driver off <sup>1)</sup> | I <sub>BUS_PAS_rec</sub>                      | LIN spec 2.1<br>Param 14 |      |      | 20   | μA    |   |

| No.      | Parameter                                                              | Symbol                        | Conditions               | Min   | Тур. | Max   | Unit             |

|----------|------------------------------------------------------------------------|-------------------------------|--------------------------|-------|------|-------|------------------|

| 1.3.84.  | Control unit disconnected from ground <sup>1)</sup>                    | I <sub>BUS_NO_GND</sub>       | LIN spec 2.1<br>Param 15 | -1    |      | 1     | mA               |

| 1.3.85.  | $V_{BAT}$ supply disconnected <sup>1)</sup>                            | I <sub>BUS_NO_BAT</sub>       | LIN spec 2.1<br>Param 16 |       |      | 100   | μA               |

| 1.3.86.  | Receiver dominant state, $V_{DDE} > 7V^{1)}$                           | V <sub>BUSdom</sub>           | LIN spec 2.1<br>Param 17 |       |      | 0.4   | $V_{\text{DDE}}$ |

| 1.3.87.  | Receiver recessive state, $V_{DDE} > 7V^{1)}$                          | V <sub>BUSrec</sub>           | LIN spec 2.1<br>Param 18 | 0.6   |      |       | $V_{\text{DDE}}$ |

| 1.3.88.  | Center of receiver threshold <sup>1)</sup>                             | V <sub>BUS_CNT</sub>          | LIN spec 2.1<br>Param 19 | 0.475 | 0.5  | 0.525 | $V_{\text{DDE}}$ |

| 1.3.89.  | Receiver hysteresis voltage <sup>1)</sup>                              | V <sub>HYS</sub>              | LIN spec 2.1<br>Param 20 |       |      | 0.175 | $V_{\text{DDE}}$ |

| 1.3.90.  | Voltage drop at serial diodes <sup>1)</sup>                            | V <sub>SerDiode</sub>         | LIN spec 2.1<br>Param 21 | 0.4   | 0.7  | 1     | V                |

| 1.3.91.  | Battery shift <sup>1)</sup>                                            | V <sub>SHIFT_BAT</sub>        | LIN spec 2.1<br>Param 22 |       |      | 0.115 | V <sub>BAT</sub> |

| 1.3.92.  | Ground shift <sup>1)</sup>                                             | $V_{BUS\_GND}$                | LIN spec 2.1<br>Param 23 |       |      | 0.115 | $V_{BAT}$        |

| 1.3.93.  | Difference between battery shift and ground shift <sup>1)</sup>        | V <sub>SHIFT_Difference</sub> | LIN spec 2.1<br>Param 24 | 0     |      | 8     | %                |

| 1.3.94.  | LIN pull-up resistor <sup>1)</sup>                                     | R <sub>SLAVE</sub>            | LIN spec 2.1<br>Param 26 | 20    | 30   | 47    | kΩ               |

| 1.3.95.  | Duty cycle 1 <sup>1)</sup>                                             | D1                            | LIN spec 2.1<br>Param 27 | 0.396 |      |       |                  |

| 1.3.96.  | Duty cycle 2 <sup>1)</sup>                                             | D2                            | LIN spec 2.1<br>Param 28 |       |      | 0.581 |                  |

| 1.3.97.  | Duty cycle 3 <sup>1)</sup>                                             | D3                            | LIN spec 2.1<br>Param 29 | 0.417 |      |       |                  |

| 1.3.98.  | Duty cycle 4 <sup>1)</sup>                                             | D4                            | LIN spec 2.1<br>Param 30 |       |      | 0.590 |                  |

| 1.3.99.  | Receiver propagation delay <sup>1)</sup>                               | T <sub>RX_pdr</sub>           | LIN spec 2.1<br>Param 31 |       |      | 6     | μs               |

| 1.3.100. | Symmetry receiver propagation delay, rising/falling edge <sup>1)</sup> | T <sub>RX_sym</sub>           | LIN spec 2.1<br>Param 32 | -2    |      | 2     | μs               |

| No.            | Parameter Symbol Conditions M                                                       |             | Min                      | Тур. | Мах | Unit |    |

|----------------|-------------------------------------------------------------------------------------|-------------|--------------------------|------|-----|------|----|

| 1.3.101.       | Capacitance of slave node <sup>1)</sup>                                             | $C_{SLAVE}$ | LIN spec 2.1<br>Param 23 |      |     | 250  | pF |

| 1.3.102.       | .3.102. LIN pin capacitance <sup>1)</sup>                                           |             |                          | -    | -   | 30   | pF |

| 2)<br>3)<br>4) | <ul> <li>2) Depends on chopping and OSR settings.</li> <li>3) FSR = 1.2V</li> </ul> |             |                          |      |     |      |    |

Figure 1.1 Measurement Method for Determining VDDP Pin Current Capability

# 1.4 Timing Parameters

# Table 1.4Timing Parameters

| No                                   | Parameter                                                | Symbol                | Conditions   | Min   | Тур | Max                                                                        | Unit        |  |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------|-----------------------|--------------|-------|-----|----------------------------------------------------------------------------|-------------|--|--|--|--|--|--|--|

| SPI Protocol Timing (See Figure 1.2) |                                                          |                       |              |       |     |                                                                            |             |  |  |  |  |  |  |  |

| 1.4.1.                               | SPI operational frequency <sup>1)</sup>                  | fspi                  |              | -     | -   | 8                                                                          | MHz         |  |  |  |  |  |  |  |

| 1.4.2.                               | SCLK clock period for registers read/write <sup>1)</sup> | <b>t</b> SCLKPreg     |              | 125   | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.3.                               | SCLK clock period for OTP read <sup>1)</sup>             | <b>t</b> SCLKPotp     |              | 200   | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.4.                               | SCLK clock pulse width 1)                                | tsclkw                |              | 40    | 50  | 60                                                                         | %<br>tsclkp |  |  |  |  |  |  |  |

| 1.4.5.                               | CSN setup time <sup>1)</sup>                             | tcsu                  |              | 50    | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.6.                               | CSN hold time <sup>1)</sup>                              | tснр                  |              | 50    | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.7.                               | CSN high time 1)                                         | tсні                  |              | 300   | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.8.                               | MOSI data setup time 1)                                  | tosu                  |              | 20    | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.9.                               | MOSI data hold time 1)                                   | tоно                  |              | 10    | -   | -                                                                          | ns          |  |  |  |  |  |  |  |

| 1.4.10.                              | MISO data access time 1)                                 | t dacc                |              | -     | -   | 25                                                                         | ns          |  |  |  |  |  |  |  |

| Timer 0                              | (Sleep Timer)                                            |                       |              |       |     |                                                                            |             |  |  |  |  |  |  |  |

| 1.4.11.                              | Time interval <sup>1)</sup>                              | SLPTI1                | Programmable | 0.1   |     | 6553.5                                                                     | S           |  |  |  |  |  |  |  |

| 1.4.12.                              | Time interval with post-scaler <sup>1)</sup>             | SLPTI2                | Programmable |       |     | 466                                                                        | h           |  |  |  |  |  |  |  |

| 1.4.13.                              | Resolution <sup>1)</sup>                                 | SLPTI1 <sub>res</sub> |              |       | 100 |                                                                            | ms          |  |  |  |  |  |  |  |

| Timer 1                              | (Watchdog Timer WDT)                                     |                       |              |       |     |                                                                            |             |  |  |  |  |  |  |  |

| 1.4.14.                              | Time interval <sup>1)</sup>                              | WDTI                  | Programmable | 8µ    |     | 6553.5                                                                     | S           |  |  |  |  |  |  |  |

| 1.4.15.                              | Resolution <sup>1)</sup>                                 | WDTI <sub>res</sub>   | Programmable | 0.008 |     | 100                                                                        | ms          |  |  |  |  |  |  |  |

| Startup                              | Timing (See Figure 1.3)                                  |                       |              |       |     |                                                                            |             |  |  |  |  |  |  |  |

| 1.4.16.                              | PORB delay until analog blocks settled <sup>1)</sup>     | $T_{PORB\_dly}$       |              |       |     | 1                                                                          | ms          |  |  |  |  |  |  |  |

| 1)                                   | Not tested in production test; given by design and/or    | characterizatio       | n.           |       |     | 1) Not tested in production test; given by design and/or characterization. |             |  |  |  |  |  |  |  |

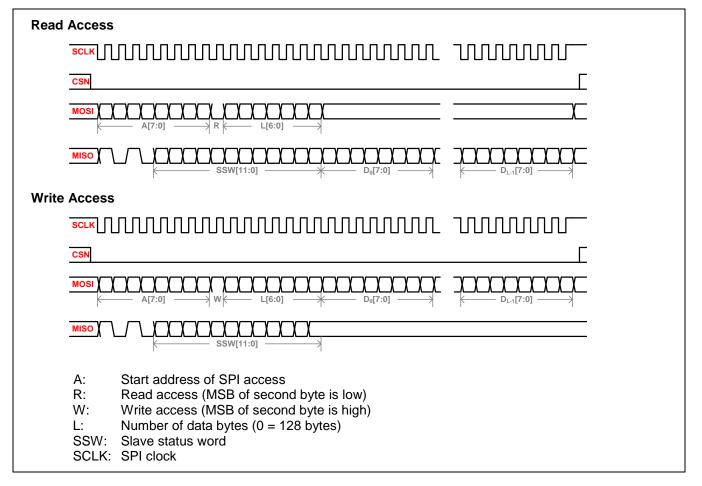

Figure 1.2 SPI Protocol Timing

Figure 1.3 ZSSC1750/51 Power-Up and Power-Down Sequence

# 2 Circuit Description

### 2.1 Overview

The ZSSC1750/51 is a data acquisition System Basis Chip (SBC) assembled in a PQFN36 6x6mm package. It contains a high voltage circuit, analog input stage including peripheral blocks, sigma-delta ( $\Sigma\Delta$ ) ADCs (SD\_ADC), digital filtering, and a LIN transceiver (for ZSSC1750 only). Communication between an external microcontroller and the SBC is handled by a Serial Peripheral Interface (SPI). The functions of the ZSSC1750/51 are controlled by register settings. The circuit starts after power-on with default register and calibration settings that can be overwritten by the user's software.

One input channel measures  $I_{BAT}$  via the voltage drop at the external shunt resistor. The second channel measures  $V_{BAT}$  and the temperature. By simultaneously measuring  $V_{BAT}$  and  $I_{BAT}$ , it is possible to dynamically determine Rdi, which is correlated with the state of health (SOH) of the battery. By integrating  $I_{BAT}$ , it is possible to determine the state of charge (SOC) of the battery. These are the fundamental parameters for an intelligent battery sensor. The necessary microcontroller and the software for determining these parameters is not part of the ZSSC1750/51.

#### Figure 2.1 Functional Block Diagram

During the Standby Mode and the system's Sleep Mode (e.g., engine is off), the system periodically measures the values to monitor the discharge of the battery (see section 3.7 regarding modes). Measurement cycles are controlled by the user's software and are dependent on the detected events. The ZSSC1750/51 is designed for low current consumption during Sleep Mode in the range of less than 60µA.

<sup>© 2016</sup> Integrated Device Technology, Inc.

# 2.2 SBC-to-MCU Interface Pins

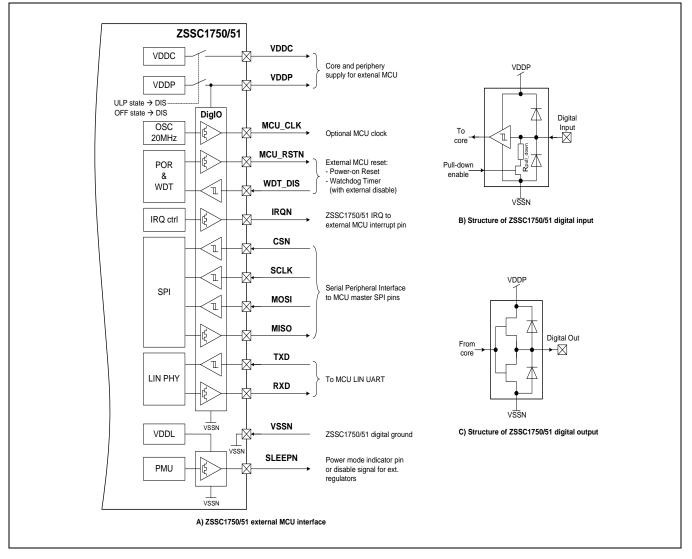

The ZSSC1750/51 connects to the external microcontroller (MCU) using pins shown in Figure 2.2-A. ZSSC1750/51 pins can be classified in three categories: digital IOs, microcontroller supply pins, and the power state indicator pin.

#### 2.2.1 Digital I/Os

The digital I/O pins include the SPI interface pins, MCU clock, rest and interrupt pins, LIN UART pins (for ZSSC1750 only), and watchdog timer disable pin.

All digital input pins of the ZSSC1750/51 feature a Schmitt trigger (see Figure 2.2-B), as well as configurable pull-down resistors and protection diodes. The pull-down resistors have values specified by parameter 1.3.16. They are enabled after power-on-reset and can be further controlled via the pullResEna register (see section 3.11.1.1).

All digital output pins of the ZSSC1750/51 have a push-pull stage and protection diodes connected as shown in Figure 2.2-C.

All digital I/Os are supplied by the VDDP voltage, which is switched off when the ZSSC1750/51 is in the ULP or OFF State (see section 2.3); i.e. the I/Os are also off in this state.

**Note:** In order to avoid parasitic supply of the digital I/O circuitry when the ZSSC1750/51 is in the ULP or OFF State, the digital outputs of the external microcontroller should be disabled. This is valid when the external microcontroller is not supplied by the ZSSC1750/51.

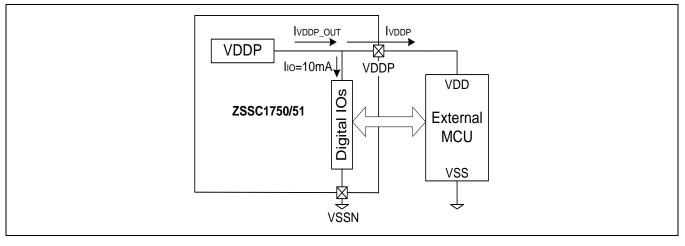

#### 2.2.2 External Microcontroller (MCU) Supply Pins

The ZSSC1750/51 provides two separate regulators for the external microcontroller supply. The VDDP regulator provides 3.3V, and VDDC provides 1.8V. Both voltages are switched off when the ZSSC1750/51 is in the ULP or OFF State. For more information regarding the VDDP and VDDC regulators, including trimming options, refer to sections 3.12.5 and 3.12.6. The current capability of the VDDP and VDDC pins is specified by parameters 1.3.11 and 1.3.13 respectively.

#### 2.2.3 SLEEPN Power State Indicator Pin

The ZSSC1750/51 features a SLEEPN pin that indicates the power state of the ZSSC1750/51 (see section 2.3). When the ZSSC1750/51 is in the full power (FP) state or low power (LP) state, the SLEEPN pin is HIGH; when the state is ULP or OFF, SLEEPN is LOW. In order to remain powered in these states, the SLEEPN pin circuitry is supplied by the VDDL regulator. When HIGH, the SLEEPN pin has a 1.8V output voltage level; the HIGH and LOW levels are specified with parameters 1.3.20 and 1.3.21.

In the application, the SLEEPN pin can be connected to the external microcontroller (if it remains powered in system Sleep Mode), or it can be used for disabling an external circuitry when the ZSSC1750/51 goes into one of the power saving modes. Depending on the application specifics, an external buffer (e.g., a transistor) might be needed for the SLEEPN pin for a proper level or current conditioning.

### 2.3 System Power States

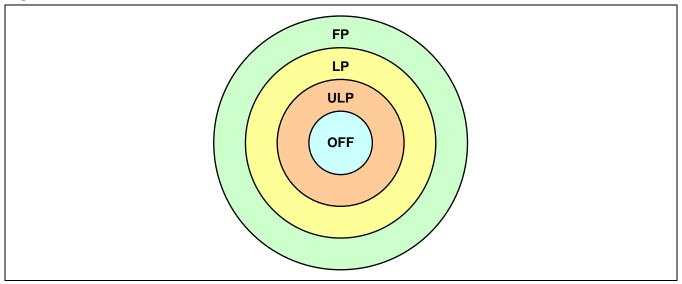

There are four different power states implemented in the ZSSC1750/51 as illustrated in Figure 2.3. Full details are given in section 3.7.

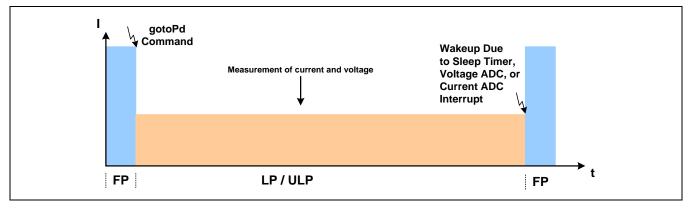

Figure 2.3 ZSSC1750/51 Power States

#### 2.3.1 Full Power State (FP)

The ZSSC1750/51 enters the Full Power (FP) State after power-on reset or after wake-up. In this power state, the ZSSC1750/51 is fully operational and the external microcontroller is supplied and running (see section 3.7). In the FP State, the ADCs are fully powered and running on the 4MHz base clock, which is generated from the 20MHz high-precision oscillator.

Of the four power states, the FP State consumes the most power. The MCU software can trigger the power management unit (PMU) inside the ZSSC1750/51 to enter any other power state (see section 3.7).

## 2.3.2 Low Power State (LP)

The Low Power (LP) State is intended for scenarios where the ZSSC1750/51 will only perform low-power measurements without any operation by the external microcontroller (MCU). For its ADC operations, it uses a 125kHz clock from the low-power oscillator as the base clock. The system can wake up from this power state via any enabled interrupt of the SBC as well as via an MCU reset generated by the watchdog timer.