Power Management Switch ICs for PCs and Digital Consumer Products

# **Power Switch IC** for ExpressCard<sup>™</sup>

No.11029EAT26 BD4157MUV

#### Description

BD4157MUV is a power management switch IC for the next generation PC card (ExpressCard<sup>TM</sup>) developed by the PCMCIA. It conforms to the PCMCIA ExpressCard<sup>TM</sup> Standard, ExpressCard<sup>TM</sup> Compliance Checklist., and ExpressCard<sup>TM</sup> Implementation Guideline, and obtains Compliance ID "EC100395" from PCMCIA. The power switch offers a number of functions - card detector, and system status detector - which are ideally suited for laptop and desktop computers.

#### Features

- 1) Incorporates three low on-resistance FETs for ExpressCard<sup>TM</sup>.

- Incorporates an FET for output discharge.

- 3) Incorporates an enabler.

- 4) Incorporates under voltage lockout (UVLO) protection.

- 5) Employs an VQFN020V4040 package.

- Built-in thermal shutdown protector (TSD).

- Built-in thermal shutdown protector (TSD).

- Incorporates an overcurrent protection (OCP).

- 9) Built-in enable signal for PLL

- Built-in Pull up resistance for detecting ExpressCard<sup>TM</sup>

Conforms to the ExpressCard<sup>TM</sup> Standard.

Conforms to the ExpressCard<sup>TM</sup> Compliance Checklist.

Conforms to the ExpressCard<sup>TM</sup> Implementation Guideline.

#### Applications

Laptop and desktop computers, and other ExpressCard <sup>™</sup> equipped digital devices.

#### Product Lineup

| Parameter | BD4157MUV    |

|-----------|--------------|

| Package   | VQFN020V4040 |

<sup>&</sup>quot;ExpressCard<sup>TM</sup>" is a registered trademark registered of the PCMCIA (Personal Computer Memory Card International Association).

● Absolute Maximum Ratings

| Parameter                    | Symbol                                    | Ratings                          | Unit |

|------------------------------|-------------------------------------------|----------------------------------|------|

| Input Voltage                | V3AUX_IN, V3_IN, V15_IN                   | -0.3~4.5 * <sup>1</sup>          | V    |

| Logic Input Voltage 1        | EN,CPPE#,CPUSB#,SYSR,<br>PERST_IN#,RCLKEN | -0.3~V3AUX_IN+0.3 *1             | V    |

| Logic Output Voltage 1       | RCLKEN                                    | -0.3~V3AUX_IN+0.3 * <sup>1</sup> | V    |

| Logic Output Voltage 2       | PERST#                                    | -0.3~V3AUX_IN+0.3                | V    |

| Output Voltage               | V3AUX,V3, V15                             | -0.3~4.5 * <sup>1</sup>          | V    |

| Output Current 1             | IOV3AUX                                   | 1.0                              | А    |

| Output Current 2             | IOV3                                      | 2.0                              | А    |

| Output Current 3             | IOV15                                     | 2.0                              | А    |

| Power Dissipation 1          | Pd1                                       | 0.34 *2                          | mW   |

| Power Dissipation 2          | Pd2                                       | 0.70 *3                          | mW   |

| Operating Temperature Range  | Topr                                      | -40 <b>~</b> +100                | °C   |

| Storage Temperature Range    | Tstg                                      | -55 <b>~</b> +150                | °C   |

| Maximum Junction Temperature | Tjmax                                     | +150                             | °C   |

<sup>\*1</sup> Not to exceed Pd.

#### **Operating Conditions** (Ta=25°C)

| Parameter              | Symbol                                 | Ratir | ıgs      | Unit  |

|------------------------|----------------------------------------|-------|----------|-------|

| Farameter              | Symbol                                 | MIN   | MAX      | Offic |

| Input Voltage 1        | V3AUX_IN                               | 3.0   | 3.6      | V     |

| Input Voltage 2        | V3_IN                                  | 3.0   | 3.6      | V     |

| Input Voltage 3        | V15_IN                                 | 1.35  | 1.65     | V     |

| Logic Input Voltage 1  | EN                                     | -0.3  | 3.6      | V     |

| Logic Input Voltage 2  | CPPE#,CPUSB#,SYSR,<br>PERST_IN#,RCLKEN | 0     | V3AUX_IN | V     |

| Logic Output Voltage 1 | RCLKEN                                 | 0     | V3AUX_IN | V     |

| Logic Output Voltage 2 | PERST#                                 | 0     | V3AUX_IN | V     |

| Output Current 1       | IOV3AUX                                | 0     | 275      | mA    |

| Output Current 2       | IOV3                                   | 0     | 1.3      | Α     |

| Output Current 3       | IOV15                                  | 0     | 650      | mA    |

<sup>★</sup> This product is not designed to offer protection against radioactive rays.

<sup>\*2</sup> Reduced by 2.7mW for each increase in Ta of 1°C over 25°C

\*3 Reduced by 5.6mW for each increase in Ta of 1°C over 25°C(When mounted on a board 74.2mm×74.2mm×1.6mm Glass-epoxy PCB) .

●ELECTRICAL CHARACTERISTICS (Unless otherwise noted, Ta=25°C, V3AUX\_IN =V3\_IN=3.3V, V15\_IN=1.5V VEN=OPEN,VSYSR=OPEN,CPPE#=0V,CPUSB#=OPEN,PERST\_IN#=OPEN)

| Parameter                       | Symbol                 |       | Limits | T   | Unit | Condition                        |

|---------------------------------|------------------------|-------|--------|-----|------|----------------------------------|

|                                 |                        | MIN   | TYP    | MAX |      |                                  |

| Standby Current                 | IST                    | -     | 40     | 80  | μΑ   | VEN=0V<br>(Include IEN, IRCLKEN) |

| Bias Current 1                  | lcc1                   | -     | 100    | 250 | μΑ   | VSYSR=0V,<br>CPPE#=OPEN          |

| Bias Current 2                  | lcc2                   | -     | 250    | 500 | μΑ   |                                  |

| [Enable]                        |                        | 1     |        | T   | T    | 1                                |

| High Level Enable Input Voltage | VENHI                  | 2.0   | -      | 3.6 | V    |                                  |

| Low Level Enable Input Voltage  | VENLOW                 | -0.2  | -      | 0.8 | V    |                                  |

| Enable Pin Input Current        | IEN                    | 10    | -      | 30  | μΑ   | VEN=0V                           |

| [Logic]                         |                        | 1     |        | l   | l    | 1                                |

| High Level Logic Input Voltage  | VLHI                   | 2.0   | -      | -   | V    |                                  |

| Low Level Logic Input Voltage   | VLLOW                  | -     | -      | 0.8 | V    |                                  |

|                                 | ICPPE#                 | -     | 0      | 1   | μΑ   | CPPE#=3.6V                       |

|                                 | IOFFE#                 | 10    | -      | 30  | μΑ   | CPPE#=0V                         |

|                                 | ICPUSB#                | -     | 0      | 1   | μA   | CPUSB#=3.6V                      |

|                                 | 101 00211              | 10    | -      | 30  | μA   | CPUSB#=0V                        |

| Logic Pin Input Current         | ISYSR                  | -     | 0      | 1   | μΑ   | SYSR=3.6V                        |

|                                 |                        | 10    | -      | 30  | μA   | SYSR=0V                          |

|                                 | IPRT_IN#               | -     | 0      | 1   | μA   | PERST_IN#=3.6V                   |

|                                 |                        | 10    | -      | 30  | μA   | PERST_IN#=0V                     |

|                                 | IRCLKEN                | -     | 0      | 1   | μA   | RCLKEN=3.6V                      |

|                                 |                        | 10    | -      | 30  | μA   | RCLKEN=0V                        |

| RCLKEN Low Voltage              | VRCLKEN                | -     | 0.1    | 0.3 | V    | IRCLKEN=0.5mA                    |

| RCLKEN Leak Current             | IRCLKEN                | -     | -      | 1   | μA   | VRCLKEN=3.6V                     |

| [Switch V3AUX]                  |                        |       |        |     |      |                                  |

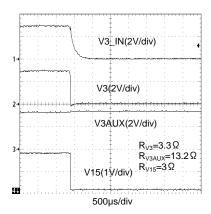

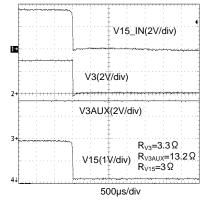

| On Resistance                   | R <sub>V3AUX</sub>     | -     | 140    | 220 | mΩ   | Tj=-10∼100°C                     |

| Discharge On Resistance         | R <sub>V3AUX</sub> Dis | -     | 30     | 150 | Ω    |                                  |

| [Switch V3]                     |                        |       |        |     |      |                                  |

| On Resistance                   | R <sub>V3</sub>        | -     | 50     | 90  | mΩ   | Tj=-10∼100°C                     |

| Discharge On Resistance         | R <sub>V3</sub> Dis    | -     | 30     | 150 | Ω    |                                  |

| [Switch V15]                    |                        |       |        |     |      |                                  |

| On Resistance                   | R <sub>V15</sub>       | -     | 50     | 90  | mΩ   | Tj=-10∼100°C                     |

| Discharge On Resistance         | R <sub>V15</sub> Dis   | -     | 30     | 150 | Ω    |                                  |

| [Over Current Protection]       |                        |       |        |     |      |                                  |

| V3 Over Current                 | OCP <sub>V3</sub>      | 1.3   | -      | -   | А    |                                  |

| V3AUX Over Current              | ОСР <sub>VЗАUX</sub>   | 0.275 | -      | -   | Α    |                                  |

|                                 |                        |       |        |     |      |                                  |

| Davamatav                   | Coursels al                |       | Limits |       | I Imit | Condition                 |

|-----------------------------|----------------------------|-------|--------|-------|--------|---------------------------|

| Parameter                   | Symbol                     | MIN   | TYP    | MAX   | Unit   | Condition                 |

| [Under Voltage Lockout]     |                            |       |        |       |        |                           |

| V3_IN UVLO OFF Voltage      | VUVLO <sub>V3_IN</sub>     | 2.60  | 2.80   | 3.00  | V      | sweep up                  |

| V3_IN Hysteresis Voltage    | ∠VUVLO <sub>V3_IN</sub>    | 50    | 100    | 150   | mV     | sweep down                |

| V3AUX_IN UVLO OFF Voltage   | VUVLO <sub>V3AUX_IN</sub>  | 2.60  | 2.80   | 3.00  | V      | sweep up                  |

| V3AUX_IN Hysteresis Voltage | ⊿VUVLO <sub>V3AUX_IN</sub> | 50    | 100    | 150   | mV     | sweep down                |

| V15_IN UVLO OFF Voltage     | VUVLO <sub>V15_IN</sub>    | 1.10  | 1.20   | 1.30  | ٧      | sweep up                  |

| V15_IN Hysteresis Voltage   | △VUVLO <sub>V15_IN</sub>   | 50    | 100    | 150   | mV     | sweep down                |

| [POWER GOOD]                |                            |       |        |       |        |                           |

| V3 POWER GOOD Voltage       | PG <sub>V3</sub>           | 2.700 | 2.850  | 3.000 | V      |                           |

| V3AUX POWER GOOD Voltage    | РG <sub>V3AUX</sub>        | 2.700 | 2.850  | 3.000 | ٧      |                           |

| V15 POWER GOOD Voltage      | PG <sub>V15</sub>          | 1.200 | 1.275  | 1.350 | V      |                           |

| PERST# LOW Voltage          | VPERST# <sub>Low</sub>     | -     | 0.01   | 0.1   | V      | I <sub>PERST</sub> =0.5mA |

| PERST# HIGH Voltage         | VPERST# <sub>HIGH</sub>    | 3.0   | -      | -     | V      |                           |

| PERST# Delay Time           | T <sub>PERST#</sub>        | 4     | -      | 20    | ms     |                           |

| PERST# assertion time       | Tast                       | -     | -      | 500   | ns     |                           |

| [OUTPUT RISE TIME]          | [OUTPUT RISE TIME]         |       |        |       |        |                           |

| V3_IN to V3                 | T <sub>V3</sub>            | 0.1   | -      | 3     | ms     |                           |

| V3AUX_IN to V3AUX           | T <sub>V3AUX</sub>         | 0.1   | -      | 3     | ms     |                           |

| V15_IN to V15               | T <sub>V15</sub>           | 0.1   | -      | 3     | ms     |                           |

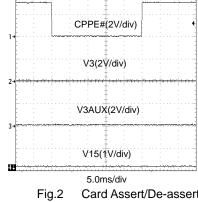

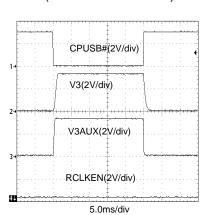

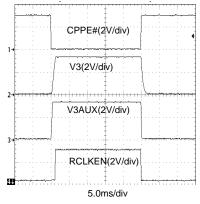

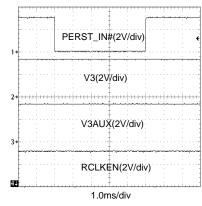

# Reference data CPPE#(2V/div) V3(2V/div) V3AUX(2V/div) V15(1V/div)

5.0ms/div

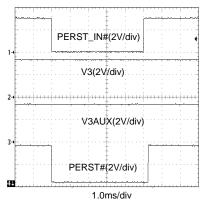

Fig.1 Card Assert/ De-assert

(Active)

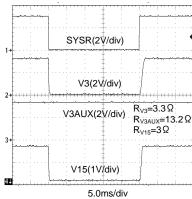

Fig.2 Card Assert/De-assert (Standby)

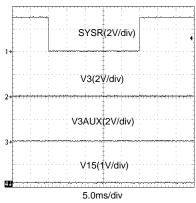

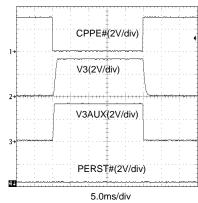

Fig.3 System Active ⇔Standbv( Card Present)

Fig.4 System Active ⇔Standby(No Card)

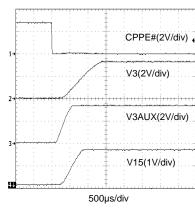

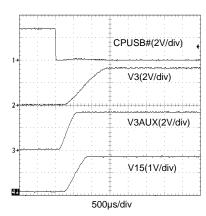

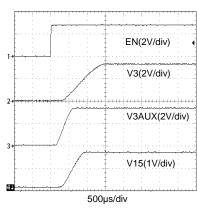

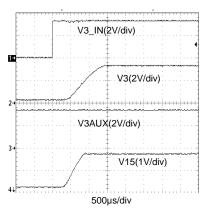

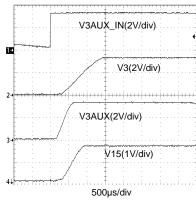

Fig.5 Wakeup Wave Form (Card Assert)

Fig.6 Wakeup Wave Form (USB2.0 Assert)

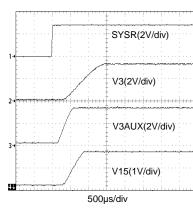

Fig.7 Wakeup Wave Form (Shut Down→Active)

Fig.8 Wakeup Wave Form (Standby→Active)

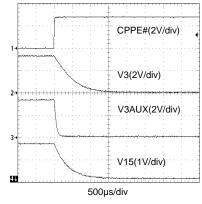

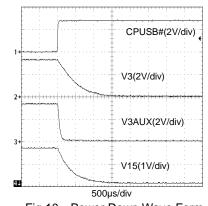

Fig.9 Power Down Wave Form (Card De-assert)

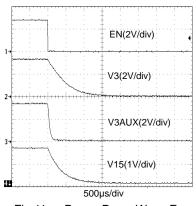

Fig.10 Power Down Wave Form (USB2.0 De-assert)

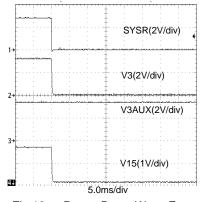

Fig.11 Power Down Wave Form (Active→Shut Down)

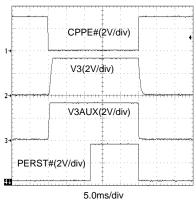

Fig.12 Power Down Wave Form (Active→Standby)

Fig.13 PERST# Wave Form (Card Assert/ De-assert)

Fig.16 RCLKEN Wave Form (USB2.0 Assert/ De-assert)

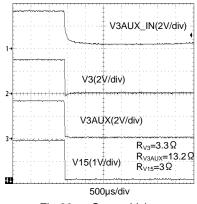

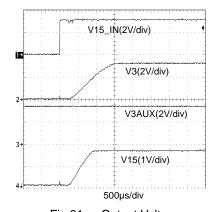

Fig.19 Output Voltage (V3\_IN:OFF→ON)

Fig.22 Output Voltage (V3\_IN:ON→OFF)

Fig.14 RCLKEN Wave Form (Card Assert/ De-assert)

Fig.17 PERST# Wave Form (PERST\_IN# Input)

Fig.20 Output Voltage (V3AUX\_IN:OFF→ON)

Fig.23 Output Voltage (V3AUX\_IN:ON→OFF)

Fig.15 PERST# Wave Form (USB2.0 Assert/ De-assert)

Fig.18 RCLKEN Wave Form (PERST\_IN# Input)

Fig.21 Output Voltage (V15\_IN:OFF→ON)

Fig.24 Output Voltage (V15\_IN:ON→OFF)

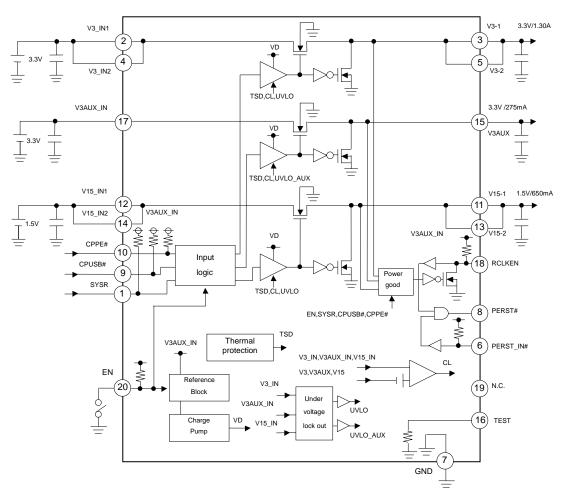

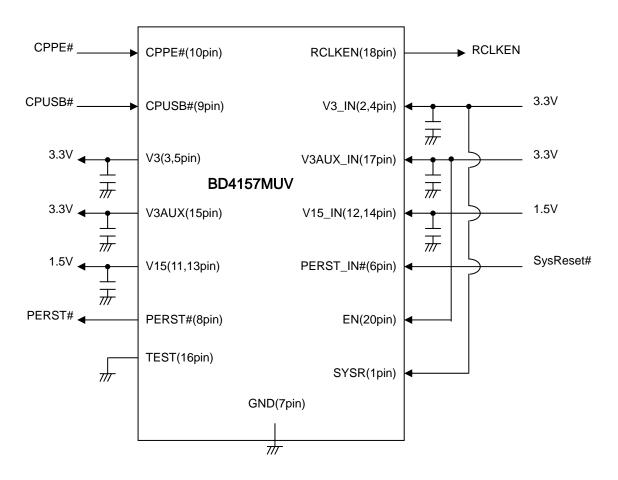

#### ●Block Diagram

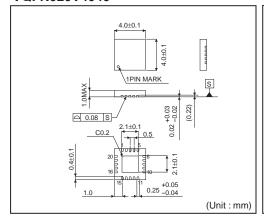

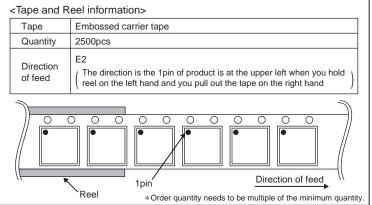

#### Physical Dimensions

●Pin Function

| PIN FUNCTIO | on .      |                                                                |

|-------------|-----------|----------------------------------------------------------------|

| PIN No      | PIN NAME  | PIN FUNCTION                                                   |

| 1           | SYSR      | Logic input pin                                                |

| 2           | V3_IN1    | V3 input pin                                                   |

| 3           | V3-1      | V3 output pin                                                  |

| 4           | V3_IN2    | V3 input pin                                                   |

| 5           | V3-2      | V3 output pin                                                  |

| 6           | PERST_IN# | PERST# control input pin (SysReset#)                           |

| 7           | GND       | GND pin                                                        |

| 8           | PERST#    | Logic output pin                                               |

| 9           | CPUSB#    | Logic input pin                                                |

| 10          | CPPE#     | Logic input pin                                                |

| 11          | V15-1     | V15 output pin                                                 |

| 12          | V15_IN1   | V15 input pin                                                  |

| 13          | V15-2     | V15 output pin                                                 |

| 14          | V15_IN2   | V15 input pin                                                  |

| 15          | V3AUX     | V3AUX output pin                                               |

| 16          | TEST      | Test pin. Must be open or GND.                                 |

| 17          | V3AUX_IN  | V3AUX input pin 1                                              |

| 18          | RCLKEN    | Reference clock enable signal/<br>Power good signal (No delay) |

| 19          | N.C.      | Must be open or GND.                                           |

| 20          | EN        | Enable input pin                                               |

|             | I         | <u> </u>                                                       |

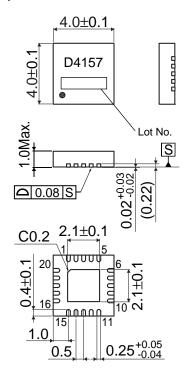

VQFN020V4040 Package (Unit:mm)

#### Description of block operation

#### ΕN

With an input of 2.0 volts or higher, this terminal goes HIGH to activate the circuit, and goes LOW to deactivate the circuit (with the standby circuit current of 40 µA), It discharges each output and lowers output voltage when the input falls to 0.8 volts or less.

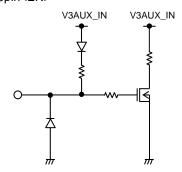

#### V3\_IN, V15\_IN, and V3AUX\_IN

These are the input terminals for each channel of a 3ch switch. V3\_IN and V15\_IN terminals have two pins each, which should be short-circuited on the pc board with a thick conductor. A large current runs through these three terminals : (V3\_IN: 1.3A; V3AUX\_IN: 0.275 A; and V15\_IN: 0.65 A). In order to lower the output impedance of the connected power supply, it is recommended that ceramic capacitors (with B-type characteristics or better) be provided between these terminals and the ground. Specifically, the capacitors should be on the order of 1  $\mu$ F between V3\_IN and GND, and between V15\_IN and GND; and on the order of 0.1  $\mu$ F between V3AUX\_IN and GND.

#### V3, V15, and V3AUX

These are the output terminals for each switch. The V3 and V15 terminals have two pins each, which should be short-circuited on the PC board and connected to an ExpressCard connector with a thick conductor, as short as possible. In order to stabilize the output, it is recommended that ceramic capacitors (with B-type characteristics or better) be provided between these terminals and the ground. Specifically, the capacitors should be on the order of 10  $\mu$ F between V3 and GND, and between V15 and GND; and on the order of 1  $\mu$ F between V3AUX and GND.

#### CPPE#

This pin is used to find whether or not a PCI-Express signal compatible card is present. Turns to "High" level with an input of 2.0 volts or higher, which means that no card is provided, while it turns to "Low" level when the input is lowered to 0.8 volts or less, which means that a card is provided. Controls the ON/OFF, switch selecting the proper mode based on the status of the system. Pull up resistance  $(100k\Omega \sim 200k\Omega)$  is built into, so the number of components is reduced.

#### CPUSB#

This pin is used to find whether or not a USB2.0 signal compatible card is present. Turns to "High" level with an input of 2.0 volts or higher, which means that no card is provided, while it turns to "Low" level when the input is lowered to 0.8 volts or less, which means that a card is provided. Controls the ON/OFF switch, selecting the proper mode based on the system status. Pull up resistance  $(100 \text{k}\Omega \sim 200 \text{k}\Omega)$  is built into, so the number of components is reduced.

#### SYSR

This pin is used to detect the system status. Turns to "High" level with an input of 2.0 volts or higher, which means that the system is activated, while it turns to "Low" level when the input is lowered to 0.8 volts or less, which means that the system is on standby.

#### PERST\_IN#

This pin is used to control the reset signal (PERST#) to a card from the system side. (Also referred to as "SysReset#" by PCMCIA.) Turns to "High" level with an input of 2.0 volts or higher, and sets PERST# to "High" AND with a "Power Good" output. Turns to "Low" level and sets PERST# to "Low" when the input falls to 0.8 volts or less.

#### PERST#

This pin is used to send a reset signal to a PCI-Express compatible card. Reset status is determined by the outputs, PERST\_IN#, CPPE# system status, and EN on/off status. Turns to "High" level and activates the PCI-Express compatible card only if each output is within the "Power Good" threshold, with the card inserted and PERST\_IN# turned to "High" level.

#### **RCLKEN**

This pin is used to send an enable signal to the reference clock. Activation status is determined by the outputs, CPPE# system status, and EN on/off status. Turns to "High" level and activates the reference clock PLL only if each output is within the "Power Good" threshold, with the card kept inserted.

#### TEST

This pin is used to test, which should be short-circuited to the GND. When it is short-circuited to V3AUX\_IN, UVLO (V3\_IN, V15\_IN) turns OFF.

#### ●Timing Chart

# Power ON/OFF Status of ExpressCard<sup>TM</sup>

| System  | Status    | ExpressCard <sup>TM</sup> Module | Power Switch Status          |                         |    |

|---------|-----------|----------------------------------|------------------------------|-------------------------|----|

| Primary | Auxiliary | Status                           | Primary<br>(+3.3V and +1.5V) | Auxiliary<br>(3.3V Aux) |    |

| OFF     | OFF       | Don't care                       | OFF                          | OFF                     |    |

| ON      | ON        | De-asserted                      | OFF                          | OFF                     |    |

| ON      | ON        | V ON                             | Asserted                     | ON                      | ON |

|         |           | De-asserted                      | OFF                          | OFF                     |    |

| ON      | ON        | Asserted Before This             | OFF                          | ON                      |    |

|         |           | Asserted After This              | OFF                          | OFF                     |    |

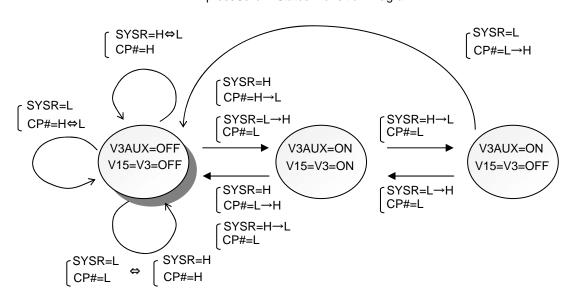

# ExpressCard<sup>TM</sup> States Transition Diagram

| System Status              |           | Card Status                         |          |  |

|----------------------------|-----------|-------------------------------------|----------|--|

| Stand-by Status            | :SYSR=L   | Card Asserted Status                | :CP#=L   |  |

| ON Status                  | :SYSR=H   | Card De-asserted Status             | :CP#=H   |  |

| From ON to Stand-by Status | :SYSR=H→L | From De-asserted to Asserted Status | :CP#=H→L |  |

| From Stand-by to ON Status | :SYSR=L→H | From Asserted to De-asserted Status | :CP#=L→H |  |

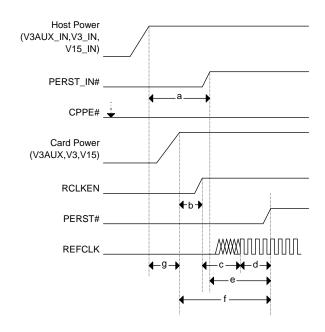

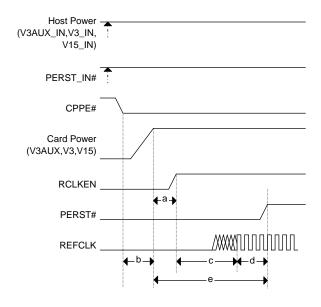

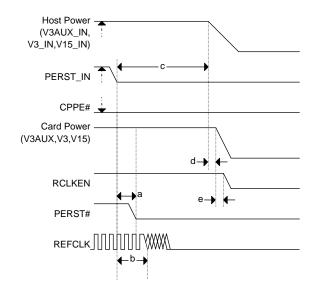

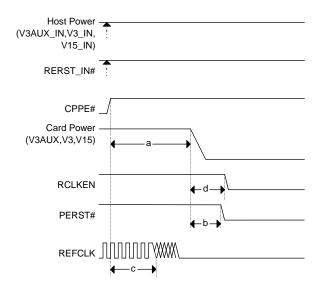

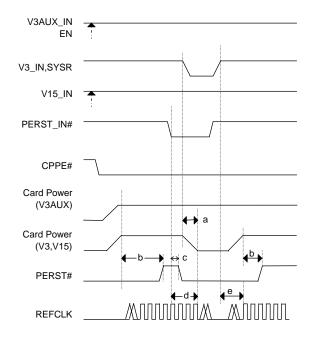

# ●ExpressCard<sup>TM</sup> Timing Diagrams

Timing Signals-Card Present Before Host Power is On

| Tpd | Min      | Max      | Units |

|-----|----------|----------|-------|

| а   | System D | ependent |       |

| b   | -        | 100      | μs    |

| С   | System D |          |       |

| d   | System D |          |       |

| е   | 100      | -        | μs    |

| f   | 4        | 20       | ms    |

| g   | -        | 10       | ms    |

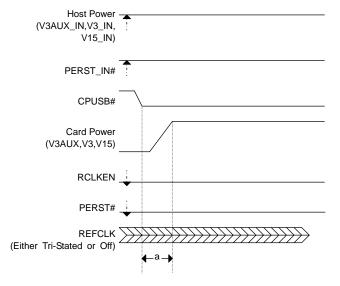

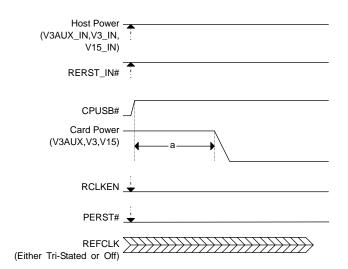

Timing Signals-USB Present Before Host Power is On

| Tpd | Min      | Max | Units |

|-----|----------|-----|-------|

| а   | System D |     |       |

| b   | -        | 10  | ms    |

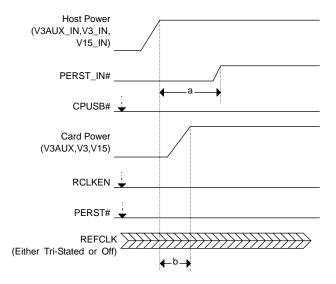

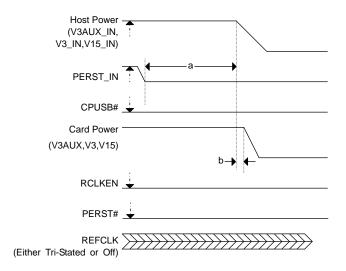

Timing Signals Host Power is On Prior to Card Insertion

| Tpd | Min      | Max              | Units |  |

|-----|----------|------------------|-------|--|

| а   | -        | 100              | μs    |  |

| b   | -        | 10               | ms    |  |

| С   | System D | System Dependent |       |  |

| d   | System D | System Dependent |       |  |

| е   | 4        | 10               | ms    |  |

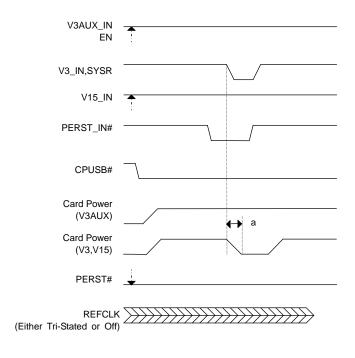

Timing Signals Host Power is On Prior to USB Insertion

| Tpd | Min | Max | Units |

|-----|-----|-----|-------|

| а   | -   | 10  | ms    |

#### Application Information (continued)

Timing Signals-Host System In Standby Prior to Card Insertion

Timing Signals-Host System In Standby Prior to USB Insertion

12/24

2011.06 - Rev.A

Timing Signals Host Controlled Power Down

| Tpd | Min      | Min Max |  |  |

|-----|----------|---------|--|--|

| а   | -        | - 2     |  |  |

| b   | System D |         |  |  |

| С   | System D |         |  |  |

| d   | Load De  |         |  |  |

| е   | -        | - 2     |  |  |

Timing Signals Host Controlled Power Down

| Tpd | Min            | Max | Units |

|-----|----------------|-----|-------|

| а   | System D       |     |       |

| b   | Load Dependent |     |       |

#### Application Information (continued)

Timing Signals Controlled Power Down When EN Asserted

| Tpd | Min      | Min Max        |  |  |

|-----|----------|----------------|--|--|

| а   | Load De  | Load Dependent |  |  |

| b   | System D |                |  |  |

| С   | -        | - 500          |  |  |

| d   | -        | - 2            |  |  |

| е   | System D |                |  |  |

| f   | System D |                |  |  |

Timing Signals Controlled Power Down When EN Asserted

| Tpd | Min Max  |  | Units |

|-----|----------|--|-------|

| а   | Load De  |  |       |

| b   | System D |  |       |

| С   | System D |  |       |

Timing Signals-Surprise Card Removal

| Tpd | Min      | Min Max          |    |  |  |

|-----|----------|------------------|----|--|--|

| а   | Load De  | Load Dependent   |    |  |  |

| b   | -        | - 500            |    |  |  |

| С   | System D | System Dependent |    |  |  |

| d   | -        | 2                | μs |  |  |

Timing Signals-Surprise USB Removal

| Tpd | Min            | Max | Units |

|-----|----------------|-----|-------|

| а   | Load Dependent |     |       |

| Tpd | Min              | Max              | Units |  |  |

|-----|------------------|------------------|-------|--|--|

| а   | System D         | System Dependent |       |  |  |

| b   | 4                | 4 20             |       |  |  |

| С   | -                | - 2              |       |  |  |

| d   | System D         |                  |       |  |  |

| е   | System Dependent |                  |       |  |  |

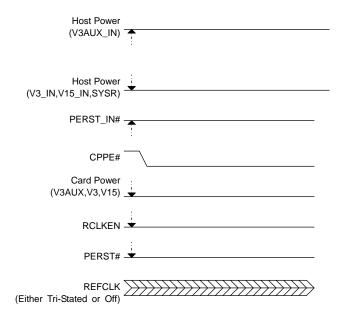

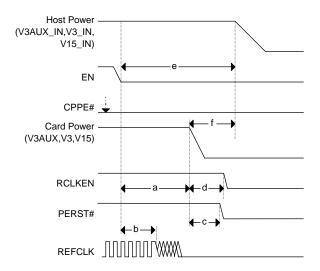

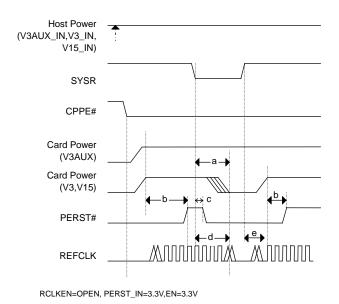

Timing Signals Power state transitions (Signal applies for SYSR)

| Tpd | Min      | Max      | Units |

|-----|----------|----------|-------|

| а   | System D | ependent |       |

RCLKEN=OPEN, PERST\_IN=3.3V,EN=3.3V

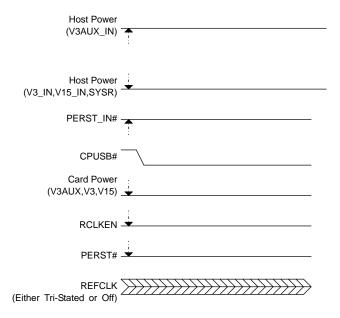

Timing Signals Power state transitions (Signal applies for SYSR)

| Tpd | Min      | Max  | Units |  |  |

|-----|----------|------|-------|--|--|

| а   | System D |      |       |  |  |

| b   | 4        | 4 20 |       |  |  |

| С   | - 2      |      | μs    |  |  |

| d   | System D |      |       |  |  |

| е   | System D |      |       |  |  |

RCLKEN=OPEN, PERST\_IN# is asserted in advance of power changes.

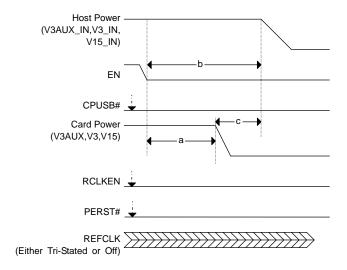

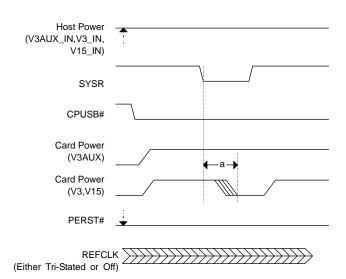

Timing Signals – Power state transitions (SYSR and EN are connected to V3\_IN/V3AUX\_IN.)

| Tpd | Min      | Max              | Units |

|-----|----------|------------------|-------|

| а   | System D | System Dependent |       |

RCLKEN=OPEN, PERST\_IN# is asserted in advance of power changes.

Timing Signals – Power state transitions (SYSR and EN are connected to V3\_IN/V3AUX\_IN.)

●Output Condition List(Output)

| atput contains | ·· = (   |              |        |    |       |       |        |        |       |

|----------------|----------|--------------|--------|----|-------|-------|--------|--------|-------|

| Ctoto          |          | Power Supply | 1      |    | Logic | input |        | Ou     | tput  |

| State          | V3AUX_IN | V3_IN        | V15_IN | EN | SYSR  | CPPE# | CPUSB# | V3/V15 | V3AUX |

| OFF            | 0        | ×            | ×      | ×  | ×     | ×     | ×      | OFF    | OFF   |

| Shut down      | 1        | ×            | ×      | 0  | ×     | ×     | ×      | OFF    | OFF   |

| ON             |          |              |        |    |       | 1     | 1      | OFF    | OFF   |

| $\downarrow$   | 1        | ×            | ×      | 1  | 1→0   | ×     | 0      | OFF    | ON    |

| Stand-by       |          |              |        |    |       | 0     | ×      | OFF    | ON    |

| Stand-by       | 1        | ×            | ×      | 1  | 0     | ×     | ×      | OFF    | OFF   |

|                |          |              |        |    |       | 1     | 1      | OFF    | OFF   |

| ON             | 1        | 1            | 1      | 1  | 1     | ×     | 0      | ON     | ON    |

|                |          |              |        |    |       | 0     | ×      | ON     | ON    |

| State        | Logic     | input         | Logic  | output |

|--------------|-----------|---------------|--------|--------|

| State        | PERST_IN# | RCLKEN(Input) | PERST# | RCLKEN |

| OFF          | ×         | ×             | 0      | 0      |

| Shut down    | ×         | ×             | 0      | 0      |

| Stand-by     | ×         | ×             | 0      | 0      |

| ON(No Card)  | ×         | ×             | 0      | 0      |

|              | 0         | Hiz           | 0      | 0      |

| ON(CPUSB#=0) | 0         | 0             | 0      | 0      |

| ON(CF03B#=0) | 1         | Hiz           | 0      | 0      |

|              | 1         | 0             | 0      | 0      |

|              | 0         | Hiz           | 0      | 1      |

| ON(CPPE#=0)  | 0         | 0             | 0      | 0      |

| ON(GPPE#=0)  | 1         | Hiz           | 1      | 1      |

|              | 1         | 0             | 0      | 0      |

Downloaded from: http://www.datasheetcatalog.com/

● Application Circuit (Circuit for ExpressCard TM Compliance Checklist)

#### Heat loss

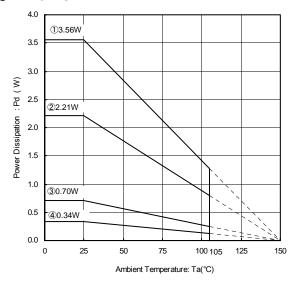

Thermal design should allow the device to operate within the following conditions. Note that the temperatures listed are the allowed temperature limits. Thermal design should allow sufficient margin from these limits.

- 1. Ambient temperature Ta can be no higher than 100°C.

- 2. Chip junction temperature Tj can be no higher more than 150°C.

Chip junction temperature Tj can be determined as follows:

Chip junction temperature Tj is calculated from ambient temperature Ta:  $Tj=Ta+\theta$   $j-a\times W$

<Reference value>

$\theta$  j-c:VQFN020V4040 367.6°C/W IC only 178.6°C/W 1-layer (copper foil density 10.29mm²) 56.6°C/W 4-layer (copper foil density 10.29mm²/ 2,3-layer copper foil density 5505mm²) 35.1°C/W 4-layer (copper foil density 5505mm²) Substrate size  $74.2 \times 74.2 \times 1.6$ mm³ (thermal vias in the board.)

Most of heat loss in the BD4157MUV occurs at the output switch. The power lost is determined by multiplying the on-resistance by the square of output current of each switch.

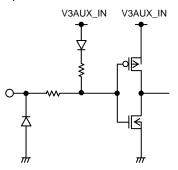

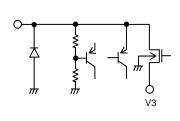

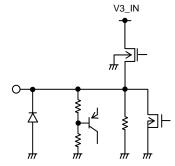

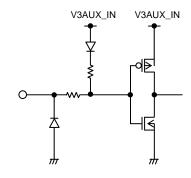

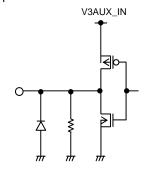

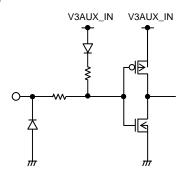

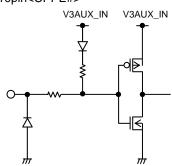

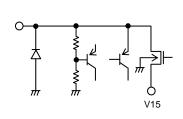

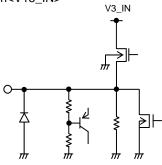

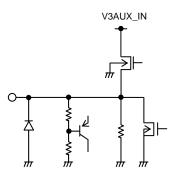

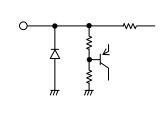

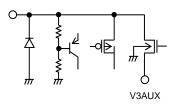

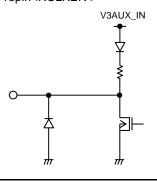

#### ● Equivalent Circuit

. 1pin<SYSR>

2,4pin<V3\_IN>

3,5pin<V3>

6pin<PERST\_IN#>

8pin<PERST#>

9pin<CPUSB#>

10pin<CPPE#>

11,13pin<V15>

12,14pin<V15\_IN>

15pin<V3AUX>

16pin<TEST>

17pin<V3AUX\_IN>

18pin<RCLKEN >

20pin<EN>

#### Notes for use

#### 1. Absolute maximum ratings

Although quality is rigorously controlled, the device may be destroyed when applied voltage, operating temperature, etc. exceeds its absolute maximum rating. Because the source (short mode or open mode) cannot be identified once the IC is destroyed, it is important to take physical safety measures such as fusing when implementing any special mode that operates in excess of absolute rating limits.

#### 2. Thermal design

Consider allowable loss (Pd) under actual operating conditions and provide sufficient margin in the thermal design.

#### 3. Terminal-to-terminal short-circuit and mis-mounting

When the mounting the IC to a printed circuit board, take utmost care to assure the position and orientation of the IC are correct. In the event that the IC is mounted erroneously, it may be destroyed. The IC may also be destroyed when a short-circuit is caused by foreign matter introduced into the clearance between outputs, or between an output and power-GND.

#### 4. Operation in strong electromagnetic fields

Using the IC in strong electromagnetic fields may cause malfunctions. Exercise caution in respect to electromagnetic fields.

#### 5. Built-in thermal shutdown protection circuit

This IC incorporates a thermal shutdown protection circuit (TSD circuit). The working temperature is 175°C (standard value) with a -15°C (standard value) hysteresis width. When the IC chip temperature rises the TSD circuit is activated, while the output terminal is brought to the OFF state. The built-in TSD circuit is intended exclusively to shut down the IC in a thermal runaway event, and is not intended to protect the IC or guarantee performance in these conditions. Therefore, do not operate the IC after with the expectation of continued use or subsequent operation once this circuit is activated.

#### 6. Capacitor across output and GND

When a large capacitor is connected across the output and GND, and the V3AUX\_IN is short-circuited with 0V or GND for any reason, current charged in the capacitor flows into the output and may destroy the IC. Therefore, use a capacitor smaller than 1000  $\mu$ F between the output and GND.

#### Set substrate inspection

Connecting a low-impedance capacitor to a pin when running an inspection with a set substrate may produce stress on the IC. Therefore, be certain to discharge electricity at each process of the operation. To prevent electrostatic accumulation and discharge in the assembly process, thoroughly ground yourself and any equipment that could sustain ESD damage, and continue observing ESD-prevention procedures in all handling, transfer and storage operations. Before attempting to connect the set substrate to the test setup, make certain that the power supply is OFF. Likewise, be sure the power supply is OFF before removing the substrate from the test setup.

#### 8. IC terminal input

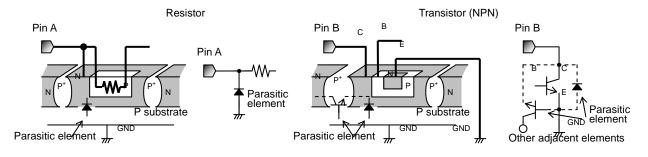

This integrated circuit is a monolithic IC, with P substrate and P<sup>+</sup> isolation between elements.

The P layer and N layer of each element form a, PN junction. When the potential relation is GND>terminal A>terminal B, the PN junction works as a diode, and when terminal B>GND terminal A, the PN junction operates as a parasitic transistor

Parasitic elements inevitably form, due to the nature of the IC construction. The operation of the parasitic element gives rise to mutual interference between circuits and results in malfunction, and eventually, breakdown. Consequently, take utmost care not to use the IC in a way that would cause the parasitic element to actively operate, such as applying voltage lower than GND (P substrate) to the input terminal.

#### 9. GND wiring pattern

If both a small signal GND and a high current GND are present, it is recommended that the patterns for the high current GND and the small signal GND be separated. Proper grounding to the reference point of the set should also be provided. In this way, the small signal GND voltage will by unaffected by the change in voltage stemming from the pattern wiring resistance and the high current. Also, pay special attention to avoid undesirable wiring pattern fluctuations in any externally connected GND component.

#### 10. Electrical characteristics

The electrical characteristics in the Specifications may vary, depending on ambient temperature, power supply voltage, circuit(s) externally applied, and/or other conditions. Therefore, please check all such factors, including transient characteristics, that could affect the electrical characteristics.

#### 11. Capacitors applied to input terminals

The capacitors applied to the input terminals (V3\_IN, V3AUX\_IN and V15\_IN) are used to lower the output impedance of the connected power supply. An increase in the output impedance of the power supply may result in destabilization of input voltages (V3\_IN, V3AUX\_IN and V15\_IN). It is recommended that a low-ESR capacitor be used, with a lower temperature coefficient (change in capacitance vs. change in temperature), Recommended capacitors are on the order of 0.1  $\mu$ F for V3AUX\_IN, and1  $\mu$ F for V3\_IN and V15\_IN. However, they must be thoroughly checked at the temperature and with the load range expected in actual use, because capacitor selection depends to a significant degree on the characteristics of the input power supply to be used and the conductor pattern of the PC board.

#### 12. Capacitors applied to output terminals

Capacitors for the output terminals (V3, V3\_AUX, and V15), should be connected between each of the output terminals and GND. A low-ESR, low temperature coefficient output capacitor is recommended-on the order of 1  $\mu$ F for V3 and V15 terminals, and 1 $\mu$ F less for V3\_AUX. However, they must be thoroughly checked at the temperature and with the load range expected in actual use, because capacitor selection depends to a significant degree on the temperature and the load conditions.

13. Not of a radiation-resistant design.

#### 14. Allowable loss (Pd)

With respect to the allowable loss, please refer to the thermal derating characteristics shown in the Exhibit, which serves as a rule of thumb. When the system design causes the IC to operate in excess of the allowable loss, chip temperature will rise, reducing the current capacity and decreasing other basic IC functionality. Therefore, design should always enable IC operation within the allowable loss only.

#### 15. Operating range

Basic circuit functions and operations are warranted within the specified operating range the working ambient temperature range. Although reference values for electrical characteristics are not warranted, no rapid or extraordinary changes in these characteristics are expected, provided operation is within the normal operating and temperature range.

- 16. The applied circuit example diagrams presented here are recommended configurations. However, actual design depends on IC characteristics, which should be confirmed before operation. Also, note that modifying external circuits may impact static, noise and other IC characteristics, including transient characteristics. Be sure to allow sufficient margin in the design to accommodate these factors.

- 17. Wiring to the input terminals (V3 IN, V3AUX IN, and V15 IN) and output terminals (V3, V3AUX and V15) of the built-in FET should be carried out with special care. Using unnecessarily long and/or thin conductors may decrease output voltage and degrade other characteristics.

#### 18. Heatsink

The heatsink is connected to the SUB, which should be short-circuited to the GND. Proper heatsink soldering to the PC board should enable lower thermal resistance.

Downloaded from: http://www.datasheetcatalog.com/

#### ●Power Dissipation

⊚BD4157MUV

- ①4-layer (copper foil density 5505mm²)  $\theta$  j-a=35.1°C/W

- 4-layer (copper foil density 10.29mm²)

(2,3-layer copper foil density 5505mm²)

θ j-a=56.6°C/W

- 3 1-layer (copper foil density 10.29mm<sup>2</sup>)  $\theta$  j-a=178.6°C/W

- 4IC only

- θ j-a=367.6°C/W

23/24

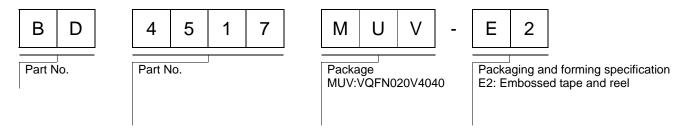

# Ordering part number

#### VQFN020V4040

# **Notice**

#### **Precaution on using ROHM Products**

Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment (Note 1), transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

(Note1) Medical Equipment Classification of the Specific Applications

| JÁP    | AN               | USA      | EU         | CHINA    |

|--------|------------------|----------|------------|----------|

| CLASSⅢ |                  | CLACCIII | CLASS II b | CLASSIII |

| CLAS   | CLASSIV CLASSIII |          | CLASSⅢ     |          |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse. is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7. De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8. Confirm that operation temperature is within the specified range described in the product specification.

- 9. ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

#### Precaution for Mounting / Circuit board design

- 1. When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2. In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the ROHM representative in advance.

For details, please refer to ROHM Mounting specification

Notice - GE © 2014 ROHM Co., Ltd. All rights reserved.

# **Precautions Regarding Application Examples and External Circuits**

- 1. If change is made to the constant of an external circuit, please allow a sufficient margin considering variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- You agree that application notes, reference designs, and associated data and information contained in this document are presented only as guidance for Products use. Therefore, in case you use such information, you are solely responsible for it and you must exercise your own independent verification and judgment in the use of such information contained in this document. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of such information.

#### **Precaution for Electrostatic**

This Product is electrostatic sensitive product, which may be damaged due to electrostatic discharge. Please take proper caution in your manufacturing process and storage so that voltage exceeding the Products maximum rating will not be applied to Products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

#### **Precaution for Storage / Transportation**

- 1. Product performance and soldered connections may deteriorate if the Products are stored in the places where:

- [a] the Products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] the temperature or humidity exceeds those recommended by ROHM

- [c] the Products are exposed to direct sunshine or condensation

- [d] the Products are exposed to high Electrostatic

- 2. Even under ROHM recommended storage condition, solderability of products out of recommended storage time period may be degraded. It is strongly recommended to confirm solderability before using Products of which storage time is exceeding the recommended storage time period.

- 3. Store / transport cartons in the correct direction, which is indicated on a carton with a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- 4. Use Products within the specified time after opening a humidity barrier bag. Baking is required before using Products of which storage time is exceeding the recommended storage time period.

#### **Precaution for Product Label**

QR code printed on ROHM Products label is for ROHM's internal use only.

#### **Precaution for Disposition**

When disposing Products please dispose them properly using an authorized industry waste company.

#### **Precaution for Foreign Exchange and Foreign Trade act**

Since our Products might fall under controlled goods prescribed by the applicable foreign exchange and foreign trade act, please consult with ROHM representative in case of export.

#### **Precaution Regarding Intellectual Property Rights**

- 1. All information and data including but not limited to application example contained in this document is for reference only. ROHM does not warrant that foregoing information or data will not infringe any intellectual property rights or any other rights of any third party regarding such information or data. ROHM shall not be in any way responsible or liable for infringement of any intellectual property rights or other damages arising from use of such information or data.:

- 2. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third parties with respect to the information contained in this document.

#### **Other Precaution**

- 1. This document may not be reprinted or reproduced, in whole or in part, without prior written consent of ROHM.

- 2. The Products may not be disassembled, converted, modified, reproduced or otherwise changed without prior written consent of ROHM.

- In no event shall you use in any way whatsoever the Products and the related technical information contained in the Products or this document for any military purposes, including but not limited to, the development of mass-destruction weapons.

- 4. The proper names of companies or products described in this document are trademarks or registered trademarks of ROHM, its affiliated companies or third parties.

Notice - GE © 2014 ROHM Co., Ltd. All rights reserved.

#### **General Precaution**

- 1. Before you use our Products, you are requested to care fully read this document and fully understand its contents. ROHM shall not be in any way responsible or liable for failure, malfunction or accident arising from the use of a ny ROHM's Products against warning, caution or note contained in this document.

- 2. All information contained in this docume nt is current as of the issuing date and subject to change without any prior notice. Before purchasing or using ROHM's Products, please confirm the latest information with a ROHM sale s representative.

- 3. The information contained in this document is provided on an "as is" basis and ROHM does not warrant that all information contained in this document is accurate an d/or error-free. ROHM shall not be in an y way responsible or liable for any damages, expenses or losses incurred by you or third parties resulting from inaccuracy or errors of or concerning such information.

Notice – WE © 2014 ROHM Co., Ltd. All rights reserved.