## 5V/10 V Low-Drop Voltage Regulator

### **Functional Description**

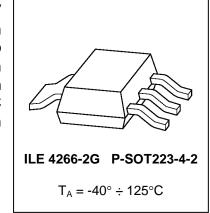

ILE 4266-2 is a low-drop voltage regulator for 5 V or 10 V supply in a P-SOT223-4-2 SMD package. The IC regulates an input voltage V in the range of 5.5 V/10.5 V < V < 45 V to  $V_{\text{Qrated}} = 5 \text{ V/10 V}$ . The maximum output current is more than 120 mA. The IC can be switched off via the inhibit input, which causes the current consumption to drop below 10 uA. The IC is shortcircuit-proof and incorporates temperature protection that disables the IC an overheating.

### Features

- Output voltage 5 V or 10 V

- •Output voltage tolerance  $\leq \pm 2$  %

- •120 mA current capability

- Very low current consumption

- Low-drop voltage

- Overtemperature protection

- •Reverse polarity proof

- •Wide temperature range

- Suitable for use in automotive electronics

- Inhibit

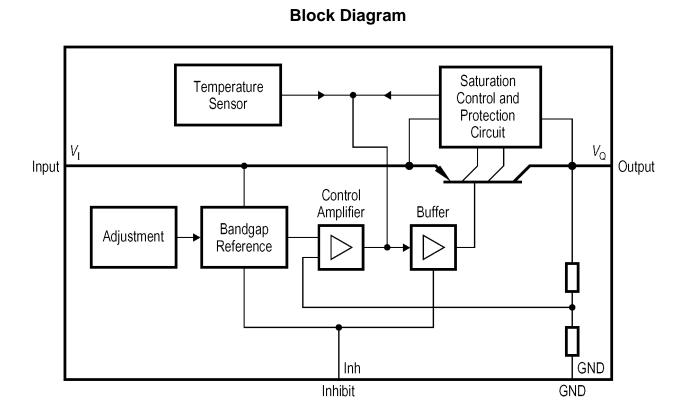

## **Dimensioning Information on External Components**

The input capacitor  $C_1$  is necessary for compensating line influences. Using a resistor of approx. 1 Ohm in series with  $C_1$ , the oscillating of input inductivity and input capacitance can be clamped. The output capacitor  $C_Q$  is necessary for the stability of the regulating circuit. Stability is guaranteed at values  $C_Q \ge 10$  uF and an ESR  $\le 10$  Ohm within the operating temperature range.

## **Pin Definitions and Functions**

| Pin | Symbol  | Function                                                                    |  |  |  |

|-----|---------|-----------------------------------------------------------------------------|--|--|--|

| 1   | Vı      | Input voltage; block to ground directly at the IC with a ceramic capacitor. |  |  |  |

| 2   | Inh     | Inhibit; low-active input.                                                  |  |  |  |

| 3   | $V_{Q}$ | <b>Output voltage;</b> block to ground with a capacitor. <i>C</i> ≥10 uF.   |  |  |  |

| 4   | GND     | Ground                                                                      |  |  |  |

#### **PIN CONFIGURATION**

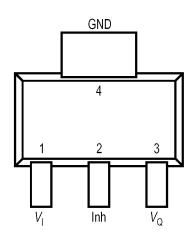

### **Circuit Description**

The device produces a precise reference voltage, that is very accurate due to resistor adjustment. A control amplifier compares the divided output voltage to this reference voltage and drives the base of the PNP series transistor through a buffer. Saturation control as a function of the load current prevents any oversaturation of the power element. The IC also incorporates a number of protection circuitry for:

- Overload

- Overtemperature

- Reverse polarity

16

internally

limited

45

25\*

100\*

220\*

| Ja | nuary, 201 | 11, Rev. 01 |

|----|------------|-------------|

| Parameter Symbol                     | Unit | Maximu | m Ratings  | Absolute Maximum<br>Ratings |            |

|--------------------------------------|------|--------|------------|-----------------------------|------------|

| -                                    |      | min.   | max.       | min.                        | max.       |

| Junction temperature, T <sub>J</sub> | °C   | -40    | 125        | -40                         | 150        |

| Storage temperature, Ts              | °C   | -      | -          | -50                         | 150        |

| Input voltage, V <sub>1</sub>        | V    | 6      | 28         | -42                         | 45         |

| Input current, I <sub>I</sub>        | A    | -      | internally | -                           | internally |

|                                      |      |        | limited    |                             | limited    |

mΑ

V

A

V

°C /W

°С/Вт

4,9

-

-

## Maximum & Absolute Maximum Ratings

\* Thermal resistance junction ambient for IC with heat dissipater is calculated by formula: (1)

$R_{\rm th\,ja} = R_{\rm th\,jc} + R_{\rm th\,ca} ,$

- without heat dissipater

Current on common pin, IGND

Thermal resistance junction case,

Thermal resistance junction ambient,

Output voltage, U<sub>Q</sub>

Output current (pin 3)

Inhibit voltage, UINH

$\mathsf{R}_{\mathsf{th}\,\mathsf{jc}}$

R<sub>th ja</sub>, - on PCB.

$\bar{R}_{th\,jc}$  - thermal resistance junction case, °C /W.

Application circuit and heat dissipater have to provide  $T_J \le 125$  °C.

Maximum power  $P_{tot}$ , BT, dissipated by IC for  $T_A$ , is calculated by formula:

$P_{tot} = (125 - T_A) / R_{th ja}$ ,

125 – maximum permitable operating junction temperature, <sup>o</sup>C.

\* Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

VI = 13.5 V; − 40 °C ≤Tj ≤ 125 °C

|                           |                       | Limit Values |      |       |      |                                                              |  |

|---------------------------|-----------------------|--------------|------|-------|------|--------------------------------------------------------------|--|

| Parameter                 | Symbol                | min.         | typ. | max.  | Unit | Test Condition                                               |  |

| Output voltage            | V <sub>Q</sub>        | 4.9          | 5    | 5.1   | V    | 5 mA ≤I <sub>Q</sub> ≤ 100 mA<br>6 V ≤Vi ≤ 28 V              |  |

| Output-current limitation | Ι <sub>Q</sub>        | 120          | 150  | _     | mA   | -                                                            |  |

| Current consumption       | I <sub>q</sub>        | -            | 0    | 10    | uA   | $V_{INH}$ = 0 V; Tj $\leq$ 100 °C                            |  |

| $I_q = I_I - I_Q$         |                       | _            | -    | 400   | uA   | $I_Q = 1 \text{ mA Inhibit ON}$                              |  |

|                           |                       | _            | 10   | 15    | mA   | $I_Q = 100 \text{ mA Inhibit ON}$                            |  |

| Drop voltage              | V <sub>Dr</sub>       | -            | 0.25 | 0.5   | V    | $I_{Q} = 100 \text{ mA}^{1}$                                 |  |

| Load regulation           | $\Delta V_Q$          | -            | -    | 40    | mV   | $I_Q = 5 \text{ to } 100 \text{ mA}$<br>V <sub>1</sub> = 6 V |  |

| Supply-voltage regulation | ΔV <sub>Q</sub>       | -            | 15   | 30    | mV   | $V_1 = 6 V \text{ to } 28 V$<br>$I_0 = 5 \text{ mA}$         |  |

| Supply-voltage rejection  | SVR                   | -            | 54   | -     | dB   | fr = 100 Hz,<br>Vr = 0.5 V <sub>SS</sub>                     |  |

| Inhibit                   |                       |              |      |       |      |                                                              |  |

| Inhibit on voltage        | V <sub>INH, on</sub>  | 3.5          | _    | _     | V    | _                                                            |  |

| Inhibit off voltage       | V <sub>INH, off</sub> | -            | _    | - 0.8 | V    | -                                                            |  |

| Inhibit current           | I <sub>INH</sub>      | 5            | 15   | 25    | uA   | Ve = 5 V                                                     |  |

<sup>1)</sup> Drop voltage =  $V_1 - V_Q$  (measured when the output voltage VQ has dropped 100 mV from the nominal value obtained at  $V_1 = 13.5$  V).

(2)

50

-1

-

-42

\_

15

5,1

internally

limited

25\*

100\*

220\*

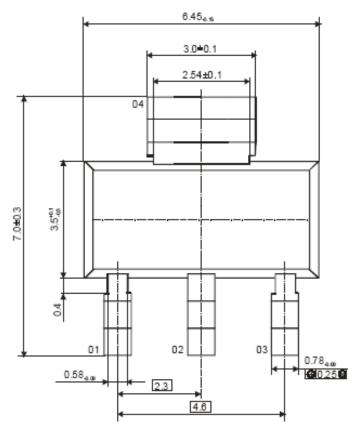

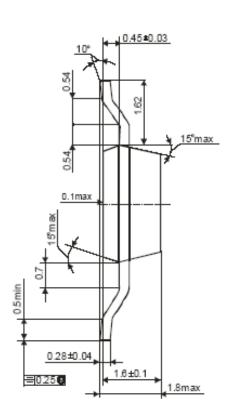

# Package Dimension