Features

design flexibility.

# 3/2/1+2/1-Phase Driver Embedded PWM Controller with SMBus Digital Interface Control for IMVP8

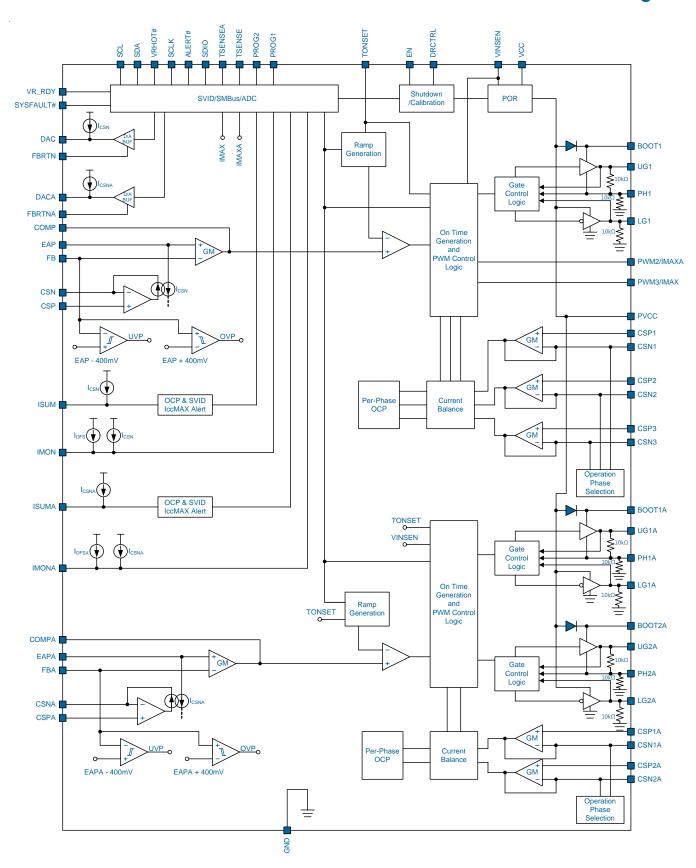

### **General Description**

The uP9506 is an IMVP8 compliant desktop CPU voltage regulator controller that integrates a 3-phase PWM controller for Vcore and a 2-phase controller for VccGT. The Vcore controller can be configured as 3/2/1-phase, and the VccGT controller can be configured as 2/1-phase for platform power design flexibility. This part integrates 3 bootstrap diode embedded 12V MOSFET drivers. For the typical 3+2-phase application, the 3-phase Vcore controller has one embedded MOSFET driver and two PWM outputs. The 2-phase VccGT controller has 2 embedded MOSFET drivers. The integrated SMBus interface programmability makes this part with high performance and easy design. Designer can define different power scenario for different current states to optimize the performance and efficiency. The uP9506 combines true differential output voltage sense, differential inductor DCR current sense, input voltage feedforward sense and adaptive voltage positioning to provide accurately regulated power for desktop CPU. It adopts uPI's proprietary RCOT+™ (Robust Constant On-Time) topology to have fast transient response and smooth mode transition. Similar to digital based PWM controller, the loop gain is also programmable by SMBus interface to achieve

The uP9506 provides VR\_RDY indicator and selectable VR parameters, such as SVID VR address, SMBus device address and Vboot voltage. It also provides complete fault protection functions, including over voltage, under voltage, over current, over temperature and under voltage lockout. The uP9506 is available in VQFN7x7 - 60L package.

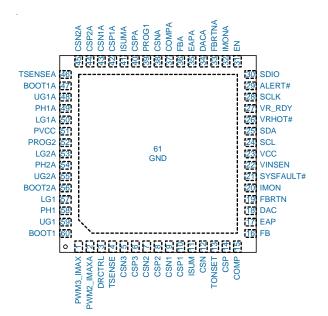

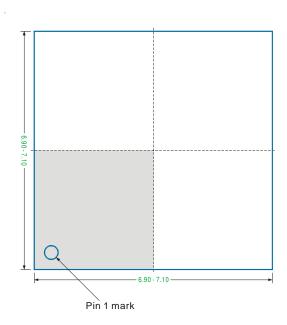

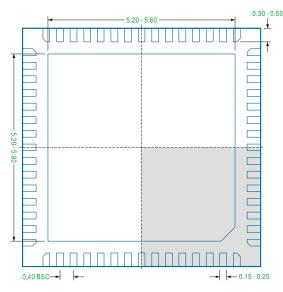

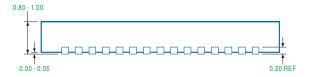

### Pin Configuration

Intel IMVP8 Compatible

- Support S-Line Desktop CPU

- Thermal Sense with VRHOT# Indication

- RCOT+™ Control Topology

- Easy Setting

- Smooth Mode Transition

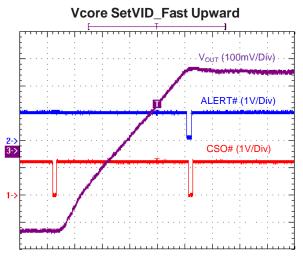

- Fast Transition Response

- 3 Integrated 12V MOSFET Drivers

- Embedded Bootstrap Diode

- 3+2 Phase: 1 driver for Vcore, 2 drivers for VccGT

- External MOSFET Driver Enable Control

- Support Operation Phase Disable Function

- Vcore: 3/2/1-Phase

- VccGT: 2/1-Phase

- Build-in ADC for Platform Parameter Setting

- Selectable SVID VR Address

- Selectable SMBus Device Address

- Selectable Vboot Voltage

- SMBus Interface for Performance and Efficiency Optimization

- Dynamic Programmable VR Parameters

- Programmable Protection Thresholds

- VR Output Reporting

- Programmable Loop Gain

- Enable Control and VR RDY Indicator

- System Thermal Management

- Differential Remote Voltage Sense

- Differential Current Balance Sense Amplifier

- OCP/OVP/UVP/Thermal Shutdown

- RoHS Compliant and Halogen Free

#### Applications

Desktop PC CPU Power Supplies

#### **Ordering Information**

| Order Number | Package       | Top Marking |  |  |

|--------------|---------------|-------------|--|--|

| uP9506PQGZ   | VQFN7x7 - 60L | uP9506P     |  |  |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 and RoHS requirements. They are 100% matte tin (Sn) plating and suitable for use in SnPb or Pb-free soldering processes.

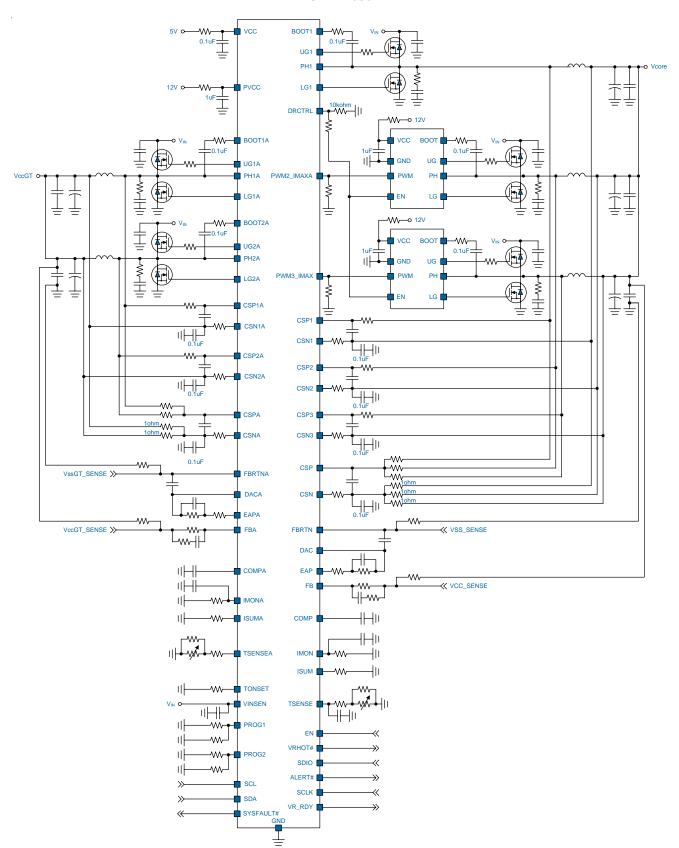

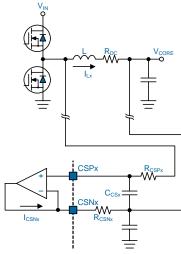

### **Typical Application Circuit**

#### 3+2 Phase

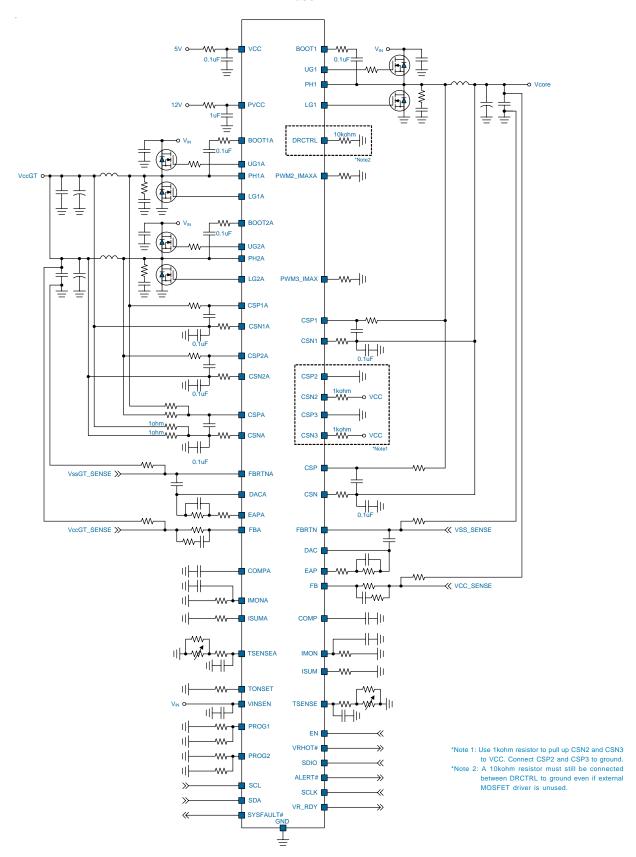

### **Typical Application Circuit**

#### 1+2 Phase

| This pin is a multi-functional pin. It outputs a PWM logic signal for external discrete MOSFET driver for Vcore rail and it is also used to set the Vcore SVID register content. Phase 3 PWM Output. Connect this pin to the PWM input of external MOSFET driver. IMAX Setting Input for Vcore. Connect a resistor from this pin to GND to set the SVID lockMAX register (0x21h) value for Vcore rail.  This pin is a multi-functional pin. It outputs a PWM logic signal for external discrete MOSFET driver for Vcore rail and it is also used to set the VccCT SVID register content. Phase 2 PWM Output. Connect this pin to PWM input of external MOSFET driver. IMAXA Setting Input for VccGT. Connect a resistor from this pin to GND to set the SVID locMAX register (0x21h) value for VccGT rail.  MOSFET Driver Enable Control Output. This pin is a multi-functional pin. It is used to enable/disable all external discrete MOSFET drivers. Connect a 10kΩ resistor from this pin to ground and place this resistor close to the controller. Do not use any other resistance value. Do not connect amy capacitor directly to this pin. PCB trace routing of this pin has special consideration. Refer to the related section in Application Information for detail.  TSENSE  TSENSE  TOTHER Monitoring Input for Vcore. Connect a specified negative temperature coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature coefficient (NTC) thermistor network from this pin to GND for Vcore Phase 3. When Vcore phase 3 is not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM3 to let Vcore VR operate in 2-phase configuration.  Regative Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase conf | No.  | Name       | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM3_MAX   PWM0_Uput_Connect this pin to the PWM input of external MOSFET driver.   MAX Setting Input for Vcore. Connect a resistor from this pin to the deverage MOSFET driver.   MAX Setting Input for Vcore rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 140. | Hame       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

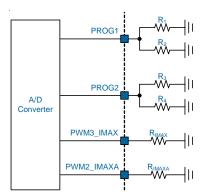

| PWM2_MAXA   Postitive   Process   Postitive   Posti   | 1    | PWM3_IMAX  | MOSFET driver for Vcore rail and it is also used to set the Vcore SVID register content.  Phase 3 PWM Output. Connect this pin to the PWM input of external MOSFET driver.  IMAX Setting Input for Vcore. Connect a resistor from this pin to GND to set the SVID                                                                                                                                                                                                                                                                                    |

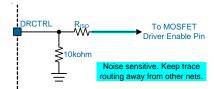

| PRCTRL   enable/disable all external discrete MOSFET drivers. Connect a 10kΩ resistor from this pin to ground and place this resistor close to the controller. Do not use any other resistance value. Do not connect any capacitor directly to this pin. PCB trace routing of this pin has special consideration. Refer to the related section in Application Information for detail.    Thermal Monitoring Input for Vcore. Connect a specified negative temperature coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature sensing. Recommend to use 100kΩ/β = 4250 NTC thermistor by Murata (NCP15WF104F03RC). See the related section in Application Information for detail.    Negative Differential Current Sense Input for Vcore Phase 3. When Vcore phase 3 is not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM3 to let Vcore VR operate in 2-phase configuration.    Positive Differential Current Sense Input for Vcore Phase 3. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in 2-phase configuration.    Negative Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to VCC through a 1kΩ resistor to disable PWM2 to let Vcore VR operate in single-phase configuration.    Positive Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase configuration.    Positive Differential Current Sense Input for Vcore Phase 1.    Positive Differential Current Sense Input for Vcore Phase 1.    Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pi   | 2    | PWM2_IMAXA | MOSFET driver for Vcore rail and it is also used to set the VccGT SVID register content.  Phase 2 PWM Output. Connect this pin to PWM input of external MOSFET driver.  IMAXA Setting Input for VccGT. Connect a resistor from this pin to GND to set the SVID                                                                                                                                                                                                                                                                                       |

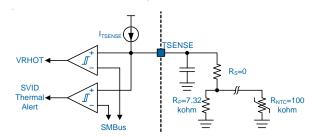

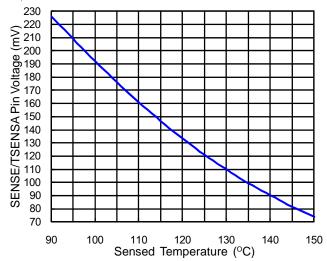

| TSENSE coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature sensing. Recommend to use 100kΩ/β = 4250 NTC thermistor by Murata (NCP15WF104F03RC). See the related section in Application Information for detail.  Negative Differential Current Sense Input for Vcore Phase 3. When Vcore phase 3 is not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM3 to let Vcore VR operate in 2-phase configuration.  Positive Differential Current Sense Input for Vcore Phase 3. When Vcore phase 3 is not used, short this pin to GND when Vcore VR is configured in 2-phase configuration.  Negative Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM2 to let Vcore VR operate in single-phase configuration.  Positive Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase configuration.  Positive Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase configuration.  Negative Differential Current Sense Input for Vcore Phase 1.  Positive Differential Current Sense Input for Vcore Phase 1.  Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.5V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  PWM On-time Setting. Connect a resistor fro | 3    | DRCTRL     | enable/disable all external discrete MOSFET drivers. Connect a $10k\Omega$ resistor from this pin to ground and place this resistor close to the controller. Do not use any other resistance value. Do not connect any capacitor directly to this pin. PCB trace routing of this pin has special consideration. Refer to the related section in Application Information                                                                                                                                                                              |

| CSN3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4    | TSENSE     | coefficient (NTC) thermistor network from this pin to GND for Vcore VR temperature sensing. Recommend to use $100k\Omega/\beta=4250$ NTC thermistor by Murata                                                                                                                                                                                                                                                                                                                                                                                        |

| not used, short this pin to GND when Vcore VR is configured in 2-phase configuration.  Negative Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM2 to let Vcore VR operate in single-phase configuration.  Positive Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase configuration.  Negative Differential Current Sense Input for Vcore Phase 1.  Negative Differential Current Sense Input for Vcore Phase 1.  Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the locmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  TONSET  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5    | CSN3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7 CSN2 not used, pull high this pin to VCC through a 1kΩ resistor to disable PWM2 to let Vcore VR operate in single-phase configuration.  Positive Differential Current Sense Input for Vcore Phase 2. When Vcore phase 2 is not used, short this pin to GND when Vcore VR is configured in single-phase configuration.  9 CSN1 Negative Differential Current Sense Input for Vcore Phase 1.  10 CSP1 Positive Differential Current Sense Input for Vcore Phase 1.  Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  12 CSN Inverting Input of Total Current Sense Amplifier for Vcore.  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6    | CSP3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| not used, short this pin to GND when Vcore VR is configured in single-phase configuration.  Negative Differential Current Sense Input for Vcore Phase 1.  CSP1 Positive Differential Current Sense Input for Vcore Phase 1.  Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  CSN Inverting Input of Total Current Sense Amplifier for Vcore.  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7    | CSN2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10 CSP1 Positive Differential Current Sense Input for Vcore Phase 1.  Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  12 CSN Inverting Input of Total Current Sense Amplifier for Vcore.  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8    | CSP2       | not used, short this pin to GND when Vcore VR is configured in single-phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

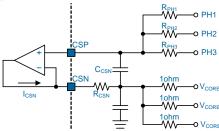

| Over Current Protection Threshold Setting and Sensing for Vcore. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  12 CSN Inverting Input of Total Current Sense Amplifier for Vcore.  13 TONSET PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9    | CSN1       | Negative Differential Current Sense Input for Vcore Phase 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of 1.5V, default), the over current protection will be tripped to shutdown the controller.  12 CSN Inverting Input of Total Current Sense Amplifier for Vcore.  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10   | CSP1       | Positive Differential Current Sense Input for Vcore Phase 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

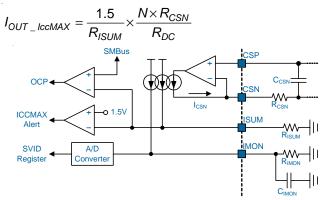

| TONSET  PWM On-time Setting. Connect a resistor from this pin to GND to set the PWM on-time. The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11   | ISUM       | resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUM voltage proportional to the total output current. When the voltage on ISUM pin exceeds 1.5V, only the ALERT# will be pulled low to issue the Iccmax alert through SVID interface. When the voltage on ISUM pin exceeds 1.95V (130% of |

| The Vcore VR and VccGT VR share the same PWM on-time setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12   | CSN        | Inverting Input of Total Current Sense Amplifier for Vcore.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14 CSP Non-Inverting Input of Total Current Sense Amplifier for Vcore.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13   | TONSET     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14   | CSP        | Non-Inverting Input of Total Current Sense Amplifier for Vcore.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| No. | Name      | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | COMP      | Output of Control Loop Error Amplifier for Vcore. Connect a capacitor from this pin to GND for voltage control loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

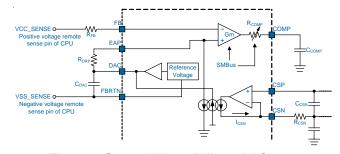

| 16  | FB        | Inverting Input of the Error Amplifier for Vcore.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17  | EAP       | Non-inverting Input of the Error Amplifier for Vcore. Connect a resistor between this pin and DAC to set the droop (load line) function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18  | DAC       | <b>DAC Output for Vcore.</b> The output voltage of this pin is the reference voltage for the Vcore rail. DAC voltage is measured with respect to FBRTN. Connect a capacitor from this pin to FBRTN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19  | FBRTN     | Output Voltage Feedback Return for Vcore. Inverting input to the differential voltage sense amplifier. FBRTN is the reference point in DAC output voltage measurement. Connect this pin directly to the processor output voltage feedback return sense point, namely VSS_SENSE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

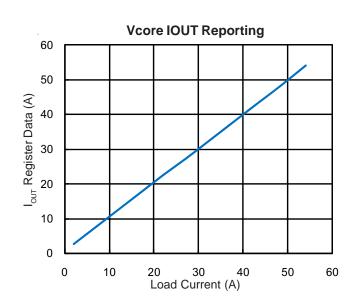

| 20  | IMON      | Output Current Monitor for Vcore. Connect a resistor from this pin to GND to implement digital output current reporting function for Vcore VR. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the IMON voltage proportional to the total output current. The built-in analog-to-digital converter (ADC) converts the IMON voltage to digital content for output current reporting via SVID interface. A capacitor can be connected from IMON to GND to adjust the response time of IMON. See the related section in functional description for IMON capacitor selection. Note that the IMON is used only for digital output current reporting. See the related section in functional description for IMON capacitor selection. |

| 21  | SYSFAULT# | SYSFAULT# Indicator. System fault indicator. This pin is an open-drain output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

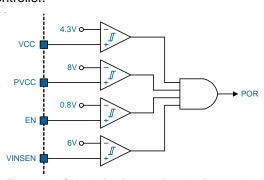

| 22  | VINSEN    | <b>Power Stage Input Voltage Sense.</b> Directly connect this pin to the power stage input $V_{\mathbb{N}}$ . The controller senses the voltage on this pin for power stage input voltage $V_{\mathbb{N}}$ detection. The VINSEN voltage is also used for PWM on-time calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23  | VCC       | Supply Input for Logic Control Circuit. Connect this pin to a 5V voltage source via an RC filter. VCC is the supply input for the logic control circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24  | SCL       | SMBus Clock Input. This pin receives serial bus clock signal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25  | SDA       | SMBus Data Input. This pin is input or output of serial bus data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 26  | VRHOT#    | <b>SVID Thermal Indicator.</b> This pin is an open drain structure and it is active low. The controller asserts VRHOT# to indicate the platform that the VR temperature is higher than the threshold in the 0x22h and 0x38h registers programmed by SMBus. Default value of VRHOT# assertion is 106°C, and the default value of SVID thermal alert is 103°C. The VRHOT# assertion threshold can be programmed through SMBus.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

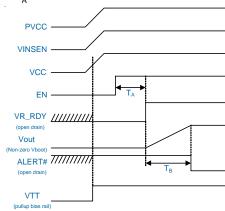

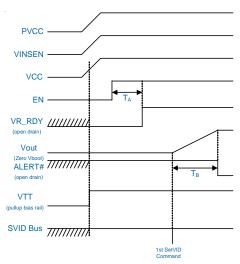

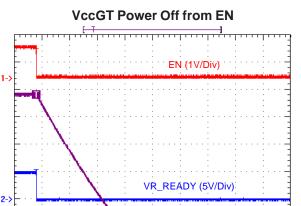

| 27  | VR_RDY    | VR Ready Indicator. This pin is an open drain structure and it is active high. Pull up this pin through a proper resistor to a voltage source. The controller asserts VR_RDY (goes high) to indicate that the controller is ready to accept SVID command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28  | SCLK      | SVID Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 29  | ALERT#    | SVID Alert# Line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 30  | SDIO      | SVID Data I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 31  | EN        | <b>Chip Enable Control Input.</b> Pull this pin above 0.8V enables the chip. Pull this pin below 0.3V to disable the chip. It's typically connected to the output of the VTT voltage power rail on the mother board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| No. | Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

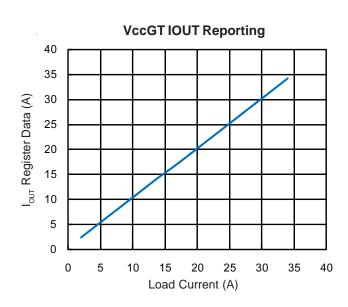

| 32  | IMONA  | Output Current Monitor for VccGT. Connect a resistor from this pin to GND to implement digital output current reporting function for VccGT VR. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the IMONA voltage proportional to the total output current. The built-in analog-to-digital converter (ADC) converts the IMONA voltage to digital content for output current reporting via SVID interface. A capacitor can be connected from IMONA to GND to adjust the response time of IMONA. Note that the IMONA is used only for digital output current reporting. See the related section in functional description for IMONA capacitor selection. |

| 33  | FBRTNA | Output Voltage Feedback Return for VccGT. Inverting input to the differential voltage sense amplifier. FBRTNA is the reference point in DACA output voltage measurement. Connect this pin directly to the processor output voltage feedback return sense point, namely VSSGT_SENSE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 34  | DACA   | DAC Output for VccGT. The output voltage of this pin is the reference voltage for the VccGT rail. DACA voltage is measured with respect to FBRTNA. Connect a capacitor from this pin to FBRTNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 35  | EAPA   | Non-Inverting Input of the Error Amplifier for VccGT. Connect a resistor between this pin and DACA to set the droop (load line) function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 36  | FBA    | Inverting Input of the Error Amplifier for VccGT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 37  | COMPA  | Output of Control Loop Error Amplifier for VccGT. Connect a capacitor from this pin to GND for voltage control loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 38  | CSNA   | Inverting Input of Total Current Sense Amplifier for VccGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 39  | PROG1  | Function Setting Pin 1. This pin is used to set SVID VR address. Connect a resistor from this pin to GND to select the SVID VR address for the two voltage regulators. The SVID VR address of [Vcore/VccGT] can be set as [00, 01], [01, 00], [00, 02] or [01, 03]. Refer to the related section in Application Information for detail and strictly follow the recommended setting.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 40  | CSPA   | Non-Inverting Input of Total Current Sense Amplifier for VccGT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 41  | ISUMA  | Over Current Protection Threshold Setting and Sensing for VccGT. Connect a resistor from this pin to GND to set the over current protection threshold. Do not connect any capacitor to this pin. The output current of this pin is proportional to the total load current. The total load current is sensed and flows out of this pin, and a resistor from this pin to GND makes the ISUMA voltage proportional to the total output current. When the voltage on ISUMA pin exceeds 1.5V, only the ALERT# will be pulled low to issue the lccmax alert through SVID interface. When the voltage on ISUMA pin exceeds 1.95V (130% of 1.5V), the over current protection will be tripped to shutdown the controller.                                                                     |

| 42  | CSP1A  | Positive Differential Current Sense Input for VccGT Phase 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43  | CSN1A  | Negative Differential Current Sense Input for VccGT Phase 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 44  | CSP2A  | Positive Differential Current Sense Input for VccGT Phase2. To disable the MOSFET driver of this phase (BOOT2A, UG2A, PH2A, LG2A), short this pin to GND. Refer to the related section in Application Information for detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 45  | CSN2A  | Negative Differential Current Sense Input for VccGT Phase2. To disable the MOSFET driver of this phase (BOOT2A, UG2A, PH2A, LG2A), pull high this pin to VCC through a $1k\Omega$ resistor to disable this phase. Refer to the related section in Application Information for detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | I       |                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                           |

| 46  | TSENSEA | Thermal Monitoring Input for VccGT. Connect a specified negative temperature coefficient (NTC) thermistor network from this pin to GND for VccGT VR temperature sensing. Recommend to use $100 k\Omega/\beta = 4250$ NTC thermistor by Murata (NCP15WF104F03RC). See the related section in Application Information for detail.                                                                        |

| 47  | BOOT1A  | Bootstrap Supply for Upper Gate Driver for VccGT Phase 1. This pin is the supply input for the upper MOSFET gate driver. Connect the bootstrap capacitor $C_{\text{BOOT}}$ between BOOT1A pin and PH1A pin. The bootstrap capacitor provides the charge to turn on the upper MOSFET. Use at least 0.1uF MLCC as $C_{\text{BOOT}}$ , and make sure $C_{\text{BOOT}}$ is placed close to the controller. |

| 48  | UG1A    | <b>Upper Gate Driver Output for VccGT Phase 1.</b> Connect this pin to the gate of upper MOSFET. This pin is monitored by the shoot-through protection circuitry to determine when to turn on/off upper MOSFET.                                                                                                                                                                                        |

| 49  | PH1A    | Switch Node for VccGT Phase 1. Connect this pin to the joint of upper MOSFET source, inductor and lower MOSFET drain. This pin is used as the return ground for upper MOSFET floating drive. Voltage on this pin is monitored by the shoot-through protection circuitry to determine when to turn on the lower MOSFET.                                                                                 |

| 50  | LG1A    | Lower Gate Driver Output for VccGT Phase 1. Connect this pin to the gate of lower MOSFET. This pin is monitored by the shoot-through protection circuitry to determine when to turn on the upper MOSFET.                                                                                                                                                                                               |

| 51  | PVCC    | Supply Input for Embedded MOSFET Driver. Connect this pin to a 12V voltage source, and bypass this pin to GND with at least 1.0uF MLCC placed very close to the PVCC pin. PVCC is the supply input for the embedded MOSFET drivers.                                                                                                                                                                    |

| 52  | PROG2   | <b>Function Setting Pin 2.</b> This pin is used to set two VR parameters. Connect a resistor from this pin to GND to select the initial start up voltage (Vboot) and the SMBus device address. The Vboot can be set to 0V, 0.8V, 1.05V, 1.2V or 1.5V. The Vcore rail and VccGT rail share the same Vboot setting. The SMBus device address can be set to 0x88h, 0x8Ah or 0x8Ch.                        |

| 53  | LG2A    | Lower Gate Driver Output for VccGT Phase 2. Connect this pin to the gate of lower MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when to turn on the upper MOSFET.                                                                                                                                                                                      |

| 54  | PH2A    | Switch Node for VccGT Phase 2. Connect this pin to the joint of upper MOSFET source, inductor and lower MOSFET drain. This pin is used as the return ground for upper MOSFET floating drive. Voltage on this pin is monitored by the shoot-through protection circuitry to determine when to turn on the lower MOSFET.                                                                                 |