## preliminary

### HIGH-RESOLUTION LINEAR IMAGE SENSORS

Rev B1, Page 1/14

#### **FEATURES**

- 1024/960/640/320 active photo pixels with 12.7 μm x 600 μm (2000 DPI)

- ♦ Pin-selectable resolution of 2000, 1000, 500 and 250 DPI (binning or averaging selectable)

- ♦ Integrating L-V conversion followed by a sample & hold circuit

- ♦ High sensitivity and uniformity over wavelength

- ♦ High pixel clock rate of up to 5 MHz

- ♦ Asynchronous, global shutter enables flexible integration times

- ♦ 3 V capable analogue output with separate supply pin

- ♦ Push-pull output amplifier

#### **APPLICATIONS**

- ♦ Triangulation sensors

- Contact image sensors

- ♦ CCD replacement

### preliminary HIGH-RESOLUTION LINEAR IMAGE SENSORS

Rev B1, Page 2/14

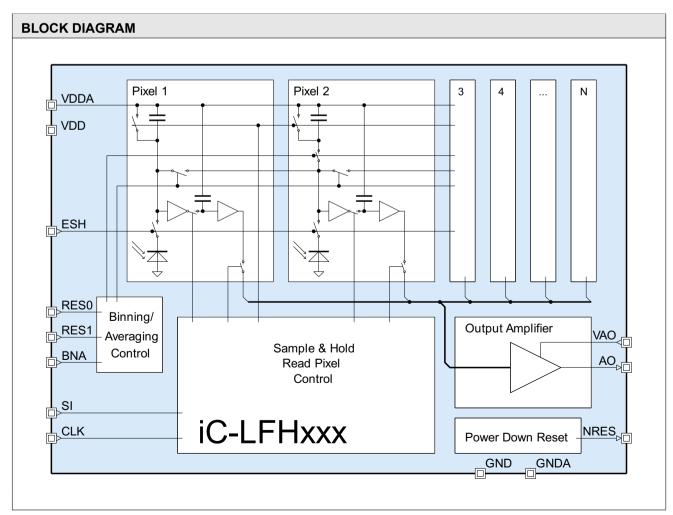

#### **DESCRIPTION**

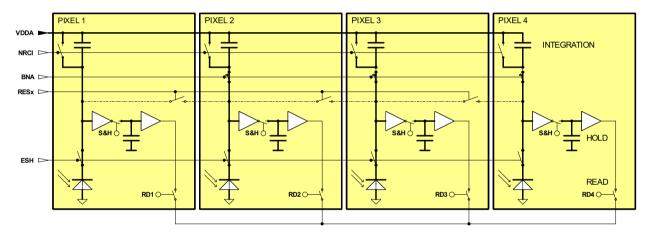

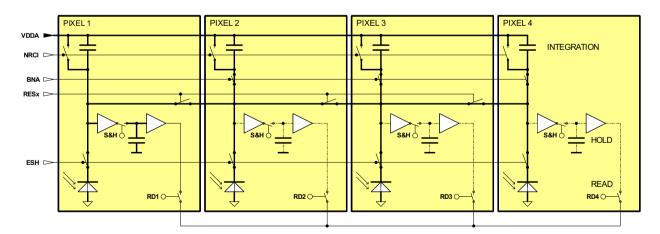

iC-LFH Series are integrating light-to-voltage converters with 1024/960/640/320 pixels pitched at 12.7 µm (center-to-center distance). Each pixel consists of a 12.7 µm x 600 µm photodiode, an integration capacitor, and a sample-and-hold circuit.

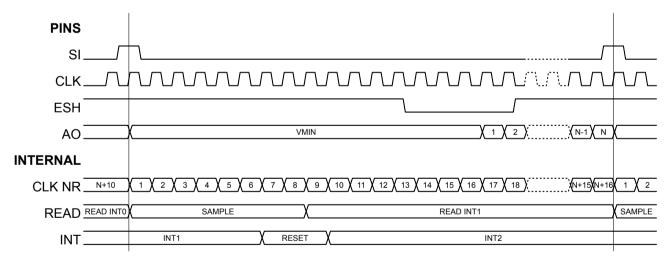

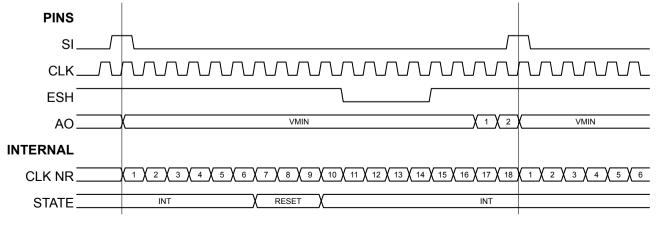

The control logic makes operation very easy, with only a start and clock signal necessary. A third input (ESH) optionally controls the asynchronous, global shutter.

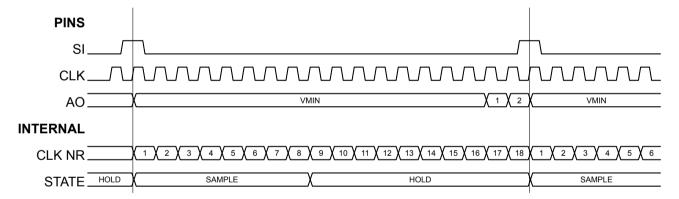

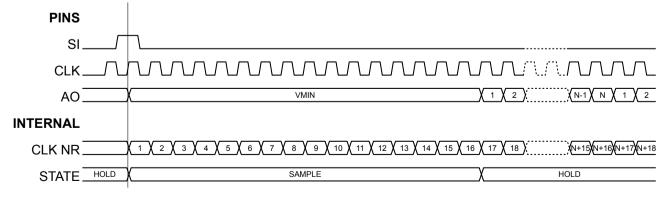

When the start signal is given, a new integration phase is initiated. Nine clocks are requiered to sample the current integration value and to reset the integration capacitor. After further 7 clocks, while the internal dark level voltage (VMIN) is output at AO, the value of the pixel #1 can be read out. With further clocks the following pixel voltages are output. The complete line sensor is read out after 1040/976/656/336 clock pulses respectively.

iC-LFHxxx is suitable for high pixel clock rates of up to 5 MHz.

#### **PACKAGING INFORMATION**

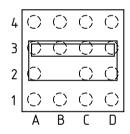

#### **PIN CONFIGURATION LFH1C**

#### **PIN FUNCTIONS**

| No. | Name | Function |

|-----|------|----------|

| Α1 | RES0 | Select Resolution Bit 0              |

|----|------|--------------------------------------|

| A2 | RES1 | Select Resolution Bit 1              |

| А3 | VAO  | Pixel Output Supply Voltage          |

| A4 | AO   | Analog Pixel Output                  |

| В1 | VDD  | Digital Supply +5 V                  |

| B2 | n/c  |                                      |

| B3 | n/c  |                                      |

| В4 | VDDA | Analog Supply +5 V                   |

| C1 | ETP  | Enable Test Mode*                    |

| C2 | GND  | Digital Ground                       |

| C3 | GNDA | Analog Ground                        |

| C4 | NRES | Power-Down Reset Output (low active) |

| D1 | CLK  | Clock                                |

| D2 | SI   | Start of Integration                 |

| D3 | ESH  | Enable Shutter                       |

| D4 | BNA  | Select Binning/Averaging             |

|    |      |                                      |

\*ETP must be connected to GND/GNDA

## preliminary

Rev B1, Page 3/14

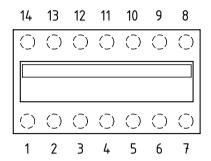

#### **PIN CONFIGURATION LFH2C**

#### **PIN FUNCTIONS**

| No   | Name  | Fund | tion |

|------|-------|------|------|

| INO. | manne | runc | JUOH |

1 RES0 Select Resolution Bit 0 Select Resolution Bit 1 2 RES1 Digital Supply +5 V 3 VDD 4 GND **Digital Ground** 5 ETP **Enable Test Mode\*** 6 SI Start of Integration

7 CLK Clock

Select Binning/Averaging 8 BNA

9 ESH **Enable Shutter**

10 NRES Power-Down Reset Output (low active)

11 GNDA Analog Ground 12 VDDA Analog Supply +5 V

13 VAO Pixel Output Supply Voltage

14 AO **Analog Pixel Output**

\*ETP must be connected to GND/GNDA

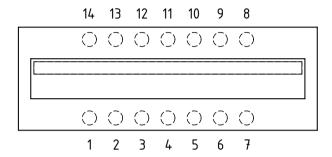

#### **PIN CONFIGURATION LFH3C**

| 14         | 13         | 12         | 11         | 10         | 9          | 8          |  |

|------------|------------|------------|------------|------------|------------|------------|--|

| $\bigcirc$ |  |

|            |            |            |            |            |            |            |  |

| $\bigcirc$ |  |

| 1          | 2          | 3          | 4          | 5          | 6          | 7          |  |

#### **PIN FUNCTIONS**

#### No. Name Function

1 RES0 Select Resolution Bit 0 Select Resolution Bit 1 2 RES1 3 VDD Digital Supply +5 V 4 GND Digital Ground Enable Test Mode\* 5 ETP 6 SI Start of Integration

7 CLK Clock

8 BNA Select Binning/Averaging

9 ESH **Enable Shutter**

10 NRES Power-Down Reset Output (low active)

11 GNDA Analog Ground 12 VDDA Analog Supply +5 V

Pixel Output Supply Voltage 13 VAO

14 AO **Analog Pixel Output**

\*ETP must be connected to GND/GNDA

## preliminary

HIGH-RESOLUTION LINEAR IMAGE SENSORS

Rev B1, Page 4/14

#### **PIN CONFIGURATION LFH5C**

#### **PIN FUNCTIONS**

#### No. Name Function

| 1 | RES0 | Select Resolution Bit 0  |

|---|------|--------------------------|

| 2 | RES1 | Select Resolution Bit 1  |

| 3 | VDD  | Digital Supply +5 V      |

| 4 | GND  | Digital Ground           |

| 5 | ETP  | Enable Test Mode*        |

| 6 | SI   | Start of Integration     |

| 7 | CLK  | Clock                    |

| 8 | BNA  | Select Binning/Averaging |

9 ESH Enable Shutter

10 NRES Power-Down Reset Output (low active)

11 GNDA Analog Ground 12 VDDA Analog Supply +5 V

Pixel Output Supply Voltage 13 VAO

**Analog Pixel Output** 14 AO

\*ETP must be connected to GND/GNDA

## preliminary

Rev B1, Page 5/14

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

HIGH-RESOLUTION LINEAR IMAGE SENSORS

| Item | Symbol | Parameter                                     | Conditions                            |      |           | Unit |

|------|--------|-----------------------------------------------|---------------------------------------|------|-----------|------|

| No.  |        |                                               |                                       | Min. | Max.      |      |

| G001 | VDD    | Digital Supply Voltage                        |                                       | -0.3 | 6         | V    |

| G002 | VDDA   | Analog Supply Voltage                         |                                       | -0.3 | 6         | V    |

| G003 | VAO    | Analog Output AO Supply Voltage               |                                       | -0.3 | 6         |      |

| G004 | V()    | Voltage at SI, CLK, ESH, RES0, RES1, BNA, ETP |                                       | -0.3 | VDD + 0.3 | V    |

| G005 | I()    | Current in AO                                 |                                       | -10  | 10        | mA   |

| G006 | Vd()   | ESD Susceptibility at all pins                | HBM 100 pF, discharged through 1.5 kΩ |      | 4         | kV   |

| G007 | Tj     | Junction Temperature                          |                                       | -40  | 150       | °C   |

| G008 | Ts     | Chip Storage Temperature                      |                                       | -40  | 150       | °C   |

#### **THERMAL DATA**

Operating Conditions: VDDA = VDD =  $5 V \pm 10 \%$

| ltem | Symbol | Parameter                     | Conditions                              |      |      |      |  |  |

|------|--------|-------------------------------|-----------------------------------------|------|------|------|--|--|

| No.  |        |                               |                                         | Min. | Тур. | Max. |  |  |

| T01  | Та     | Operating Ambient Temperature | See the relevant package specifications |      |      |      |  |  |

Rev B1, Page 6/14

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDDA = VDD = 5 V  $\pm 10$  %, Tj = -25...110 °C unless otherwise noted

| Item<br>No. | Symbol                  | Parameter                                                          | Conditions                                                                                                                                                           | Min.       | Тур.                            | Max.                 | Unit                 |

|-------------|-------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------|----------------------|----------------------|

| Total [     | Device                  |                                                                    |                                                                                                                                                                      |            |                                 |                      |                      |

| 001         | VDD                     | Digital Supply Voltage Range                                       |                                                                                                                                                                      | 4.5        |                                 | 5.5                  | V                    |

| 002         | VDDA                    | Analog Supply Voltage Range                                        |                                                                                                                                                                      | 4.5        |                                 | 5.5                  | V                    |

| 003         | I(VDD)                  | Supply Current in VDD                                              | f(CLK) = 1 MHz                                                                                                                                                       |            |                                 | 300                  | μA                   |

| 004         | I(VDDA)                 | Supply Current in VDDA                                             | N = 320<br>N = 640<br>N = 960<br>N = 1024                                                                                                                            |            | 11<br>20<br>26<br>28            | 15<br>25<br>30<br>32 | mA<br>mA<br>mA<br>mA |

| 005         | Vc()hi                  | Clamp Voltage hi at SI, CLK,<br>ESH, RES0, RES1, BNA, ETP,<br>NRES | Vc()hi = V() - V(VDD), I() = 1 mA                                                                                                                                    | 0.3        |                                 | 1.8                  | V                    |

| 006         | Vc()lo                  | Clamp Voltage Io at SI, CLK,<br>ESH, RES0, RES1, BNA, ETP,<br>NRES | Vc()hi = V() - V(GNDA), I() = -1 mA                                                                                                                                  | -1.5       |                                 | -0.3                 | V                    |

| 007         | Vc()hi                  | Clamp Voltage hi at AO                                             | Vc()hi = V(AO) - V(VAO), I(AO) = 1 mA                                                                                                                                | 0.3        |                                 | 1.5                  | V                    |

| 800         | Vc()lo                  | Clamp Voltage lo at AO, VDDA,<br>VDD, GND                          | Vc()lo = V() - V(GNDA), I() = -1 mA                                                                                                                                  | -1.5       |                                 | -0.3                 | V                    |

| Photo       | diode Array             |                                                                    |                                                                                                                                                                      |            |                                 |                      |                      |

| 201         | A()                     | Radiant Sensitive Area                                             | 600 μm x 12.70 μm, per Pixel                                                                                                                                         |            | 0.00762                         |                      | mm <sup>2</sup>      |

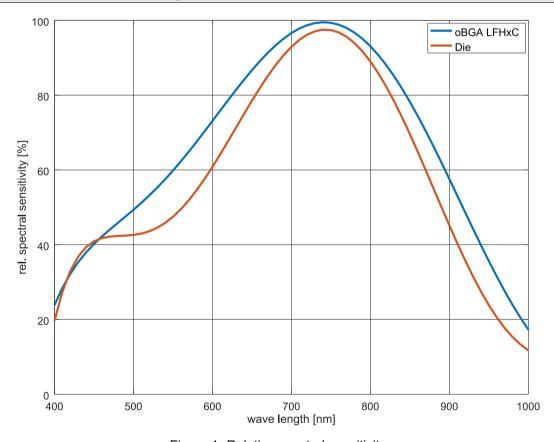

| 203         | $\lambda$ ar            | Spectral Application Range                                         | $S(\lambda ar) = 0.25 \times S(\lambda) max$                                                                                                                         | 420        |                                 | 980                  | nm                   |

| Analo       | gue Output              | AO, VAO                                                            |                                                                                                                                                                      |            |                                 |                      |                      |

|             |                         | Permissible Input Voltage                                          | G(AO) = 1<br>G(AO) = 1.67                                                                                                                                            | 3<br>4.5   | 3.3<br>5.0                      | 3.6<br>5.5           | V                    |

| 302         | I(VAO)                  | Supply Current in VAO                                              | 10 pF load at AO, f(CLK) = 5 MHz;<br>V(VAO) = 33.6 V<br>V(VAO) = 4.55.5 V                                                                                            |            |                                 | 2.5<br>3             | mA<br>mA             |

| 303         | G(AO)                   | Gain                                                               | VAO < th(VAO)<br>VAO > th(VAO)                                                                                                                                       | 0.9<br>1.3 | 1<br>1.67                       | 1.1<br>1.8           |                      |

| 304         | Vt(VAO)hi               | Threshold Voltage Gain Switch hi                                   |                                                                                                                                                                      | 3.7        |                                 | 4.6                  | V                    |

| 305         | Vt(VAO)lo               | Threshold Voltage Gain Switch lo                                   |                                                                                                                                                                      | 3.5        |                                 | 4.4                  | V                    |

| 306         | Vt(VAO)hys              | Hysteresis Gain Switch                                             |                                                                                                                                                                      | 100        |                                 | 350                  | mV                   |

| 308         | Vs(AO)hi                | Saturation Voltage hi                                              | Vs(AO)hi = VAO - V(AO), I(AO) = -2 mA                                                                                                                                |            | 120                             | 250                  | mV                   |

| 311         | KR                      | Sensitivity Sensitivity Ratio                                      | RES1/0 = 00, $\lambda$ = 775 nm;<br>G(AO) = 1<br>G(AO) = 1.67<br>K(Binning * 2) / K<br>K(Binning * 4) / K<br>K(Binning * 8) / K<br>K(Averaging * X) / K; X = 2, 4, 8 |            | 0.9<br>1.5<br>1.8<br>3.3<br>4.7 |                      | V/pWs<br>V/pWs       |

| 312         | V0(AO)                  | Offset Voltage                                                     | Integration time 1 ms, no illumination                                                                                                                               | 100        | 200                             | 500                  | mV                   |

| 313         | ΔV0(AO)                 | Offset Voltage Deviation during integration mode                   | $\Delta$ V0(AO) = V(AO)t1 - V(AO)t2,<br>$\Delta$ t = t2 - t1 = 1 ms                                                                                                  | -150       |                                 | 150                  | mV                   |

| 314         | ∆V(AO)                  | Signal Deviation during hold mode                                  | $\Delta V(AO) = V(AO)t1 - V(AO)t2,$<br>$\Delta t = t2 - t1 = 1 \text{ ms}$                                                                                           | -150       |                                 | 150                  | mV                   |

| 315         | tp(CLK-AO)              | Settling Time                                                      | CI(AO) = 10  pF,<br>$CLK \text{ Io} \rightarrow \text{hi until V(AO)} = 0.95 * Vs(AO)\text{hi}$                                                                      |            |                                 | 200*                 | ns                   |

| 316         | PRNU                    | Pixel Response Nonuniformity                                       | V(AO) = 2.5 V                                                                                                                                                        |            | ±10                             | ±15                  | %                    |

| 317         | INL                     | Integral Nonlinearity                                              | G(AO) = 1: V(AO) = 0.53.0 V,<br>G(AO) = 1.67: V(AO) = 0.54.5 V                                                                                                       |            | ±1.5*                           |                      | %                    |

| 318         | V <sub>noise</sub> (AO) | Output Noise Voltage                                               | V(AO) = 2.5 V                                                                                                                                                        |            | 1.5*                            |                      | $mV_{RMS}$           |

| 319         | DR                      | Dynamic Range <sup>†</sup>                                         | V(VAO) = 5.0 V; V(AO) <sub>max</sub> = 5 V<br>V(VAO) = 3.3 V; V(AO) <sub>max</sub> = 3.3 V                                                                           |            | 70<br>66                        |                      | dB<br>dB             |

| 320         | V(AO)min                | Output Reference Voltage                                           |                                                                                                                                                                      | 150        | 200                             | 280                  | mV                   |

|             | -Down Rese              |                                                                    |                                                                                                                                                                      |            | I                               | 1                    | П                    |

| 801         | VDDon                   | Power-On Release by VDD                                            |                                                                                                                                                                      |            | 4.0                             | 4.4                  | V                    |

## preliminary

Rev B1, Page 7/14

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDDA = VDD = 5 V ±10 %, Tj = -25...110 °C unless otherwise noted

| Item   | Symbol       | Parameter                     | Conditions                                               |                    |      |      | Unit |

|--------|--------------|-------------------------------|----------------------------------------------------------|--------------------|------|------|------|

| No.    |              |                               |                                                          | Min.               | Тур. | Max. |      |

| 802    | VDDoff       | Power-Down Reset by VDD       |                                                          | 3.0                | 3.5  |      | V    |

| 803    | VDDhys       | Hysteresis                    | VDDhys = VDDon - VDDoff                                  | 350                | 460  | 800  | mV   |

| 804    | Vs()lo       | Saturation Voltage lo         | I() = 1.6 mA                                             | 0                  |      | 0.3  | V    |

| 805    | Vs()hi       | Saturation Voltage hi         | I() = -1.6 mA, Vs()hi = VDD - V()                        | 0                  |      | 0.3  | V    |

| 806    | Isc()lo      | Short Current lo              | V() = lo and pin shorted with VDD                        | 5                  |      | 70   | mA   |

| 807    | Isc()hi      | Short Current hi              | V() = hi and pin shorted with GND                        | -70                |      | -5   | mA   |

| TTL In | put Interfac | e BNA, CLK, ESH, ETP, RES0, R | ES1, SI                                                  |                    |      |      |      |

| I01    | Vt()hi       | Threshold Voltage hi          |                                                          |                    |      | 2.0  | V    |

| 102    | Vt()lo       | Threshold Voltage lo          |                                                          | 0.8                |      |      | V    |

| 103    | Vt()hys      | Hysteresis                    | Vt()hys = Vt()hi - Vt()lo                                | 200                |      | 500  | mV   |

| 104    | l()pd        | Pull-Down Current             |                                                          | 5                  | 30   | 70   | μA   |

| 105    | fclk         | Permissible Clock Frequency   | Reset integration and digital control Read Pixel and S&H |                    |      | 10   | MHz  |

|        |              |                               | N = 320                                                  | (0.3)‡             |      | 5    | MHz  |

|        |              |                               | N = 640                                                  | $(0.6)^{\ddagger}$ |      | 5    | MHz  |

|        |              |                               | N = 960, 1024                                            | (1)‡               |      | 5    | MHz  |

#### **OPTICAL CHARACTERISTICS: Diagrams**

Figure 1: Relative spectral sensitivity

<sup>\*</sup> Projected values by sample characterization †  $DR = 20 \times log \frac{V(AO)_{max} - V0(AO)_{max}}{V_{noise}(AO)}$

<sup>‡</sup> Relates to a 1 ms hold time; cf. Electrcal Characteristics Nos. 313 and 314.

# preliminary (

Rev B1, Page 8/14

#### **OPERATING REQUIREMENTS: Integration and Read Control**

Operating conditions: VDDA = VDD = 4.5...5.5 V, GNDA = GND = 0 V, Tj = -25...110 °C

| Item    | Symbol                      | Parameter                                            | Conditions |      |      | Unit |

|---------|-----------------------------|------------------------------------------------------|------------|------|------|------|

| No.     |                             |                                                      |            | Min. | Max. |      |

| Integra | ntegration and Read Control |                                                      |            |      |      |      |

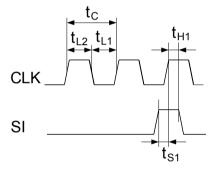

| 1001    | t <sub>C</sub>              | Permissible Clock Period CLK                         |            | 100  |      | ns   |

| 1002    | t <sub>L1</sub>             | Clock Signal CLK Hi-Level<br>Duration                |            | 50   |      | ns   |

| 1003    | t <sub>L2</sub>             | Clock Signal CLK Lo-Level Duration                   |            | 50   |      | ns   |

| 1004    | t <sub>S1</sub>             | Setup Time: SI stable before CLK lo $\rightarrow$ hi |            | 50   |      | ns   |

| 1005    | t <sub>H1</sub>             | Hold Time: SI stable after CLK lo $\rightarrow$ hi   |            | 50   |      | ns   |

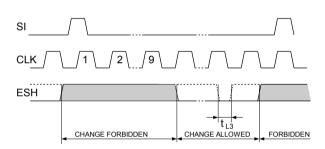

| 1006    | t <sub>L3</sub>             | Shutter Signal ESH Lo-Level Duration                 |            | 100  |      | ns   |

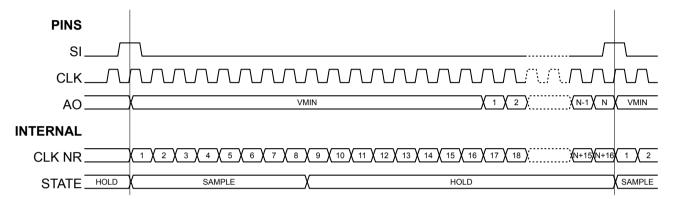

Figure 2: Timing diagram

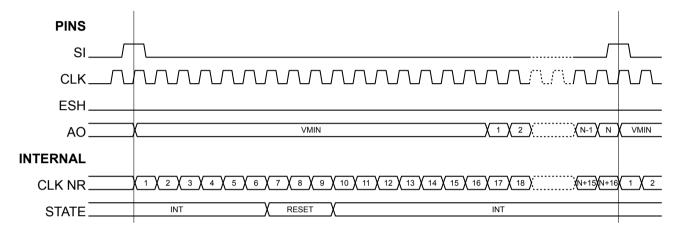

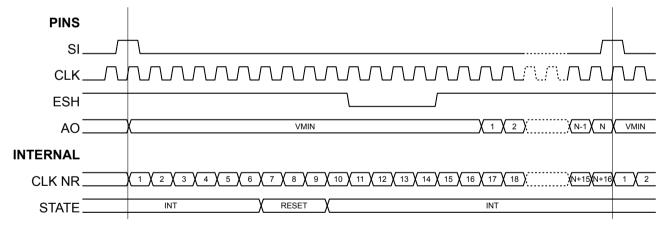

Figure 3: Timing diagram shutter

## preliminary

Rev B1, Page 9/14

#### **DESCRIPTION OF FUNCTIONS**

#### Pixel structure and resolution

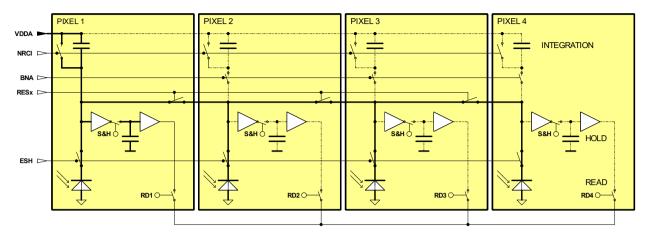

One pixel consist of a photodiode, an integration capacitor, and an S&H stage. For reducing the resolution, the pixels can be grouped together by means of pins RES1/0. Changing the resolution can be achieved in two ways, binning or averaging. Averaging does not change the sensitivity, whereas binning increases the sensitivity by the ratio given in the table on the right. Pin BNA selects the mode respectively.

| PINS RES1 | PINS RES1/0                                   |               |            |                                |  |  |  |

|-----------|-----------------------------------------------|---------------|------------|--------------------------------|--|--|--|

| State     | Pin BNA                                       | Pixels        | Resolution | Sensitivity ratio <sup>1</sup> |  |  |  |

| 0/0       | -                                             | N pixels      | 2000 dpi   | 1                              |  |  |  |

| 0/1       | 0                                             | N/2 pixels    | 1000 dpi   | 1                              |  |  |  |

|           | 1                                             | N/2 pixels    | 1000 dpi   | 1.8                            |  |  |  |

| 1/0       | 0                                             | N/4 pixels    | 500 dpi    | 1                              |  |  |  |

|           | 1                                             | N/4 pixels    | 500 dpi    | 3.3                            |  |  |  |

| 1/1       | 0                                             | N/8 pixels    | 250 dpi    | 1                              |  |  |  |

|           | 1                                             | N/8 pixels    | 250 dpi    | 4.7                            |  |  |  |

|           | <sup>1</sup> all pixels uniformly illuminated |               |            |                                |  |  |  |

|           | N = 320/640                                   | /960/1024 pix | els        |                                |  |  |  |

Figure 4: Pixel structure with RES1/0 = 00

Figure 5: Pixel structure with resolution change and averaging mode

## preliminary 624

### HIGH-RESOLUTION LINEAR IMAGE SENSORS

Rev B1, Page 10/14

Figure 6: Pixel structure with resolution change and binning mode

#### **Operation description**

Following an internal power-on reset the integration and hold capacitors are discharged. A high signal at SI and a rising edge at CLK triggers a readout cycle and with it a new integration cycle. Six clocks later the internal reset is done and the device is in integration mode. The readout of the analog pixel values starts with the 17<sup>th</sup> clock pulse.

#### Operation with the shutter function

Integration can be suspended at any time via pin ESH (asynchronous, global shutter), i.e. the photodiodes are disconnected from their corresponding integration capacitor when ESH is high and the current integration capacitor voltages are maintained. If this pin is open or switched to GND, the pixel photocurrents are summed up by the integration capacitors until the next SI signal.

Figure 7: example integration and readout cycle

## preliminary

Rev B1, Page 11/14

#### **READ CONTROL**

The readout of the analog pixel values is controlled by the following pins:

- Pin SI

- · Pin CLK

A rising CLK edge with a hi value at SI resets the internal read out circuit, initiating a readout of the previously sampled pixel values. While clocking more then N clocks the read out will restart with pixel #1 without sampling. Thus a non-destructive re-read is possible.

Figure 8: Complete readout cycle

Figure 9: Interrupting the readout cycle

Figure 10: Non-destructive restart of readout cycle

## preliminary

Rev B1, Page 12/14

#### **INTEGRATION CONTROL**

The integration is controlled by the signals:

- Pin SI

- Pin CLK

- Pin ESH

A new integration phase is started with a rising CLK edge and SI high. After 9 clocks a new integration cy-

cle is initiated. With pin ESH = lo all photodiodes are connected to the internal capacitors and the photodiode currents are integrated. The integration can be suspended by setting pin ESH to hi, disconnecting the photodiodes from their integration capacitors.

Figure 11: Integration cycle

Figure 12: Integration cycle with shutter action

Figure 13: Integration cycle with shutter action and readout interrupt

## preliminary

Rev B1, Page 13/14

#### **DESIGN REVIEW: Function Notes**

| iC-LFHxxx<br>1 |                                                                       |                                                   |

|----------------|-----------------------------------------------------------------------|---------------------------------------------------|

| No.            | Function, parameter/code                                              | Description and application notes                 |

| 1              | Sensitivity ratio with binning,<br>Electrical Characteristics No. 309 | Gain increase in binning is lower than stated     |

| 2              | Settling time,<br>Electrical Characteristics No. 314                  | Dips in the pixel voltage slow down settling time |

Table 5: Notes on chip functions regarding iC-LFHxxx chip release 1

| iC-LFHxxx<br>Z |                                                      |                                                   |

|----------------|------------------------------------------------------|---------------------------------------------------|

| No.            | Function, parameter/code                             | Description and application notes                 |

| 1              | Binning/averaging                                    | Binning/averaging cannot be used                  |

| 2              | Settling time,<br>Electrical Characteristics No. 314 | Dips in the pixel voltage slow down settling time |

Table 6: Notes on chip functions regarding iC-LFHxxx chip release Z

| iC-LFHxxx<br>Z1 |                                                      |                                                   |  |

|-----------------|------------------------------------------------------|---------------------------------------------------|--|

| No.             | Function, parameter/code                             | Description and application notes                 |  |

| 1               | Settling time,<br>Electrical Characteristics No. 314 | Dips in the pixel voltage slow down settling time |  |

Table 7: Notes on chip functions regarding iC-LFHxxx chip release Z1

#### **REVISION HISTORY**

| Rel. | Rel. Date* | Chapter                       | Modification                              | Page |

|------|------------|-------------------------------|-------------------------------------------|------|

| B1   | 2017-09-01 | ELECTRICAL<br>CHARACTERISTICS | Operating conditions: Tj = -25110 °C      | 6-7  |

|      |            | ELECTRICAL<br>CHARACTERISTICS | Item No. 302 added                        | 6    |

|      |            | ELECTRICAL<br>CHARACTERISTICS | Item Nos. 309, 311 corrected              | 6    |

|      |            | ELECTRICAL<br>CHARACTERISTICS | OPTICAL CHARACTERISTICS: Diagrams updated | 7    |

|      |            | OPERATING REQUIREMENTS        | Operating conditions: Tj = -25110 °C      | 8    |

|      |            | DESCRIPTION OF FUNCTIONS      | PINS RES1/0 table corrected               | 9    |

iC-Haus expressly reserves the right to change its products and/or specifications. An Infoletter gives details as to any amendments and additions made to the relevant current specifications on our internet website www.ichaus.com/infoletter and is automatically generated and shall be sent to registered users by email. Copying - even as an excerpt - is only permitted with iC-Haus' approval in writing and precise reference to source.

The data specified is intended solely for the purpose of product description and shall represent the usual quality of the product. In case the specifications contain obvious mistakes e.g. in writing or calculation, iC-Haus reserves the right to correct the specification and no liability arises insofar that the specification was from a third party view obviously not reliable. There shall be no claims based on defects as to quality in cases of insignificant deviations from the specifications or in case of only minor impairment of usability.

No representations or warranties, either expressed or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus products are not designed for and must not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (Safety-Critical Applications) without iC-Haus' specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems. iC-Haus products are not designed nor intended for use in military or aerospace applications or environments or in automotive applications unless specifically designated for such use by iC-Haus.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

Software and its documentation is provided by iC-Haus GmbH or contributors "AS IS" and is subject to the ZVEI General Conditions for the Supply of Products and Services with iC-Haus amendments and the ZVEI Software clause with iC-Haus amendments (www.ichaus.com/EULA).

<sup>\*</sup> Release Date format: YYYY-MM-DD

## preliminary HIGH-RESOLUTION LINEAR IMAGE SENSORS

Rev B1, Page 14/14

#### **ORDERING INFORMATION**

| Туре       | Package    | Order Designation     |

|------------|------------|-----------------------|

| iC-LFH320  | oBGA LFH1C | iC-LFH320 oBGA LFH1C  |

| iC-LFH640  | oBGA LFH2C | iC-LFH640 oBGA LFH2C  |

| iC-LFH960  | oBGA LFH3C | iC-LFH960 oBGA LFH3C  |

| iC-LFH1024 | oBGA LFH5C | iC-LFH1024 oBGA LFH5C |

Please send your purchase orders to our order handling team:

Fax: +49 (0) 61 35 - 92 92 - 692 E-Mail: dispo@ichaus.com

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Tel.: +49 (0) 61 35 - 92 92 - 0 **Am Kuemmerling 18** Fax: +49 (0) 61 35 - 92 92 - 192 D-55294 Bodenheim Web: http://www.ichaus.com **GERMANY** E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.com/sales\_partners